# RENESAS

# HA16114P/PJ/FP/FPJ, HA16120FP/FPJ

Switching Regulator for Chopper Type DC/DC Converter

REJ03F0055-0200Z (Previous: ADE-204-020A) Rev.2.0 Sep.18.2003

# Description

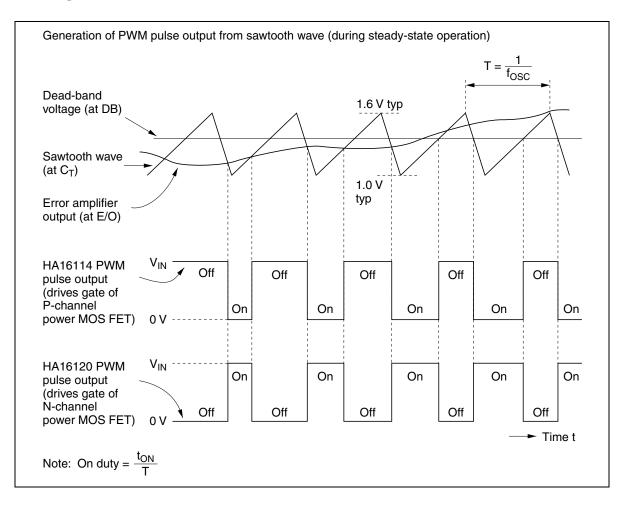

The HA16114P/FP/FPJ and HA16120FP/FPJ are single-channel PWM switching regulator controller ICs suitable for chopper-type DC/DC converters. Integrated totem-pole output circuits enable these ICs to drive the gate of a power MOSFET directly. The output logic of the HA16120 is designed to control a DC/DC step-up (boost) converter using an N-channel power MOS FET. The output logic of the HA16114 is designed to control a DC/DC step-down (buck) converter or inverting converter using a P-channel power MOS FET.

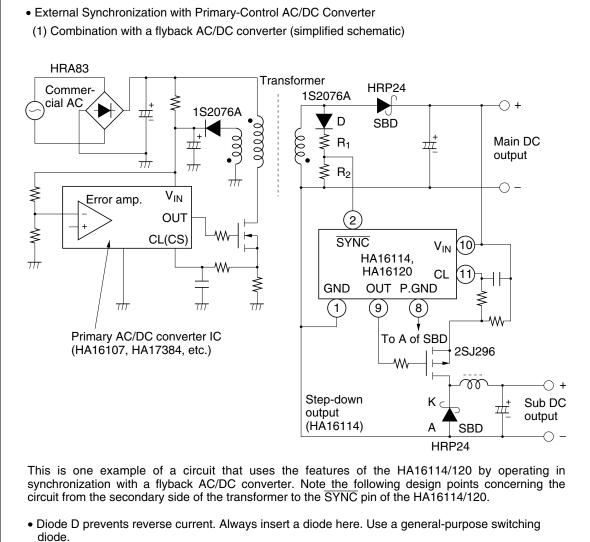

These ICs can operate synchronously with external pulse, a feature that makes them ideal for power supplies that use a primary-control AC/DC converter to convert commercial AC power to DC, then use one or more DC/DC converters on the secondary side to obtain multiple DC outputs. Synchronization is with the falling edge of the 'sync' pulse, which can be the secondary output pulse from a flyback transformer. Synchronization eliminates the beat interference that can arise from different operating frequencies of the AC/DC and DC/DC converters, and reduces harmonic noise. Synchronization with an AC/DC converter using a forward transformer is also possible, by inverting the 'sync' pulse.

Overcurrent protection features include a pulse-by-pulse current limiter that can reduce the width of individual PWM pulses, and an intermittent operating mode controlled by an on-off timer. Unlike the conventional latched shutdown function, the intermittent operating function turns the IC on and off at controlled intervals when pulse-by-pulse current limiting continues for a programmable time. This results in sharp vertical settling characteristics. Output recovers automatically when the overcurrent condition subsides.

Using these ICs, a compact, highly efficient DC/DC converter can be designed easily, with a reduced number of external components.

# Functions

- 2.5 V voltage reference

- Sawtooth oscillator (Triangle wave)

- Overcurrent detection

- External synchronous input

- Totem-pole output

- Undervoltage lockout (UVL)

- Error amplifier

- Vref overvoltage protection (OVP)

Rev.2.0, Sep.18.2003, page 1 of 37

# Features

- Wide supply voltage range: 3.9 V to 40 V\*

- Maximum operating frequency: 600 kHz

- Able to drive a power MOS FET (±1 A maximum peak current) by the built-in totem-pole gate predriver circuit

- Can operate in synchronization with an external pulse signal, or with another controller IC

- Pulse-by-pulse overcurrent limiting (OCL)

- Intermittent operation under continuous overcurrent

- Low quiescent current drain when shut off by grounding the ON/OFF pin HA16114: I<sub>OFF</sub> = 10 μA (max) HA16120: I<sub>OFF</sub> = 150 μA (max)

- Externally trimmable reference voltage (Vref): ±0.2 V

- Externally adjustable undervoltage lockout points (with respect to  $V_{IN}$ )

- Stable oscillator frequency

- Soft start and quick shut function

Note: The reference voltage 2.5 V is under the condition of  $V_{IN} \ge 4.5$  V.

# **Ordering Information**

#### Hitachi Control ICs for Chopper-Type DC/DC Converters

|          | Product | Channel | Control Functions |                     |   |                 | Overcurrent                               |  |  |

|----------|---------|---------|-------------------|---------------------|---|-----------------|-------------------------------------------|--|--|

| Channels | Number  | No.     | Step-Up           | Step-Down Inverting |   | Output Circuits | Protection                                |  |  |

| Dual     | HA17451 | Ch 1    | О                 | О                   | 0 | Open collector  | SCP with timer (latch)                    |  |  |

|          |         | Ch 2    | О                 | О                   | 0 |                 |                                           |  |  |

| Single   | HA16114 | _       | _                 | О                   | О | Totem pole      | Pulse-by-pulse                            |  |  |

|          | HA16120 | _       | 0                 | _                   | _ | power MOS FET   | current limiter and                       |  |  |

| Dual     | HA16116 | Ch 1    | _                 | 0                   | 0 | driver          | intermittent operation<br>by on/off timer |  |  |

|          |         | Ch 2    | —                 | О                   | _ |                 |                                           |  |  |

|          | HA16121 | Ch 1    | _                 | О                   | О | -               |                                           |  |  |

|          |         | Ch 2    | 0                 | _                   | _ |                 |                                           |  |  |

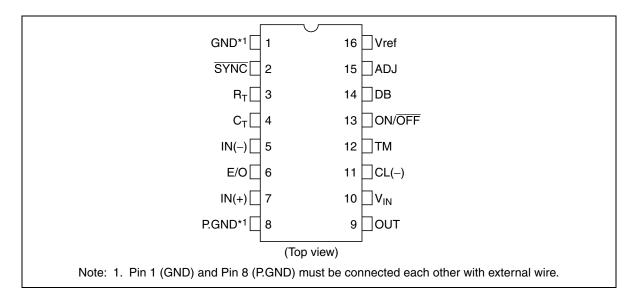

# **Pin Arrangement**

# **Pin Description**

| Pin No. | Symbol          | Function                                                                                                 |

|---------|-----------------|----------------------------------------------------------------------------------------------------------|

| 1       | GND             | Signal ground                                                                                            |

| 2       | SYNC            | External sync signal input (synchronized with falling edge)                                              |

| 3       | $R_{T}$         | Oscillator timing resistor connection (bias current control)                                             |

| 4       | C <sub>T</sub>  | Oscillator timing capacitor connection (sawtooth voltage output)                                         |

| 5       | IN(–)           | Inverting input to error amplifier                                                                       |

| 6       | E/O             | Error amplifier output                                                                                   |

| 7       | IN(+)           | Non-inverting input to error amplifier                                                                   |

| 8       | P.GND           | Power ground                                                                                             |

| 9       | OUT             | Output (pulse output to gate of power MOS FET)                                                           |

| 10      | V <sub>IN</sub> | Power supply input                                                                                       |

| 11      | CL(-)           | Inverting input to current limiter                                                                       |

| 12      | ТМ              | Timer setting for intermittent shutdown when overcurrent is detected<br>(sinks timer transistor current) |

| 13      | ON/OFF          | IC on/off control (off below approximately 0.7 V)                                                        |

| 14      | DB              | Dead-band duty cycle control input                                                                       |

| 15      | ADJ             | Reference voltage (Vref) adjustment input                                                                |

| 16      | Vref            | 2.5 V reference voltage output                                                                           |

Rev.2.0, Sep.18.2003, page 3 of 37

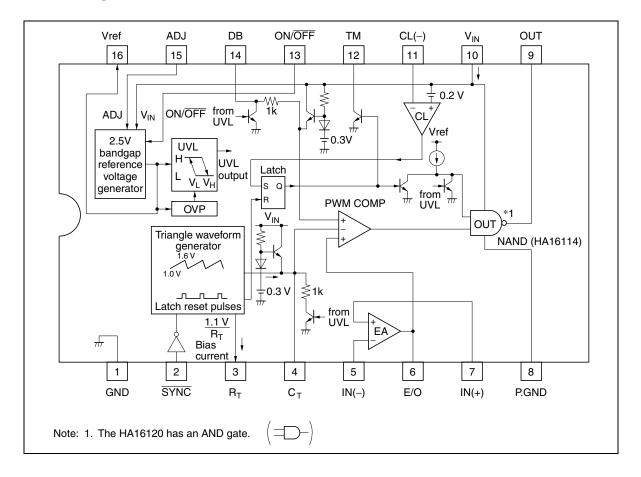

# **Block Diagram**

Rev.2.0, Sep.18.2003, page 4 of 37

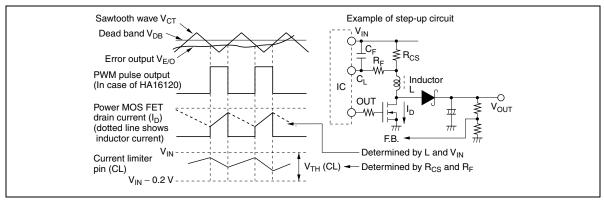

# **Timing Waveforms**

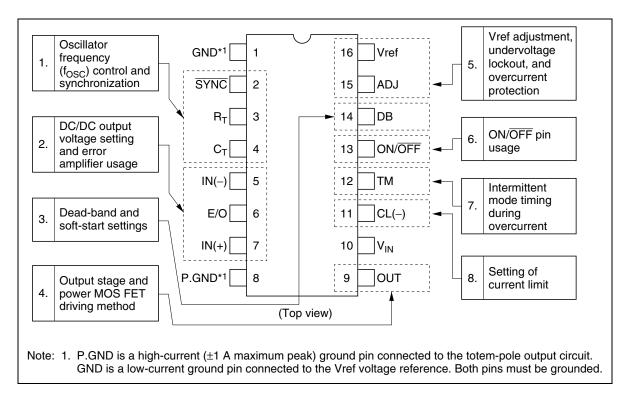

# **Guide to the Functional Description**

The description covers the topics indicated below.

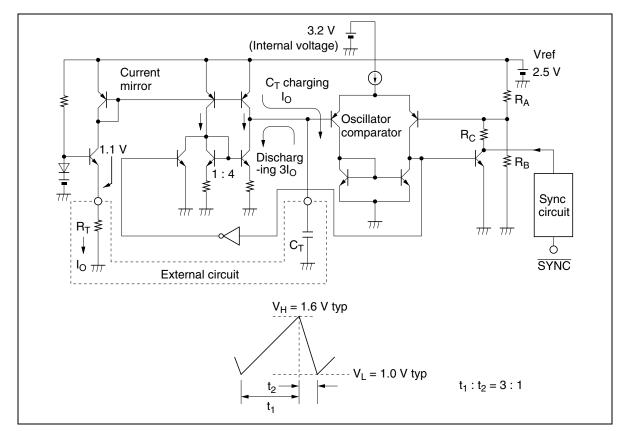

#### 1. Sawtooth Oscillator (Triangle Wave)

#### 1.1 Operation and Frequency Control

The sawtooth wave is a voltage waveform from which the PWM pulses are created (See figure 1). The sawtooth oscillator operates as follows. A constant current  $I_o$  determined by an external timing resistor  $R_T$  is fed continuously to an external timing capacitor  $C_T$ . When the  $C_T$  pin voltage exceeds a comparator threshold voltage  $V_{TH}$ , the comparator output opens a switching transistor, allowing a  $3I_o$  discharge current to flow from  $C_T$ . When the  $C_T$  pin voltage drops below a threshold voltage  $V_{TL}$ , the comparator output closes the switching transistor, stopping the  $3I_o$  discharge. Repetition of these operations generates a sawtooth wave.

The value of  $I_0$  is 1.1 V/R<sub>T</sub>  $\Omega$ . The  $I_0$  current mirror has a limited current capacity, so R<sub>T</sub> should be at least 5 k $\Omega$  ( $I_0 \le 220 \ \mu$ A).

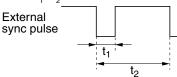

Internal resistances  $R_A$ ,  $R_B$ , and  $R_C$  set the peak and valley voltages  $V_{TH}$  and  $V_{TL}$  of the sawtooth waveform at approximately 1.6 V and 1.0 V.

Rev.2.0, Sep.18.2003, page 6 of 37

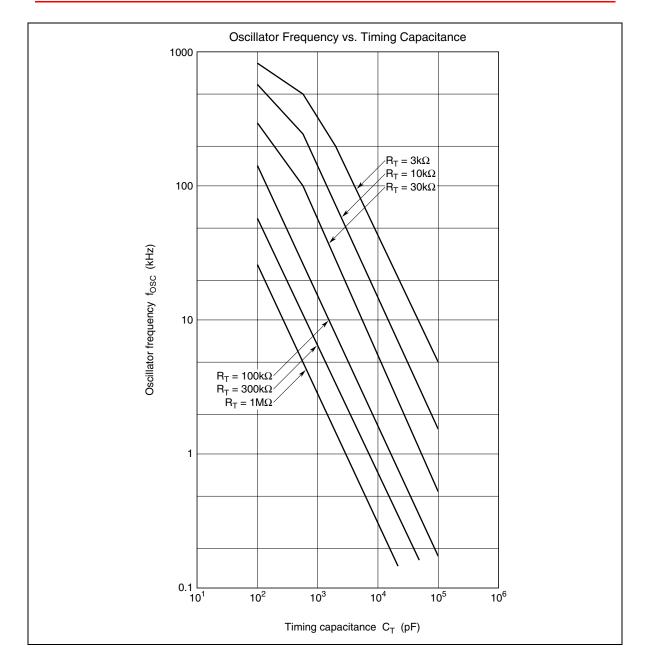

The oscillator frequency  $f_{\rm osc}$  can be calculated as follows.

$$f_{OSC} = \frac{1}{t_1 + t_2 + t_3}$$

Here,  $t_1 = \frac{C_T \times (V_H - V_L)}{1.1 \text{ V/R}_T}$

$t_2 = \frac{C_T \times (V_H - V_L)}{3 \times 1.1 \text{ V/R}_T}$

$t_3 \approx 0.8 \ \mu s$  (comparator delay time)

Since

$$V_H - V_L = 0.6 V$$

$f_{OSC} \approx \frac{1}{0.73 \times C_T \times R_T + 0.8 (\mu s)}$  (Hz)

At high frequencies the comparator delay causes the sawtooth wave to overshoot the 1.6 V threshold and undershoot the 1.0 V threshold, and changes the dead-band thresholds accordingly. Select constants by testing under implementation conditions.

Figure 1.1 Equivalent Circuit of Oscillator

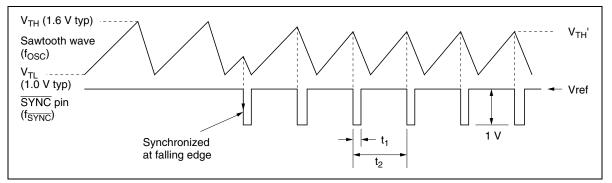

#### **1.2 External Synchronization**

These ICs have a sync input pin so that they can be synchronized to a primary-control AC/DC converter. Pulses from the secondary winding of the switching transformer should be dropped through a resistor voltage divider to the sync input pin. Synchronization takes place at the falling edge, which is optimal for multiple-output power supplies that synchronize with a flyback AC/DC converter.

The sync input pin (SYNC) is connected internally through a synchronizing circuit to the sawtooth oscillator to synchronize the sawtooth waveform (see figure 1.2).

- Synchronization is with the falling edge of the external sync signal.

- The frequency of the external sync signal must be in the range  $f_{osc} < f_{SYNC} < f_{osc} \times 2$ .

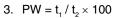

- The duty cycle of the external sync signal must be in the range  $5\% < t_1/t_2 < 50\%$  ( $t_1 = 300$  ns Min).

- With external synchronization,  $V_{TH}$  can be calculated as follows.

$$V_{TH}' = (V_{TH} - V_{TL}) \times \frac{f_{OSC}}{f_{SYNC}} + V_{TL}$$

Note: When not using external synchronization, connect the SYNC pin to the Vref pin.

Figure 1.2 External Synchronization

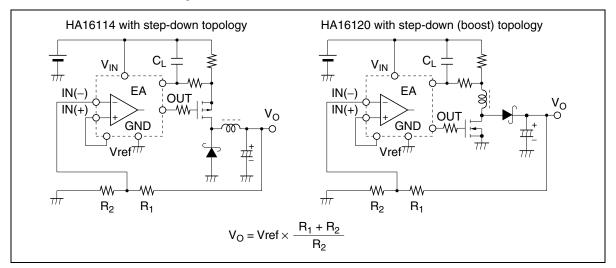

#### 2. DC/DC Output Voltage Setting and Error Amplifier Usage

#### 2.1 DC/DC Output Voltage Setting

1. Positive Output Voltage ( $V_0 > Vref$ )

Figure 2.1 Output Voltage Setting (1)

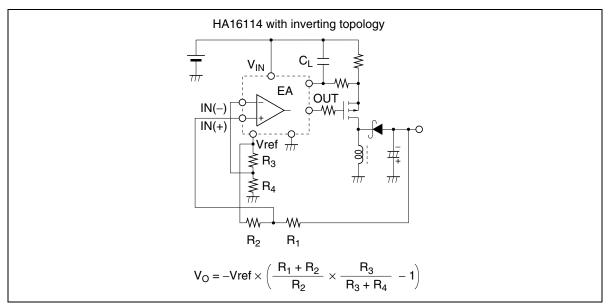

2. Negative Output Voltage ( $V_0 < 0 V$ )

Figure 2.2 Output Voltage Setting (2)

#### 2.2 Error Amplifier Usage

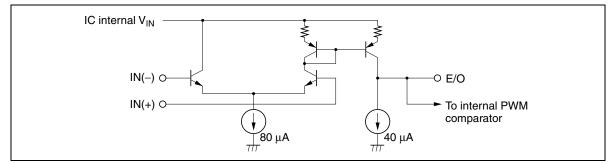

Figure 2.3 shows an equivalent circuit of the error amplifier. The error amplifier in these ICs is a simple NPN-transistor differential amplifier with a constant-current-driven output circuit.

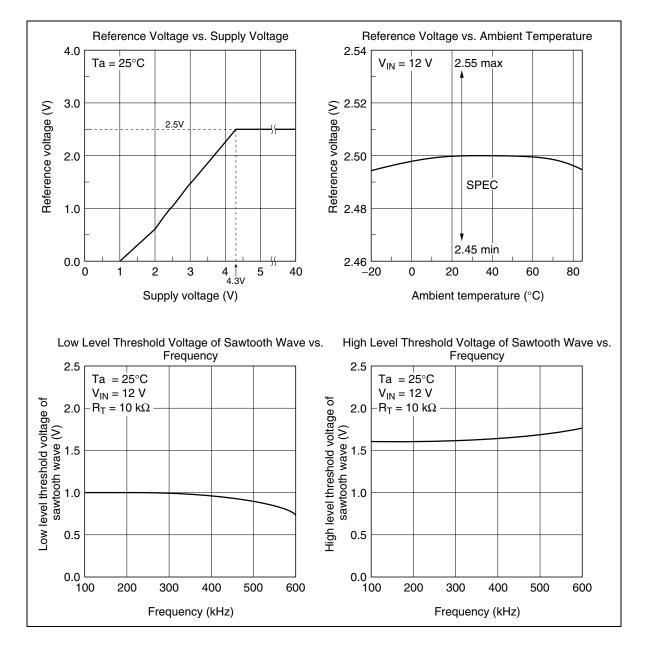

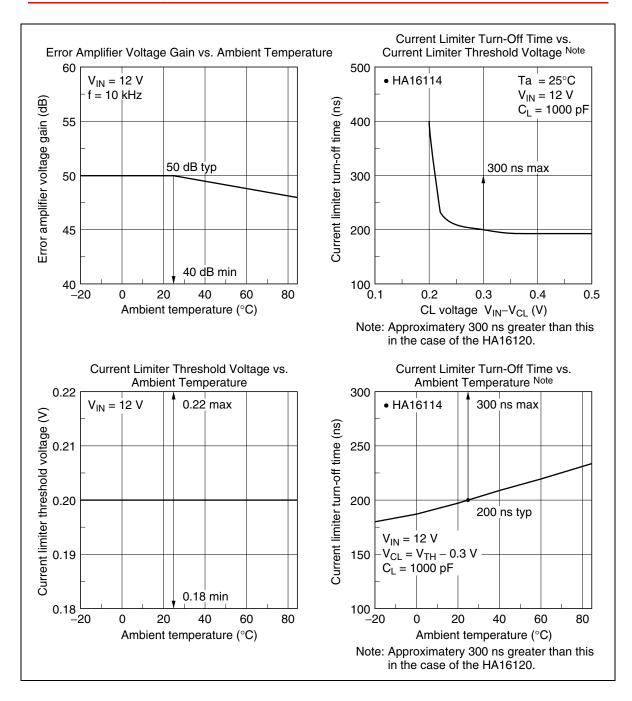

The amplifier combines a wide bandwidth ( $f_T = 4 \text{ MHz}$ ) with a low open-loop gain (50 dB Typ), allowing stable feedback to be applied when the power supply is designed. Phase compensation is also easy.

Figure 2.3 Error Amplifier Equivalent Circuit

#### 3. Dead-Band Duty Cycle and Soft-Start Settings

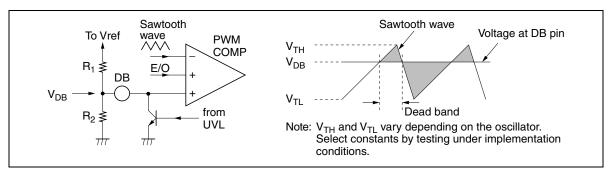

### 3.1 Dead-Band Duty Cycle Setting

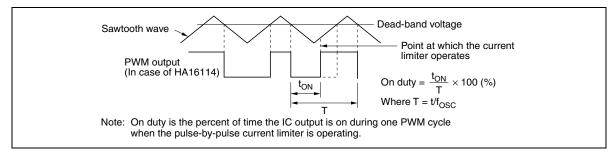

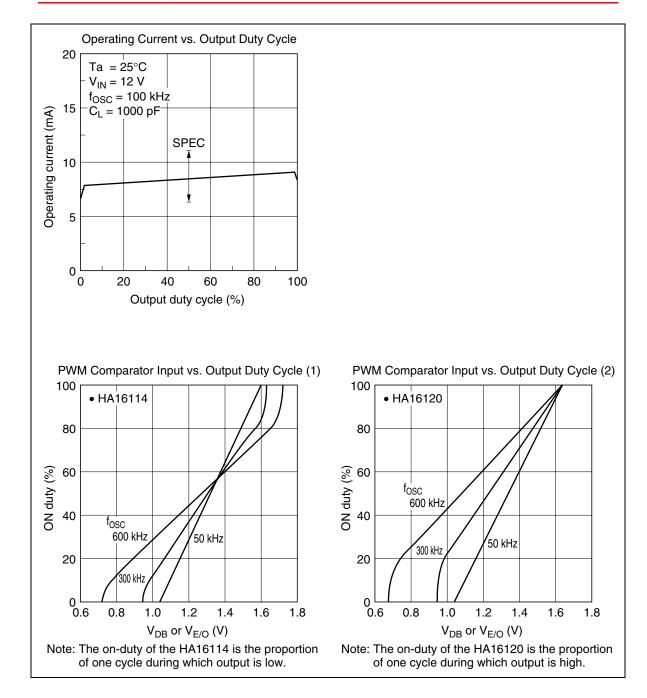

The dead-band duty cycle (the maximum duty cycle of the PWM pulse output) can be programmed by the voltage  $V_{DB}$  at the DB pin. A convenient way to obtain  $V_{DB}$  is to divide the IC's Vref output by two external resistors. The dead-band duty cycle (DB) and  $V_{DB}$  can be calculated as follows.

Note:  $V_{DB}$  is the voltage at the DB pin.

Vref is typically 2.5 V. Select  $R_1$  and  $R_2$  so that  $1.0 \text{ V} \le V_{DB} \le 1.6 \text{ V}$ .

Figure 3.1 Dead-Band Duty Cycle Setting

Rev.2.0, Sep.18.2003, page 10 of 37

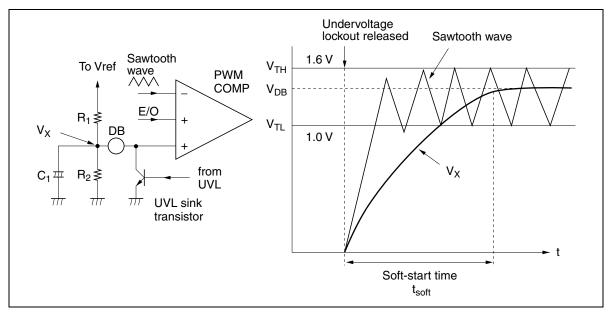

#### 3.2 Soft-Start Setting

Soft-start avoids overshoot at power-up by widening the PWM output pulses gradually, so that the converted DC output rises slowly. Soft-start is programmed by connecting a capacitor between the DB pin and ground. The soft-start time is determined by the time constant of this capacitor and the resistors that set the voltage at the DB pin.

$$\begin{split} t_{\text{soft}} &= -C_1 \times R \times \text{ln} \ (1 - \frac{V_X}{V_{\text{DB}}}) \\ R &= \frac{R_1 \times R_2}{R_1 + R_2} \\ V_{\text{DB}} &= \text{Vref} \times \frac{R_2}{R_1 + R_2} \end{split}$$

Note:  $V_x$  is the voltage at the DB pin after time t ( $V_x < V_{DB}$ ).

Figure 3.2 Soft-Start Setting

#### 3.3 Quick Shutdown

The quick shutdown function resets the voltages at all pins when the IC is turned off, to assure that PWM pulse output stops quickly. Since the UVL pull-down resistor in the IC remains on even when the IC is turned off, the sawtooth wave output, error amplifier output, and DB pin are all reset to low voltage.

This feature helps in particular to discharge capacitor  $C_1$  in figure 3.2, which has a comparatively large capacitance. In intermittent mode (explained on a separate page), this feature enables the IC to soft-start in each on-off cycle.

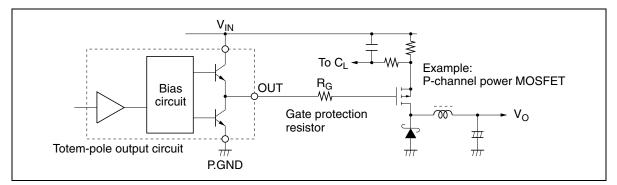

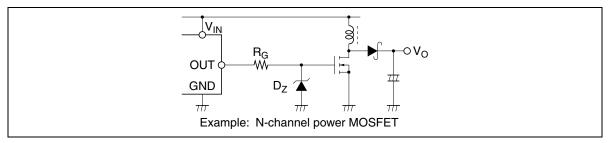

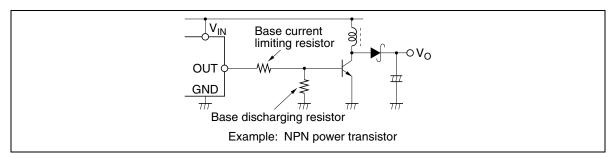

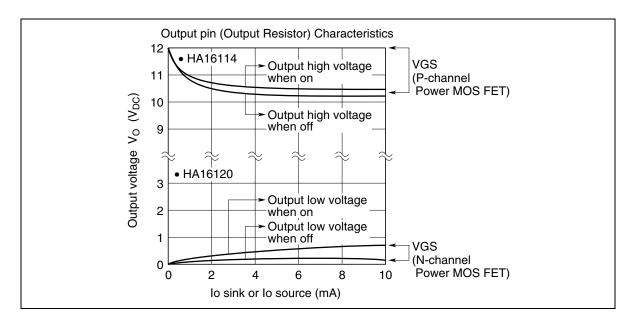

#### 4. PWM Output Circuit and Power MOSFET Driving Method

These ICs have built-in totem-pole push-pull drive circuits that can drive a power MOS FET as shown in figure 4.1. The power MOS FET can be driven directly through a gate protection resistor.

If  $V_{IN}$  exceeds the gate breakdown voltage of the power MOS FET additional protective measures should be taken, e.g. by adding Zener diodes as shown in figure 4.2.

To drive a bipolar power transistor, the base should be protected by voltage and current dividing resistors as shown in figure 4.3.

Figure 4.1 Connection of Output Stage to Power MOS FET

Figure 4.2 Gate Protection by Zener Diodes

Figure 4.3 Driving a Bipolar Power Transistor

Rev.2.0, Sep.18.2003, page 12 of 37

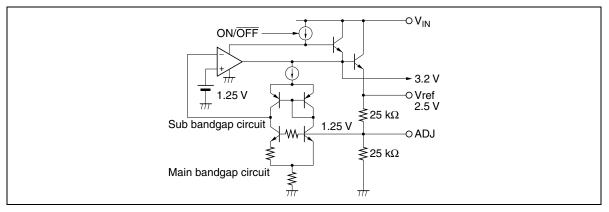

#### 5. Voltage Reference (Vref = 2.5 V)

#### 5.1 Voltage Reference

A bandgap reference built into the IC (see figure 5.1) outputs 2.5 V  $\pm$  50 mV. The sawtooth oscillator, PWM comparator, latch, and other internal circuits are powered by this 2.5 V and an internally-generated voltage of approximately 3.2 V.

The voltage reference section shut downs when the IC is turned off at the ON/OFF pin as described later, saving current when the IC is not used and when it operates in intermittent mode during overcurrent.

Figure 5.1 Vref Reference Circuit

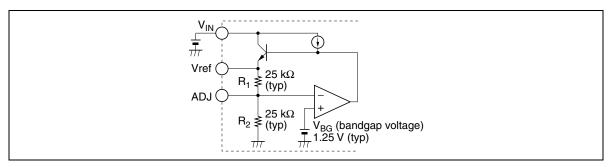

#### 5.2 Trimming the Reference Voltage (Vref and ADJ pins)

Figure 5.2 shows a simplified circuit equivalent to figure 5.1. The ADJ pin in this circuit is provided for trimming the reference voltage (Vref). The output at the ADJ pin is a voltage  $V_{ADJ}$  of 1.25 V (Typ) generated by the bandgap circuit. Vref is determined by  $V_{ADJ}$  and the ratio of internal resistors  $R_1$  and  $R_2$  as follows:

$$Vref = V_{ADJ} \times \frac{R_1 + R_2}{R_2}$$

The design values of  $R_1$  and  $R_2$  are 25 k $\Omega$  with a tolerance of ±25%.

If trimming is not performed, the ADJ pin open can be left open.

Figure 5.2 Simplified Diagram of Voltage Reference Circuit

Rev.2.0, Sep.18.2003, page 13 of 37

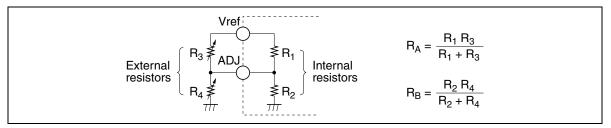

The relation between Vref and the ADJ pin enables Vref to be trimmed by inserting one external resistor  $(R_3)$  between the Vref and ADJ pins and another  $(R_4)$  between the ADJ pin and ground, to change the resistance ratio. Vref is then determined by the combined resistance ratio of the internal  $R_1$  and  $R_2$  and external  $R_3$  and  $R_4$ .

$$Vref = V_{ADJ} \times \frac{R_A + R_B}{R_B}$$

Where,  $R_A$ : parallel resistance of  $R_1$  and  $R_3$

$R_{\rm B}$ : parallel resistance of  $R_2$  and  $R_4$

Although Vref can be trimmed by  $R_3$  or  $R_4$  alone, to decrease the temperature dependence of Vref it is better to use two resistors having identical temperature coefficients. Vref can be trimmed in the range of 2.5 V ± 0.2 V. Outside this range, the bandgap circuit will not operate and the IC may shut down.

Figure 5.3 Trimming of Reference Voltage

#### 5.3 Vref Undervoltage Lockout and Overvoltage Protection

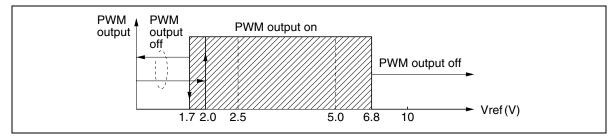

The undervoltage lockout (UVL) function turns off PWM pulse output when the input voltage ( $V_{IN}$ ) is low. In these ICs, this is done by monitoring the Vref voltage, which normally stays constant at approximately 2.5 V. The UVL circuit operates with hysteresis: it shuts PWM output off when Vref falls below 1.7 V, and turns PWM output back on when Vref rises above 2.0 V. Undervoltage lockout also provides protection in the event that Vref is shorted to ground.

The overvoltage protection circuit shuts PWM output off when Vref goes above 6.8 V. This provides protection in case the Vref pin is shorted to  $V_{IN}$  or another high-voltage source.

Figure 5.4 Vref Undervoltage Lockout and Overvoltage Protection

| UVL Voltage    | Vref (V typ) | V <sub>IN</sub> (V typ) | Description                                                                          |

|----------------|--------------|-------------------------|--------------------------------------------------------------------------------------|

| V <sub>H</sub> | 2.0 V        | 3.6 V                   | $V_{IN}$ increasing: UVL releases; PWM output starts                                 |

| VL             | 1.7 V        | 3.3 V                   | $V_{{\scriptscriptstyle \rm IN}}$ decreasing: undervoltage lockout; PWM output stops |

Rev.2.0, Sep.18.2003, page 14 of 37

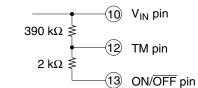

#### 6. Usage of ON/OFF Pin

This pin is used for the following purposes:

- To shut down the IC while its input power remains on (power management)

- To externally alter the UVL release voltage

- With the timer (TM) pin, to operate in intermittent mode during overcurrent (see next section)

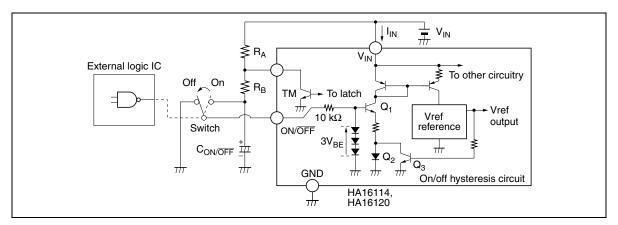

#### 6.1 Shutdown by ON/OFF Pin Control

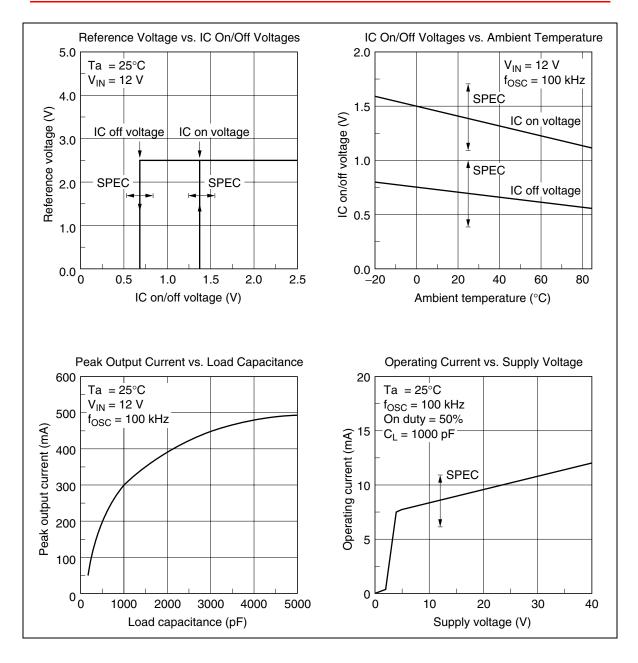

The IC can be shut down safely by bringing the voltage at the ON/OFF pin below about 0.7 V (the internal VBE value). This feature can be used in power supply systems to save power. When shut down, the HA16114 draws a maximum current ( $I_{OFF}$ ) of 10  $\mu$ A, while the HA16120 draws a maximum 150  $\mu$ A. The ON/OFF pin sinks 290  $\mu$ A (Typ) at 5 V, so it can be driven by TTL and other logic ICs. If intermittent mode will also be employed, use a logic IC with an open-collector or open-drain output.

Figure 6.1 Shutdown by ON/OFF Pin Control

#### 6.2 Adjustment of UVL Voltages (when not using intermittent mode)

These ICs permit external adjustment of the undervoltage lockout voltages. The adjustment is made by changing the undervoltage lockout thresholds  $V_{TH}$  and  $V_{TL}$  relative to  $V_{IN}$ , using the relationships shown in the accompanying diagrams.

When the IC is powered up, transistor  $Q_3$  is off, so  $V_{ON}$  is  $2V_{BE}$ , or about 1.4 V. Connection of resistors  $R_C$  and  $R_D$  in the diagram makes undervoltage lockout release at:

$$V_{IN} = 1.4 \text{ V} \times \frac{\text{R}_{\text{C}} + \text{R}_{\text{D}}}{\text{R}_{\text{D}}}$$

This  $V_{IN}$  is the supply voltage at which undervoltage lockout is released. At the release point Vref is still below 2.5 V. To obtain Vref = 2.5 V,  $V_{IN}$  must be at least about 4.3 V.

Since  $V_{on/OFF}$  operates in relation to the base-emitter voltage of internal transistors,  $V_{on}$  has a temperature coefficient of approximately –4 mV/°C. Keep this in mind when designing the power supply unit.

When undervoltage lockout and intermittent mode are both used, the intermittent-mode time constant is shortened, so the constants of external components may have to be altered.

RENESAS

Rev.2.0, Sep.18.2003, page 15 of 37

Figure 6.2 Adjustment of UVL Voltages

#### 7. Timing of Intermittent Mode during Overcurrent

#### 7.1 Principle of Operation

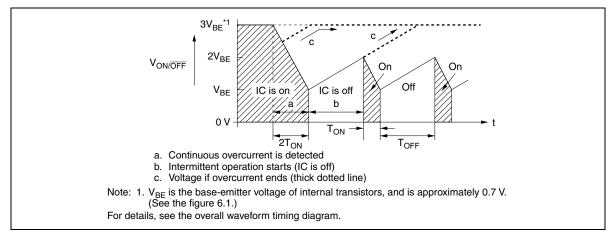

These ICs provide pulse-by-pulse overcurrent protection by sensing the current during each pulse and shutting off the pulse if overcurrent is detected. In addition, the TM and ON/OFF pins can be used to operate the IC in intermittent mode if the overcurrent state continues. A power supply with sharp settling characteristics can be designed in this way.

Intermittent mode operates by making use of the hysteresis of the ON/OFF pin threshold voltages  $V_{ON}$  and  $V_{OFF} (V_{ON} - V_{OFF} = V_{BF})$ . The timing can be programmed as explained below.

When not using intermittent mode, leave the TM pin open, and pull the ON/OFF pin up to  $V_{on}$  or higher. The  $V_{BE}$  is base emitter voltage of internal transistors.

Figure 7.1 Connection Diagram (example)

Rev.2.0, Sep.18.2003, page 16 of 37

#### 7.2 Intermittent Mode Timing Diagram (V<sub>ON/OFF</sub> only)

Figure 7.2 Intermittent Mode Timing Diagram (V<sub>on/OFF</sub> only)

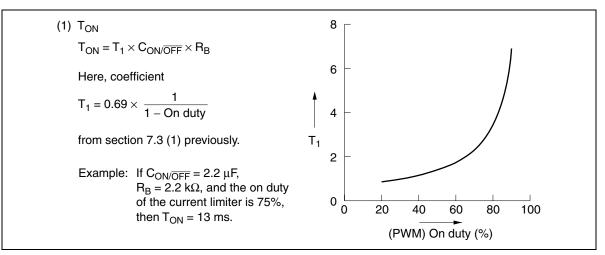

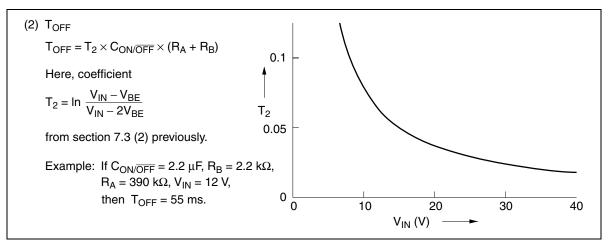

#### 7.3 Calculation of Intermittent Mode Timing

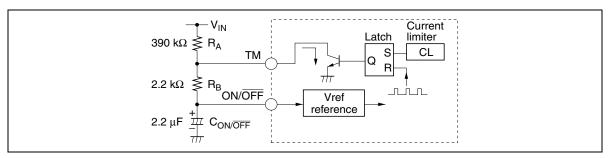

Intermittent mode timing is calculated as follows.

(1)  $T_{ON}$  (time until the IC shuts off when continuous overcurrent occurs)

$$T_{ON} = C_{ON/\overline{OFF}} \times R_{B} \times \ln\left(\frac{2V_{BE}}{V_{BE}}\right) \times \left(\frac{1}{1 - \text{On duty}^{*}}\right)$$

$$= C_{ON/\overline{OFF}} \times R_{B} \times \ln 2 \times \left(\frac{1}{1 - \text{On duty}^{*}}\right)$$

$$\approx 0.69 \times C_{ON/\overline{OFF}} \times R_{B} \times \left(\frac{1}{1 - \text{On duty}^{*}}\right)$$

(2)  $T_{OFF}$  (time from when the IC shuts off until it next turns on)

$$T_{OFF} = C_{ON/\overline{OFF}} \times (R_{A} + R_{B}) \times \ln\left(\frac{V_{IN} - V_{BE}}{V_{IN} - 2V_{BE}}\right)$$

Where  $V_{BE} \approx 0.7 V$

The greater the overload, the sooner the pulse-by-pulse current limiter operates, the smaller  $t_{_{ON}}$  becomes, and from the first equation (1) above, the smaller  $T_{_{ON}}$  becomes. From the second equation (2),  $T_{_{OFF}}$  depends on  $V_{_{IN}}$ . Note that with the connections shown in the diagram, when  $V_{_{IN}}$  is switched on the IC does not turn on until  $T_{_{OFF}}$  has elapsed.

Figure 7.3

Rev.2.0, Sep.18.2003, page 17 of 37

#### 7.4 Examples of Intermittent Mode Timing (calculated values)

Figure 7.4 Examples of Intermittent Mode Timing (1)

Figure 7.5 Examples of Intermittent Mode Timing (2)

Rev.2.0, Sep.18.2003, page 18 of 37

Figure 7.6

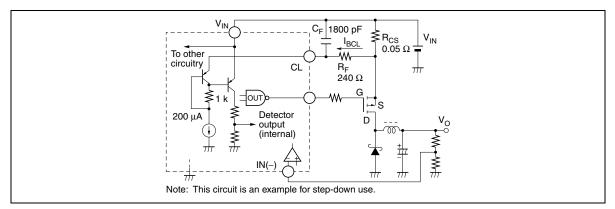

#### 8. Setting the Overcurrent Detection Threshold

The voltage drop  $V_{TH}$  at which overcurrent is detected in these ICs is typically 0.2 V. The bias current is typically 200  $\mu$ A. The power MOS FET peak current value before the current limiter goes into operation is given as follows.

$$I_{D} = \frac{V_{TH} - (R_{F} + R_{CS}) \times I_{BCL}}{R_{CS}}$$

Where,  $V_{TH} = V_{IN} - V_{CL} = 0.2 \text{ V}$ ,  $V_{CL}$  is a voltage refered on GND.

Note that  $R_F$  and  $C_F$  form a low-pass filter with a cutoff frequency determined by their RC time constant. This filter prevents incorrect operation due to current spikes when the power MOS FET is switched on or off.

Figure 8.1 Example for Step-Down Use

With the values shown in the diagram, the peak current is:

$$I_{D} = \frac{0.2 \text{ V} - (240 \ \Omega + 0.05 \ \Omega) \times 200 \ \mu\text{A}}{0.05 \ \Omega} = 3.04 \text{ A}$$

The filter cutoff frequency is calculated as follows:

$$f_{\rm C} = \frac{1}{2\pi \ {\rm C_F \ R_F}} = \frac{1}{6.28 \times 1800 \ {\rm pF} \times 240 \ \Omega} = 370 \ {\rm kHz}$$

Rev.2.0, Sep.18.2003, page 19 of 37

## **Absolute Maximum Ratings**

$(Ta = 25^{\circ}C)$

|                               |                     | Rating                    |                              |      |  |

|-------------------------------|---------------------|---------------------------|------------------------------|------|--|

| Item                          | Symbol              | HA16114P/FP,<br>HA16120FP | HA16114PJ/FPJ,<br>HA16120FPJ | Unit |  |

| Supply voltage                | V <sub>IN</sub>     | 40                        | 40                           | V    |  |

| Output current (DC)           | I <sub>o</sub>      | ±0.1                      | ±0.1                         | А    |  |

| Output current (peak)         | l <sub>o</sub> peak | ±1.0                      | ±1.0                         | А    |  |

| Current limiter input voltage | V <sub>CL</sub>     | V <sub>IN</sub>           | V <sub>IN</sub>              | V    |  |

| Error amplifier input voltage | $V_{IEA}$           | V <sub>IN</sub>           | V <sub>IN</sub>              | V    |  |

| E/O input voltage             | V <sub>IE/O</sub>   | Vref                      | Vref                         | V    |  |

| RT source current             | I <sub>RT</sub>     | 500                       | 500                          | μA   |  |

| TM sink current               | I <sub>TM</sub>     | 3                         | 3                            | mA   |  |

| SYNC voltage                  | V <sub>SYNC</sub>   | Vref                      | Vref                         | V    |  |

| SYNC current                  | I <sub>SYNC</sub>   | ±250                      | ±250                         | μA   |  |

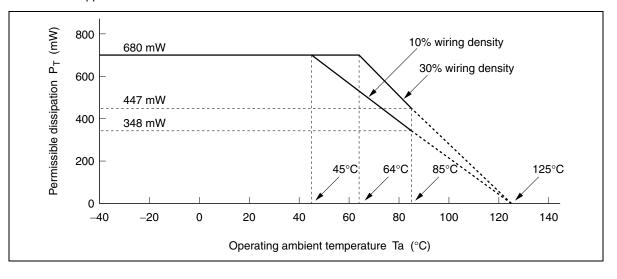

| Power dissipation             | P <sub>T</sub>      | 680* <sup>1, *2</sup>     | 680* <sup>1, *2</sup>        | mW   |  |

| Operating temperature         | Topr                | -40 to +85                | -40 to +85                   | °C   |  |

| Junction temperature          | TjMax               | 125                       | 125                          | °C   |  |

| Storage temperature           | Tstg                | -55 to +125               | -55 to +125                  | °C   |  |

Notes: 1. This value is for an SOP package (FP) and is based on actual measurements on a 40 × 40 × 1.6 mm glass epoxy circuit board. With a 10% wiring density, this value is permissible up to Ta = 45°C and should be derated by 8.3 mW/°C at higher temperatures. With a 30% wiring density, this value is permissible up to Ta = 64°C and should be derated by 11.1 mW/°C at higher temperatures.

For the DIP package. (P) This value applies up to Ta = 45°C; at temperatures above this, 8.3 mW/°C derating should be applied.

Rev.2.0, Sep.18.2003, page 20 of 37

# **Electrical Characteristics**

$(Ta = 25^{\circ}C, V_{IN} = 12 V, f_{OSC} = 100 \text{ kHz})$

| Item                            |                                         | Symbol               | Min   | Тур  | Max   | Unit       | Test Conditions                                                                                                             | Notes |

|---------------------------------|-----------------------------------------|----------------------|-------|------|-------|------------|-----------------------------------------------------------------------------------------------------------------------------|-------|

| Voltage<br>reference<br>section | Output voltage                          | Vref                 | 2.45  | 2.50 | 2.55  | V          | I <sub>o</sub> = 1 mA                                                                                                       |       |

|                                 | Line regulation                         | Line                 | _     | 2    | 60    | mV         | $4.5~V \leq V_{_{\rm IN}} \leq 40V$                                                                                         | 1     |

| 3601011                         | Load regulation                         | Load                 | _     | 30   | 60    | mV         | $0 \le I_o \le 10 \text{ mA}$                                                                                               |       |

|                                 | Short-circuit output current            | I <sub>os</sub>      | 10    | 24   | _     | mA         | Vref = 0 V                                                                                                                  |       |

|                                 | Vref overvoltage protection threshold   | Vrovp                | 6.2   | 6.8  | 7.4   | V          |                                                                                                                             |       |

|                                 | Temperature stability of output voltage | ∆Vref/∆Ta            | —     | 100  | —     | ppm/°C     |                                                                                                                             |       |

|                                 | Vref adjustment voltage                 | $V_{\text{adj}}$     | 1.225 | 1.25 | 1.275 | V          |                                                                                                                             |       |

| Sawtooth                        | Maximum frequency                       | fmax                 | 600   | _    | _     | kHz        |                                                                                                                             |       |

| oscillator<br>section           | Minimum frequency                       | fmin                 | _     | _    | 1     | Hz         |                                                                                                                             |       |

| Section                         | Frequency stability with input voltage  | $\Delta f/f_{_{01}}$ | —     | ±1   | ±3    | %          | $4.5 V \le V_{_{IN}} \le 40 V$<br>(f <sub>01</sub> = (fmax + fmin)/2)                                                       |       |

|                                 | Frequency stability with temperature    | $\Delta f/f_{_{02}}$ | _     | ±5   |       | %          | $\label{eq:constraint} \begin{array}{l} -20^{\circ}C \leq Ta \leq 85^{\circ}C \\ (f_{_{02}} = (fmax + fmin)/2) \end{array}$ |       |

|                                 | Oscillator frequency                    | f <sub>osc</sub>     | 90    | 100  | 110   | kHz        | R <sub>τ</sub> = 10 kΩ<br>C <sub>τ</sub> = 1300 pF                                                                          |       |

| Dead-band<br>adjustment         | Low level threshold voltage             | V <sub>TL</sub>      | 0.9   | 1.0  | 1.1   | V          | Output duty cycle:<br>0% on                                                                                                 |       |

| section                         | High level threshold voltage            | $V_{\text{TH}}$      | 1.5   | 1.6  | 1.7   | V          | Output duty cycle:<br>100% on                                                                                               |       |

|                                 | Threshold difference                    | $\Delta V_{_{TH}}$   | 0.5   | 0.6  | 0.7   | V          | $\Delta V_{_{TH}} = V_{_{TH}} - V_{_{TL}}$                                                                                  |       |

|                                 | Output source current                   | Isource              | 170   | 250  | 330   | μ <b>A</b> | DB pin: 0 V                                                                                                                 |       |

| PWM<br>comparator<br>section    | Low level threshold voltage             | V <sub>TL</sub>      | 0.9   | 1.0  | 1.1   | V          | Output duty cycle:<br>0% on                                                                                                 |       |

|                                 | High level threshold voltage            | $V_{\text{TH}}$      | 1.5   | 1.6  | 1.7   | V          | Output duty cycle: 100% on                                                                                                  |       |

|                                 | Threshold difference                    | $\Delta V_{TH}$      | 0.5   | 0.6  | 0.7   | V          | $\Delta V_{TH} = V_{TH} - V_{TL}$                                                                                           |       |

Rev.2.0, Sep.18.2003, page 21 of 37

# **Electrical Characteristics** (cont.)

$(Ta = 25^{\circ}C, V_{IN} = 12 V, f_{OSC} = 100 \text{ kHz})$

| Item                          |                                   | Symbol              | Min                   | Тур                  | Max                   | Unit | Test Conditions                               | Notes |

|-------------------------------|-----------------------------------|---------------------|-----------------------|----------------------|-----------------------|------|-----------------------------------------------|-------|

| Error<br>amplifier<br>section | Input offset voltage              | V <sub>io</sub>     | _                     | 2                    | 10                    | mV   |                                               |       |

|                               | Input bias current                | I <sub>B</sub>      | _                     | 0.5                  | 2.0                   | μA   |                                               |       |

| 3001011                       | Output sink current               | I <sub>Osink</sub>  | 28                    | 40                   | 52                    | μA   | V <sub>o</sub> = 2.5 V                        |       |

|                               | Output source<br>current          | Osource             | 28                    | 40                   | 52                    | μA   | V <sub>o</sub> = 1.0 V                        |       |

|                               | Common-mode input voltage range   | $V_{\rm CM}$        | 1.1                   | _                    | 3.7                   | V    |                                               |       |

|                               | Voltage gain                      | A <sub>v</sub>      | 40                    | 50                   | _                     | dB   | f = 10 kHz                                    |       |

|                               | Unity gain<br>bandwidth           | BW                  | _                     | 4                    | _                     | MHz  |                                               |       |

|                               | High level output voltage         | $V_{_{OH}}$         | 3.5                   | 4.0                  | _                     | V    | I <sub>o</sub> = 10 μA                        |       |

|                               | Low level output voltage          | $V_{_{OL}}$         | _                     | 0.2                  | 0.5                   | V    | I <sub>o</sub> = 10 μA                        |       |

| Overcurrent                   | Threshold voltage                 | V <sub>TH</sub>     | V <sub>IN</sub> -0.22 | V <sub>IN</sub> -0.2 | V <sub>IN</sub> -0.18 | V    |                                               |       |

| detection<br>section          | CL(-) bias current                | I <sub>BCL(-)</sub> | 140                   | 200                  | 260                   | μA   | $CL(-) = V_{IN}$                              |       |

| 3001011                       | Turn-off time                     | t <sub>off</sub>    | _                     | 200                  | 300                   | ns   |                                               | 1     |

|                               |                                   |                     | _                     | 500                  | 600                   | ns   |                                               | 2     |

| UVL section                   | Vref high level threshold voltage | $V_{\text{TH}}$     | 1.7                   | 2.0                  | 2.3                   | V    |                                               |       |

|                               | Vref low level threshold voltage  | V <sub>TL</sub>     | 1.4                   | 1.7                  | 2.0                   | V    |                                               |       |

|                               | Threshold<br>difference           | $\Delta_{\rm VTH}$  | 0.1                   | 0.3                  | 0.5                   | V    | $\Delta V_{\rm TH} = V_{\rm TH} - V_{\rm TL}$ |       |

|                               | VIN high level threshold voltage  | $V_{\rm INH}$       | 3.3                   | 3.6                  | 3.9                   | V    |                                               |       |

|                               | VIN low level threshold voltage   | $V_{\rm INL}$       | 3.0                   | 3.3                  | 3.6                   | V    |                                               |       |

Notes: 1. HA16114 only.

2. HA16120 only.

# **Electrical Characteristics** (cont.)

# $(Ta = 25^{\circ}C, V_{IN} = 12 V, f_{OSC} = 100 \text{ kHz})$

| Item            |                                     | Symbol                     | Min                  | Тур                  | Max                    | Unit | Test Conditions                                | Notes |

|-----------------|-------------------------------------|----------------------------|----------------------|----------------------|------------------------|------|------------------------------------------------|-------|

| Output          | Output low voltage                  | V <sub>ol</sub>            | _                    | 0.9                  | 1.5                    | V    | $I_{_{Osink}} = 10 \text{ mA}$                 |       |

| stage           | Output high voltage                 | $V_{_{OH1}}$               | V <sub>IN</sub> –2.2 | V <sub>IN</sub> -1.6 | _                      | V    | $I_{Osource} = 10 \text{ mA}$                  |       |

|                 | High voltage when off               | $V_{_{OH2}}$               | V <sub>IN</sub> -2.2 | V <sub>IN</sub> -1.6 | _                      | V    | I <sub>osource</sub> = 1 mA<br>ON/OFF pin: 0 V | 1     |

|                 | Low voltage when off                | $V_{_{OL2}}$               | _                    | 0.9                  | 1.5                    | V    | I <sub>osink</sub> = 1 mA<br>ON/OFF pin: 0 V   | 2     |

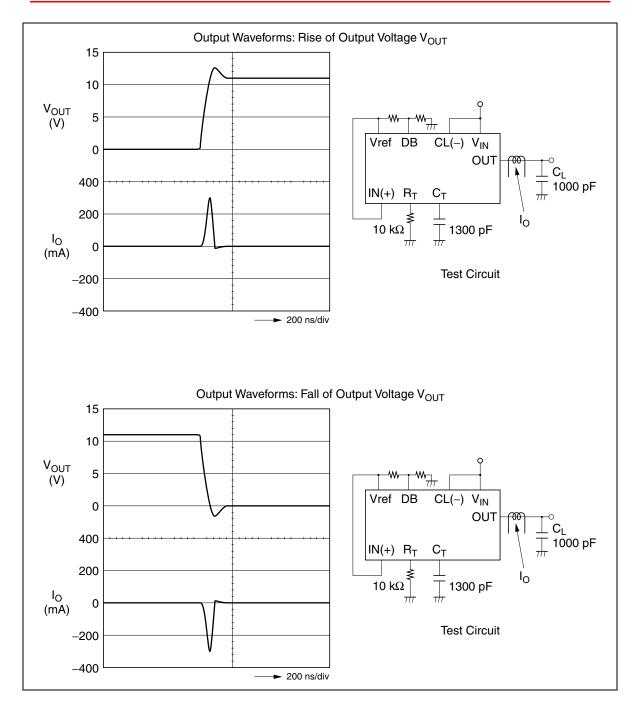

|                 | Rise time                           | t,                         | _                    | 50                   | 200                    | ns   | C <sub>L</sub> = 1000 pF                       |       |

|                 | Fall time                           | t,                         | _                    | 50                   | 200                    | ns   | C <sub>L</sub> = 1000 pF                       |       |

| External        | SYNC source current                 | I <sub>SYNC</sub>          | 120                  | 180                  | 240                    | μA   | SYNC pin: 0 V                                  |       |

| sync<br>section | Sync input<br>frequency range       | $\mathbf{f}_{\text{SYNC}}$ | f <sub>osc</sub>     |                      | $\rm f_{osc} \times 2$ | kHz  |                                                |       |

|                 | External sync<br>initiation voltage | $V_{\text{SYNC}}$          | Vref-1.0             |                      | Vref-0.5               | V    |                                                |       |

|                 | Minimum pulse width of sync input   | PWmin                      | 300                  | —                    | _                      | ns   |                                                |       |

|                 | Input sync pulse<br>duty cycle      | PW                         | 5                    |                      | 50                     | %    |                                                | 3     |

| On/off          | ON/OFF sink current 1               | I ON/ OFF 1                | 60                   | 90                   | 120                    | μA   | ON/OFF pin: 3 V                                |       |

| section         | ON/OFF sink current 2               | I ON/ OFF 2                | 220                  | 290                  | 380                    | μA   | ON/OFF pin: 5 V                                |       |

|                 | IC on threshold                     | V <sub>on</sub>            | 1.1                  | 1.4                  | 1.7                    | V    |                                                |       |

|                 | IC off threshold                    | V                          | 0.4                  | 0.7                  | 1.0                    | V    |                                                |       |

|                 | ON/OFF threshold difference         | $\Delta V_{\text{ON/OFF}}$ | 0.5                  | 0.7                  | 0.9                    | V    |                                                |       |

| Total           | Operating current                   | I <sub>IN</sub>            | 6.0                  | 8.5                  | 11.0                   | mA   | C <sub>L</sub> = 1000 pF                       |       |

| device          | Quiescent current                   | I <sub>OFF</sub>           | 0                    | _                    | 10                     | μA   | ON/OFF pin: 0 V                                | 1     |

|                 |                                     |                            | _                    | 120                  | 150                    | μA   | ON/OFF pin: 0 V                                | 2     |

Notes: 1. HA16114 only.

2. HA16120 only.

Rev.2.0, Sep.18.2003, page 23 of 37

# **Characteristic Curves**

Rev.2.0, Sep.18.2003, page 28 of 37

Rev.2.0, Sep.18.2003, page 29 of 37

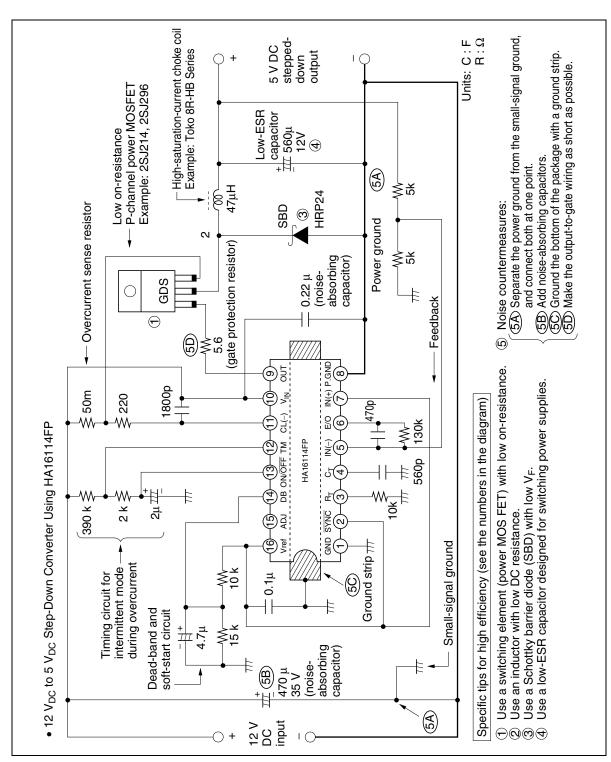

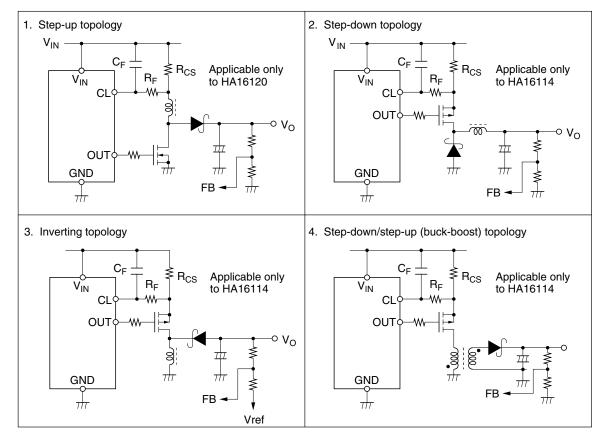

# **Application Examples (1)**

Rev.2.0, Sep.18.2003, page 32 of 37

# **Application Examples (2)**

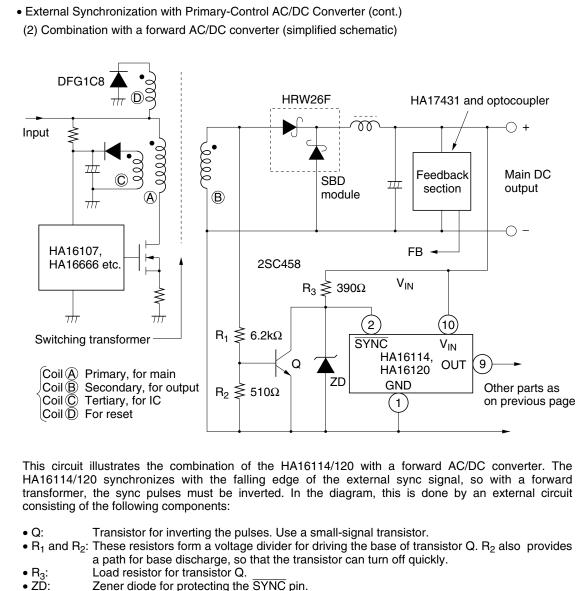

• Resistors  $R_1$  and  $R_2$  form a voltage divider to ensure that the input voltage swing at the SYNC pin does not exceed Vref (2.5 V). To maintain operating speed,  $R_1 + R_2$  should not exceed 10 k $\Omega$ .

Rev.2.0, Sep.18.2003, page 33 of 37

# **Application Examples (3)**

Zener diode for protecting the  $\overline{\text{SYNC}}$  pin.

Rev.2.0, Sep.18.2003, page 34 of 37

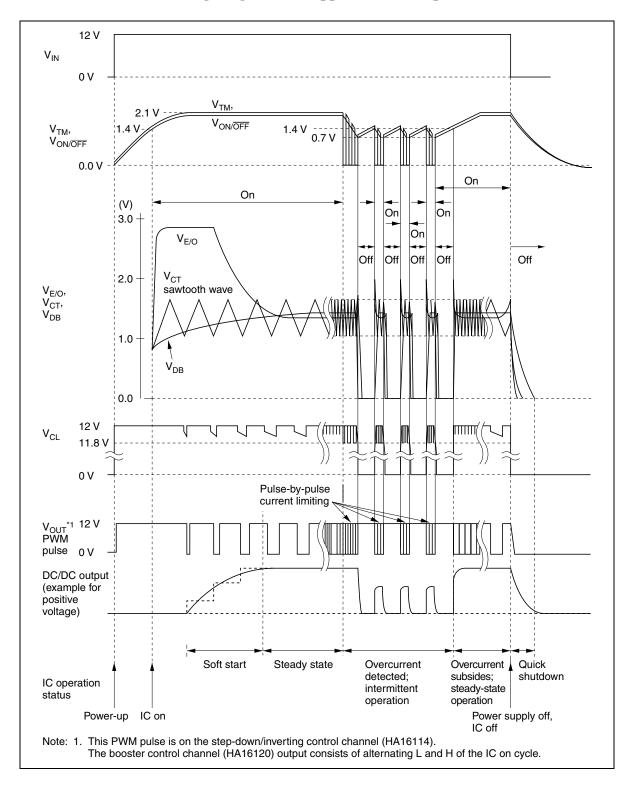

**Overall Waveform Timing Diagram (for Application Example (1))**

Rev.2.0, Sep.18.2003, page 35 of 37  $\,$

# **Application Examples (4) (Some Pointers on Use)**

1. Inductor, Power MOS FET, and Diode Connections

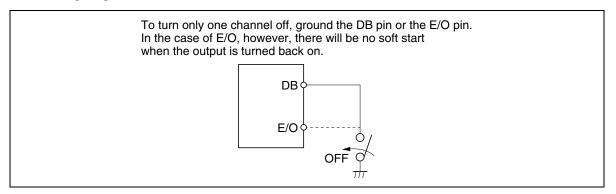

2. Turning Output On and Off while the IC is On

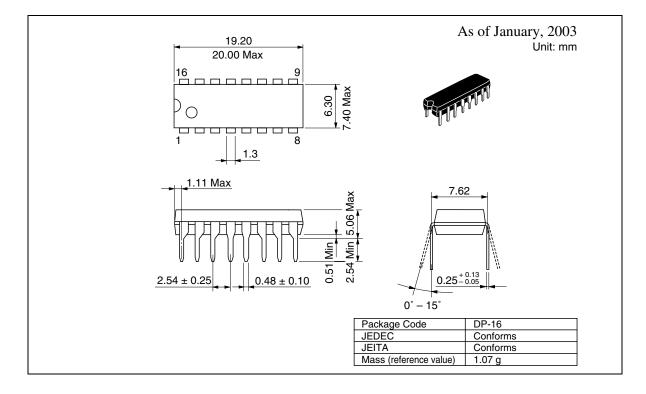

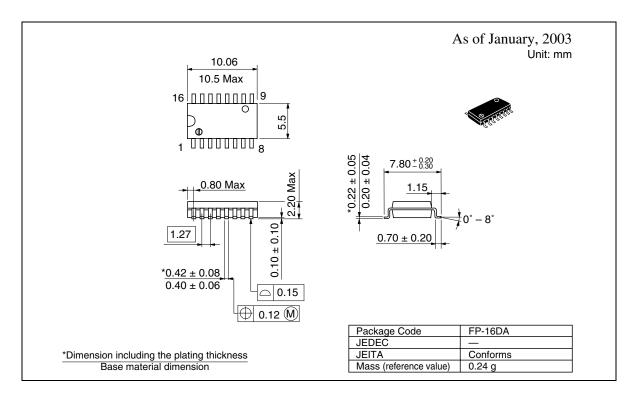

# **Package Dimensions**

Rev.2.0, Sep.18.2003, page 37 of 37

# RenesasTechnology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

#### Keep safety first in your circuit designs!

- The party inst in your circuit designs:

1. Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

- Notes regarding these materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party.

Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors. Please also pay attention to information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product.

4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to eva use.

- use. 6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials. 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination. Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited. 8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.

http://www.renesas.com

# **RENESAS SALES OFFICES**

Renesas Technology America, Inc. 450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500 Fax: <1> (408) 382-7501

#### Renesas Technology Europe Limited.

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, United Kingdom Tel: <44> (1628) 585 100, Fax: <44> (1628) 585 900

Renesas Technology Europe GmbH Dornacher Str. 3, D-85622 Feldkirchen, Germany Tel: <49> (89) 380 70 0, Fax: <49> (89) 929 30 11

Renesas Technology Hong Kong Ltd. 7/F., North Tower, World Finance Centre, Harbour City, Canton Road, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2375-6836

Renesas Technology Taiwan Co., Ltd. FL 10, #99, Fu-Hsing N. Rd., Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999

Renesas Technology (Shanghai) Co., Ltd. 26/F., Ruijin Building, No.205 Maoming Road (S), Shanghai 200020, China Tel: <86> (21) 6472-1001, Fax: <86> (21) 6415-2952

Renesas Technology Singapore Pte. Ltd. 1, Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001