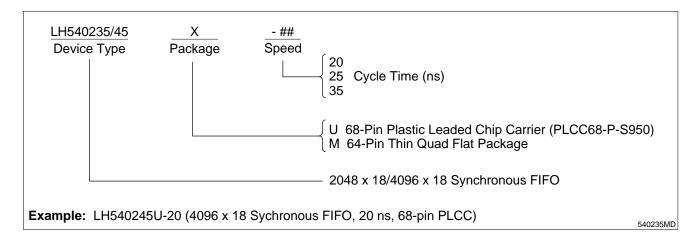

# LH540235/45

# 2048 $\times$ 18 / 4096 $\times$ 18 Synchronous FIFOs

### **FEATURES**

- Fast Cycle Times: 20/25/35 ns

- Pin-Compatible Drop-In Replacements for IDT72235B/45B FIFOs

- Choice of IDT-Compatible or *Enhanced* Operating Mode; Selected by an Input Control Signal

- Device Comes Up into One of Two Known Default <u>States at Reset Depending on the State of the</u>

<u>EMODE</u> Control Input: Programming is Allowed, but is not Required

- Internal Memory Array Architecture Based on CMOS Dual-Port SRAM Technology, 2048 × 18 or 4096 × 18

- 'Synchronous' Enable-Plus-Clock Control at Both Input Port and Output Port

- Independently-Synchronized Operation of Input Port and Output Port

- Control Inputs Sampled on Rising Clock Edge

- Most Control Signals Assertive-LOW for Noise Immunity

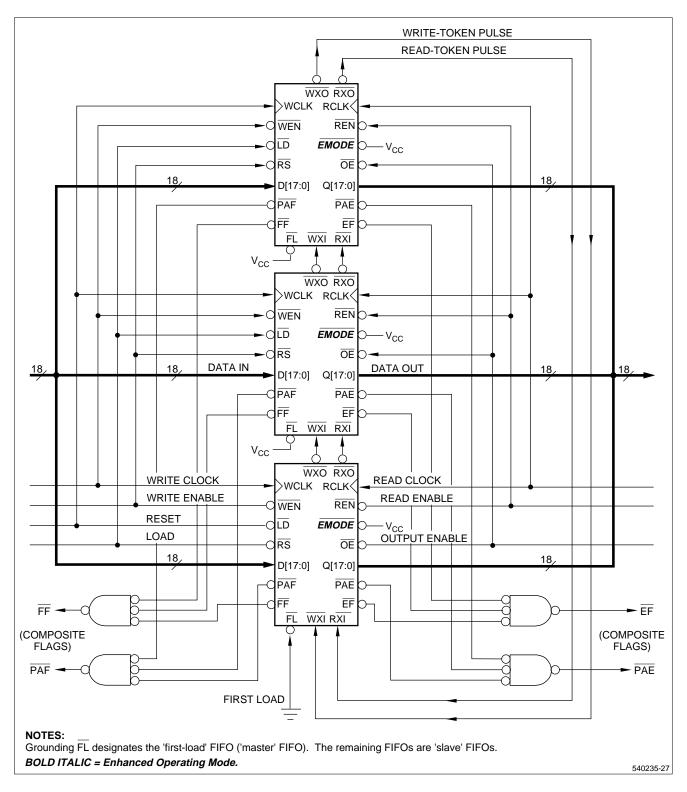

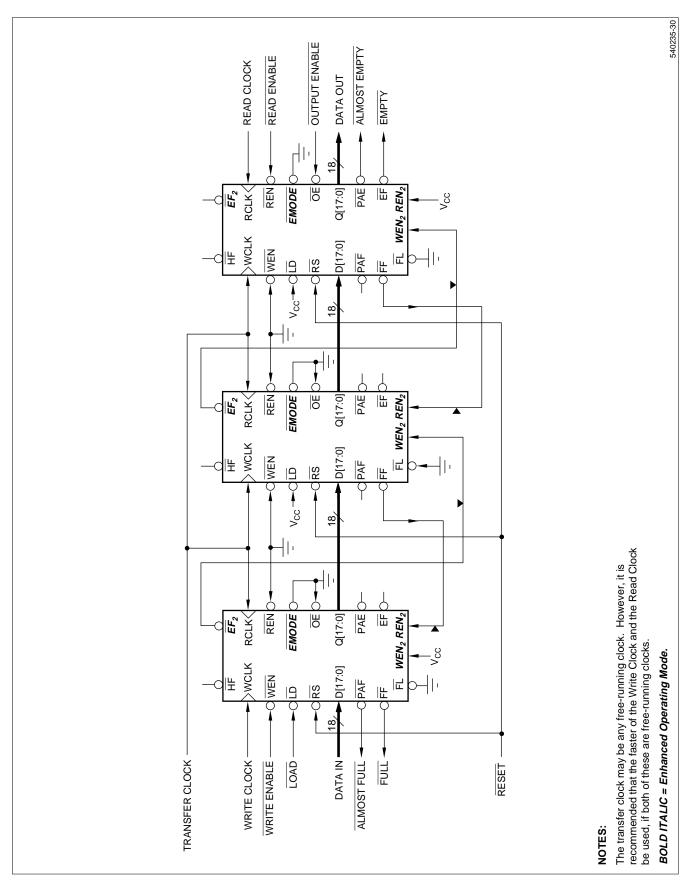

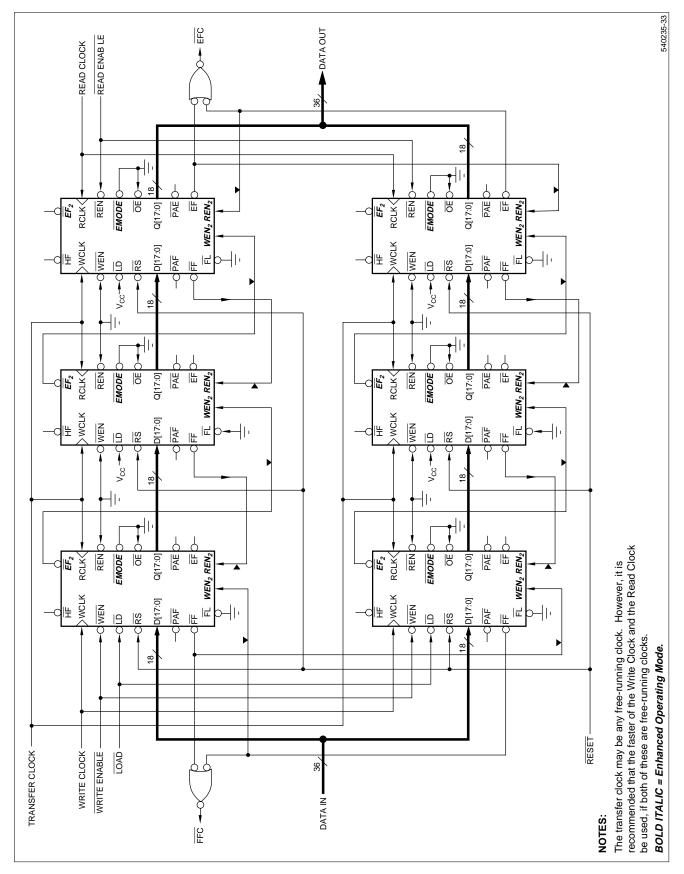

- May be Cascaded for Increased Depth, or Paralleled for Increased Width

- 16 mA-IOL High-Drive Three-State Outputs

- Five Status Flags: Full, Almost-Full, Half-Full, Almost-Empty, and Empty; 'Almost' Flags are Programmable

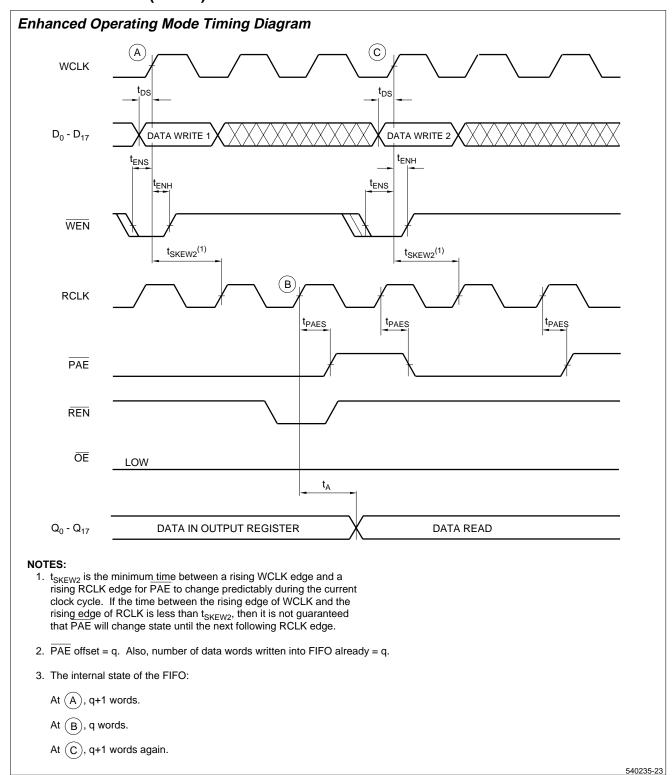

- In Enhanced Operating Mode, Almost-Full, Half-Full, and Almost-Empty Flags can be Made Completely Synchronous

- In Enhanced Operating Mode, Duplicate Enables for Interlocked Paralleled FIFO Operation, for 36-Bit Data Width, when Selected and Appropriately Connected

- In Enhanced Operating Mode, Disabling Three-State Outputs May be Made to Suppress Reading

- Data Retransmit Function

- TTL/CMOS-Compatible I/O

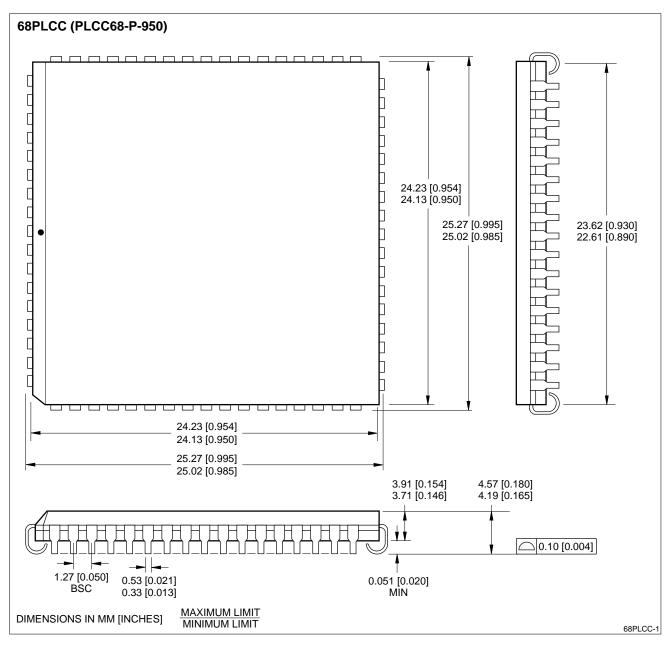

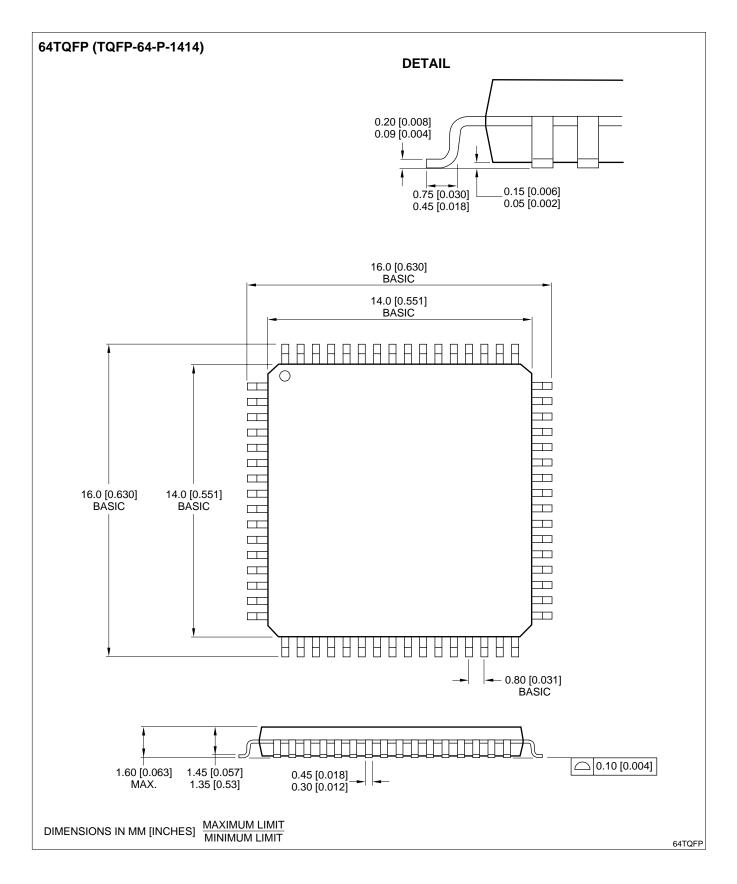

- Space-Saving 68-Pin PLCC Package; Even-Smaller 64-Pin TQFP Package

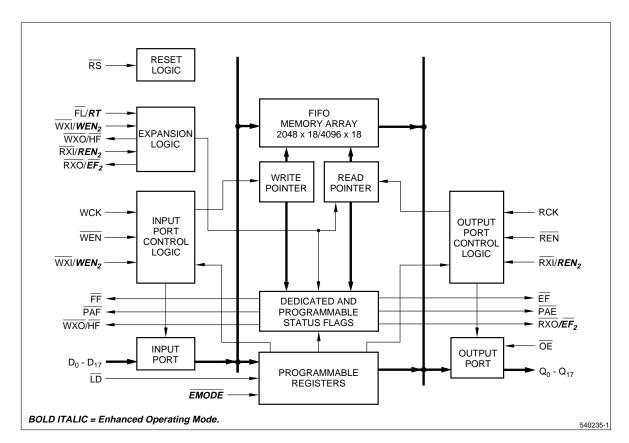

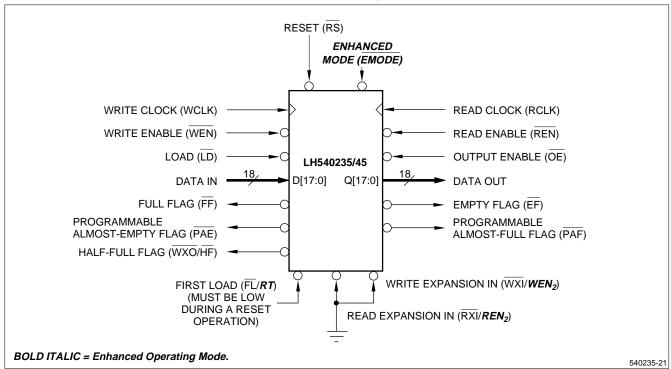

Figure 1. LH540235/45 Block Diagram

### **FUNCTIONAL DESCRIPTION**

NOTE: Throughout this data sheet, a *BOLD ITALIC* type font is used for all references to *Enhanced Operating Mode* features which do not function in IDT-Compatible Operating Mode; and also for all references to the *retransmit* facility (which is not an IDT72235B/45B FIFO feature), even though it may be used – subject to some restrictions – in either of these two operating modes. Thus, readers interested only in using the LH540235/45 FIFOs in IDT-Compatible Operating Mode may skip over *BOLD ITALIC* sections, if they wish.

The LH540235/45 parts are FIFO (First-In, First-Out) memory devices, based on fully-static CMOS dual-port SRAM technology, capable of containing up to 2048 or 4096 18-bit words respectively. They can replace two or more byte-wide FIFOs in many applications, for microprocessor-to-microprocessor or microprocessor-to-bus communication. Their architecture supports synchronous operation, tied to two independent free-running clocks at the input and output ports respectively. However, these 'clocks' also may be aperiodic, asynchronous 'demand' signals. Almost all control-input signals and status-output signals are synchronized to these clocks, to simplify system design.

The input and output ports operate altogether independently of each other, unless the FIFO becomes either totally full or else totally empty. Data flow is initiated at a port by the rising edge of its corresponding clock, and is gated by the appropriate edge-sampled enable signals.

The following FIFO status flags monitor the extent to which the internal memory has been filled: Full, Almost-Full, Half-Full, Almost-Empty, and Empty. The Almost-Full and Almost-Empty flag offsets are programmable over the entire FIFO depth; but, during a reset operation, each of these is initialized to a default offset value of 12710 FIFO-memory words, from the respective FIFO boundary. If this default offset value is satisfactory, no further programming is required.

After a reset operation during which the **EMODE** control input was not asserted (was HIGH), these FIFOs operate in the IDT-Compatible Operating Mode. In this mode, each part is pin-compatible and functionally-compatible with the IDT72235B/45B part of similar depth and speed grade; and the **Control Register** is not even accessible or visible to the external-system logic which is controlling the FIFO, although it still performs the same control functions.

However, assertion of the EMODE control input during a reset operation leaves Control Register bits 00-05 set, and causes the FIFO to operate in the Enhanced Operating Mode. In essence, asserting EMODE chooses a different default state for the Con-

trol Register. The system optionally then may program the Control Register in any desired manner to activate or deactivate any or all of the Enhanced-Operating-Mode features which it can control, including selectable-clock-edge flag synchronization, and read inhibition when the data outputs are disabled.

Whenever EMODE is being asserted, interlockedoperation paralleling also is available, by appropriate interconnection of the FIFO's expansion inputs.

The retransmit facility is available during standalone operation, in either IDT-Compatible Operating Mode or Enhanced Operating Mode (see Tables 1 and 2). It is inoperative if the FL/RT input signal is grounded. It is not an IDT72235B/45B feature. The Retransmit control signal causes the internal FIFO read-address pointer to be set back to zero, without affecting the internal FIFO write-address pointer. Thus, the Retransmit control signal also provides a mechanism whereby a block of data delimited by the zero physical address and the current write-address-pointer address may be read out repeatedly, an arbitrary number of times.

The only restrictions are that neither the read-address pointer nor the write-address pointer may 'wrap around' during this entire process, and that the retransmit facility is not available during depth-cascaded operation, either in IDT-Compatible Operating Mode or in Enhanced Operating Mode (see Tables 1 and 2). Also, the flags behave differently for a short time after a retransmit operation. Otherwise, the retransmit facility is available during standalone operation, in either IDT-Compatible Operating Mode or Enhanced Operating Mode.

Note that, when FL/RT is being used as RT, RT is an assertive-HIGH signal, rather than assertive-LOW as it is in most other FIFOs having a retransmit facility.

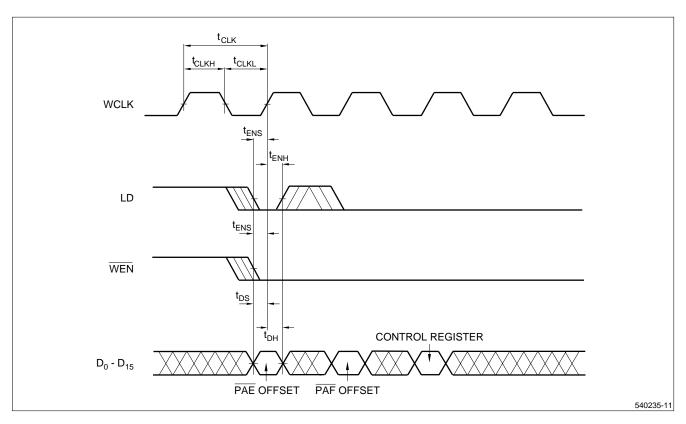

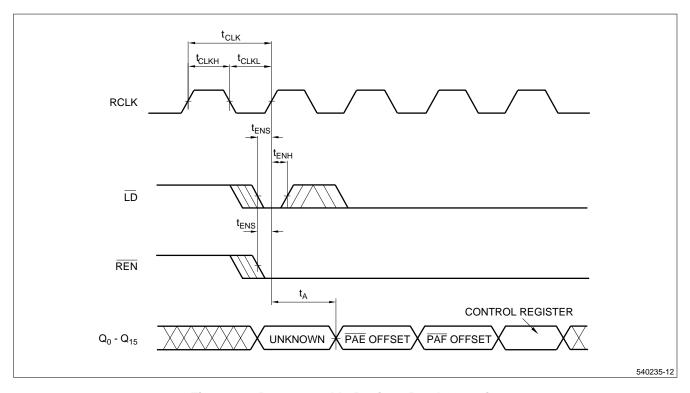

Programming the programmable-flag offsets, the timing synchronization of the various status flags, the optional read-suppression functionality of OE, and the behavior of the pointers which access the offsetvalue registers and the Control Register may be individually controlled by asserting the signal  $\overline{LD}$ , without any reset operation. When LD is being asserted, and writing is being enabled by asserting WEN, some portion of the input bus word D<sub>0</sub> - D<sub>17</sub> is used at the next rising edge of WCLK to program one or more of the programmable registers on successive write clocks. Likewise, the values programmed into these programmable registers may be read out for verification by asserting  $\overline{LD}$  and  $\overline{REN}$ , with the outputs Q0 - Q17 enabled. Reading out these programmable registers should not be initiated while they are being written into. Table 3 defines the possible modes of operation for loading and reading out the contents of programmable registers.

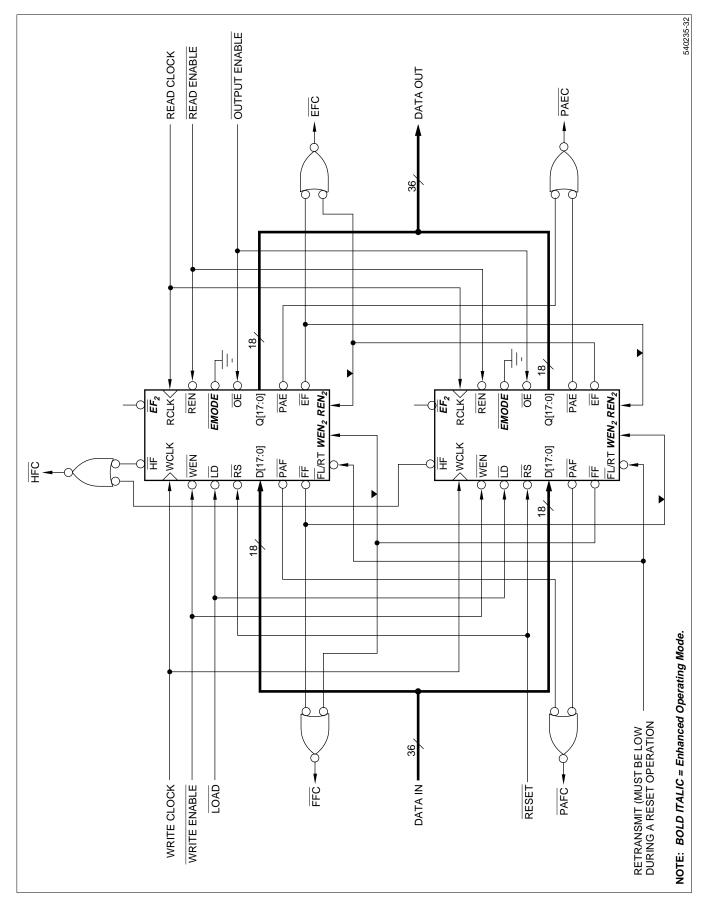

In the Enhanced Operating Mode, coordinated operation of two 18-bit FIFOs as one 36-bit FIFO may be ensured by 'interlocked' crosscoupling of the statusflag outputs from each FIFO to the expansion inputs of the other one; that is, FF to WXI/WEN2, and EF to RXI/REN2, in both directions between two paralleled FIFOs. This 'interlocked' operation takes effect

automatically, if two paralleled <u>FIFOs</u> are crossconnected in this manner, with the <u>FMODE</u> control input being asserted (LOW) (see Tables 1 and 2, also Figures 28 and 31). IDT-compatible depth cascading no longer is available when operating in this 'interlocked-paralleled' mode; however, pipelined depth cascading remains available.

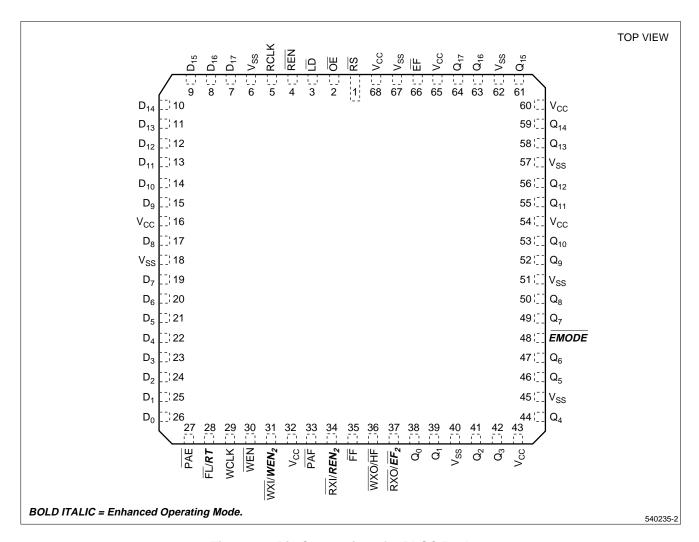

Figure 2. Pin Connections for PLCC Package

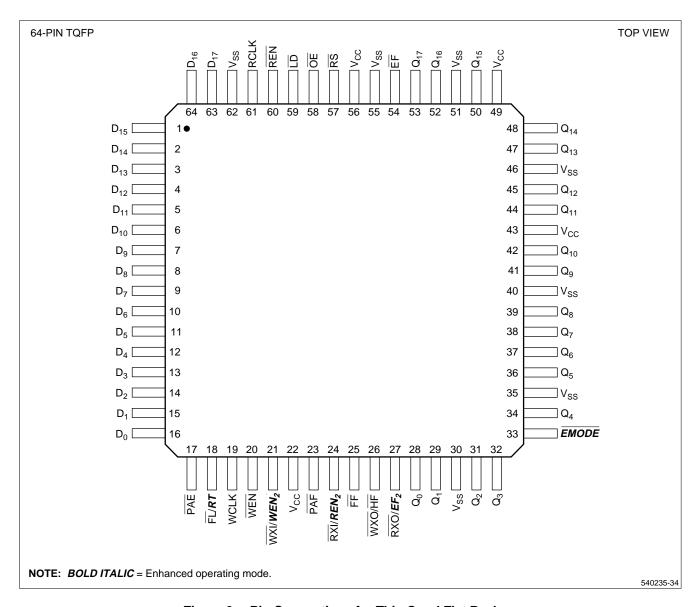

Figure 3. Pin Connections for Thin Quad Flat Package

### **SUMMARY OF SIGNALS/PINS**

| PIN                              | NAME                               |

|----------------------------------|------------------------------------|

| D <sub>0</sub> - D <sub>17</sub> | Data Inputs                        |

| RS                               | Reset                              |

| EMODE                            | Enhanced Operating Mode            |

| WCLK                             | Write Clock                        |

| WEN                              | Write Enable                       |

| RCLK                             | Read Clock                         |

| REN                              | Read Enable                        |

| ŌE                               | Output Enable                      |

| LD                               | Load                               |

| FL/RT                            | First Load/ <i>Retransmit</i>      |

| RXI/REN <sub>2</sub>             | Read Expansion Input/Read Enable 2 |

| PIN                         | NAME                                  |

|-----------------------------|---------------------------------------|

| WXI <b>/WEN</b> 2           | Write Expansion Input/Write Enable 2  |

| FF                          | Full Flag                             |

| PAF                         | Programmable Almost-Full Flag         |

| WXO/HF                      | Write Expansion Output/Half-Full Flag |

| PAE                         | Programmable Almost-Empty Flag        |

| EF                          | Empty Flag                            |

| RXO/ <b>EF</b> <sub>2</sub> | Read Expansion Output/Empty Flag 2    |

| $Q_0 - Q_{17}$              | Data Outputs                          |

| Vcc                         | Power                                 |

| Vss                         | Ground                                |

# **PIN LIST**

| SIGNAL NAME                 | PLCC PIN NO. | TQFP PIN NO. |

|-----------------------------|--------------|--------------|

| RS                          | 1            | 57           |

| ŌĒ                          | 2            | 58           |

| LD                          | 3            | 59           |

| REN                         | 4            | 60           |

| RCLK                        | 5            | 61           |

| D <sub>17</sub>             | 7            | 63           |

| D <sub>16</sub>             | 8            | 64           |

| D <sub>15</sub>             | 9            | 1            |

| D <sub>14</sub>             | 10           | 2            |

| D <sub>13</sub>             | 11           | 3            |

| D <sub>12</sub>             | 12           | 4            |

| D <sub>11</sub>             | 13           | 5            |

| D <sub>10</sub>             | 14           | 6            |

| D <sub>9</sub>              | 15           | 7            |

| D <sub>8</sub>              | 17           | 8            |

| D <sub>7</sub>              | 19           | 9            |

| D <sub>6</sub>              | 20           | 10           |

| D <sub>5</sub>              | 21           | 11           |

| D <sub>4</sub>              | 22           | 12           |

| D <sub>3</sub>              | 23           | 13           |

| D <sub>2</sub>              | 24           | 14           |

| D <sub>1</sub>              | 25           | 15           |

| D <sub>0</sub>              | 26           | 16           |

| PAE                         | 27           | 17           |

| FT/RT                       | 28           | 18           |

| WCLK                        | 29           | 19           |

| WEN                         | 30           | 20           |

| ₩XI/ <b>WEN</b> 2           | 31           | 21           |

| PAF                         | 33           | 23           |

| RXI/ <b>REN</b> ₂           | 34           | 24           |

| FF                          | 35           | 25           |

| WXO/HF                      | 36           | 26           |

| RXO/ <b>EF</b> <sub>2</sub> | 37           | 27           |

| $Q_0$                       | 38           | 28           |

| SIGNAL NAME     | PLCC PIN NO. | TQFP PIN NO. |

|-----------------|--------------|--------------|

| Q <sub>1</sub>  | 39           | 29           |

| $Q_2$           | 41           | 31           |

| $Q_3$           | 42           | 32           |

| Q <sub>4</sub>  | 44           | 34           |

| Q <sub>5</sub>  | 46           | 36           |

| Q <sub>6</sub>  | 47           | 37           |

| EMODE           | 48           | 33           |

| Q <sub>7</sub>  | 49           | 38           |

| Q <sub>8</sub>  | 50           | 39           |

| Q <sub>9</sub>  | 52           | 41           |

| Q <sub>10</sub> | 53           | 42           |

| Q <sub>11</sub> | 55           | 44           |

| Q <sub>12</sub> | 56           | 45           |

| Q <sub>13</sub> | 58           | 47           |

| Q <sub>14</sub> | 59           | 48           |

| Q <sub>15</sub> | 61           | 50           |

| Q <sub>16</sub> | 63           | 52           |

| Q <sub>17</sub> | 64           | 53           |

| ĒF              | 66           | 54           |

| V <sub>SS</sub> | 6            | 62           |

| V <sub>CC</sub> | 16           | NC           |

| V <sub>SS</sub> | 18           | NC           |

| Vcc             | 32           | 22           |

| V <sub>SS</sub> | 40           | 30           |

| V <sub>CC</sub> | 43           | NC           |

| V <sub>SS</sub> | 45           | 35           |

| V <sub>SS</sub> | 51           | 40           |

| V <sub>CC</sub> | 54           | 43           |

| V <sub>SS</sub> | 57           | 46           |

| V <sub>CC</sub> | 60           | 49           |

| V <sub>SS</sub> | 62           | 51           |

| V <sub>CC</sub> | 65           | NC           |

| V <sub>SS</sub> | 67           | 55           |

| V <sub>CC</sub> | 68           | 56           |

# **PIN DESCRIPTIONS**

| PIN                              | NAME                          | PIN<br>TYPE <sup>1</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------|-------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D <sub>0</sub> – D <sub>17</sub> | Data Inputs                   | I                        | Data inputs from an 18-bit bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RS                               | Reset                         | I                        | When RS is taken LOW, the FIFO's internal read and write pointers are set to address the first physical location of the RAM array; FF, PAF, and HF go HIGH; and PAE and EF go LOW. The programmable-flag-offset registers and the <u>Control Register</u> are set to their default values. (But see the description of <u>EMODE</u> , below.) A reset operation is required before an initial read or write operation after power-up.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| EMODE                            | Enhanced<br>Operating<br>Mode | ı                        | When EMODE is tied LOW, the default setting for Control Register bits 00-05 after a reset operation changes to HIGH rather than LOW, thus enabling all Control-Register-controllable Enhanced Operating Mode features, and allowing access to the Control Register for reprogramming or readback (see Tables 1, 2, and 5). If this behavior is desired, EMODE may be grounded; however, Control Register bits 00-06 still may be individually programmed to selectively enable or disable certain of the Enhanced Mode features, even though those features associated with interlocked-paralleled operation always are enabled whenever EMODE is being asserted (see Table 2). Alternatively, EMODE may be tied to V <sub>CC</sub> , so that the FIFO is functionally IDT-compatible, and the Control Register is not accessible or visible, and all of its bits remain LOW. Controlling EMODE dynamically during system operation is not recommended. |

| WCLK                             | Write Clock                   | _                        | <u>Data</u> is written into the FIFO on a LOW-to-HIGH transition of WCL <u>K</u> , whenever WEN (Write Enable) is being asserted (LOW), and LD is HIGH. If LD is LOW, a programmable register rather than the internal FIFO memory is written into. <i>In the Enhanced Operating Mode, whenever Control Register bit 06 is HIGH, WEN<sub>2</sub> is ANDed with WEN to produce an effective internal write-enable signal. <sup>2</sup></i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| WEN                              | Write Enable                  | ı                        | When WEN is LOW and LD is HIGH, an 18-bit data word is written into the FIFO on every LOW-to-HIGH transition of WCLK. When WEN is HIGH, the FIFO internal memory continues to hold the previous data (see Table 3). Data will not be written into the FIFO if FF is LOW. In the Enhanced Operating Mode, whenever Control Register bit 06 is HIGH, WEN2 is ANDed with WEN to produce an effective internal write-enable signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RCLK                             | Read Clock                    | I                        | <u>Data</u> is read from the FIFO on a LOW-to-HIGH transition of RCLK whenever REN (Read Enable) is being asserted (LOW), and LD is HIGH. If LD is LOW, a programmable register rather than the internal FIFO memory is read from. <i>In the Enhanced Ope<u>rating</u> Mode, whenever Control Register bit 06 is HIGH, REN<sub>2</sub> is ANDed with REN (and whenever Control Register bit 05 is HIGH, also with OE) to produce an effective internal read-enable signal.<sup>2</sup></i>                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| REN                              | Read Enable                   | I                        | When $\overline{\text{REN}}$ is LOW and $\overline{\text{LD}}$ is HIGH, an 18-bit data word is read from the FIFO on every LOW-to-HIGH transition of RCLK. When $\overline{\text{REN}}$ is HIGH, and/or also when $\overline{\text{EF}}$ is LOW, the FIFO's output register continues to hold the previous data word, whether or not $Q_0 - Q_{17}$ (the data outputs) are enabled (see Table 3). In the Enhanced Operating Mode, whenever Control Register bit 06 is HIGH, REN <sub>2</sub> is ANDed with REN (and whenever Control Register bit 05 is HIGH, also with $\overline{\text{OE}}$ ) to produce an effective internal read-enable signal. $^2$                                                                                                                                                                                                                                                                                              |

| ŌĒ                               | Output Enable                 | I                        | When $\overline{\text{OE}}$ is LOW, the FIFO's data outputs drive the bus to which they are connected. If $\overline{\text{OE}}$ is HIGH, the FIFO's outputs are in high-Z (high-impedance) state. In the Enhanced Operating Mode, $\overline{\text{OE}}$ not only continues to control the outputs in this same manner, but also can function as an additional ANDing input to the combined effective read-enable signal, along with REN and REN <sub>2</sub> , whenever Control Register bit 05 is HIGH (see Table 5). <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                   |

# PIN DESCRIPTIONS (cont'd)

| PIN                              | NAME                                 | PIN<br>TYPE <sup>1</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------|--------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LD                               | Load                                 | I                        | When $\overline{LD}$ is LOW, the data word on $D_0 - D_{17}$ (the data inputs) is written into a programmable-flag-offset register, <i>or into the Control Register (when in the Enhanced Operating Mode)</i> , on the LOW-to-HIGH transition of WCLK, whenever WEN is LOW (see Table 3). Also, when $\overline{LD}$ is LOW, a word is read to $Q_0 - Q_{17}$ (the data outputs) from the offset registers <i>and/or the Control Register (when in the Enhanced Operating Mode)</i> on the LOW-to-HIGH transition of RCLK, whenever REN is LOW (see again Table 3, and particularly the Notes following this table). When $\overline{LD}$ is HIGH, normal FIFO write and read operations are enabled. |

| WEN <sub>2</sub>                 | Write Enable 2                       | 1                        | Tie LOW in Standard Mode, cascading is not supported. In the Enhanded Operating Mode, whenever Control Register Bit06 is HIGH, WXI/WEN2 functions as a second write-enable signal, WEN2, which is ANDed with WEN to produce an effective internal write-enable signal.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| REN <sub>2</sub>                 | Read Enable 2                        | 1                        | Tie LOW in Standard Mode. In the Enhanced Operating Mode, whenever Control Register Bit06 is HIGH, RXI/REN <sub>2</sub> functions as a second read-enable signal, REN <sub>2</sub> , which is ANDed with REN to produce an effective internal readenable signal.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

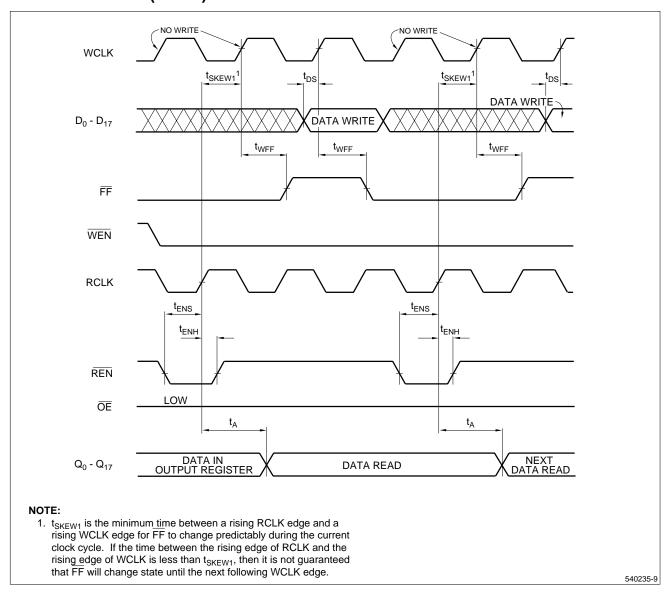

| FF                               | Full Flag                            | 0                        | When FF is LOW, the FIFO is full; further advancement of its internal write-address pointer, and further data writes through its Data Inputs into its internal memory array, are inhibited. When FF is HIGH, the FIFO is not full. FF is synchronized to WCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

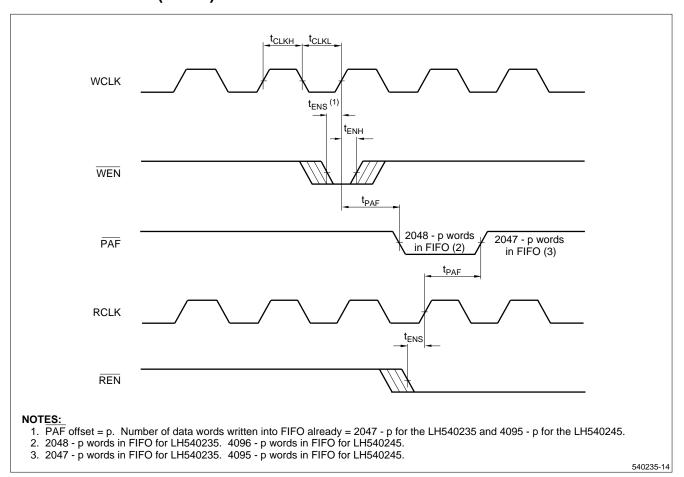

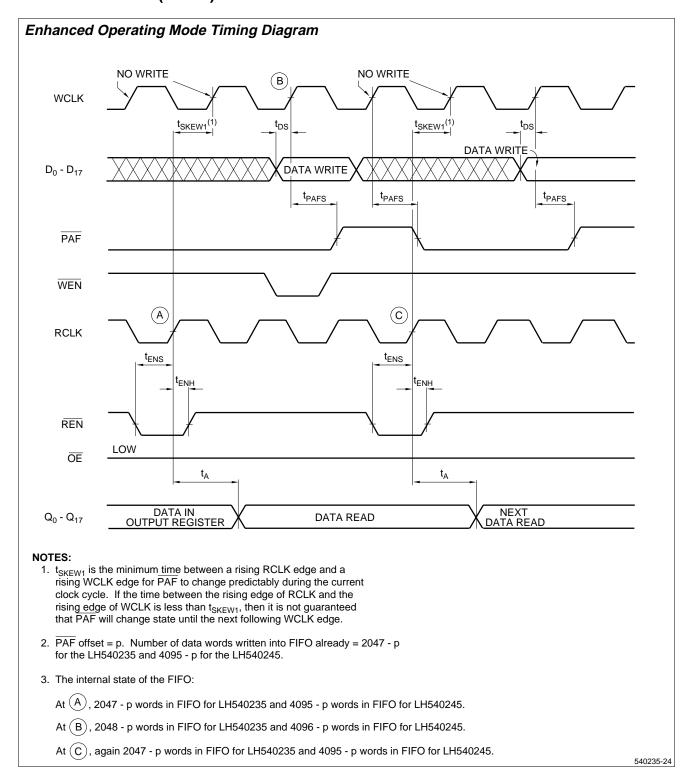

| PAF                              | Programmable<br>Almost-Full Flag     | 0                        | When PAF is LOW, the FIFO is 'almost full,' based on the almost-full-offset value programmed into the FIFO's Almost-Full Offset Register. The default value of this offset at reset is 127 <sub>10</sub> , measured from 'full' (see Table 4). In the IDT-Compatible Operating Mode, PAF is asynchronous. In the Enhanced Operating Mode, PAF is synchronized to WCLK after a reset operation, according to the state of Control Register bit 04 (see Table 5).                                                                                                                                                                                                                                       |

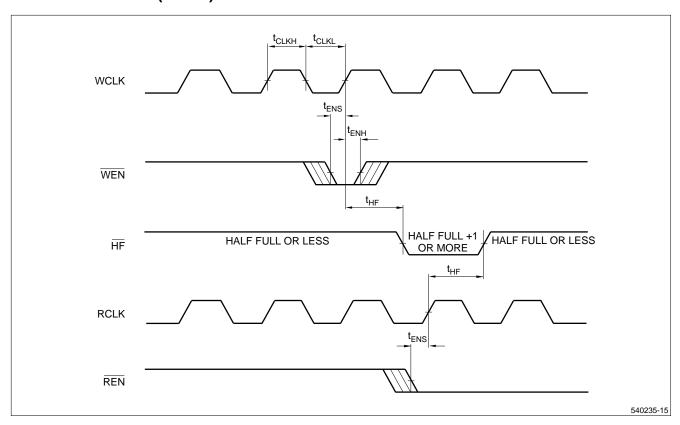

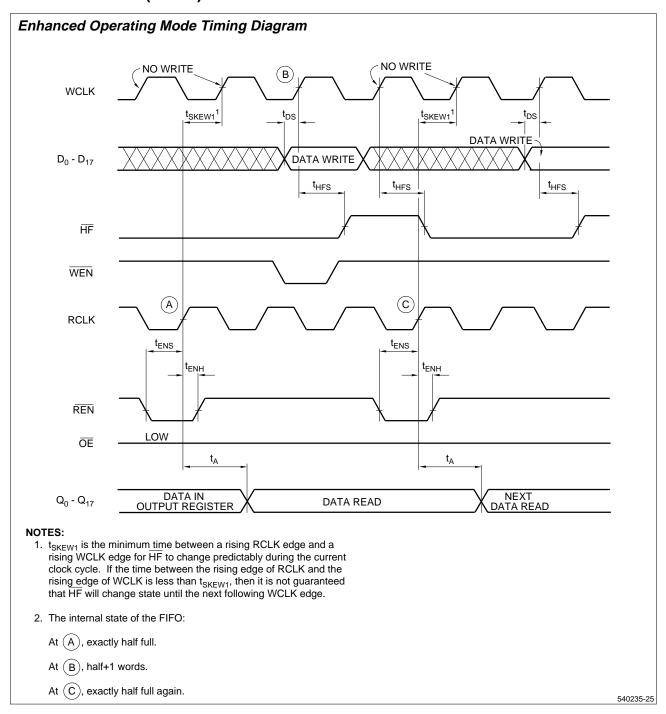

| ΉF                               | Half-Full Flag                       | 0                        | In the standalone or paralleled configuration, whenever HF is LOW the device is more than half full. In IDT-Compatible Operating Mode, HF is asynchronous; in the Enhanced Operating Mode, HF may be synchronized either to WCLK or to RCLK after a reset operation, according to the state of Control Register bits 02 and 03 (see Table 5).                                                                                                                                                                                                                                                                                                                                                         |

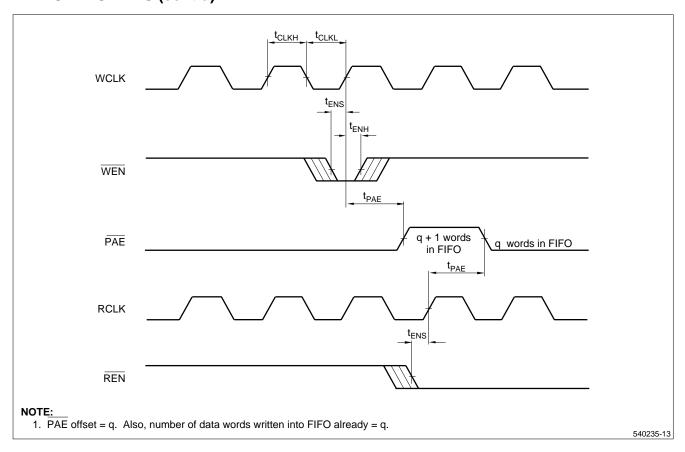

| PAE                              | Programmable<br>Almost-Empty<br>Flag | 0                        | When PAE is LOW, the FIFO is 'almost empty,' based on the almost-empty-offset value programmed into the FIFO's Almost-Empty Offset Register. The default value of this offset at reset is 127 <sub>10</sub> , measured from 'empty' (see Table 4). In IDT-Compatible Operating Mode, PAE is asynchronous. In the Enhanced Operating Mode, PAE is synchronized to RCLK after a reset operation, according to the state of Control Register bit 01. (See Table 5.)                                                                                                                                                                                                                                      |

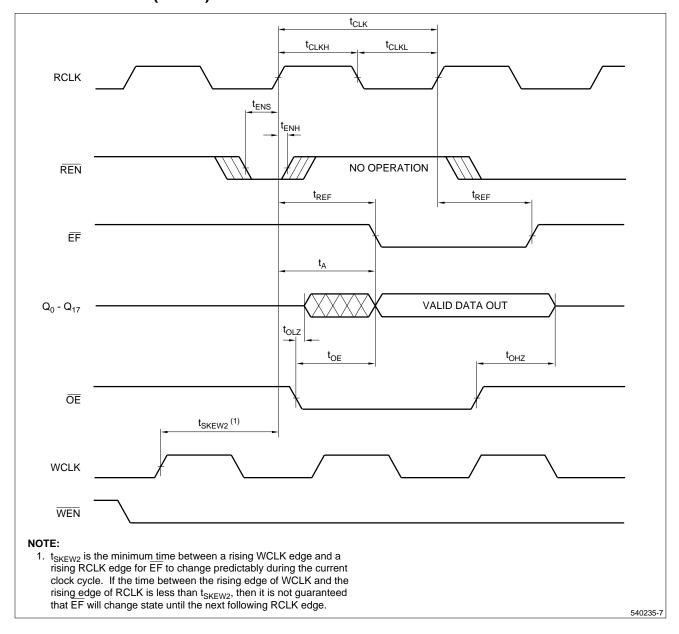

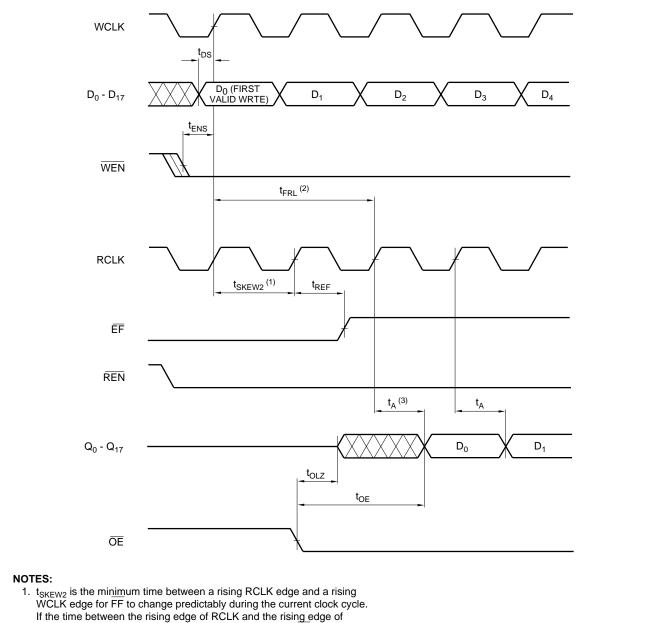

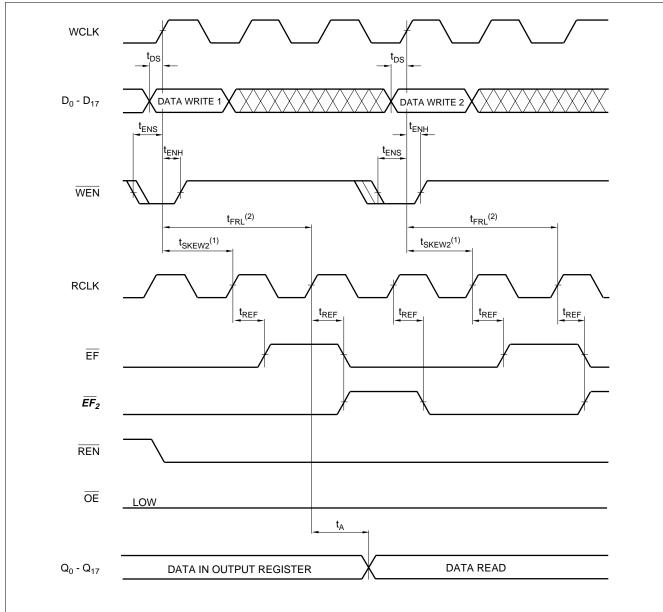

| ĒF                               | Empty Flag                           | 0                        | When $\overline{EF}$ is LOW, the FIFO is empty; further advancement of its internal read-<br>address pointer, and further readout of data words from its internal memory array to<br>its Data Outputs, are inhibited. When $\overline{EF}$ is HIGH, the FIFO is not empty. $\overline{EF}$ is<br>synchronized to RCLK.                                                                                                                                                                                                                                                                                                                                                                                |

| ĒF₂                              | Empty Flag 2                         | 0                        | In the Enhanced Operating Mode, Control Register bit 06 is HIGH, EF <sub>2</sub> behaves as an exact duplicate of EF, but delayed by one full cycle of RCLK with respect to EF.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Q <sub>0</sub> – Q <sub>17</sub> | Data Outputs                         | O/Z                      | Data outputs to drive an 18-bit bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Vcc                              | Power                                | V                        | +3.3 V power-supply pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| V <sub>SS</sub>                  | Ground                               | V                        | 0 V ground pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

### NOTES:

- 1 I = Input, O = Output, Z = High-Impedance, V = Power Voltage Level

- 2 The ostensible differences in signal assertiveness are reconciled before ANDing.

### **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER                                         | RATING                                     |

|---------------------------------------------------|--------------------------------------------|

| Supply Voltage to V <sub>SS</sub> Potential       | -0.5 V to 7 V                              |

| Signal Pin Voltage to V <sub>SS</sub> Potential   | $-0.5 \text{ V to V}_{CC} + 0.5 \text{ V}$ |

| DC Output Current <sup>1</sup>                    | ±75 mA                                     |

| Temperature Range with Power Applied <sup>2</sup> | -55°C to 125°C                             |

| Storage Temperature Range                         | −65°C to 150°C                             |

| Power Dissipation (PLCC Package Limit)            | 2 W                                        |

#### NOTES:

- 1. Only one output may be shorted at a time, for a period not exceeding 30 seconds.

- 2. Measured with clocks idle.

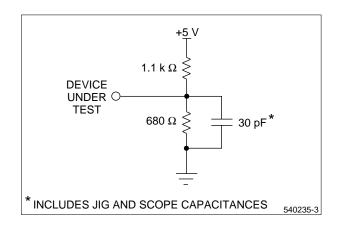

Figure 4. Output Load Circuit

### **OPERATING RANGE**

| SYMBOL           | PARAMETER                | MIN. | MAX.           | UNIT |

|------------------|--------------------------|------|----------------|------|

| T <sub>A</sub>   | Temperature, Ambient     | 0    | 70             | С    |

| V <sub>C</sub> C | Supply Voltage           | 4.5  | 5.5            | V    |

| V <sub>SS</sub>  | Supply Voltage           | 0    | 0              | V    |

| $V_{IL}$         | Logic LOW Input Voltage  | -0.5 | 0.8            | V    |

| V <sub>IH</sub>  | Logic HIGH Input Voltage | 2.0  | $V_{CC} + 0.5$ | V    |

# **DC ELECTRICAL CHARACTERISTICS (Over Operating Range)**

| SYMBOL | PARAMETER                                   | TEST CONDITIONS                                             | MIN. | MAX. | UNIT |

|--------|---------------------------------------------|-------------------------------------------------------------|------|------|------|

| ILI    | Input Leakage                               | $V_{CC} = 5.5 \text{ V}, V_{IN} = 0 \text{ V to } V_{CC}$   | -10  | 10   | μΑ   |

| ILO    | I/O Leakage                                 | $\overline{OE} \ge V_{IH}$ , $0 \ V \le V_{OUT} \le V_{CC}$ | -10  | 10   | μΑ   |

| Vон    | Output HIGH Voltage                         | $I_{OH} = -8.0 \text{ mA}$                                  | 2.4  |      | V    |

| VoL    | Output LOW Voltage                          | I <sub>OL</sub> = 16.0 mA                                   |      | 0.4  | V    |

| Icc    | Average Operating Supply Current 1,2        | Measured at f <sub>CC</sub> = 50 MHz                        |      | 245  | mA   |

| ICC2   | Average Standby Supply Current <sup>2</sup> | All inputs = V <sub>IHMIN</sub> (clocks idle)               |      | 25   | mA   |

| Icc3   | Power-Down Supply Current <sup>2</sup>      | All inputs = V <sub>CC</sub> - 0.2 V (clocks idle)          |      | 1    | mA   |

| ICC4   | Power-Down Supply Current <sup>2</sup>      | All inputs = V <sub>CC</sub> – 0.2 V (clocks at 50 MHz)     |      | 1    | mA   |

### NOTES:

- 1. Output load is disconnected.

- 2. I<sub>CC</sub>, I<sub>CC2</sub>, and I<sub>CC3</sub> are dependent upon actual output loading, and I<sub>CC</sub> and I<sub>CC4</sub> are also dependent on cycle rates. Specified values are with outputs open; and, for I<sub>CC</sub> and I<sub>CC4</sub>, operating at minimum cycle times.

### **AC TEST CONDITIONS**

| Р                              | RATING                            |                        |  |

|--------------------------------|-----------------------------------|------------------------|--|

| Input Pulse Levels             |                                   | V <sub>SS</sub> to 3 V |  |

| Input Rise and F               | Fall Times (10% to 90%)           | 3 ns                   |  |

| Input Timing Reference Levels  |                                   | 1.5 V                  |  |

| Output Timing Reference Levels |                                   | 1.5 V                  |  |

| Output Load,                   | R <sub>1</sub> (Top Resistor)     | 1.1k Ω                 |  |

| Timing Tests<br>(Figure 5)     | R <sub>2</sub> (Bottom Resistor)  | 680 Ω                  |  |

|                                | C <sub>L</sub> (Load Capacitance) | 30 pF                  |  |

### **CAPACITANCE**

| PARAMETER                                                    | RATING |

|--------------------------------------------------------------|--------|

| C <sub>IN</sub> (Input Capacitance) V <sub>IN</sub> = 0 V    | 9 pF   |

| C <sub>OUT</sub> (Output Capacitance) V <sub>OUT</sub> = 0 V | 9 pF   |

### **AC ELECTRICAL CHARACTERISTICS**

| SYMBOL             | PARAMETER                                                                | -:   | 20   | -    | 25   | -35  |      |

|--------------------|--------------------------------------------------------------------------|------|------|------|------|------|------|

| STWIBOL            | FARAWETER                                                                | MIN. | MAX. | MIN. | MAX. | MIN. | MAX. |

| fcc                | Clock Cycle Frequency                                                    |      | 50   |      | 40   |      | 28.6 |

| t <sub>A</sub>     | Data Access Time                                                         | 2    | 12   | 3    | 15   | 3    | 20   |

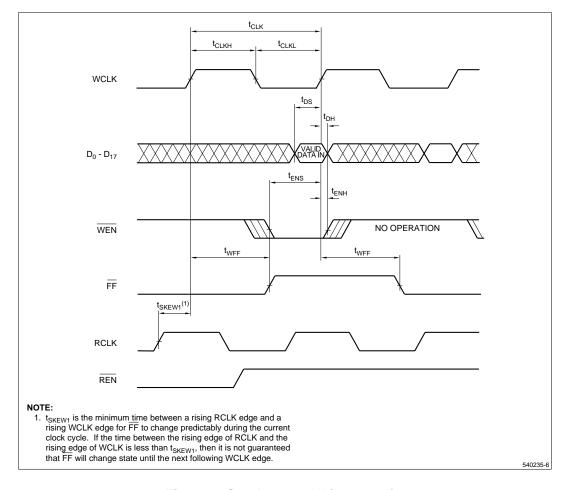

| t <sub>CLK</sub>   | Clock Cycle Time                                                         | 20   |      | 25   |      | 35   |      |

| t <sub>CLKH</sub>  | Clock HIGH Time                                                          | 8    |      | 10   |      | 14   |      |

| tCLKL              | Clock LOW Time                                                           | 8    |      | 10   |      | 14   |      |

| t <sub>DS</sub>    | Data Setup Time                                                          | 5    |      | 6    |      | 7    |      |

| t <sub>DH</sub>    | Data Hold Time                                                           | 2    |      | 2    |      | 2    |      |

| t <sub>ENS</sub>   | Enable Setup Time                                                        | 5    |      | 6    |      | 7    |      |

| t <sub>ENH</sub>   | Enable Hold Time                                                         | 2    |      | 2    |      | 2    |      |

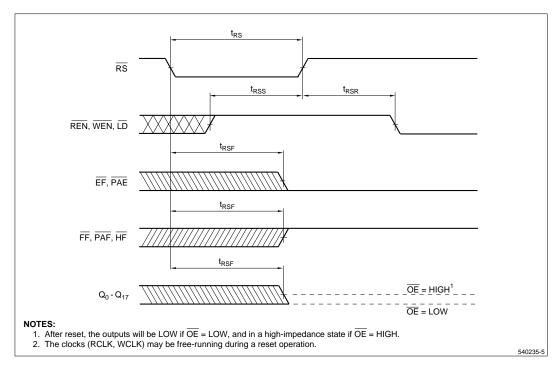

| t <sub>RS</sub>    | Reset Pulse Width <sup>1</sup>                                           | 20   |      | 25   |      | 35   |      |

| t <sub>RSS</sub>   | Reset Setup Time <sup>2</sup>                                            | 12   |      | 15   |      | 20   |      |

| t <sub>RSR</sub>   | Reset Recovery Time <sup>2</sup>                                         | 12   |      | 15   |      | 20   |      |

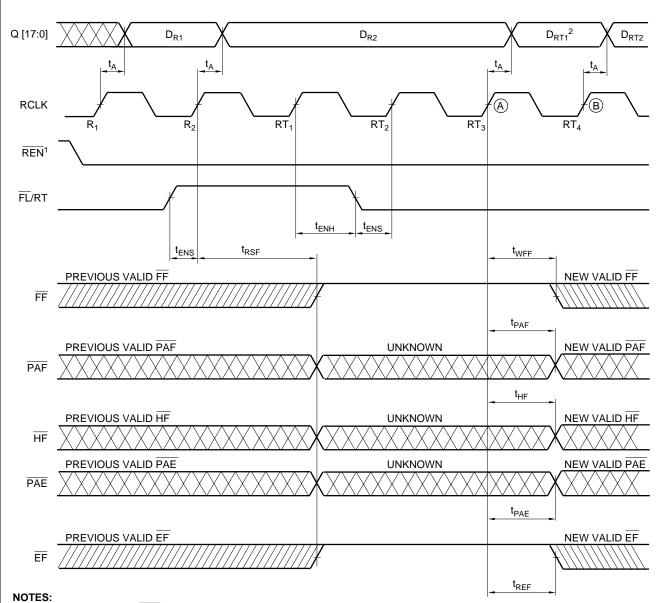

| t <sub>RSF</sub>   | Reset to Flag and Output Time                                            |      | 30   |      | 35   |      | 40   |

| toLZ               | Output Enable to Output in Low-Z 2                                       | 0    |      | 0    |      | 0    |      |

| toE                | Output Enable to Output Valid                                            |      | 9    |      | 12   |      | 15   |

| tonz               | Output Enable to Output in High-Z <sup>2</sup>                           | 1    | 9    | 1    | 12   | 1    | 15   |

| t <sub>WFF</sub>   | Write Clock to Full Flag                                                 |      | 12   |      | 15   |      | 20   |

| t <sub>REF</sub>   | Read Clock to Empty Flag                                                 |      | 12   |      | 15   |      | 20   |

| tpaf               | Clock to Programmable Almost-Full Flag (IDT-Compatible Operating Mode)   |      | 14   |      | 17   |      | 23   |

| t <sub>PAE</sub>   | Clock to Programmable Almost-Empty Flag (IDT-Compatible Operating Mode)  |      | 14   |      | 17   |      | 23   |

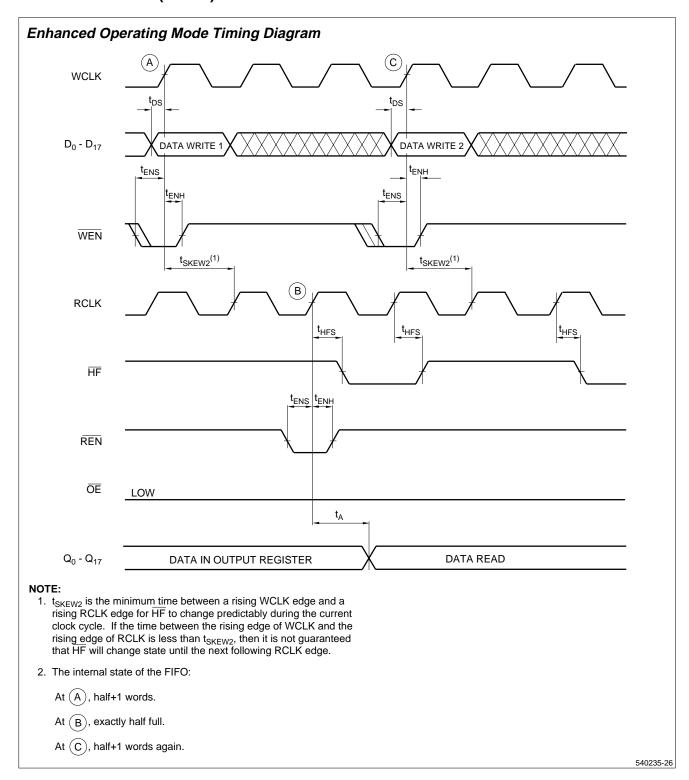

| t <sub>HF</sub>    | Clock to Half-Full Flag (IDT-Compatible Operating Mode)                  |      | 14   |      | 17   |      | 23   |

| t <sub>PAFS</sub>  | Clock to Programmable Almost-Full Flag (Enhanced Operating Mode)         |      | 14   |      | 17   |      | 23   |

| <i>t</i> PAES      | Clock to Programmable Almost-Empty Flag (Enhanced Operating Mode)        |      | 14   |      | 17   |      | 23   |

| tHFS               | Clock to Half-Full Flag (Enhanced Operating Mode)                        |      | 14   |      | 17   |      | 23   |

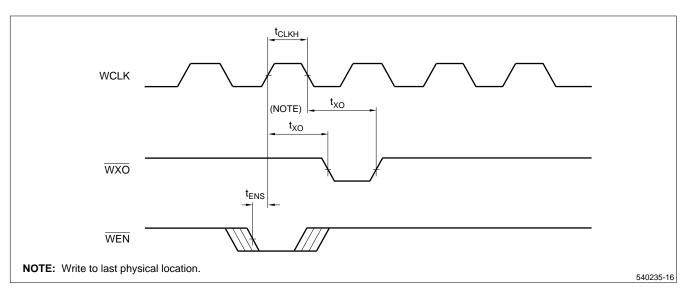

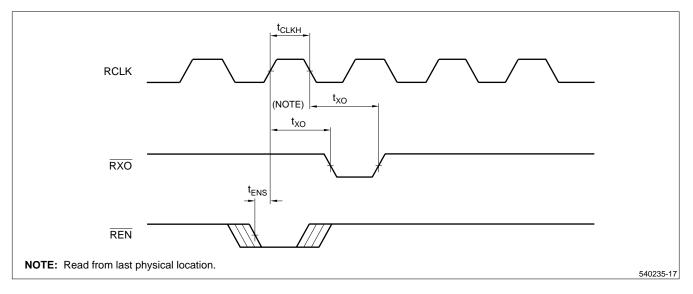

| t <sub>XO</sub>    | Clock to Expansion-Out                                                   |      | 12   |      | 15   |      | 20   |

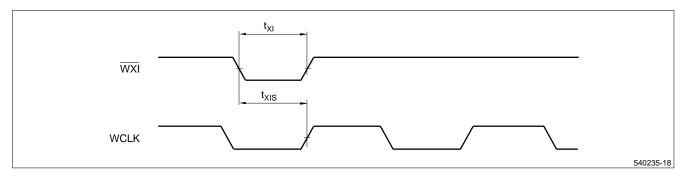

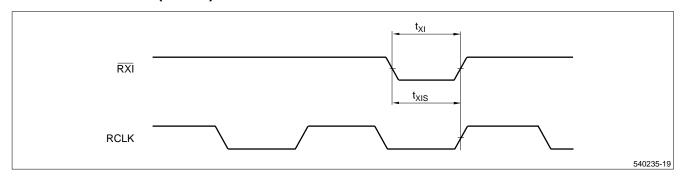

| t <sub>XI</sub>    | Expansion-In Pulse Width                                                 | 8    |      | 9    |      | 13   |      |

| t <sub>XIS</sub>   | Expansion-In Setup Time                                                  | 8    |      | 9    |      | 14   |      |

| tskew1             | Skew Time Between Read Clock and Write Clock for Full Flag <sup>3</sup>  | 9    |      | 11   |      | 16   |      |

| t <sub>SKEW2</sub> | Skew Time Between Write Clock and Read Clock for Empty Flag <sup>4</sup> | 9    |      | 11   |      | 16   |      |

#### NOTES

- 1. Pulse widths less than the stated minimum values may cause incorrect operation.

- 2. Values are guaranteed by design; not currently tested.

- 3. These times also apply to the Programmable-Almost-Full and Half-Full flags when they are synchronized to WCLK.

- 4. These times also apply to the Half-Full and Programmable-Almost-Empty flags when they are synchronized to RCLK.

### **DESCRIPTION OF SIGNALS AND OPERATING SEQUENCES**

Table 1. Grouping-Mode Determination

During a Reset Operation <sup>5</sup>

| EMODE          | WXI/WEN₂ | RXI/REN <sub>2</sub> | FL/RT          | MODE                                   | WXO/HF<br>USAGE | WXI/WEN₂<br>USAGE | RXI/REN <sub>2</sub><br>USAGE | FL/RT<br>USAGE | RXO/EF <sub>2</sub><br>USAGE |

|----------------|----------|----------------------|----------------|----------------------------------------|-----------------|-------------------|-------------------------------|----------------|------------------------------|

| H <sup>1</sup> | Н        | Н                    | Н              | Cascaded<br>Slave <sup>2</sup>         | WXO             | WXI               | RXI                           | FL             | RXO                          |

| H <sup>1</sup> | Н        | Н                    | L              | Cascaded<br>Master <sup>2</sup>        | WXO             | WXI               | RXI                           | FL             | RXO                          |

| Н              | Н        | L                    | Х              | (Reserved)                             | _               | _                 | _                             | _              | _                            |

| Н              | L        | Н                    | Х              | (Reserved)                             | _               | _                 | _                             | _              | _                            |

| н              | L        | L                    | H <sup>3</sup> | (Not<br>Allowed<br>During<br>Reset)    | (HF)            | (none)            | (none)                        | (RT)           | (none)                       |

| Н              | L        | L                    | L <sup>3</sup> | Standalone                             | HF              | (none)            | (none)                        | RT             | (none)                       |

| L              | Х        | х                    | H <sup>3</sup> | (Not<br>Allowed<br>During<br>Reset)    | (HF)            | (WEN₂)            | (REN <sub>2</sub> )           | (RT)           | (EF <sub>2</sub> )           |

| L              | X        | X                    | L 3            | Interlocked<br>Paralleled <sup>4</sup> | HF              | WEN <sub>2</sub>  | REN <sub>2</sub>              | RT             | EF <sub>2</sub>              |

#### NOTES:

- 1. In IDT-compatible cascading, a reset operation forces WXO/HF and RXO/EF<sub>2</sub> HIGH for the nth FIFO, thus forcing WXI/WEN<sub>2</sub> and RXI/REN<sub>2</sub> HIGH for the (n + 1)st FIFO.

- 2. The terms 'master' and 'slave' refer to IDT-compatible cascading. In pipelined cascading<sup>4</sup>, there is no such distinction.

- 3. Once grouping mode has been determined during a reset operation, FL/RT then may go HIGH to activate a retransmit operation.

- 4. EMODE must be asserted for access to the Control Register to be enabled. Also, FIFOs being used in a pipelined-cascading configuration should be in Interlocked Paralleled mode.

- 5. Setup-time and recovery-time specifications apply during a reset operation.

Table 2. Expansion-Pin Usage According to Grouping Mode

| I/O | PIN                 | IDT-COM                  | ENHANCED<br>OPERATING MODE |                         |                           |

|-----|---------------------|--------------------------|----------------------------|-------------------------|---------------------------|

|     |                     | DEPTH-CASCADED<br>MASTER | DEPTH-CASCADED<br>SLAVE    | STANDALONE              | INTERLOCKED<br>PARALLELED |

| I   | WXI /WEN2           | From WXO ((n-1)st FIFO)  | From WXO ((n-1)st FIFO)    | Grounded                | From FF (other FIFO)      |

| 0   | WXO/HF              | To WXI ((n+1)st FIFO)    | To WXI ((n+1)st FIFO)      | Becomes HF              | Becomes HF                |

| I   | RXI/ <b>REN</b> 2   | From RXO ((n-1)st FIFO)  | From RXO ((n-1)st FIFO)    | Grounded                | From EF (other FIFO)      |

| 0   | RXO/EF <sub>2</sub> | To RXI ((n+1)st FIFO)    | To RXI ((n+1)st FIFO)      | Unused                  | Becomes EF <sub>2</sub>   |

| I   | FL/ <i>RT</i>       | Grounded (Logic LOW)     | Logic HIGH                 | Becomes RT <sup>1</sup> | Becomes RT <sup>1</sup>   |

### NOTE:

FL/RT may be grounded if the Retransmit facility is not being used.

Table 3. Selection of Read and Write Operations

| LD | WEN 3,4 | REN 3,4 | WCLK | RCLK | ACTION                                                                                    |

|----|---------|---------|------|------|-------------------------------------------------------------------------------------------|

| L  | Х       | Х       | _    | _    | No operation.                                                                             |

| L  | L       | L       | ^    | ^    | Illegal combination, which will cause errors.                                             |

| L  | L       | Н       | ^    | Х    | Write to a programmable register. <sup>1</sup>                                            |

| L  | Н       | Н       | ^    | Х    | Hold present value of programmable-register write counter, and do not write. <sup>2</sup> |

| L  | Н       | L       | Х    | ^    | Read from a programmable register. <sup>1</sup>                                           |

| L  | Н       | Н       | Х    | ^    | Hold present value of programmable-register read counter, and do not read. <sup>2</sup>   |

| Н  | L       | Х       | ^    | Х    | Normal FIFO write operation.                                                              |

| Н  | Х       | L       | Х    | ^    | Normal FIFO read operation.                                                               |

| Н  | L       | Х       | _    | Х    | No write operation.                                                                       |

| Н  | Н       | Х       | Х    | Х    | No write operation.                                                                       |

| Н  | Х       | L       | Х    | _    | No read operation.                                                                        |

| Н  | Х       | Н       | Х    | Х    | No read operation.                                                                        |

| Н  | L       | L       | _    | _    | No operation.                                                                             |

| Н  | Н       | Н       | Х    | Х    | No operation.                                                                             |

#### KEY:

H = Logic 'HIGH'; L = Logic 'LOW'; X = 'Don't-care' (logic 'HIGH,' logic 'LOW,' or any transition);

$\wedge$  = A 'LOW'-to-'HIGH' transition; -= Any condition EXCEPT a 'LOW'-to-'HIGH' transition.

- The selection of a programmable register to be written or read is controlled by two simple state machines. One state machine controls the selection for writing; the other state machine controls the selection for reading. These two state machines operate independently of each other. Both state machines are reset to point to Word 0 by a reset operation. In the <u>Enhanced Operating Mode, if Control Register bit 00 is set, both</u> state machines are also reset to point to Word 0 by deassertion of LD after LD has been asserted (that is, by a rising edge of LD), followed by a valid memory array write cycle for the writing-control state machine and/or by a valid memory array read cycle for the reading-control state machine.

- The order of the two programmable registers which are accessible in IDT-Compatible Operating Mode, as selected by either state machine, is always:

Word 0: Almost-Empty Offset Register Word 1: Almost-Full Offset Register Word 0: Almost-Empty Offset Register

(repeats indefinitely)

The order of the three programmable registers which are accessible in Enhanced Operating Mode, as selected by either state machine, is always:

Word 0: Almost-Empty Offset Register

Word 1: Almost-Full Offset Register

Word 2: Control Register

Word 0: Almost-Empty Offset Register

(repeats indefinitely)

Note that, in IDT-Compatible Operating Mode, Word 2 is not accessed; Word 0 and Word 1 alternate.

- After normal FIFO operation has begun, writing new contents into either of the offset registers should only be done when the FIFO is empty.

- WEN<sub>2</sub>, REN<sub>2</sub>, and  $\overline{OE}$  may be ANDed terms in the enabling of read and write operations, according to the state of the EMODE control input and of Control Register bit 05.

Table 4. Status Flags

| NUMBER OF UNREAD DATA W  | ORDS PRESENT WITHIN FIFO 1,2          | FULL<br>FLAG | MIDDLE FLAGS |     |    | EMPTY<br>FLAG |

|--------------------------|---------------------------------------|--------------|--------------|-----|----|---------------|

| 2048 × 18 FIFO           | FF                                    | PAF          | HF           | PAE | EF |               |

| 0                        | 0                                     | Н            | Н            | Н   | L  | L             |

| 1 to q                   | 1 to q 1 to q                         |              | Н            | Н   | L  | Н             |

| (q + 1) to 1024          | (q + 1) to 1024 (q + 1) to 2048       |              | Н            | Н   | Н  | Н             |

| 1025 to (2048 – (p + 1)) | 2049 to (4096 – (p + 1))              | Н            | Н            | L   | Н  | Н             |

| (2048 – p) to 2047       | (2048 – p) to 2047 (4096 – p) to 4095 |              | L            | L   | Н  | Н             |

| 2048 4096                |                                       | L            | L            | L   | Н  | Н             |

#### NOTES:

- 1. q = Programmable-Almost-Empty Offset value. (Default value: <math>q = 127.)

- 2. p = Programmable-Almost-Full Offset value. (Default value: p = 127.)

- 3. Only 11 (2048 × 18), or all 12 (4096 × 18), of the 12 offset-value-register bits should be programmed. The unneeded most-significant-end 2048 × 18 bit should be LOW (zero).

- 4. The flag output is delayed by one full clock cycle in Enhanced Operating Mode, when synchronous operation is specified for intermediate flags.

# **DESCRIPTION OF SIGNALS AND OPERATING SEQUENCES (cont'd)**

Table 5. Control-Register Format

| COMMAND               |           | VALUE AF  | TER RESET | FLAG                |                                                                                                                                                                                                                                                                              |                                                                                                                                      |

|-----------------------|-----------|-----------|-----------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| REGISTER<br>BITS      |           | EMODE = H | EMODE = L | AFFECTED,<br>IF ANY | DESCRIPTION                                                                                                                                                                                                                                                                  | NOTES                                                                                                                                |

|                       | L         |           | н         | _                   | Deassertion of LD does not reset the programmable-register write pointer and read pointer.                                                                                                                                                                                   | IDT-compatible addressing of programmable registers.                                                                                 |

| 00                    | н         | L         |           |                     | Deassertion of LD resets the programmable-register write pointer and read pointer to address Word 0, the Programmable-Almost-Empty-Flag-Offset Register. The change takes effect after a valid write operation or a valid read operation, respectively, to the memory array. | Non-ambiguous<br>addressing of<br>programmable registers.                                                                            |

| 01                    | L         | L H       |           | PAE                 | Set by ↑RCLK, reset by ↑WCLK.                                                                                                                                                                                                                                                | Asynchronous flag clocking.                                                                                                          |

|                       | Н         |           |           |                     | Set and reset by TRCLK.                                                                                                                                                                                                                                                      | Synchronous flag clocking.                                                                                                           |

|                       | LL        |           | нн        | ĦF                  | Set by ↑WCLK, reset by ↑RCLK.                                                                                                                                                                                                                                                | Asynchronous flag clocking.                                                                                                          |

| 03, 02                | LH        | LL        |           |                     | Set and reset by ↑RCLK.                                                                                                                                                                                                                                                      | Synchronous flag clocking at output port.                                                                                            |

|                       | HL,<br>HH |           |           |                     | Set and reset by ↑WCLK.                                                                                                                                                                                                                                                      | Synchronous flag clocking at input port.                                                                                             |

| 04                    | L         | L         | Н         | PAF                 | Set by ↑WCLK, reset by ↑RCLK.                                                                                                                                                                                                                                                | Asynchronous flag clocking.                                                                                                          |

|                       | Н         |           |           |                     | Set and reset by ↑WCLK.                                                                                                                                                                                                                                                      | Synchronous flag clocking.                                                                                                           |

|                       | L         | L         | н         | -                   | OE has no effect on an internal read operation, apart from disabling the outputs.                                                                                                                                                                                            | Allows the read-address pointer to advance even when $Q_0 - Q_{17}$ are not driving the output bus.                                  |

| 05                    | н         |           |           |                     | Deassertion of $\overline{OE}$ inhibits a read operation; whenever the data outputs $Q_0 - Q_{17}$ are in the high-Z state, the read pointer does not advance.                                                                                                               | Inhibits the read-address pointer from advancing when $Q_0 - Q_{17}$ are not driving the output bus; thus, guards against data loss. |

|                       | L         |           |           | -                   | Reserved.                                                                                                                                                                                                                                                                    | Future use to control depth                                                                                                          |

| 06                    | Н         | L         | L         |                     |                                                                                                                                                                                                                                                                              | cascading and interlocked paralleling.                                                                                               |

| 11, 10,<br>09, 08, 07 | LLLLL     | LLLLL     | LLLLL     | _                   | Reserved.                                                                                                                                                                                                                                                                    | Reserved.                                                                                                                            |

#### NOTES:

When <u>FMODE</u> is HIGH, and <u>Control Register bits 00-05 are LOW</u>, the FIFO behaves in a manner functionally equivalent to the IDT72235B/45B FIFO of similar depth and speed grade. Under these conditions, the <u>Control Register</u> is not visible or accessible to the external system which includes the FIFO.

If EMODE is not asserted (is HIGH), Control Register bits 00-05 remain LOW after a reset operation. However, if EMODE is asserted (is LOW) during a reset operation. Control Register bits 00-05 are forced HIGH, and remain HIGH until changed. Control Register bits 06-11 are unaffected by EMODE.

### **Data Inputs**

### DATA IN $(D_0 - D_{17})$

Data, programmable-flag-offset values, and *Control-Register* codes are input to the FIFO as 18-bit words on  $D_0 - D_{17}$ . Unused bit positions in offset-value *and Control-Register* words should be zero-filled.

### **Control Inputs**

### RESET (RS)

The FIFO is reset whenever the asynchronous Reset (RS) input is taken to a LOW state. A reset operation is required after power-up, before the first write operation may occur. The state of the FIFO is fully defined after a reset operation. If the default values which are entered into the Programmable-Flag-Offset-Value Registers and the Control Register by a reset operation are acceptable, then no device programming is required. A reset operation initializes the FIFO's internal read-address and write-address pointers to the FIFO's first physical memory location. The five status flags, FF, PAF, HF, PAE, and EF, are updated to indicate that the FIFO is completely empty: thus, the first three of these are reset to HIGH, and the last two are reset to LOW. The flag-offset values for PAF and PAE each are initialized to 127<sub>10</sub>. If **EMODE** is not being asserted (i.e., if **EMODE** is HIGH), all **Control** Register bits are initialized to LOW, to configure the FIFO to operate in the IDT72235B/45B-Compatible Operating Mode. Until a write operation occurs, the data outputs  $D_0 - D_{17}$  all are LOW whenever  $\overline{OE}$  is LOW.

### **ENHANCED OPERATING MODE (EMODE)**

Whenever EMODE is asserted during a reset operation, Control Register bits 00-05 remain HIGH rather than LOW after the completion of the reset operation. Thus, EMODE has the effect of activating all of the Enhanced-Operating-Mode features during a reset operation. Subsequently, they may be individually disabled or re-enabled by changing the setting of Control-Register bits. The behavior of these Enhanced-Operating-Mode features is described in Table 5. For permanent Enhanced-Operating-Mode operation, EMODE must be grounded; dynamic control of EMODE during system operation is not recommended.

Asserting EMODE during a reset operation also causes WXI/WEN2 to be configured as WEN2, and RXI/REN2 to be configured as REN2, to support interlocked-paralleled operation of two FIFOs 'side by side' (see Figure 28). Additionally, RXO/EF2 is configured as EF2, which duplicates the EF signal with one extra RCK cycle delay, in order to provide proper timing for 'pipelined' cascaded operation.

### WRITE CLOCK (WCLK)

A rising edge (LOW-to-HIGH transition) of WCLK initiates a FIFO write cycle if  $\overline{LD}$  is HIGH, or a programmable-register write cycle if  $\overline{LD}$  is LOW. The 18 data inputs, and all input-side synchronous control inputs, must meet setup and hold times with respect to the rising edge of WCLK. The input-side status flags are meaningful after specified time intervals, following a rising edge of WCLK.

Conceptually, the WCLK input receives a free-running, periodic 'clock' waveform, which is used to control other signals which are edge-sensitive. However, there actually is not any absolute requirement that the WCLK waveform *must* be periodic. An 'asynchronous' mode of operation is in fact possible, if WEN is continuously asserted (that is, is continuously held LOW), and WCLK receives aperiodic 'clock' pulses of suitable duration. There likewise is no requirement that WCLK must have any particular synchronization relation to the read clock RCLK. These two clock inputs may in fact receive the same 'clock' signal; or they may receive totally-different signals, which are not synchronized to each other in any way.

### WRITE ENABLE (WEN)

Whenever WEN is being asserted (is LOW) and LD is HIGH, and the FIFO is not full, an 18-bit data word is loaded into the effective input register for the memory array at every WCLK rising edge (LOW-to-HIGH transition). Data words are stored into the two-port memory array sequentially, regardless of any ongoing read operation. Whenever WEN is not being asserted (is HIGH), the input register retains whatever data word it contained previously, and no new data word gets loaded into the memory array.

To prevent overrunning the internal FIFO boundaries, further write operations are inhibited whenever the Full Flag ( $\overline{FF}$ ) is being asserted (is LOW). If a valid read operation then occurs, upon the completion of that read cycle  $\overline{FF}$  again goes HIGH after a time  $t_{WFF}$ , and another write operation is allowed to begin whenever WCLK makes another LOW-to-HIGH transition. Effectively,  $\overline{WEN}$  is overridden by  $\overline{FF}$ ; thus, during normal FIFO operation,  $\overline{WEN}$  has no effect when the FIFO is full.

In the Enhanced Operating Mode, WXI/WEN<sub>2</sub> functions as WEN<sub>2</sub>, an additional duplicate (albeit assertive-HIGH) write-enable input, in order to provide an interlocking mechanism for reliable synchronization of two paralleled FIFOs. To control writing, WEN<sub>2</sub> is ANDed with WEN; this logic-AND function (WEN • WEN<sub>2</sub>) then behaves like WEN in the foregoing description.

# DESCRIPTION OF SIGNALS AND OPERATING SEQUENCES (cont'd)

### **READ CLOCK (RCLK)**

A rising edge (LOW-to-HIGH transition) of RCLK initiates a FIFO read cycle if  $\overline{\text{LD}}$  is HIGH, or a programmable-register read cycle if  $\overline{\text{LD}}$  is LOW. All output-side synchronous control inputs must meet setup and hold times with respect to the rising edge of RCLK. The 18 data outputs, and the output-side status flags, are meaningful after specified time intervals, following a rising edge of RCLK.

Conceptually, the RCLK input receives a free-running, periodic 'clock' waveform, which is used to control other signals which are edge-sensitive. However, there actually is not any absolute requirement that the RCLK waveform *must* be periodic. An 'asynchronous' mode of operation is in fact possible, if REN is continuously asserted (that is, is continuously held LOW), and RCLK receives aperiodic 'clock' pulses of suitable duration. There likewise is no requirement that RCLK must have any particular synchronization relation to the write clock WCLK. These two clock inputs may in fact receive the same 'clock' signal; or they may receive totally-different signals, which are not synchronized to each other in any way.

### **READ ENABLE (REN)**

Whenever REN is being asserted (is LOW), and the FIFO is not empty, an 18-bit data word is loaded into the output register from the memory array at every RCLK rising edge (LOW-to-HIGH transition). Data words are read from the two-port memory array sequentially, regardless of any ongoing write operation. Whenever REN is not being asserted (is HIGH), the output register retains whatever data word it contained previously, and no new data word gets loaded into it from the memory array.

To prevent underrunning the internal FIFO boundaries, further read operations are inhibited whenever the Empty Flag  $(\overline{EF})$  is being asserted (is LOW). If a valid write operation then occurs, upon the completion of that write cycle  $\overline{EF}$  again goes HIGH after a time  $t_{REF}$ , and another read operation is allowed to begin whenever RCLK makes another LOW-to-HIGH transition. Effectively,  $\overline{REN}$  is overridden by  $\overline{EF}$ ; thus, during normal FIFO operation,  $\overline{REN}$  has no effect when the FIFO is empty.

In the Enhanced Operating Mode, one (or, sometimes two) additional read-enable inputs may be ANDed with  $\overline{REN}$  to control reading, depending on the state of Control-Register bit 05. The additional read-enable input(s) are  $REN_2$  (and  $\overline{OE}$ ).

Also in the Enhanced Operating Mode,  $\overline{RX}$ //REN<sub>2</sub> functions as REN<sub>2</sub>, an additional duplicate (albeit assertive-HIGH) Read-Enable input, in order to provide an 'interlocking' mechanism for reliable synchronization of two paralleled FIFOs.

Also, if Control Register bit 05 is HIGH,  $\overline{OE}$  takes on the extra role of serving as yet another duplicate read-enable input, in addition to its usual function of controlling the FIFO's data outputs, in order to inhibit further read operations whenever the FIFO's data outputs are disabled, and thereby to prevent data loss under some circumstances.

### **OUTPUT ENABLE (OE)**

$\overline{\text{OE}}$  is an assertive-LOW, asynchronous, output enable. In the IDT-Compatible Operating Mode,  $\overline{\text{OE}}$  has only the effect of enabling or disabling the data outputs  $Q_0-Q_{17}$ . That is, disabling  $Q_0-Q_{17}$  does not inhibit a read operation, for data being transmitted to the output register; the same data will remain available later, when the outputs are again enabled, unless subsequently overwritten. When  $Q_0-Q_{17}$  are enabled, each of these 18 data outputs is in a normal HIGH or LOW state, according to the bit pattern of the data word in the output register. When  $Q_0-Q_{17}$  are disabled, each of these outputs is in the high-Z (high-impedance) state.

In the Enhanced Operating Mode, if Control Register bit 05 is HIGH,  $\overline{OE}$  behaves as an additional read-enable control input, as well as enabling and disabling the data outputs  $Q_0-Q_{17}$ . Under these circumstances, incrementing the read-address pointer is inhibited whenever  $Q_0-Q_{17}$  are in the high-Z state. Thus, 'reading' successive words which fail ever to reach the outputs is prevented, as a safeguard against data loss.

### LOAD $(\overline{LD})$

The Sharp LH540235/45 FIFOs contain *three* 18-bit programmable registers. The contents of these three registers may be loaded with data from the data inputs  $D_0 - D_{17}$ , or read out onto the data outputs  $Q_0 - Q_{17}$ . The first two registers are the Programmable-Flag-Offset-Value Registers, for the Programmable Almost-Empty Flag (PAE) and the Programmable Almost-Full Flag (PAF) respectively. The third register is the Control Register, which includes several configuration-control bits for selectively enabling and disabling Sharp's Enhanced-Operating-Mode features.

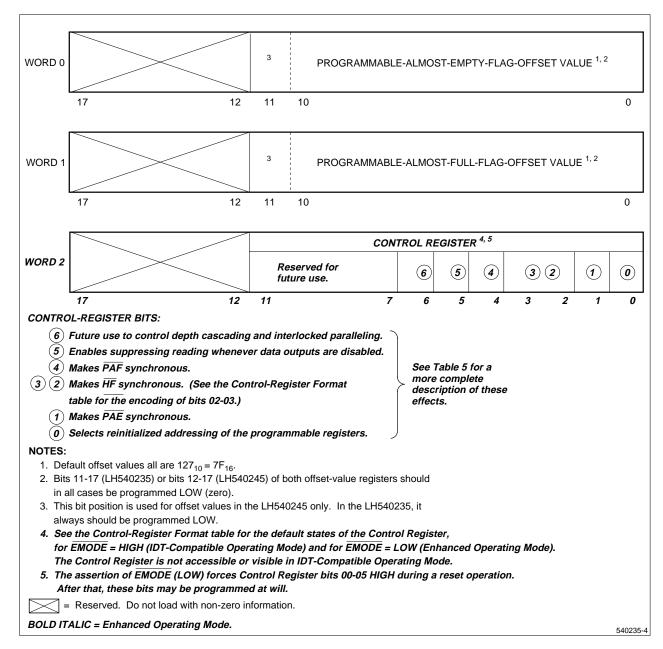

Figure 5. Programmable Registers

None of these three registers makes use of all of its available 18 bits. Figure 6 shows which bit positions of each register are operational. The two Programmable-Flag-Offset-Value Registers each contain an offset value in bits 0-10 (LH540235) or bits 0-11 (LH540245); bits 11-17 (LH540235) or bits 12-17 (LH540245) are unused. The default values for both offsets are 127<sub>10</sub>.

The *Control Register* configuration is shown in Figure 6 and in Table 5. For the *Control Register*, in the IDT-Compatible Operating Mode, with *EMODE* deasserted (HIGH), the default value for all Control-Register bits is zero (LOW). *In the Enhanced Operating Mode, with EMODE* asserted (LOW), the default value for bits 00-05 is HIGH, and the default value for bits 06-11 is LOW.

BOLD ITALIC = Enhanced Operating Mode

Whenever  $\overline{\text{LD}}$  and  $\overline{\text{WEN}}$  are simultaneously being asserted (are both LOW), the 18-bit data word from the data inputs D<sub>0</sub> – D<sub>17</sub> is written into the Programmable-Almost-Empty-Flag-Offset-Value Register at the first rising edge (LOW-to-HIGH transition) of the write clock (WCLK). (See Table 3.) If  $\overline{\text{LD}}$  and  $\overline{\text{WEN}}$  continue to be simultaneously asserted, another 18-bit data word from the data inputs D<sub>0</sub> – D<sub>17</sub> is written into the Programmable-Almost-Full-Flag-Offset-Value Register at the second rising edge of WCLK.

# DESCRIPTION OF SIGNALS AND OPERATING SEQUENCES (cont'd)

What happens next is determined by the state of the  $\overline{\it EMODE}$  control input. If it is deasserted (HIGH), the next 18-bit word from the data inputs D<sub>0</sub> – D<sub>17</sub> is written back into the Programmable-Almost-Empty-Flag-Offset-Value Register again.

But, if  $\overline{EMODE}$  is asserted (LOW), then still another 18-bit data word from the data inputs  $D_0 - D_{17}$  is written into the Control Register at the third rising edge of WCLK. At the fourth rising edge of WCLK, writing again occurs to the Programmable-Almost-Empty-Flag-Offset-Value Register; and the same three-step writing sequence gets repeated on subsequent WCLK rising edges.

The lower 11 bits of these offset-value words are made use of by the 2048-word LH540235, and the lower 12 bits by the 4096-word LH540245. *Six active bits are used for the Control Register, by both the LH540235 and the LH540245.* There is no restriction on the values which may occur in these offset-value *and Control-Register* fields. However, *reserved* bit positions must be encoded LOW, in order to maintain forward compatibility.

Writing contents to these two *or three* programmable registers does not have to occur all at one time, or to be effected by one single sequence of steps. Whenever  $\overline{LD}$  is being asserted (is LOW) but  $\overline{WEN}$  is not being asserted (is HIGH), the FIFO's internal programmable-register-write-address pointer maintains its present value, without any writing actually taking place at each rising edge of WCLK (see Table 3). Thus, for instance, one or two programmable registers may be written, after which the FIFO may be returned to normal FIFO-array-read/write operation by deasserting  $\overline{LD}$  (to HIGH).