# SANYO Semiconductors **DATA SHEET**

An ON Semiconductor Company

LV49152V — Class-D Audio Power Amplifier BTL 15W × 2ch

#### Overview

The LV49152V is a 15W per channel stereo digital power amplifier that takes analog inputs. The LV49152V uses unique SANYO-developed feedback technology to achieve excellent audio quality despite being a class D amplifier and can be used to implement high quality flat display panel (FDP) based systems.

#### **Features**

- BTL output, class D amplifier system

- Unique SANYO-developed feedback technology achieves superb audio quality

- High-efficiency class D amplifier

- Soft muting function reduces impulse noise at power on/off

- Full complement of built-in protection circuits : over current protection, thermal protection, and low power supply voltage protection circuits

- Built in Power limiter

#### **Functions**

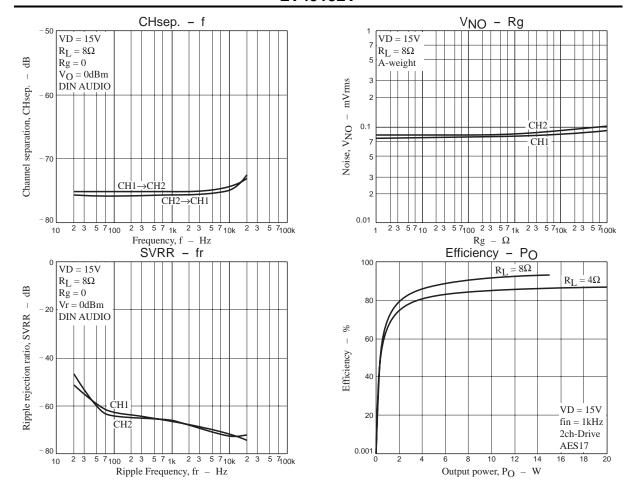

• Power :  $15W \times 2$ ch output (VD = 15V, R<sub>L</sub> =  $8\Omega$ , fin = 1kHz, AES17, THD + N = 10%)

• Efficiency: 93% (VD = 15V,  $R_L = 8\Omega$ , fin = 1kHz,  $P_O = 15W$ )

$\bullet$  THD + N  $\,$  : 0.08% (VD = 15V, RL = 80, fin = 1kHz, PO = 1W, Filter : AES17)

• Noise : 90µVrms (Filter : A-weight)

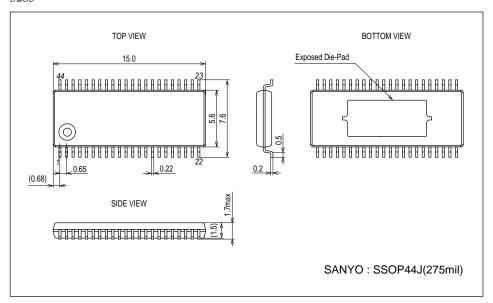

• Package SSOP44J (275mil)

- Any and all SANYO Semiconductor Co.,Ltd. products described or contained herein are, with regard to "standard application", intended for the use as general electronics equipment (home appliances, AV equipment, communication device, office equipment, industrial equipment etc.). The products mentioned herein shall not be intended for use for any "special application" (medical equipment whose purpose is to sustain life, aerospace instrument, nuclear control device, burning appliances, transportation machine, traffic signal system, safety equipment etc.) that shall require extremely high level of reliability and can directly threaten human lives in case of failure or malfunction of the product or may cause harm to human bodies, nor shall they grant any guarantee thereof. If you should intend to use our products for applications outside the standard applications of our customer who is considering such use and/or outside the scope of our intended standard applications, please consult with us prior to the intended use. If there is no consultation or inquiry before the intended use, our customer shall be solely responsible for the use.

- Specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

#### SANYO Semiconductor Co., Ltd.

www.semiconductor-sanyo.com/network

# **Specifications**

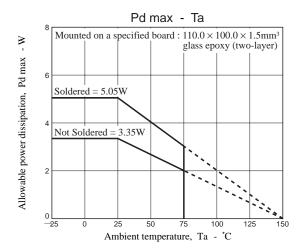

#### **Absolute Maximum Ratings** at Ta = 25°C

| Parameter                    | Symbol | Conditions              | Ratings     | Unit |

|------------------------------|--------|-------------------------|-------------|------|

| Maximum supply voltage       | VD     | Supply voltage          | 20          | V    |

| Allowable power dissipation  | Pd max | Our PCB, Soldered *     | 5.05        | W    |

| Package thermal resistance   | θјс    | Our PCB, Soldered *     | 2.1         | °C/W |

|                              |        | Our PCB, Not soldered * | 3.6         | °C/W |

| Maximum junction temperature | Tj max |                         | 150         | °C   |

| Operating temperature        | Topr   |                         | -25 to +75  | °C   |

| Storage temperature          | Tstg   |                         | -50 to +150 | °C   |

<sup>\*:</sup> Mounted on a specified board 110.0mm × 100.0mm × 1.5mm, glass epoxy (two-layer)

#### **Recommended Operating Range** at Ta = 25°C

| Doromotor            | Parameter Symbol Conditions |                | Ratings |     |     | Unit |

|----------------------|-----------------------------|----------------|---------|-----|-----|------|

| Parameter            |                             |                | min     | typ | max | Unit |

| Supply voltage range | VD                          | Supply voltage | 9       | 15  | 18  | V    |

| Load impedance range | RL                          | Speaker load   | 4       | 8   |     | Ω    |

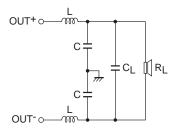

# Electrical Characteristics at $Ta=25^{\circ}C,~VD=15V,~R_L=8\Omega,~L=33\mu H~(TOKO:A7502BY-330M),~C=0.1\mu F,~C_L=0.47\mu F$

| Demonstra                      | 0                   | Symbol Conditions                        |      | Ratings |     |       |  |

|--------------------------------|---------------------|------------------------------------------|------|---------|-----|-------|--|

| Parameter                      | Symbol Conditions   |                                          | min  | typ     | max | Unit  |  |

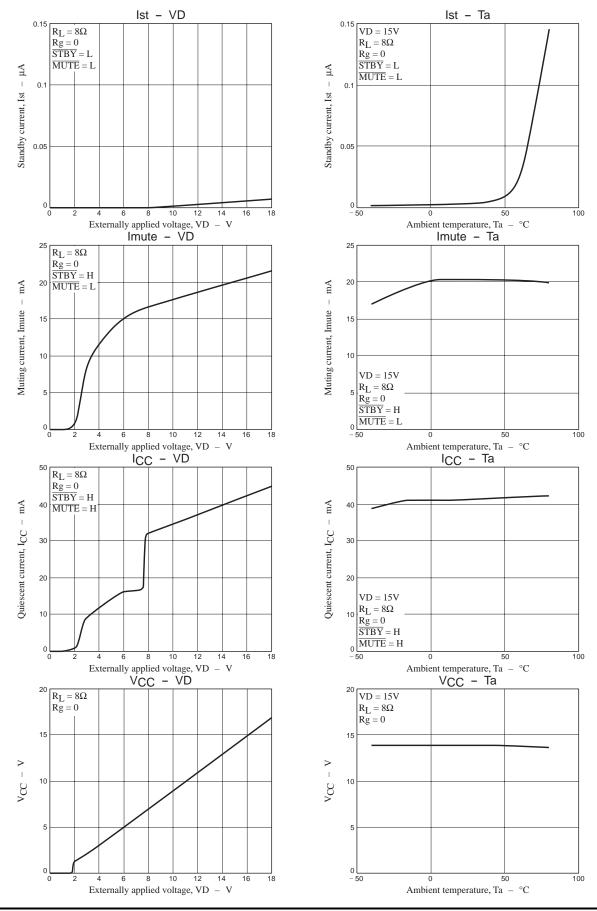

| Standby current                | Ist                 | STBY = L, MUTE = L                       |      | 1       | 10  | μΑ    |  |

| Mute current                   | Imute               | STBY = H, MUTE = L                       | 14   | 20      | 26  | mA    |  |

| Quiescent current              | Icco                | STBY = H, MUTE = H                       | 35   | 45      | 55  | mA    |  |

| Voltage gain                   | VG                  | fin = 1kHz, V <sub>O</sub> = 0dBm        | 28   | 30      | 32  | dB    |  |

| Offset voltage                 | Voffset             | Rg = 0                                   | -150 |         | 150 | mV    |  |

| Total harmonic distortion      | THD+N               | P <sub>O</sub> = 1W, fin = 1kHz, AES17   |      | 0.08    | 0.4 | %     |  |

| Output power                   | P <sub>O</sub> @10% | THD+N = 10%, AES17                       | 13   | 15      |     | W     |  |

| Channel separation             | CHsep.              | Rg = 0, V <sub>O</sub> = 0dBm, DIN AUDIO | 55   | 70      |     | dB    |  |

| Ripple rejection ratio         | SVRR                | fr = 100Hz, Vr = 0dBm, Rg = 0, DIN AUDIO | 50   | 60      |     | dB    |  |

| Noise                          | V <sub>NO</sub>     | Rg = 0, A-weight                         |      | 90      | 300 | μVrms |  |

| High-level input voltage       | V <sub>IH</sub>     | STBY and MUTE pin                        | 3    |         | VD  | V     |  |

| Low-level input voltage        | V <sub>IL</sub>     | STBY and MUTE pin                        | 0    |         | 1   | V     |  |

| Under voltage protection UPPER | UV_UPPER            | VD voltage measure                       |      | 8.0     |     | V     |  |

| Under voltage protection LOWER | UV_LOWER            | VD voltage measure                       |      | 7.0     |     | V     |  |

Note: The values of these characteristics were measured in the SANYO test environment. The actual values in an end system will vary depending on the printed circuit board pattern, the external components actually used, and other factors.

# **Package Dimensions**

unit: mm (typ)

3285

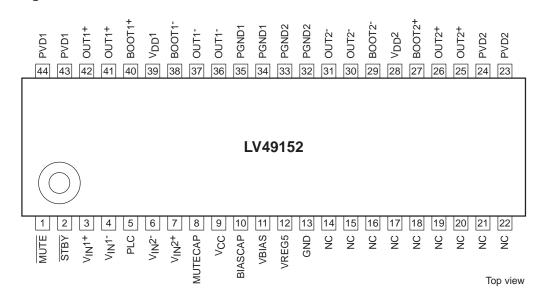

#### **Pin Assignment**

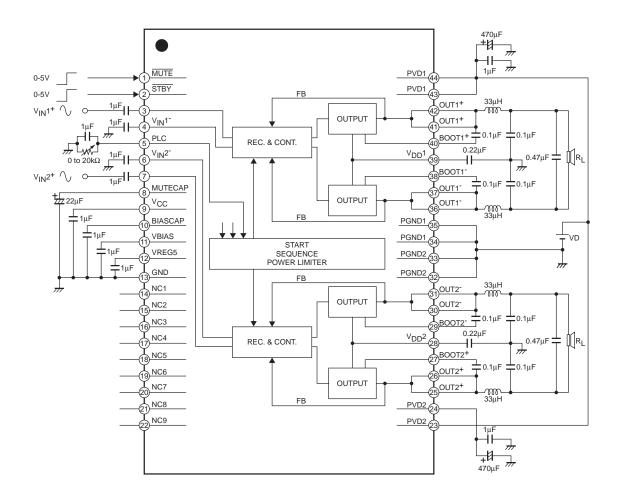

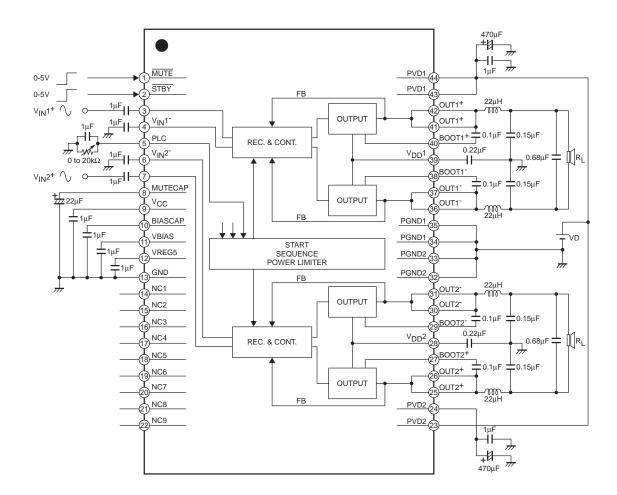

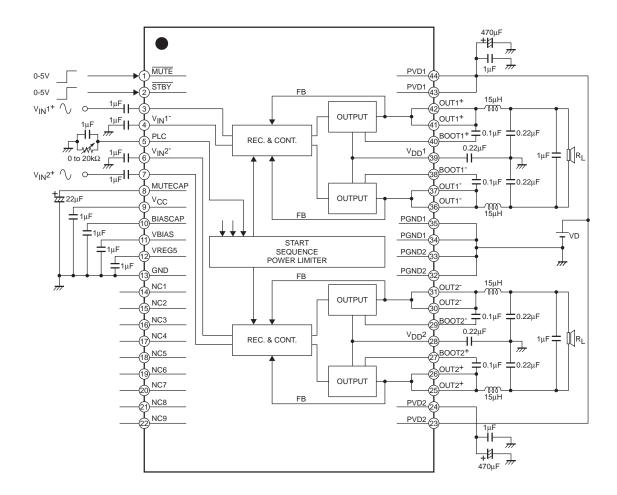

# Block Diagram and Application Circuit Example 1 ( $R_L = 8\Omega$ )

# Application Circuit Example 2 ( $R_L = 6\Omega$ )

# Application Circuit Example 3 ( $R_L = 4\Omega$ )

# Pin Equivalent Circuit

| Pin No. | Pin name                       | I/O | Description             | Equivalent Circuit                                                                                      |

|---------|--------------------------------|-----|-------------------------|---------------------------------------------------------------------------------------------------------|

| 1       | MUTE                           | I   | Mute control pin        | $\begin{array}{c c} VD \\ \hline \\ 250k\Omega \\ \hline \\ 100k\Omega \\ \hline \\ GND \\ \end{array}$ |

| 2       | STBY                           | I   | Standby control pin     | 250kΩ \$  10kΩ                                                                                          |

| 3       | V <sub>IN</sub> 1+             | 1   | Input pin, CH1 plus     | 300Ω<br>300Ω<br>\$30kΩ<br>VBIAS<br>GND                                                                  |

| 4       | V <sub>IN</sub> 1 <sup>-</sup> | I   | Input pin, CH1 minus    | VD<br>300Ω<br>300Ω<br>VBIAS<br>GND                                                                      |

| 5       | PLC                            | ı   | Power level control pin | VD 200Ω GND                                                                                             |

|         | ontinued from preceding page.  |     |                                                      |                                        |  |  |  |  |

|---------|--------------------------------|-----|------------------------------------------------------|----------------------------------------|--|--|--|--|

| Pin No. | Pin name                       | I/O | Description                                          | Equivalent Circuit                     |  |  |  |  |

| 6       | V <sub>IN</sub> 2 <sup>-</sup> | I   | Input pin, CH2 minus                                 | VD  300Ω  \$300Ω  VBIAS  GND           |  |  |  |  |

| 7       | V <sub>IN</sub> 2+             | I   | Input pin, CH2 plus                                  | VD<br>300Ω<br>\$30kΩ<br>VBIAS<br>GND   |  |  |  |  |

| 8       | MUTECAP                        | 0   | Muteing sysytem capcitor connection                  | V <sub>DD</sub> V <sub>D</sub> 8       |  |  |  |  |

| 9       | Vcc                            | 0   | Internal power supply decupling capacitor connection | 9<br>GND                               |  |  |  |  |

| 10      | BIASCAP                        | 0   | Internal regulator decupling capacitor connection    | VD $1kΩ$ $1kΩ$ $1kΩ$ $3100kΩ$ $§100kΩ$ |  |  |  |  |

Continued from preceding page.

| Continued from preceding page. |          |     |                                                   |                     |  |  |  |  |

|--------------------------------|----------|-----|---------------------------------------------------|---------------------|--|--|--|--|

| Pin No.                        | Pin name | I/O | Description                                       | Equivalent Circuit  |  |  |  |  |

| 11                             | VBIAS    | 0   | Internal regulator decupling capacitor connection | VD<br>\$500Ω<br>GND |  |  |  |  |

|                                |          |     | decupling capacitor connection                    | VD                  |  |  |  |  |

| 13                             | GND      |     | Analog Ground                                     |                     |  |  |  |  |

| 14                             | NC       |     | Non connection                                    |                     |  |  |  |  |

| 15                             | NC       |     | Non connection                                    |                     |  |  |  |  |

| 16                             | NC       |     | Non connection                                    |                     |  |  |  |  |

| 17                             | NC       |     | Non connection                                    |                     |  |  |  |  |

| 18                             | NC       |     | Non connection                                    |                     |  |  |  |  |

| 19                             | NC       |     | Non connection                                    |                     |  |  |  |  |

| 20                             | NC       |     | Non connection                                    |                     |  |  |  |  |

| 21                             | NC       |     | Non connection                                    |                     |  |  |  |  |

| 22                             | NC       |     | Non connection                                    |                     |  |  |  |  |

| 23                             | PVD2     |     | CH2 power supply                                  |                     |  |  |  |  |

| 24                             | PVD2     |     | CH2 power supply                                  |                     |  |  |  |  |

| 25                             | OUT2+    | 0   | Output pin, CH2 plus                              | VD                  |  |  |  |  |

| 26                             | OUT2+    | 0   | Output pin, CH2 plus                              | VD (26)             |  |  |  |  |

# LV49152V

Continued from preceding page.

| Continued from preceding page. |                   |     |                                                       |                                         |  |  |  |

|--------------------------------|-------------------|-----|-------------------------------------------------------|-----------------------------------------|--|--|--|

| Pin No.                        | Pin name          | I/O | Description                                           | Equivalent Circuit                      |  |  |  |

| 27                             | BOOT2+            | I/O | Boot strap pin, CH2 plus                              |                                         |  |  |  |

| 28                             | V <sub>DD</sub> 2 | 0   | CH2 internal regulator decupling capacitor connection |                                         |  |  |  |

| 29                             | BOOT2-            | I/O | Boot strap pin, CH2 minus                             |                                         |  |  |  |

| 30                             | OUT2 <sup>-</sup> | 0   | Output pin, CH2 minus                                 | VD 30 GND                               |  |  |  |

| 31                             | OUT2              | 0   | Output pin, CH2 minus                                 | VD ———————————————————————————————————— |  |  |  |

| 32                             | PGND2             |     | CH2 Power Ground                                      |                                         |  |  |  |

| 33                             | PGND2             |     | CH2 Power Ground                                      |                                         |  |  |  |

| 34                             | PGND1             |     | CH1 Power Ground                                      |                                         |  |  |  |

| 35                             | PGND1             |     | CH1 Power Ground                                      |                                         |  |  |  |

| 36                             | OUT1 <sup>-</sup> | 0   | Output pin, CH1 minus                                 | VD ———————————————————————————————————— |  |  |  |

| 37                             | OUT1              | 0   | Output pin, CH1 minus                                 | VD ———————————————————————————————————— |  |  |  |

| 38                             | BOOT1             | I/O | Boot strap pin, CH1 minus                             |                                         |  |  |  |

| 39                             | V <sub>DD</sub> 1 | 0   | CH1 internal regulator decupling capacitor connection |                                         |  |  |  |

| 40                             | BOOT1+            | I/O | Boot strap pin, CH1 plus                              |                                         |  |  |  |

|                                |                   | •   |                                                       |                                         |  |  |  |

# LV49152V

Continued from preceding page.

| Pin No. | Pin name | I/O | Description          | Equivalent Circuit                      |

|---------|----------|-----|----------------------|-----------------------------------------|

| 41      | OUT1+    | 0   | Output pin, CH1 plus | VD ———————————————————————————————————— |

| 42      | OUT1+    | O   | Output pin, CH1 plus | VD ———————————————————————————————————— |

| 43      | PVD1     |     | CH1 power supply     |                                         |

| 44      | PVD1     |     | CH1 power supply     |                                         |

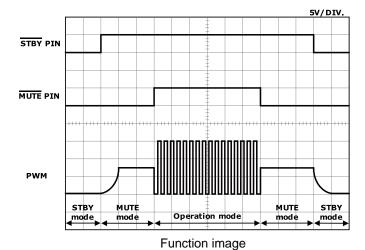

#### **Operation Mode Summary**

#### STBY mode ( $\overline{STBY} = L$ and $\overline{MUTE} = L$ )

Each bias becomes off state when the regulator in IC has been turned off.

The most of circuits becomes off state.

The supply current :  $1\mu A$  (typical).

#### MUTE mode ( $\overline{STBY} = H$ and $\overline{MUTE} = L$ )

Each bias becomes on state when the regulator in IC has been turned on.

When more than half of the circuits are active, the amplifier in the output stages become off.

The supply current: 20mA (typical).

#### Operation mode ( $\overline{STBY} = H$ and $\overline{MUTE} = H$ )

The LV49152V operates as D-class amplifier.

The output signal is synchronized with the input signal.

The supply current: 45mA (typical)

No.A1408-12/24

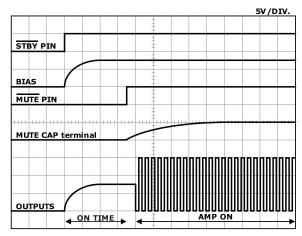

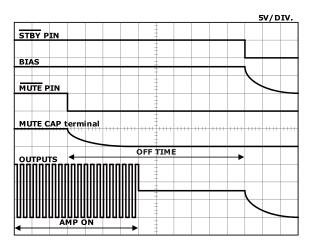

#### ON TIME/OFF TIME

#### ON TIME

Please secure ON TIME of 350msec or more for reducing Pop noise.

Function image

ON TIME ••• the time until the  $\overline{\text{MUTE}}$  pin is set to high level after the  $\overline{\text{STBY}}$  pin is set to high level

#### **OFF TIME**

Please secure OFF TIME of 1000msec or more for reducing Pop noise.

Function image

OFF TIME ••• the time until the STBY pin is set to low level after the MUTE pin is set to low level

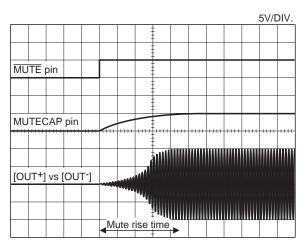

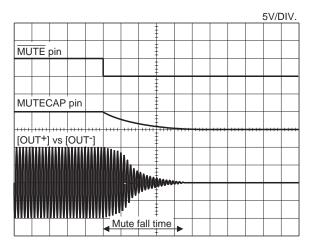

#### **SOFT MUTE**

The soft mute circuit is able to use fade in/fade out function, and can set Rise time and fall time by the time constant of the MUTECAP capacitor.

#### FADE IN

Mute rise time is Applpx.450msec in our recommended external components.

Function image

#### **FADE OUT**

Mute fall time is Applpx.450msec in our recommended external components.

Function image

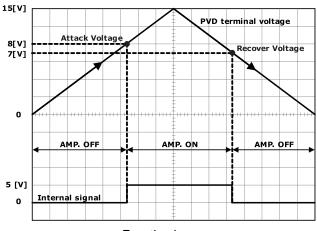

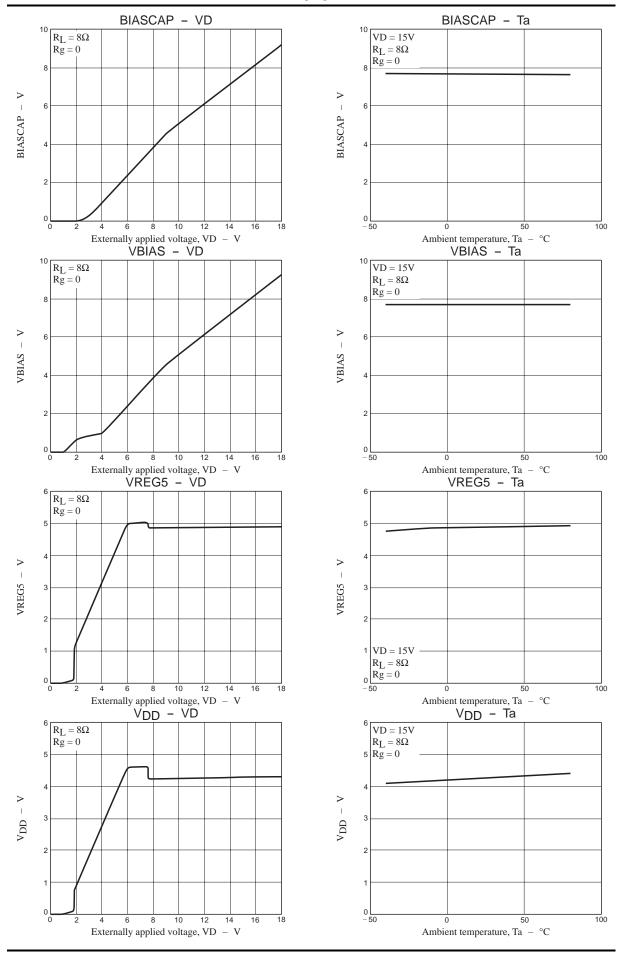

#### Power supply lowering protection circuit

Since the instable operation in the low voltage is prevented by using this circuit, after the voltage of the PVD pin is monitored and the voltage below the Attack voltage (PVD = 8V typ.), AMP is turned off.

Also, to prevent the instable operation when the voltage of the PVD pin is decreased by any cause during operations, the Attack voltage (PVD = 7V typ.) is set.

The voltage of Attack and Recover has hysteresis (About 1V) to prevent ON/OFF continuous action of the power supply lowering protection circuit.

Function image

Also, this IC is designed to turn off AMP in the same sequence that the MUTE is on as a pop noise measures when the plug of products are put off.

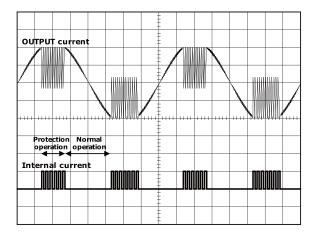

#### Over current protection circuit

The over current protection circuit is a protection circuit \* to protect the output DMOS from the over current and corresponds to any mode of the power supply, GND and a load short.

The protection operation is performed when the current reaches the detection current value set out in IC and the output DMOS is compulsorily turned off for about  $20\mu sec$ .

After compulsorily tuning off the output DMOS, when the Amplifier is automatically reset in usual operation and the over current flows continuously, the protection operation is performed again.

Function image

<sup>\*</sup> The over current protection circuit is a function to avoid the abnormal state like the output short-circuit temporarily. Unfortunately, we cannot guarantee that IC is not destroyed.

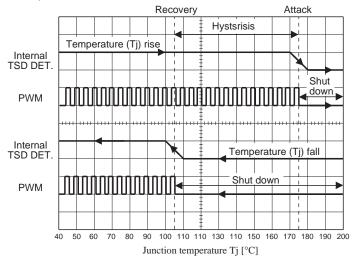

#### Thermal protection circuit

The LV49152V includes a thermal protection circuit to prevent damage to or destruction of the IC should abnormal internal heat generation occur.

This means that should the IC junction temperature (Tj) rise above about 175°C due to inadequate heat dissipation or other reason, the thermal protection circuit will operate to stop IC operation should the temperature rise further. If the temperature is reduced by lowering the input level or other means, the thermal protection circuit will recover automatically (about 105°C).

Function image

<sup>\*</sup> The thermal protection circuit is a function to avoid the abnormal state temporarily. Unfortunately, we cannot guarantee that IC is not destroyed.

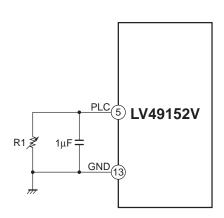

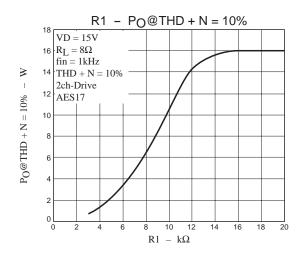

#### **PLC**

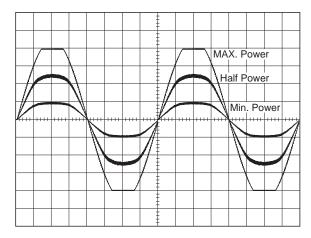

The PLC (power level control) function is able to control the maximum index modulation by setting a value of external PLC resistance R1 voluntarily, and prevent a PWM signal from becoming the over modulation mode. In addition, this circuit can be use as output power limit circuit because the PLC function can set the maximum index modulation voluntarily, and variable from 2W to 15W with output power linearly in the state that made the power supply voltage and load resistance fixation. Because the PLC function can set the suitable rated output with the same power supply voltage/speaker regardless of screen size in flat screen televisions by this, set can plan the commonization of the board.

Furthermore, The PLC function can reduce abnormal noise in the hard clip so that output wave pattern becomes the soft clip when it limited output power.

Function image

#### Measuring condition

VD = 15V,  $R_L = 8\Omega$ ,  $L = 33\mu H$  (TOKO : A7502BY-330M), C = 0.1 uF,  $C_L = 0.47 \mu F$ , Ta = 25 °C

| R1 [kΩ] | Po@10% [W] |

|---------|------------|

| 3.0     | 0.694      |

| 3.6     | 1.073      |

| 4.7     | 1.982      |

| 6.2     | 3.642      |

| 7.5     | 5.562      |

| 8.2     | 6.855      |

| 9.1     | 8.591      |

| 10      | 10.64      |

| 13      | 15.32      |

| 15      | 15.94      |

| 20      | 16.01      |

| ·       | ·          |

Setting example of the output power limit value

- \* When it is used this function as output power limit, please use the high-precision resistance such as the metal film resistor when precision of the electricity value is necessary.

- \* The value of external PLC resistance R1 please connects more than  $3k\Omega$ .

- \* When it is changed a value of external PLC resistance R1, please turn off an amplifier.

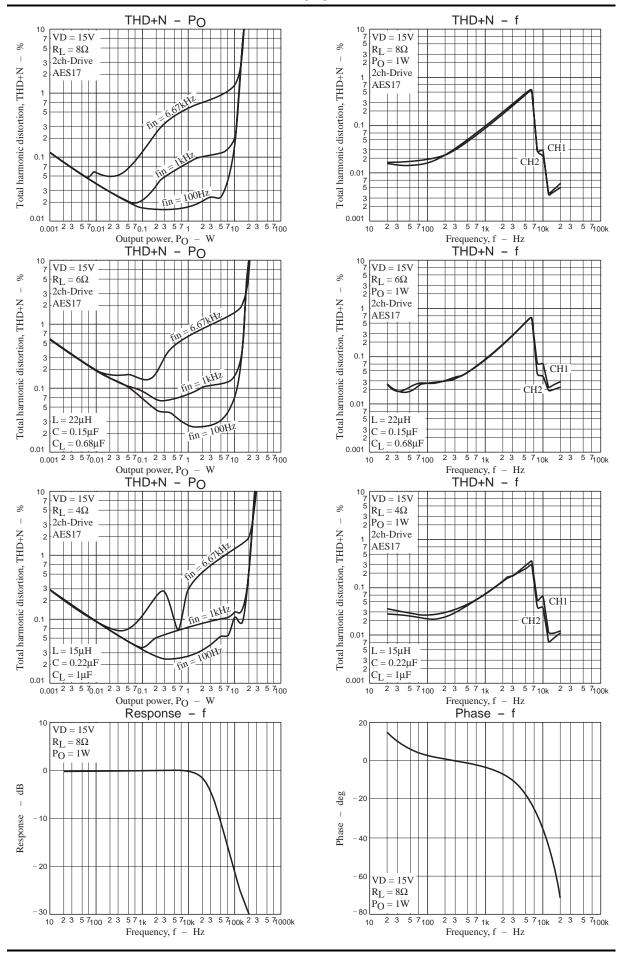

#### Cut-off frequency calculation method and the output LC filter setting

The cut off frequency fc of the output LC filter is calculated by the following formula.

$$fc = \frac{1}{2\pi\sqrt{2LC_L}}$$

Also, by setting the cut off frequency fc, the value of CL and L is calculated by using the following formula.

$$C_L = \frac{1}{2\sqrt{2} \times \pi \ R_L fc}$$

$$L = \frac{\sqrt{2} \times R_L}{4\pi \text{ fc}}$$

In general, the value from 20% to 30% of  $C_L$  is set to C.

In case of fc = 30kHz

| $R_L\left[\Omega ight]$ | L [μH] | C <sub>L</sub> [μF] | C [μF] | Q     |

|-------------------------|--------|---------------------|--------|-------|

| 4                       | 15     | 1                   | 0.22   | 0.650 |

| 6                       | 22     | 0.68                | 0.15   | 0.636 |

| 8                       | 33     | 0.47                | 0.1    | 0.704 |

| 16                      | 68     | 0.22                | 0.047  | 0.739 |

Above formula is common calculation method and is a measure of constant setting. In fact, it is necessary to set with each set that considers the speaker characteristics.

In addition, please set the fixed number to become  $Q \le 1$  in currents in the fc neighborhood increasing if Q value of the LC filter is big.

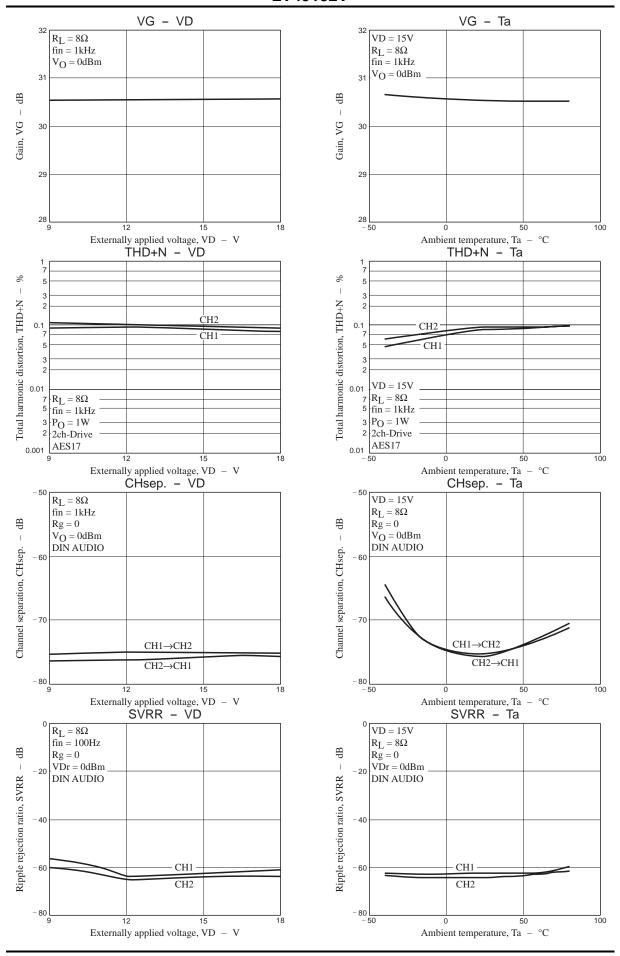

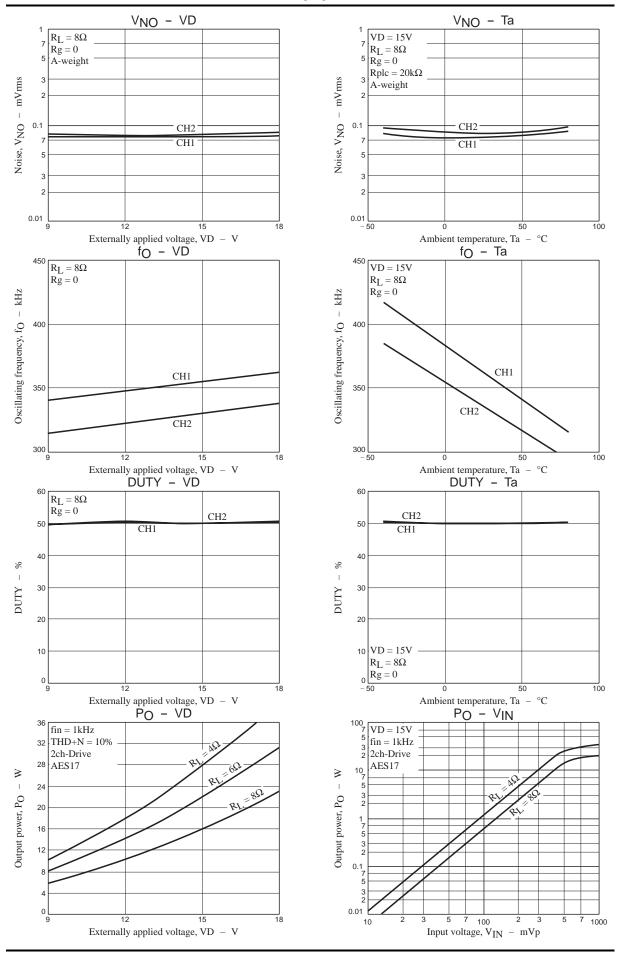

#### Glaph deta

$L = 33\mu H$  (TOKO : A7502BY-330M),  $C = 0.1\mu F$ ,  $C_L = 0.47\mu F$

- SANYO Semiconductor Co.,Ltd. assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein.

- SANYO Semiconductor Co.,Ltd. strives to supply high-quality high-reliability products, however, any and all semiconductor products fail or malfunction with some probability. It is possible that these probabilistic failures or malfunction could give rise to accidents or events that could endanger human lives, trouble that could give rise to smoke or fire, or accidents that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO Semiconductor Co.,Ltd. products described or contained herein are controlled under any of applicable local export control laws and regulations, such products may require the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written consent of SANYO Semiconductor Co.,Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO Semiconductor Co.,Ltd. product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production.

- Upon using the technical information or products described herein, neither warranty nor license shall be granted with regard to intellectual property rights or any other rights of SANYO Semiconductor Co.,Ltd. or any third party. SANYO Semiconductor Co.,Ltd. shall not be liable for any claim or suits with regard to a third party's intellectual property rights which has resulted from the use of the technical information and products mentioned above.

This catalog provides information as of Nobember, 2009. Specifications and information herein are subject to change without notice.