Product information presented is for internal use within AAT Inc. only. Details are subject to change without notice.

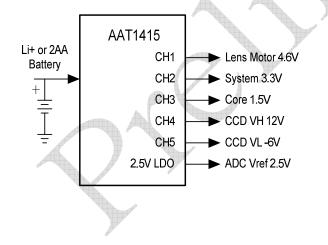

## FIVE-CHANNEL DC-DC CONVERTER WITH A 2.5V LDO

## **FEATURES**

- Complete PWM Power Control Circuitry

- Input Voltage Range: 1.5 to 5.5V

- Low Start-Up Voltage: 1.2V

- Independent On / Off Control for All Channels

- Internal Soft-Start for All Channels

- Power-OK Outputs & Overload Protection

- Adjustable Operation Frequency with External Components Ranging from 100kHz to 1MHz

- VQFN-40 5\*5 Package Available

## **APPLICATIONS**

- Digital Still Cameras

- Digital Videos

- PDAs

- Portable Devices

## **GENERAL DESCRIPTION**

The AAT1415/AAT1415A provides an integrated 5-channel pulse-width-modulation (PWM) solution and a low noise LDO for the power supply of DC-DC converter. This device improves performance and size compared to conventional controllers in battery design. The AAT1415/AAT1415A has three current mode PWM converters (CH1, CH2, and CH3) and two voltage mode PWM converters (CH4 and CH5). Each current-mode channel has on-chip synchronous power FETs. The five channels include:

CH1: Boost /buck selectable DC-DC converter, which activates PWM function at 1.2V when it is configured as a boost converter.

CH2: Boost / buck selectable DC-DC converter.

CH3: Buck DC-DC converter.

CH4: Boost DC-DC controller for the CCD positive bias.

CH5: Inverting DC-DC controller for the CCD negative bias.

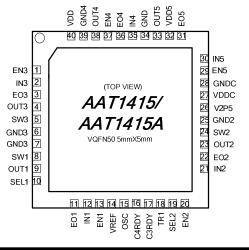

### **PIN CONFIGURATION**

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 3.00

Page 1 of 32

# **ORDERING INFORMATION**

| DEVICE<br>TYPE | PART<br>NUMBER    | PACKAGE            | PACKING             | TEMP.<br>RANGE                       | MARKING                   | MARKING<br>DESCRIPTION                                             |

|----------------|-------------------|--------------------|---------------------|--------------------------------------|---------------------------|--------------------------------------------------------------------|

| AAT1415        | AAT1415<br>-Q8-T  | Q8: VQFN<br>40-5*5 | T: Tape<br>and Reel | –40 $^{\circ}$ C to +85 $^{\circ}$ C | AAT1415<br>XXXXX<br>XXXX  | 1. Part Name<br>2. Lot No. (6~9 Digits)<br>3. Date Code (4 Digits) |

| AAT1415A       | AAT1415A<br>-Q8-T | Q8: VQFN<br>40-5*5 | T: Tape<br>and Reel | –40 °C to +85 °C                     | AAT1415A<br>XXXXX<br>XXXX | 1. Part Name<br>2. Lot No. (6~9 Digits)<br>3. Date Code (4 Digits) |

NOTE: All AAT products are lead free and halogen free.

## **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER                                                             | SYMBOL               | VALUE                | UNIT |

|-----------------------------------------------------------------------|----------------------|----------------------|------|

| Supply Voltage (VDD)                                                  | V <sub>MDD</sub>     | -0.3 to + 6.0        | V    |

| Pin Voltage 1 (OUT1, OUT2, VDDC, C3RDY, C4RDY, VDD5, SEL1, SEL2, TR1) | V <sub>I1</sub>      | -0.3 to + 6.0        | V    |

| Pin Voltage 2 (OUT3, VREF, OSC, EO_, EN_, IN_)                        | V <sub>l2</sub>      | –0.3 to (VDD + 0.3)  | V    |

| Pin Voltage 3 (OUT5)                                                  | V <sub>I3</sub>      | -0.3 to (VDD5+0.3)   | V    |

| Pin Voltage 4 (OUT4)                                                  | V <sub>I4</sub>      | –0.3 to (VDD + 0.3)  | ۷    |

| Pin Voltage 5 (V2P5)                                                  | V <sub>I5</sub>      | -0.3 to (VDDC + 0.3) | ۷    |

| Pin Voltage 6 (GND_)                                                  | V <sub>I6</sub>      | -0.3 to $+0.3$       | ۷    |

| Input Voltage 7 (SW1)                                                 | V <sub>I7</sub>      | –0.3 to (OUT1+0.3V)  | ۷    |

| Input Voltage 8 (SW2)                                                 | V <sub>I8</sub>      | –0.3 to (OUT2+0.3V)  | ٧    |

| Input Voltage 9 (SW3)                                                 | V <sub>I9</sub>      | –0.3 to (OUT3+0.3V)  | ۷    |

| SW1 Current                                                           | I <sub>SW1</sub>     | 3.6                  | А    |

| SW2 Current                                                           | I <sub>SW2</sub>     | 3.6                  | А    |

| SW3 Current                                                           | I <sub>SW3</sub>     | 3.6                  | А    |

| Open Drain NMOS Current (C3RDY, C4RDY)                                | I <sub>OD</sub>      | 10                   | mA   |

| Operating Temperature Range                                           | Т <sub>С</sub>       | -40 ° C to + 85 ° C  | °C   |

| Storage Temperature Range                                             | T <sub>STORAGE</sub> | –65 ° C to + 150 ° C | °C   |

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 3.00

Page 2 of 32

# **RECOMMENDED OPERATING CONDITIONS**

| PARAMETER                      | SYMBOL         | MIN | МАХ | UNIT |

|--------------------------------|----------------|-----|-----|------|

| Operating Free-Air Temperature | Т <sub>С</sub> | -40 | +85 | °C   |

# **ELECTRICAL CHARACTERISTICS**

( $T_{C} = 25 \circ C$ ,  $V_{DD} = OUT1 = OUT2 = OUT3 = 3.6V$ , unless otherwise specified.)

#### **General Item**

| General item                                       |                    |                                              |      | A. I |      |      |

|----------------------------------------------------|--------------------|----------------------------------------------|------|------|------|------|

| PARAMETER                                          | SYMBOL             | TEST CONDITION                               | MIN  | ТҮР  | МАХ  | UNIT |

| Input Voltage Range                                | $V_{VDD}$          |                                              | 2.6  |      | 5.5  | V    |

| VDD Under-Voltage Lockout                          | V <sub>UVLO</sub>  |                                              | 2.35 | 2.40 | 2.45 | V    |

| VDD Under-Voltage Lockout<br>Hysteresis            | V <sub>UHYS</sub>  |                                              |      | 80   |      | mV   |

| CH1 Minimum Startup Voltage                        | V <sub>START</sub> |                                              |      | 1.2  | 1.5  | V    |

| Shutdown Supply Current Into VDD                   | I <sub>SHDN</sub>  |                                              |      | 0.10 | 10.0 | μA   |

| Supply Current Into VDD with CH1<br>Enable         | I <sub>CH1</sub>   | EN1 = 3.6V, IN1 = 1.5V                       |      | 450  | 700  | μA   |

| Supply Current Into VDD with CH2<br>Enable         | I <sub>CH2</sub>   | EN2 = 3.6V, IN2 = 1.5V                       |      | 400  | 650  | μA   |

| Supply Current Into VDD with CH3<br>Enable         | Існз               | EN3 = 3.6V, IN3 = 1.5V                       |      | 400  | 650  | μA   |

| Supply Current Into VDD with CH1<br>And CH4 Enable | І <sub>СН4</sub>   | EN1 = EN4 = 3.6V,<br>IN1 = IN4 = 1.5V        |      | 550  | 800  | μA   |

| Supply Current Into VDD with CH1<br>And CH5 Enable | І <sub>СН5</sub>   | EN1 = EN5 = 3.6V,<br>IN1 = 1.5V, IN5 = -0.5V |      | 550  | 800  | μA   |

| Supply Current Into VDD with CH1<br>And LDO Enable | Існс               | EN1 = 3.6V, IN1 = 1.5V                       |      | 100  | 300  | μA   |

### **Reference Voltage**

| PARAMETER                 | SYMBOL    | TEST CONDITION                     | MIN  | ТҮР  | MAX  | UNIT |

|---------------------------|-----------|------------------------------------|------|------|------|------|

| Reference Output Voltage  | $V_{REF}$ | I <sub>REF</sub> = 20 μ Α          | 1.23 | 1.25 | 1.27 | V    |

| Reference Load Regulation |           | 10 µ A < I <sub>REF</sub> <200 µ A |      | 4.50 | 10.0 | %/mV |

| Reference Line Regulation |           | 2.7V< V <sub>DD</sub> <5.5V        |      | 1.3  | 5.0  | %/mA |

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. -

Version 3.00

Page 3 of 32

## **ELECTRICAL CHARACTERISTICS**

(  $T_{C}$  = 25 °C ,  $V_{DD}$  = OUT1 = OUT2 = OUT3 = 3.6V, unless otherwise specified.)

#### Oscillator

| PARAMETER                 | SYMBOL           | TEST CONDITION                                       | MIN   | ТҮР   | МАХ   | UNIT |

|---------------------------|------------------|------------------------------------------------------|-------|-------|-------|------|

| OSC Discharge Trip Level  | V <sub>ODT</sub> | Rising Edge                                          | 1.225 | 1.250 | 1.275 | V    |

| OSC Discharge Resistance  | R <sub>ODR</sub> | $OSC = 1.5V, I_{OSC} = 30mA$                         |       | 52    | 80    | Ω    |

| OSC Discharge Pulse Width | t <sub>OFF</sub> |                                                      |       | 150   |       | ns   |

| OSC Frequency             | f <sub>osc</sub> | R <sub>OSC</sub> = 47kΩ,<br>C <sub>OSC</sub> = 100pF |       | 500   | , 0   | kHz  |

#### **Power Fail Latch and Thermal Protection**

| PARAMETER                       | SYMBOL            | TEST CONDITION                        | MIN   | ТҮР     | МАХ   | UNIT   |

|---------------------------------|-------------------|---------------------------------------|-------|---------|-------|--------|

| CH4, CH5 Overload Condition     |                   | Duty Cycle                            |       | 100     |       | %      |

| CH1, CH2 Overload Threshold     | V <sub>F12</sub>  | IN1, IN2, Fail Detection<br>Voltage   | 1.07  | 1.10    | 1.13  | V      |

| CH3 Overload Threshold          | N/                | IN3 Fail Detection Voltage (AAT1415)  | 1.07  | 1.10    | 1.13  | V      |

| CHS Ovendad Threshold           | V <sub>F13</sub>  | IN3 Fail Detection Voltage (AAT1415A) | 0.600 | 0.625   | 0.650 | V      |

| Overload Protection Fault Delay | • A               |                                       |       | 100,000 |       | Cycles |

| Thermal Shutdown                | T <sub>SHDN</sub> |                                       |       | 160     |       | °C     |

| Thermal Hysteresis              | T <sub>HYS</sub>  |                                       |       | 20      |       | °C     |

### Logic Inputs

| PARAMETER                  | SYMBOL           | TEST CONDITION | MIN | ТҮР | MAX | UNIT |

|----------------------------|------------------|----------------|-----|-----|-----|------|

| EN_, SEL_ Input Low Level  | V <sub>IL</sub>  |                |     |     | 0.4 | V    |

| EN_, SEL_ Input High Level | V <sub>IH</sub>  |                | 1.4 |     |     | V    |

| SEL_ Input Leakage         | I <sub>L9</sub>  |                |     | 0.1 | 1.0 | μA   |

| EN_ Impedance to GND       | R <sub>EN</sub>  |                | 200 | 300 | 400 | kΩ   |

| TR1 Output Low Voltage     | V <sub>TRL</sub> | 1.2mA Into TR1 |     | 0.1 | 0.2 | V    |

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 3.00

Page 4 of 32

## **ELECTRICAL CHARACTERISTICS**

(  $T_{C}$  = 25 °C ,  $V_{DD}$  = OUT1 = OUT2 = OUT3 = 3.6V, unless otherwise specified.)

### CH1 (Boost / Buck)

| PARAMETER                                      | SYMBOL                 | TEST CONDITION                                   | MIN   | ТҮР       | МАХ   | UNIT          |

|------------------------------------------------|------------------------|--------------------------------------------------|-------|-----------|-------|---------------|

| IN1 Regulation Voltage                         | V <sub>IN1</sub>       | IN1 = EO1                                        | 1.231 | 1.250     | 1.269 | V             |

| IN1 to EO1 Transconductance                    |                        | IN1 = EO1                                        |       | 70        |       | μS            |

| CH1 Maximum Duty Cycle                         |                        | Boost Mode (SEL1 = $V_{DD}$ )                    | 85    | 90        | 95    | %             |

|                                                |                        | Buck Mode (SEL1 = GND)                           |       | 100       | •     | %             |

| IN1 Input Leakage Current                      | l <sub>L1</sub>        | IN1 = 0V to 1.5V                                 | -100  | 0.01      | +100  | nA            |

| Current-Sense Amplifier                        |                        | Boost Mode (SEL1 = V <sub>DD</sub> )             | Þ     | 0.25      |       | V/A           |

| Transresistance                                |                        | Buck Mode (SEL1 = GND)                           |       | 0.5       |       | V/A           |

| OUT1 Leakage Current                           | I <sub>LO1</sub>       | SEL1 = GND<br>V <sub>SW1</sub> = 0V, OUT1 = 3.6V |       | 0.1       | 5.0   | μA            |

| SW1 Leakage Current                            | I <sub>LSW1</sub>      | SEL1 = GND<br>V <sub>SW1</sub> = OUT1 = 3.6V     |       | 0.1       | 5.0   | μA            |

| Switch On-Resistance                           | R <sub>ON1(N)</sub>    | N Channel                                        |       | 0.1<br>95 |       | mΩ            |

| Switch On-nesistance                           | R <sub>ON1(P)</sub>    | P Channel                                        |       | 200       |       | 111 52        |

| SW1 Peak Current Limit                         | LIMIT1(N)              | Boost Mode (SEL1 = V <sub>DD</sub> )             |       | 3         |       | А             |

|                                                | I <sub>LIMIT1(P)</sub> | Buck Mode (SEL1 = GND)                           |       | 0.8       |       | А             |

| Soft-Start Interval                            |                        |                                                  |       | 4,096     |       | OSC<br>Cycles |

| OUT1 Startup-to-Normal<br>Operating Threshold  | V <sub>UVLO1</sub>     | Rising Edge                                      | 2.30  | 2.50      | 2.65  | V             |

| OUT1 Startup-to-Normal<br>Operating Hysteresis | V <sub>UHYS1</sub>     |                                                  |       | 80        |       | mV            |

| Startup t <sub>OFF</sub>                       | t <sub>os</sub>        | V <sub>DD</sub> = 1.8V                           |       | 700       |       | ns            |

| Startup Frequency                              | f <sub>start</sub>     | V <sub>DD</sub> = 1.8V                           |       | 200       |       | kHz           |

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 3.00

Page 5 of 32

## **ELECTRICAL CHARACTERISTICS**

(  $T_{C}$  = 25 °C ,  $V_{DD}$  = OUT2 = 3.6V, unless otherwise specified.)

### CH2 (Boost / Buck)

| PARAMETER                                   | SYMBOL                 | TEST CONDITION                       | MIN   | ТҮР   | МАХ   | UNIT          |

|---------------------------------------------|------------------------|--------------------------------------|-------|-------|-------|---------------|

| IN2 Regulation Voltage                      | V <sub>IN2</sub>       | IN2 = EO2                            | 1.231 | 1.250 | 1.269 | V             |

| IN2 to EO2 Transconductance                 |                        | IN2 = EO2                            |       | 70    |       | μS            |

| CH2 Maximum Duty Cycle                      |                        | Boost Mode (SEL2 = $V_{DD}$ )        | 85    | 90    | 95    | %             |

| CH2 Maximum Duty Cycle                      |                        | Buck Mode (SEL2 = GND)               |       | 100   |       | %             |

| IN2 Input Leakage Current                   | I <sub>L2</sub>        | IN2 = 0V to 1.5V                     | -100  | 0.01  | +100  | nA            |

| Current-Sense Amplifier                     |                        | Boost Mode (SEL2 = V <sub>DD</sub> ) |       | 0.25  |       | V/A           |

| Transresistance                             |                        | Buck Mode (SEL2 = GND)               |       | 0.5   |       | V/A           |

| OUT2 Leakage Current                        | I <sub>LO2</sub>       | V <sub>SW2</sub> = 0V, OUT2 = 3.6V   |       | 0.1   | 5.0   | μA            |

| SW2 Leakage Current                         | I <sub>LSW2</sub>      | V <sub>SW2</sub> = OUT2 = 3.6V       |       | 0.1   | 5.0   | μA            |

| Switch On-Resistance                        | R <sub>ON2(N)</sub>    | N Channel                            |       | 95    |       |               |

| Switch On-Resistance                        | R <sub>ON2(P)</sub>    | P Channel                            |       | 150   |       | mΩ            |

|                                             | I <sub>LIMIT2(N)</sub> | Boost Mode (SEL2 = V <sub>DD</sub> ) |       | 3     |       | А             |

| SW2 Peak Current Limit                      | I <sub>LIMIT2(P)</sub> | Buck Mode (SEL2 = GND)               |       | 0.8   |       | А             |

| Soft-Start Interval                         |                        |                                      |       | 4,096 |       | OSC<br>Cycles |

| OUT2 Under-Voltage Lockout in<br>Buck Mode  | V <sub>UVLO2</sub>     | SEL2 = GND                           | 2.45  | 2.50  | 2.55  | V             |

| OUT2 Under-Voltage Lockout in<br>Hysteresis | V <sub>UHYS2</sub>     |                                      |       | 80    |       | mV            |

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 3.00

Page 6 of 32

## **ELECTRICAL CHARACTERISTICS**

(  $T_{\rm C}$  = 25 °C ,  $V_{DD}$  = OUT3 = 3.6V, unless otherwise specified.)

#### CH3 (Buck)

| PARAMETER                                  | SYMBOL              | TEST CONDITION                | MIN   | ТҮР   | МАХ   | UNIT          |

|--------------------------------------------|---------------------|-------------------------------|-------|-------|-------|---------------|

| IN2 Degulation Voltage                     | Maria               | IN3 = EO3 (AAT1415)           | 1.231 | 1.250 | 1.269 | V             |

| IN3 Regulation Voltage                     | V <sub>IN3</sub>    | IN3 = EO3 (AAT1415A)          | 0.784 | 0.800 | 0.816 | v             |

| IN3 to EO3 Transconductance                |                     | IN3 = EO3                     |       | 70    |       | μS            |

| CH3 Maximum Duty Cycle                     |                     |                               |       | 100   | Ø     | %             |

| IN3 Input Leakage Current                  | I <sub>L3</sub>     | IN3 = 0V to 1.5V              | -100  | 0.01  | +100  | nA            |

| Current-Sense Amplifier<br>Transresistance |                     |                               |       | 0.5   |       | V/A           |

| SW3 Leakage Current                        | I <sub>LSW3</sub>   | V <sub>SW3</sub> = 0V to 3.6V |       | 0.1   | 5.0   | μA            |

| Switch On-Resistance                       | R <sub>ON3(N)</sub> | N Channel                     | Y     | 95    |       | mΩ            |

| Switch On-Resistance                       | R <sub>ON3(P)</sub> | P Channel                     |       | 150   |       | 111.22        |

| SW3 Current Limit                          | I <sub>LIMIT3</sub> |                               |       | 0.8   |       | А             |

| Soft-Start Interval                        |                     |                               |       | 4,096 |       | OSC<br>Cycles |

| SW3 Peak Current Limit                     | LIMIT3(N)           |                               |       | 0.8   |       | А             |

| Soft-Start Interval                        |                     |                               |       | 2,048 |       | OSC<br>Cycles |

| C3RDY Output Low Voltage                   | V <sub>C3RDY</sub>  | 0.1mA Into C3RDY              |       | 0.01  | 0.10  | V             |

| C3RDY Leakage Current                      | I <sub>C3RDY</sub>  | EN3 = GND                     |       | 0.01  | 1.00  | μA            |

|                                            |                     |                               |       |       |       |               |

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 3.00

Page 7 of 32

## **ELECTRICAL CHARACTERISTICS**

(  $T_{\rm C}$  = 25 °C ,  $V_{DD}$  = OUT3 = 3.6V, unless otherwise specified.)

#### CH4 (Buck)

| PARAMETER                   | SYMBOL              | TEST CONDITION            | MIN   | ТҮР   | МАХ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | UNIT          |

|-----------------------------|---------------------|---------------------------|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| IN4 Regulation Voltage      | V <sub>IN4</sub>    | IN4 = EO4                 | 1.231 | 1.250 | 1.269                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V             |

| IN4 to EO4 Transconductance |                     | IN4 = EO4                 |       | 70    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | μS            |

| CH4 Maximum Duty Cycle      |                     | IN4 = 0V                  | 85    | 90    | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | %             |

| IN4 Input Leakage Current   | $I_{L4}$            | IN4 = 0V to 1.5V          | -100  | 0.01  | +100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | nA            |

| OUT4 Driver Resistance      | R <sub>ON4(N)</sub> | l <sub>OUT4</sub> = 10mA  | ( )   | 5     | and the second se | Ω             |

| OUT4 Driver Resistance      | R <sub>ON4(P)</sub> | I <sub>OUT4</sub> = -10mA |       | 5     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Ω             |

| Soft-Start Interval         |                     |                           |       | 4,096 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | OSC<br>Cycles |

| C4RDY Output Low Voltage    | $V_{C4RDY}$         | 0.1mA Into C4RDY          |       | 0.01  | 0.10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V             |

| C4RDY Leakage Current       | I <sub>C4RDY</sub>  | EN4 = GND                 |       | 0.01  | 1.00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | μA            |

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 3.00

Page 8 of 32

## **ELECTRICAL CHARACTERISTICS**

(  $T_{C}$  = 25 °C ,  $V_{DD}$  = OUT1 = 3.6V, unless otherwise specified.)

#### CH5

| PARAMETER                                | SYMBOL              | TEST CONDITION            | MIN   | ТҮР   | МАХ   | UNIT          |

|------------------------------------------|---------------------|---------------------------|-------|-------|-------|---------------|

| IN5 Regulation Voltage                   | V <sub>IN5</sub>    |                           | -0.01 | 0.00  | +0.01 | V             |

| IN5 to EO5 Transconductance              |                     |                           |       | 70    |       | μS            |

| Maximum Duty Cycle                       |                     | IN5 = 0V                  | 85    | 90    | 95    | %             |

| IN5 Input Leakage Current                | $I_{L5}$            | IN5 = 0V to 0.5V          | -100  | 0.1   | +100  | nA            |

| OUT5 Driver Resistance                   | R <sub>ON5(N)</sub> | I <sub>OUT5</sub> = 10mA  | ( )   | 5     |       | Ω             |

| OUTS Driver Resistance                   | R <sub>ON5(P)</sub> | I <sub>OUT5</sub> = -10mA |       | 5     |       | Ω             |

| Soft-Start Interval                      |                     |                           |       | 4,096 |       | OSC<br>Cycles |

| VDD5 Under-Voltage Lockout<br>Threshold  | V <sub>UVLO5</sub>  | Rising Edge               | 2.30  | 2.50  | 2.65  | V             |

| VDD5 Under-Voltage Lockout<br>Hysteresis | V <sub>UHYS5</sub>  |                           |       | 80    |       | mV            |

# **ELECTRICAL CHARACTERISTICS**

(  $T_{C}$  = 25 °C ,  $V_{DD}$  = VDDC = 3.6V, unless otherwise specified.)

#### 2.5V LDO

| 2.3V LDO                      |                     |                                                              |      |      |      |      |

|-------------------------------|---------------------|--------------------------------------------------------------|------|------|------|------|

| PARAMETER                     | SYMBOL              | TEST CONDITION                                               | MIN  | ТҮР  | МАХ  | UNIT |

| Input Voltage Range           | V <sub>VDDC</sub>   | I <sub>V2P5</sub> = 10mA                                     | 2.6  |      | 5.5  | V    |

| V2P5 Regulation Voltage       | V <sub>V2P5</sub>   | I <sub>V2P5</sub> = 10mA                                     | 2.45 | 2.50 | 2.55 | V    |

| V2P5 Dropout Voltage          | V <sub>DROP25</sub> | I <sub>V2P5</sub> = 10mA                                     |      |      | 50   | mV   |

| V2P5 LDO Output Current       | V <sub>V2P5</sub>   |                                                              | 100  |      |      | mA   |

| V2P5 LDO Output Current Limit | I <sub>LIMC25</sub> |                                                              |      | 150  |      | mA   |

| V2P5 VDDC PSRR                |                     |                                                              |      | 60   |      | dB   |

| V2P5 Line Regulation          |                     | Measure V <sub>V2P5</sub><br>V <sub>VDDC</sub> = 2.6V ~ 5V   |      |      | 10   | %/mV |

| V2P5 Load Regulation          |                     | Measure V <sub>V2P5</sub><br>I <sub>V2P5</sub> = 5mA ~ 100mA |      |      | 5    | %/mA |

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. -

Version 3.00

Page 9 of 32

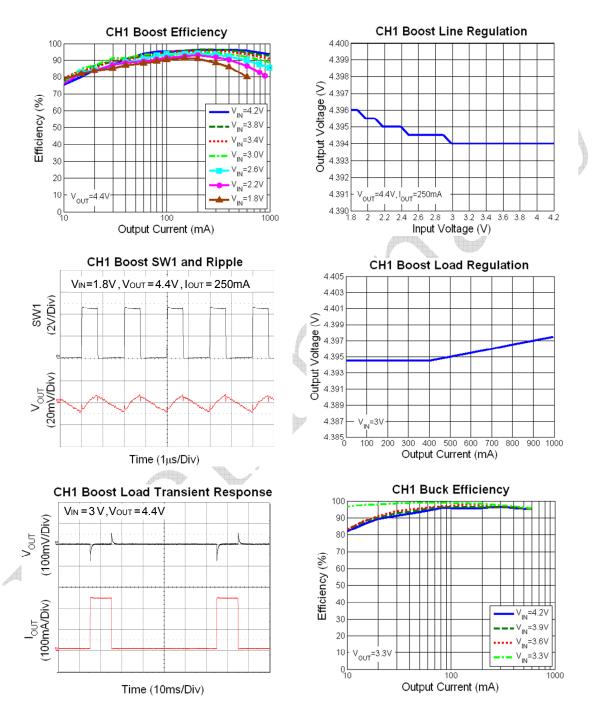

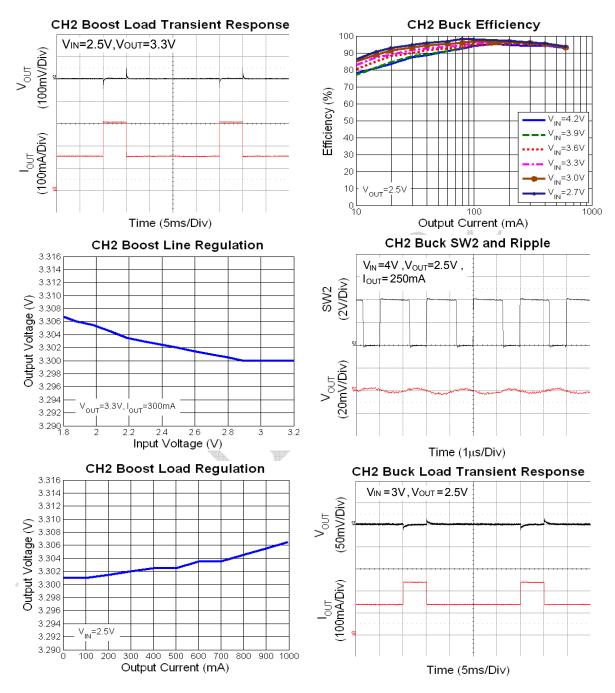

# **TYPICAL OPERATING CHARACTERISTICS**

- 台灣類比科技股份有限公司 -

- Advanced Analog Technology, Inc. -

Version 3.00

Page 10 of 32

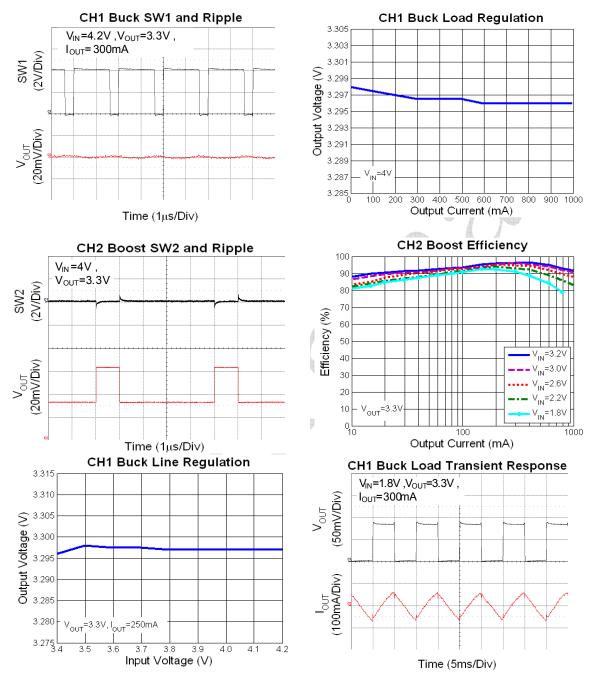

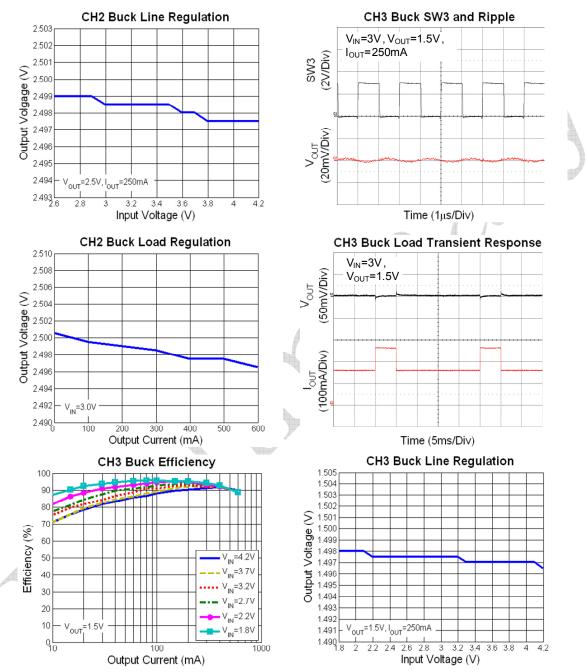

# **TYPICAL OPERATING CHARACTERISTICS**

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 3.00

Page 11 of 32

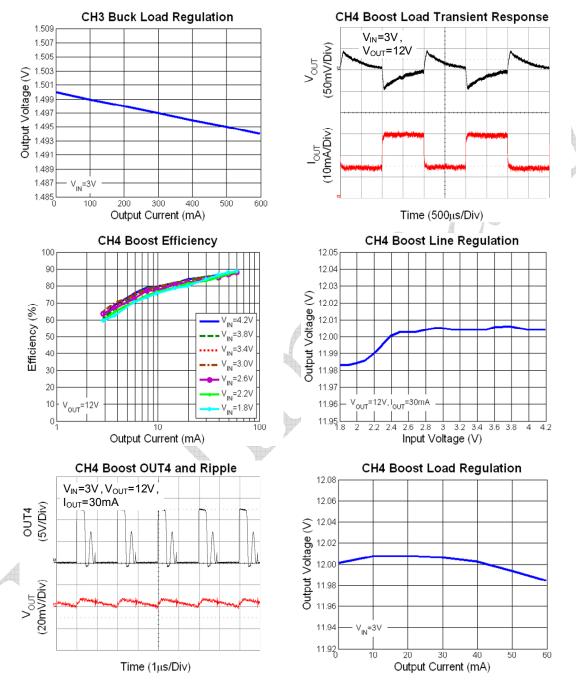

# **TYPICAL OPERATING CHARACTERISTICS**

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 3.00

Page 12 of 32

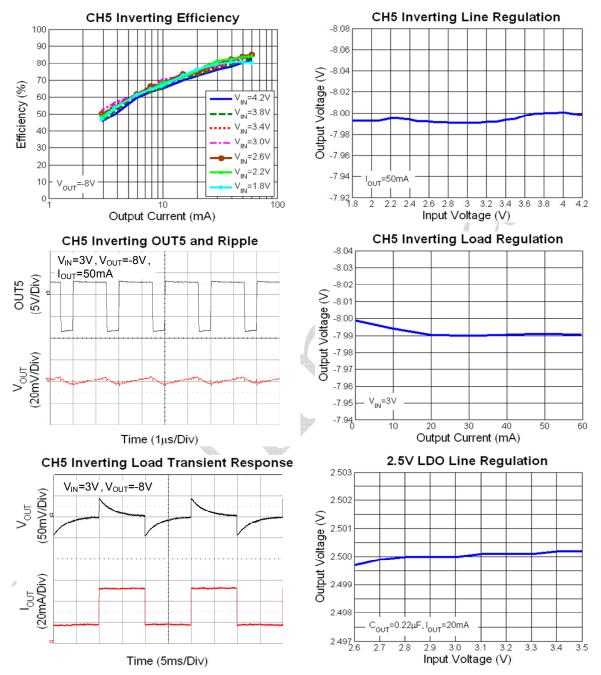

# **TYPICAL OPERATING CHARACTERISTICS**

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 3.00

Page 13 of 32

May 2008

### AAT1415/AAT1415A

# **TYPICAL OPERATING CHARACTERISTICS**

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 3.00

Page 14 of 32

# **TYPICAL OPERATING CHARACTERISTICS**

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 3.00

Page 15 of 32

# **PIN DESCRIPTION**

| PIN NO | NAME  | I/O     | FUNCTION                                             |  |  |

|--------|-------|---------|------------------------------------------------------|--|--|

| 1      | EN3   | I       | ON/OFF Control for CH3                               |  |  |

| 2      | IN3   | I       | CH3 Feedback Input                                   |  |  |

| 3      | EO3   | I/O     | CH3 Compensation Node                                |  |  |

| 4      | OUT3  | I       | CH3 Switching Power Input                            |  |  |

| 5      | SW3   | I/O     | CH3 Switching Node                                   |  |  |

| 6      | GND3  | -       | CH3 Power Ground                                     |  |  |

| 7      | GND1  | -       | CH1 Power Ground                                     |  |  |

| 8      | SW1   | I/O     | CH1 Switching Node                                   |  |  |

| 9      | OUT1  | I/O     | Switching Power Input (Boost) / Output (Buck) of CH1 |  |  |

| 10     | SEL1  | I       | Configures CH1 as a Buck or a Boost Converter        |  |  |

| 11     | EO1   | I/O     | CH1 Compensation Node                                |  |  |

| 12     | IN1   | I       | CH1 Feedback Input                                   |  |  |

| 13     | EN1   | I       | ON/OFF Control for CH1                               |  |  |

| 14     | VREF  | 0       | Reference Output                                     |  |  |

| 15     | OSC   | I/O     | Oscillator Control                                   |  |  |

| 16     | C4RDY | 0       | Power-Ok Signal for CH4                              |  |  |

| 17     | C3RDY | 0       | Power-Ok Signal for CH3                              |  |  |

| 18     | TR1   | 1/0     | CH1 Feedback Resistor Truly Shutdown Input           |  |  |

| 19     | SEL2  | A start | Configures CH2 as a Buck or a Boost Converter        |  |  |

| 20     | EN2   | 1       | ON/OFF Control for CH2                               |  |  |

| 21     | IN2   |         | CH2 Feedback Input                                   |  |  |

| 22     | EO2   | 1/0     | CH2 Compensation Node                                |  |  |

| 23     | OUT2  | I       | CH2 Switching Power Input                            |  |  |

| 24     | SW2   | I/O     | CH2 Switching Node                                   |  |  |

| 25     | GND2  | -       | CH2 Power Ground                                     |  |  |

| 26     | V2P5  | 0       | 2.5V LDO Output                                      |  |  |

| 27     | VDDC  | I       | LDO Power Input                                      |  |  |

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 3.00

Page 16 of 32

Advanced Analog Technology, Inc.

May 2008

## AAT1415/AAT1415A

| 28 | GNDC | -   | LDO Ground                    |

|----|------|-----|-------------------------------|

| 29 | EN5  | Ι   | ON/OFF Control for CH5        |

| 30 | IN5  | Ι   | CH5 Feedback Input            |

| 31 | EO5  | I/O | CH5 Compensation Node         |

| 32 | VDD5 | Ι   | CH5 Power Source              |

| 33 | OUT5 | 0   | CH5 Gate-Drive Output         |

| 34 | GND  | -   | Internal Circuit Ground       |

| 35 | IN4  | Ι   | CH4 Feedback Input            |

| 36 | EO4  | I/O | CH4 Compensation Node         |

| 37 | EN4  | Ι   | ON/OFF Control for CH4        |

| 38 | OUT4 | I/O | CH4 Gate-Drive Output         |

| 39 | GND4 | -   | CH4 Power Ground              |

| 40 | VDD  | Ι   | Internal Circuit Power Source |

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 3.00

Page 17 of 32

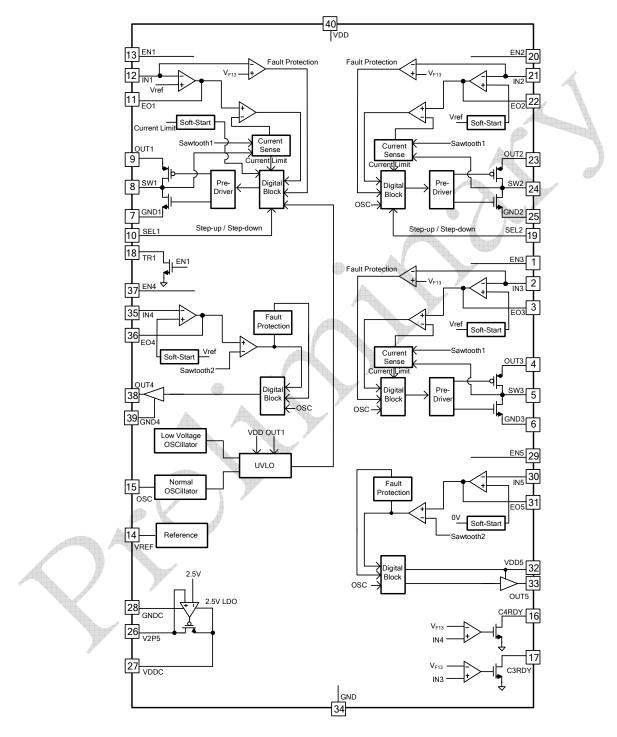

# **FUNCTION BLOCK DIAGRAM**

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. – Version 3.00

Page 18 of 32

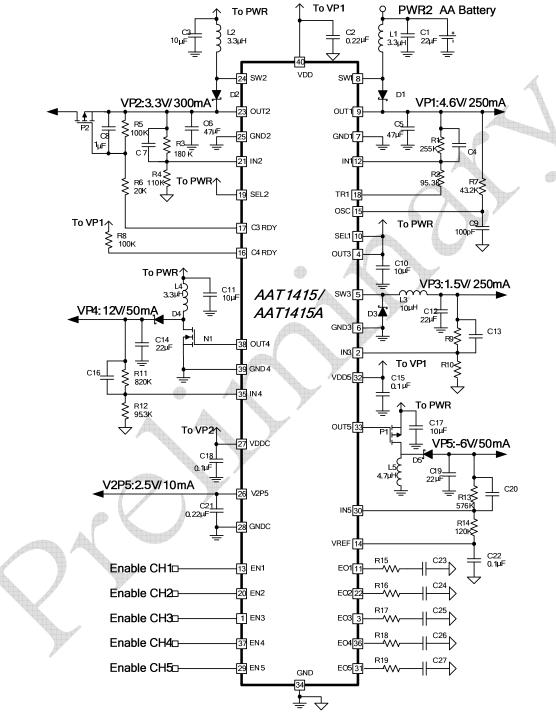

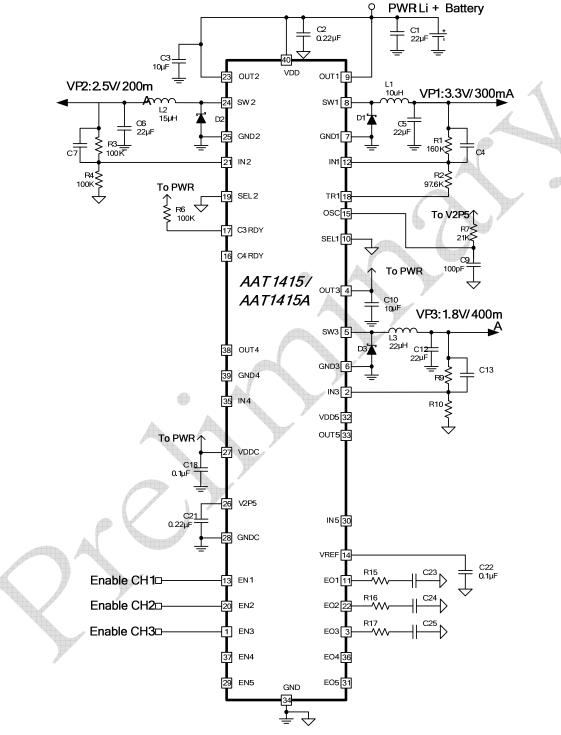

# **TYPICAL APPLICATION CIRCUIT**

Figure 1. Typical 2-Cell AA-Powered System

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. -

Version 3.00

Page 19 of 32

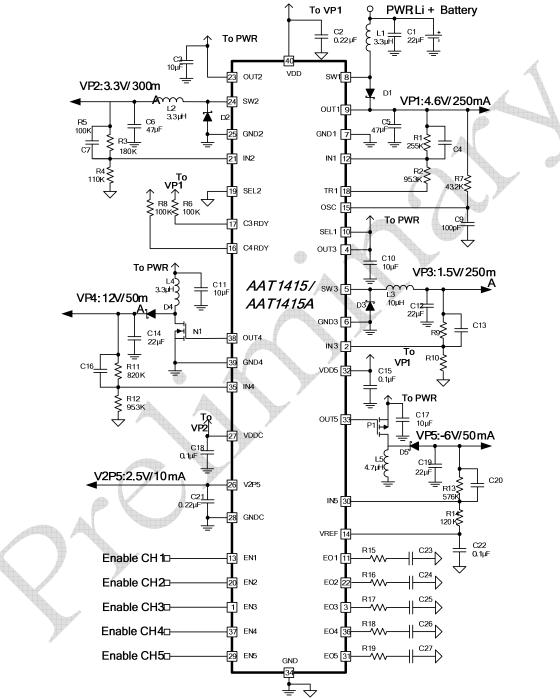

# **TYPICAL APPLICATION CIRCUIT**

- 台灣類比科技股份有限公司

Advanced Analog Technology, Inc.

Version 3.00

Page 20 of 32

# **TYPICAL APPLICATION CIRCUIT**

- 台灣類比科技股份有限公司 –

Advanced Analog Technology, Inc. –

Version 3.00

Page 21 of 32

## **DETAILED DESCRIPTION**

The AAT1415/AAT1415A is a complete power-conversion IC for digital still cameras. It can accept input from a variety of sources, including single-cell Li+ batteries and 2-cell alkaline or NiMH batteries. The AAT1415/AAT1415A includes five DC-DC converter channels and a 2.5V LDO to generate all required voltages:

- Synchronous-rectified boost or buck DC-DC converter with on-chip MOSFETs—Typically supplies 4.6V for lens motor or 3.3V for main system power.

- Synchronous-rectified boost or Buck DC-DC converter with on-chip MOSFETs— Typically supplies 3.3V for main system power or 2.5V for DDR.

- Synchronous-rectified buck DC-DC converter with on-chip MOSFETs— Typically supplies 1.5V for the DSP core.

- Boost controller— Typically used for positive voltage to bias one or more of the LCD, CCD, and LED backlights.

- Inverter controller— Typically supplies negative CCD bias when high current is needed for large pixel-count CCDs.

- 2.5V LDO— Typically supplies 2.5V for analog-to-digital converter's reference voltage. The AAT1415/AAT1415A includes three versatile status outputs that can provide information to the system. All are open-drain outputs and can directly drive MOSFET switches to facilitate sequencing, disconnect loads during overloads, or perform other hardware-based functions.

#### TR1

TR1 pulls low when EN1 pulls high. A typical use for TR1 is to reduce CH1 boost feedback network's leakage current when CH1 is disabled (Figure 1).

### AAT1415/AAT1415A

#### C3RDY

C3RDY pulls low when IN3 reaches  $V_{F13}$  (1.1V typ). C3RDY goes high impedance in shutdown, overload, and thermal limit when IN3 is under  $V_{F13}$ . A typical use for C3RDY is to enable 3.3V power to the CPU I/O after the CPU core is powered up (Figure 1), thus providing safe sequencing in hardware without system intervention.

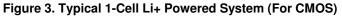

### C4RDY

C4RDY pulls low when IN4 reaches  $V_{F13}$  (1.1V typ). C4RDY goes high impedance in shutdown, overload, and thermal limit when IN4 is under  $V_{F13}$ . A typical use for C4RDY is to drive a PMOS that gates 5V power to the CCD until the VH CCD bias (generated by CH4) is powered up (Figure 4).

Figure 4. C4RDY Application Circuit

#### Soft-Start

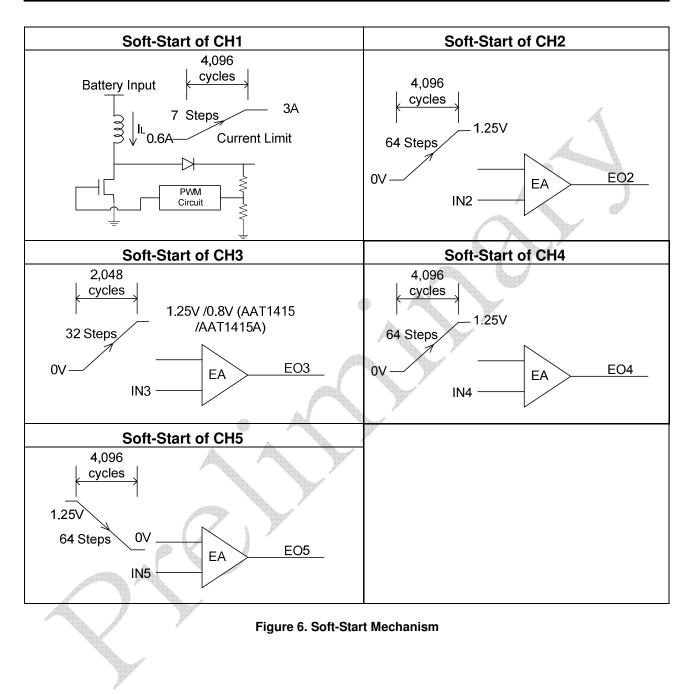

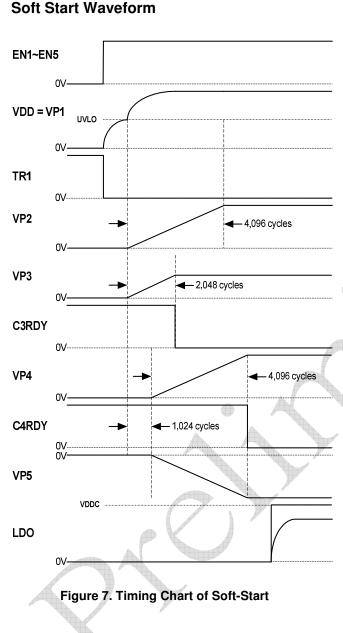

The AAT1415/AAT1415A channels feature a soft-start function that limits inrush current and prevent excessive battery loading at startup by ramping the output voltage of each channel up to the regulation voltage.

This is accomplished by ramping the internal reference inputs to mostly channel error amplifier from 0V to the 1.25V reference voltage (CH5 from 1.25V to 0V) over a period of 4,096 oscillator cycles (16ms at 500kHz) when initial power is applied or when a channel is enabled. Soft-start of CH1 is different from others in order to avoid limiting startup capability with loading.

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 3.00

Page 22 of 32

Advanced Analog Technology, Inc.

See Figure 6. soft-start mechanism. CH3 soft-start ramp takes half the time (2,048 clock cycles) of the other channel ramps. This allows the CH3 and CH2 output (when set to 3.3V) to track each other and rise at nearly the same dV/dt rate on power-up. Once the step-down output reaches its regulation point (1.5V or 1.8V typ), the CH2 output (3.3V typ) continues to rise at the same ramp rate. See Figure 7 timing chart of soft-start.

#### 2.5V LDO

The 2.5V LDO regulates the VDDC voltages when the reference voltage (VREF) is ready and VDDC voltage is greater than 2.5V.

#### **Fault Protection**

If any DC-DC converter channel remains faulted for 100,000 clock cycles (200ms at 500kHz), then all outputs latch off until the AAT1415/AAT1415A is reinitialized or by cycling the input power. The fault-detection circuitry for any channel is disabled during its initial turn-on soft-start sequence. An exception to the standard fault behavior is that there is no 100,000 clock-cycle delay in entering the fault state if the OUT1 pin is dragged below its 2.5V UVLO1 threshold or is shorted. The UVLO1 immediately triggers and shuts down all channels. The CH1 then continues to attempt to start. If the CH1 output short remains, these attempts do not succeed since OUT1 remains near ground. If a soft-short or overload remains on OUT1, the startup oscillator switches the internal NMOS, but fault is retriggered if regulation is not achieved by the end of the soft-start interval. If OUT1 is dragged below the input, the overload is supplied by the body diode of the internal synchronous rectifier or by a Schottky diode connected from the battery to OUT1.

### AAT1415/AAT1415A

#### Reference

Connect a  $0.1\mu$ F ceramic bypass capacitor from VREF to GND. VREF is enabled when EN1, EN2 or EN3 is high. The AAT1415/AAT1415A has internal 1.250V references.

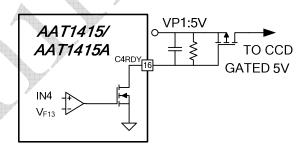

#### Oscillator

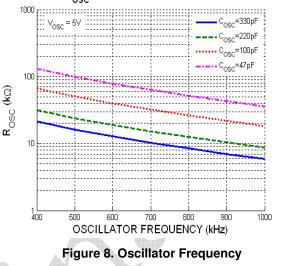

The AAT1415/AAT1415A operating frequency is set by an RC network ( $R_{OSC}$ ,  $C_{OSC}$ ) at the OSC pin. The range of usable settings is 100kHz to 1MHz. The oscillation frequency changes as the forced voltage ( $V_{OSC}$ ) ramps upward following startup. The oscillation frequency is then constant once the main output is in regulation. At the beginning of a cycle, the timing capacitor charge through the resistor until it reaches VREF. The charge time, t<sub>1</sub>, is as follows:

$$t_1 \approx -R_{OSC} \times C_{OSC} \times \ln(1 - \frac{1.25}{V_{OSC}})$$

The capacitor voltage then decays to zero over time t<sub>2</sub>  $\approx$  150ns. Choose C<sub>OSC</sub> between 47pF and 330pF. Determine R<sub>OSC</sub> and V<sub>OSC</sub>. The oscillator frequency is as follows:

$$f_{OSC} \approx \frac{1}{t_1 + t_2}$$

Figure 5. Oscillator Circuit

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 3.00

Page 23 of 32

May 2008

### AAT1415/AAT1415A

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 3.00

Page 24 of 32

May 2008

### AAT1415/AAT1415A

#### R<sub>OSC</sub> vs. OSCILLATOR FREQUENCY

#### Low-Voltage Startup Oscillator

The AAT1415/AAT1415A internal control and reference voltage circuitry receives power from VDD and do not function when VDD is less than 2.5V. To ensure low voltage startup, the CH1 employs a low-voltage startup oscillator (about 200kHz) that activates at 1.2V if a Schottky diode is connected from PWR to OUT1. The startup oscillator drives the internal NMOS at SW1 until VDD reaches 2.5V, at which point voltage control is passed to the normal oscillator (current-mode PWM circuitry). At low input voltages, the CH1 can have difficulty starting into heavy loads.

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 3.00

Page 25 of 32

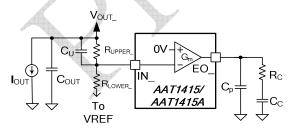

### **DESIGN PROCEDURE** Programming the Output Voltage

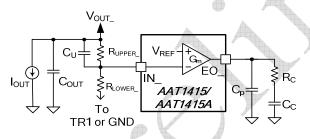

### The output voltage for each channel is programmed using a resistor divider from the output connected to the feedback pins. When setting the output voltage, connect a resistive voltage divider from the channel output to the corresponding IN\_ input and then to GND. Choose the lower-side (IN\_-to-GND) resistor, then calculate the upper-side (output-to-IN\_) resistor as follows:

$$\begin{split} & \mathsf{R}_{\mathsf{UPPER}\_} = \mathsf{R}_{\mathsf{LOWER}\_} \left( \frac{\mathsf{V}_{\mathsf{OUT}\_}}{\mathsf{V}_{\mathsf{IN}\_}} - 1 \right) \ \text{(For Boost / buck),} \\ & \mathsf{R}_{\mathsf{UPPER}\_} = \mathsf{R}_{\mathsf{LOWER}\_} \left( \frac{-\mathsf{V}_{\mathsf{OUT}\_}}{\mathsf{V}_{\mathsf{RFF}}} \right) \ \text{(For Inverting),} \end{split}$$

Where V<sub>IN</sub> is the feedback regulation voltage, 1.250V (AAT1415/AAT1415A, V<sub>IN3</sub> = 0.8V), and typical values for R<sub>LOWER</sub> are in the range of 10 k $\Omega$  to 100 k $\Omega$ .

Figure 9a. Feedback Network (For Boost/Buck)

Figure 9b. Feedback Network (For Inverting)

## AAT1415/AAT1415A

#### Inductor Selection

The inductor is typically selected to operate with

continuous conduction mode (CCM) for best efficiency in boost or buck converter and discontinuous conduction mode (DCM) for better response ability in boost or inverting controller (Table 1 and Table 2). The recommended inductance value range is between  $2.2\mu$ H and  $4.7\mu$ H for boost. The recommended inductance value range is between  $6.8\mu$ H and  $22\mu$ H for buck. The recommended inductance value range is between  $3.3\mu$ H and  $6.8\mu$ H for Inverting. With the chosen inductance value, the peak current for the inductor in steady state operation can be calculated (Table 3). It also needs to be taken into account that load transients and error conditions may cause higher inductor currents. This also needs to be taken into account when selecting an appropriate inductor.

| Table 1. Res                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ponse A | bility for | Various | Topologies |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|---------|------------|

| VIII CONTRACTOR OF CONTRACTORO |         |            |         |            |

|   | Topology                                                            | Response Ability                       |  |  |  |  |

|---|---------------------------------------------------------------------|----------------------------------------|--|--|--|--|

| p | Boost or                                                            | V <sub>IN</sub>                        |  |  |  |  |

|   | Inverting                                                           | L                                      |  |  |  |  |

|   | Buck                                                                | V <sub>IN</sub> -V <sub>OUT</sub><br>L |  |  |  |  |

| ø | V <sub>IN</sub> : Input Voltage, V <sub>OUT</sub> : Output Voltage, |                                        |  |  |  |  |

|   | L : Inductance, Response Ability Unit: $\frac{mA}{\mu s}$           |                                        |  |  |  |  |

#### Table 2. DCM/CCM Critical Inductance Values

| Topology                                                                                                                                | D                                                                | DCM/CCM                                                   |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------|--|--|--|

| Boost                                                                                                                                   | $1 - \frac{V_{IN}}{V_{OUT}}$                                     | $\frac{R_{LOAD} \cdot D \cdot (1 - D)^2}{2 \cdot f_{SW}}$ |  |  |  |

| Buck                                                                                                                                    | V <sub>OUT</sub><br>V <sub>IN</sub>                              | $\frac{(1-D) \cdot R_{LOAD}}{2 \cdot f_{SW}}$             |  |  |  |

| Inverting                                                                                                                               | $\frac{\left  V_{OUT} \right }{\left  V_{OUT} \right  + V_{IN}}$ | $\frac{R_{LOAD} \cdot (1-D)^2}{2 \cdot f_{SW}}$           |  |  |  |

| V <sub>IN</sub> : Input Voltage, V <sub>OUT</sub> : Output Voltage,<br>R <sub>LOAD</sub> : Loading, f <sub>SW</sub> : Switch Frequency, |                                                                  |                                                           |  |  |  |

| Inductance Unit: Henry                                                                                                                  |                                                                  |                                                           |  |  |  |

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. -

Version 3.00

Page 26 of 32

| Table 3. Inductor Peak Current                                                                                                 |      |                                                                                                                                                                                           |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Topology                                                                                                                       | Mode | Peak Current                                                                                                                                                                              |  |  |  |

| Boost                                                                                                                          | ССМ  | $\begin{split} & \frac{I_{O}}{(1-D)} + \frac{\Delta I_{L}}{2} , \\ & \Delta I_{L} = \frac{V_{OUT} \cdot D \cdot (1-D)}{f_{SW} \cdot L} , \\ & D = 1 - \frac{V_{IN}}{V_{OUT}} \end{split}$ |  |  |  |

|                                                                                                                                | DCM  | $\sqrt{\frac{2 \cdot (V_{OUT} - V_{IN}) \cdot I_{O}}{L \cdot f_{SW}}}$                                                                                                                    |  |  |  |

| Buck                                                                                                                           | ССМ  | $\begin{split} &I_{O} + \frac{\Delta I_{L}}{2}, \\ &(\Delta I_{L} = \frac{V_{OUT} \cdot (1 - D)}{f_{SW} \cdot L}, \\ &D = \frac{V_{OUT}}{V_{IN}}) \end{split}$                            |  |  |  |

|                                                                                                                                | DCM  | $\sqrt{\frac{2 \cdot (V_{IN} - V_{OUT}) \cdot V_{OUT} \cdot I_{O}}{L \cdot f_{SW} \cdot V_{IN}}}$                                                                                         |  |  |  |

| Inverting                                                                                                                      | ССМ  | $I_{O} + \frac{\Delta I_{L}}{2}, (\Delta I_{L} = \frac{V_{IN} \cdot D}{f_{SW} \cdot L},$ $D = \frac{ V_{OUT} }{ V_{OUT}  + V_{IN}})$                                                      |  |  |  |

|                                                                                                                                | DCM  | $\sqrt{\frac{2 \cdot  V_{OUT}  \cdot I_{O}}{L \cdot f_{SW}}}$                                                                                                                             |  |  |  |

| $V_{IN}$ : Input Voltage, $V_{OUT}$ : Output Voltage, $I_O$ : Output Current, L: Inductance, $f_{SW}$ : Switch Frequency, Peak |      |                                                                                                                                                                                           |  |  |  |

### Schottky Diode Selection

Current Unit: Ampere

Choose a Schottky diode who's maximum reverse voltage rating is greater than the value in Table 4, and who's current rating is greater than the peak inductor current.

# AAT1415/AAT1415A

| Table 4. Diode and MOS Minimum Voltage Rating |                                    |  |  |

|-----------------------------------------------|------------------------------------|--|--|

| Topology                                      | Minimum Voltage Rating             |  |  |

| Boost                                         | V <sub>OUT</sub>                   |  |  |

| Buck                                          | V <sub>IN</sub>                    |  |  |

| Inverting                                     | V <sub>IN</sub> + V <sub>OUT</sub> |  |  |

### External MOSFET Selection

The boost controller and Inverting controller drive external logic-level MOSFETs. MOSFETs' maximum drain-to-source voltage ( $V_{DS(MAX)}$ ) rating must be greater than the value in Table 4. Their on-resistance ( $R_{DS(ON)}$ ), total gate charge ( $Q_G$ ) and reverse transfer capacitance ( $C_{RSS}$ ) are the lower the better.

#### **Input Capacitor**

The input current to converters are discontinuous, and therefore input capacitors are required to supply the AC current to converters while maintaining the DC input voltage. A low ESR capacitor is required to keep the noise at the IC to a minimum. Ceramic capacitors are preferred, but tantalum or low-ESR electrolytic capacitors may also suffice. For insuring stable operation a bypass ceramic  $0.1\mu$ F capacitor should be placed as close to the IC VDD pin as possible.

### **Output Capacitor**

The output capacitor is required to maintain the DC output voltage. Low ESR capacitors are preferred to keep the output voltage ripple low. The characteristics of the output capacitor also affect the stability of the regulation control system. Ceramic, tantalum, or low ESR electrolytic capacitors are recommended. In the case of ceramic capacitors, the impedance at the switching frequency is dominated by the capacitance, and so the output voltage ripple is mostly independent of the ESR. The output voltage ripple is estimated to be:

$$V_{\text{RIPPLE}} \approx \frac{\Delta I_{\text{L}}}{2\pi \times f_{\text{SW}} \times C_{\text{OUT}}}$$

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. -

Version 3.00

Page 27 of 32

Advanced Analog Technology, Inc.

May 2008

### AAT1415/AAT1415A

Where  $V_{RIPPLE}$  is the output ripple voltage,  $\Delta I_L$  is the inductor ripple current,  $f_{SW}$  is the switching frequency and COUT is the output capacitance. In the case of tantalum or low- ESR electrolytic capacitors, the ESR dominates the impedance at the switching frequency, and so the output ripple is calculated as:

$$V_{RIPPLE} \approx \Delta I_L \times R_{ESR}$$

Where  $V_{RIPPLE}$  is the output voltage ripple,  $\Delta I_L$  is the inductor ripple current, and  $R_{ESR}$  is the equivalent series resistance of the output capacitors.

#### **Boost Converter Compensation**

The compensation resistor and capacitor (Figure 9a) are chosen to optimize control-loop stability. The boost converter employs current-mode control, thereby simplifying the control-loop compensation. When the converter operates with continuous conduction mode (typically the case), a right-half-plane zero appears in the loop-gain frequency response. To ensure stability, the cross over frequency ( $f_C$ ) should be much less than that of the right-half-plane zero.

For CCM, the right-half-plane zero frequency ( $f_{\text{RHPZ}}$ ) is given by the following:

$f_{RHPZ} = \frac{V_{OUT} \times (1-D)^2}{2\pi \times L \times I_{IOAD}}$

Typically target cross over frequency ( $f_C$ ) is the value for 1/6 of the RHPZ. Choose  $f_C$ , and then calculate compensation capacitor ( $C_C$ ) as follows:

$$C_{C} = \frac{V_{IN}}{R_{CS}} \times \frac{G_{m}}{2\pi \cdot f_{C}} \times \frac{(1-D)}{I_{LOAD}}$$

Where  $V_{IN}$  is the feedback regulation voltage, 1.25V (typ),  $R_{CS}$  is the current-sense amplifier transresistance, 0.25V/A (typ),  $G_M$  is the error amplifier transconductance, 70µS (typ). Select  $R_C$  based on the allowed transient-droop (TD%) requirements by the

following equation:

$$R_{C} = I_{L(PK)} \times \frac{R_{CS}}{TD\% \times V_{IN} \times G_{m}}$$

Where  $I_{L(PK)}$  is the inductor peak current. The output filter capacitor (typically ceramic capacitor) is then chosen to cancel the  $R_CC_C$  zero:

$$C_{OUT} = \frac{I_{LOAD}}{V_{OUT}} \times R_{C}C_{C}$$

If the output filter capacitor (typically electrolytic capacitor) has significant equivalent series resistance (ESR), a zero occurs at the following:

$$Z_{ESR} = \frac{1}{2\pi \times C_{OUT} \times R_{ESR}}$$

If  $Z_{ESR} \gg f_C$ , it can be ignored. If  $Z_{ESR}$  is less than  $f_C$ , it should be cancelled with a pole set by capacitor  $C_P$  connected from EO\_ to GND:

$$C_{P} = \frac{C_{OUT} \times R_{ESR}}{R_{C}}$$

If the system wants better transient response, it can parallel a capacitor  $C_U$  with  $R_{UPPER}\_$  from IN\_ to  $V_{OUT}$  :

$$C_{U} = \frac{1}{2\pi \times R_{UPPER} \times f_{C} \times \left( V_{IN} - V_{OUT} \right)}$$

If  $C_P$  or  $C_U$  is calculated to be less than 10pF, it can be omitted. Additionally,  $C_P$  or  $C_U$  can suppress the inrush current.

So, for a 3.3V/250mA output with V<sub>1</sub> = 2.0V, L =  $3.5\mu$ H, R<sub>UPPER</sub> = 164k, f<sub>SW</sub> = 500kHz and transient-droop 5%:

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 3.00

Page 28 of 32

Advanced Analog Technology, Inc.

May 2008

$$C_{C} = \frac{1.25V}{0.25V / A} \times \frac{70 \mu A / V}{2\pi \cdot 35 kHz} \times \frac{(1 - 0.39)}{250 mA} \approx 3.3 nF ,$$

$$\mathsf{R}_{\mathsf{C}} = 0.64 \times \frac{0.25 \,\mathsf{V} \,/\,\mathsf{A}}{0.05 \times 1.25 \times 70 \,\mu\,\mathsf{A} \,/\,\mathsf{V}} \approx 36 \mathrm{k}\Omega\,,$$

$$C_{OUT} = \frac{250mA}{3.3V} \times 36k\Omega \times 3.3nF \approx 10 \mu F$$

When the  $C_{OUT}$  value is two to three times greater than what's calculated above, better output voltage ripple can be achieved.

$$C_{U} = \frac{1}{2\pi \times 164 k\Omega \times 35 kHz \times (1.25 V/3.3 V)} \approx 100 pF$$

#### **Buck Converter Compensation**

The buck converter employs current-mode control, thereby simplifying the control-loop compensation. When the buck converter operates with continuous inductor current (typically the case), a  $R_{LOAD} C_{OUT}$  pole appears in the loop-gain frequency response. To ensure stability, set the compensation  $R_CC_C$  (Figure 9a) to zero to compensate for the  $R_{LOAD} C_{OUT}$  pole. Then set the loop crossover frequency below 1/5 of the switching frequency. The compensation resistor and capacitor are then chosen to optimize control-loop stability.

Choose the compensation capacitor  $C_C$  to set the desired crossover frequency  $f_C$ . Determine the value by the following equation:

$$C_{C} = \frac{V_{IN}}{I_{LOAD} \times R_{CS}} \times \frac{G_{m}}{2\pi \cdot f_{C}}$$

where V<sub>IN</sub> is the feedback regulation voltage, 1.25V (typ), R<sub>CS</sub> is the current-sense amplifier transresistance, 0.5V/A (typ), G<sub>m</sub> is the error amplifier transconductance, 70µS (typ). Select R<sub>C</sub> based on the allowed transient-droop (TD%) requirements by the following

equation:

$$R_{C} = I_{L(PK)} \times \frac{R_{CS}}{TD\% \times V_{IN} \times G_{m}}$$

Where  $I_{L(PK)}$  is the inductor peak current. The output filter capacitor (typically ceramic capacitor) is then chosen to cancel the  $R_CC_C$  zero:

$$C_{OUT} = \frac{I_{LOAD}}{V_{OUT}} \times R_{C}C_{C}$$

If the output filter capacitor (typically electrolytic capacitor) has significant equivalent series resistance (ESR), a zero occurs at the following:

$$Z_{ESR} = \frac{1}{2\pi \times C_{OUT} \times R_{ESR}}$$

If  $Z_{ESR} >> f_C$ , it can be ignored. If  $Z_{ESR}$  is less than  $f_C$ , it should be cancelled with a pole set by capacitor  $C_P$  connected from EO\_ to GND:

$$C_{P} = \frac{C_{OUT} \times R_{ESR}}{R_{C}}$$

If the system wants better transient response, it can parallel a capacitor  $C_U$  with  $R_{UPPER}\_$  from IN\_ to  $V_{OUT}$  :

$$C_{U} = \frac{1}{2\pi \times R_{UPPER} \times f_{C} \times \left( V_{IN} / V_{OUT} \right)}$$

If  $C_P$  or  $C_U$  is calculated to be less than 10pF, it can be omitted.

So, for a 1.5V/250mA output with V<sub>I</sub> = 3.0V, L = 10 $\mu$ H, R<sub>UPPER</sub> = 20 k $\Omega$ , f<sub>SW</sub> = 500kHz and transient-droop 3%:

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 3.00

Page 29 of 32

May 2008

$$C_{C} = \frac{1.25V}{250mA \times 0.5V / A} \times \frac{70 \mu A / V}{2\pi \cdot 70 kHz} \approx 2.2nF$$

$$R_C = 0.325A \times \frac{0.5V \,/\,A}{0.03 \times 1.25 \times 70 \,\mu\,A \,/\,V} \approx 68 k \Omega \;,$$

$$C_{OUT} = \frac{250 mA}{1.5 V} \times 68 k\Omega \times 2.2 nF \approx 22 \mu F \,, \label{eq:course}$$

$$C_{U} = \frac{1}{2\pi \times 20k\Omega \times 70kHz \times (1.25V/1.5V)} \approx 220 \text{pF}.$$

#### **Boost Controller Compensation**

The boost controller employs voltage-mode control to regulate their output voltage. A benefit of discontinuous conduction mode (DCM) is more flexible loop compensation, better response ability and no maximum duty-cycle restriction on boost ratio. When the boost converter operates with discontinuous conduction mode (typically the CCD VH case), the boost controller has a single pole at the following:

$$f_{P} = \frac{2 \times V_{OUT} - V_{I}}{2\pi \times R_{LOAD} \times C_{OUT} \times V_{OUT}}$$

Set the loop cross over frequency ( $f_C$ ) below the lower of 1/10 the switching frequency ( $f_{SW}$ ). Choose the compensation capacitor  $C_C$  to set the desired crossover frequency  $f_C$ . Determine the value by the following equation:

$$C_{C} = \frac{V_{OUT} \cdot V_{I}}{(2 \cdot V_{OUT} - V_{I})} \times \frac{G_{m}}{2\pi \cdot f_{C}} \times \sqrt{\frac{V_{OUT}}{M \cdot (V_{OUT} - V_{I})}}$$

Where:

$$M = \frac{2 \cdot L \cdot f_{SW}}{R_{LOAD}}$$

The  $R_C C_C$  zero is then used to cancel the  $f_P$  pole, so:

$$\mathsf{R}_{\mathsf{C}} = \frac{\mathsf{V}_{\mathsf{OUT}} \cdot \mathsf{R}_{\mathsf{LOAD}} \cdot \mathsf{C}_{\mathsf{OUT}}}{(2 \cdot \mathsf{V}_{\mathsf{OUT}} - \mathsf{V}_{\mathsf{I}}) \cdot \mathsf{C}_{\mathsf{C}}}$$

The typical  $R_C$  is under 500 k $\Omega$ .

If the system wants better transient response, it can parallel a capacitor  $C_U$  with  $R_{UPPER}\_$  from IN\_ to  $V_{OUT}$  :

AAT1415/AAT1415A

$$C_{U} = \frac{1}{2\pi \times R_{UPPER} \times f_{C} \times \left(V_{IN} - V_{OUT}\right)}$$

If  $C_U$  is calculated to be less than 10pF, it can be omitted. Additionally,  $C_U$  can suppress the inrush current

So, for a 13V/30mA output with V<sub>I</sub> = 3.0V, L =  $3.5 \mu$ H, R<sub>UPPER</sub> =  $100 k\Omega$ , f<sub>SW</sub> = 500kHz:

$$C_{C} = \frac{13V \cdot 3V}{(2 \cdot 13V - 3V)} \times \frac{70 \mu A / V}{2\pi \cdot 50 kHz} \times \sqrt{\frac{13V}{8m \cdot (13V - 2V)}}$$

$$\approx 4.7 nF$$

$$\mathsf{R}_{\mathsf{C}} = \frac{13\mathsf{V}\cdot433\Omega\cdot10\mu\mathsf{F}}{(2\cdot13\mathsf{V}-3\mathsf{V})\cdot4.7\mathsf{n}\mathsf{F}} \approx 500\mathsf{k}\Omega \ ,$$

$$C_{U} = \frac{1}{2\pi \times 100k \times 50kHz \times (1.25V/13V)} \approx 330pF.$$

#### Inverting Controller Compensation

The inverting controller also employs voltage-mode control to regulate their output voltage. To operate in discontinuous conduction mode (DCM) is preferred for simple loop compensation and freedom from duty-cycle restrictions on the inverter input-output ratio. When the Inverting converter operates with discontinuous conduction mode (typically the CCD VL case), the inverting controller has a single pole at the following:

$$f_{P} = \frac{1}{\pi \cdot R_{LOAD} \cdot C_{OUT}}$$

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. -

Version 3.00

Page 30 of 32

Advanced Analog Technology, Inc.

CU

May 2008

Set the loop cross over frequency ( $f_C$ ) below the lower of 1/10 the switching frequency ( $f_{SW}$ ). Choose the compensation capacitor  $C_C$  to set the desired crossover frequency  $f_C$ . Determine the value by the following equation:

$$C_{C} = \frac{V_{I}}{(\left|V_{OUT}\right| + V_{REF}) \cdot \sqrt{M}} \times \frac{G_{m}}{2\pi \cdot f_{C}}$$

Where:

$$M = \frac{2 \cdot L \cdot f_{SW}}{R_{LOAD}}$$

The  $R_C C_C$  zero is then used to cancel the  $f_P$  pole, so:

$$R_{C} = \frac{R_{LOAD} \cdot C_{OUT}}{2 \cdot C_{C}}$$

The typical  $R_C$  is under 500 k $\Omega$ .

If the system wants better transient response, it can parallel a capacitor C\_U with R\_{UPPER\_} from IN\_ to V\_{OUT\_}:

$$C_{U} = \frac{1}{2\pi \times R_{UPPER} \times f_{C} \times \left(\frac{V_{IN}}{|V_{OUT}| + V_{IN}}\right)}$$

If  $C_U$  is calculated to be less than 10pF, it can be omitted. Additional  $C_U$  can suppress the inrush current. So, for a -7V/50mA output with V<sub>I</sub> = 3.0V, L = 4.7µH,  $R_{UPPER} = 56 k\Omega$ , f<sub>SW</sub> = 500kHz:

$$C_{C} = \frac{3V}{(|-7|+1.25V) \cdot \sqrt{33.6m}} \times \frac{70 \,\mu\,\text{A}/\text{V}}{2\pi \cdot 20 \,\text{kHz}} \approx 2.2 \,\text{nF}$$

$$\mathsf{R}_{\mathsf{C}} = \frac{140\Omega \cdot 10\mu\mathsf{F}}{2 \cdot 2.2\mathsf{n}\mathsf{F}} \approx 300\mathsf{k}\Omega \; ,$$

$$\frac{\textbf{AAT1415}/\textbf{AAT1415A}}{2\pi \times 56 \text{k}\Omega \times 20 \text{kHz} \times \left(\frac{\text{V}_{\text{IN}}}{|\text{V}_{\text{OUT}}| + \text{V}_{\text{IN}}}\right)} \approx 1\text{nF}$$

LAYOUT CONSIDERATIONS

Conductors carrying discontinuous currents and any high-current path should be made as short and wide as possible. The compensation network should be very close to the EO pin and avoid through VIA. The IC must be bypassed with ceramic capacitors placed close to the VDD and VREF. A separate low-noise ground plane containing the reference and signal grounds should connect to the power-ground plane at only one point to minimize the effects of power-ground currents. Typically, the ground planes are best joined right at the IC. Tie the feedback resistor divider to be very close to output capacitor and far away from the inductor or Schottky diode. Keep the feedback network (IN) close to the IC. Switching nodes (SW) should be kept as small as possible and should be routed away from high-impedance nodes such as IN.

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 3.00

Page 31 of 32

May 2008

### AAT1415/AAT1415A

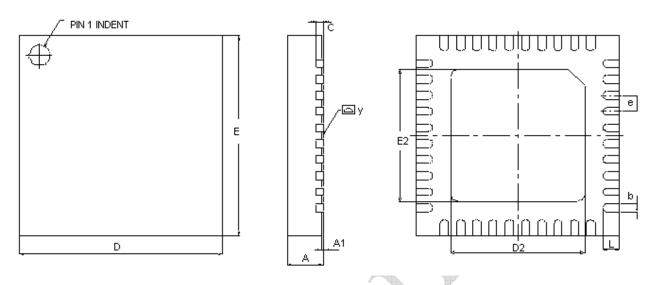

# **PACKAGE DIMENSION**

### VQFN40 5\*5

| Symbol | Dimensions In Millimeters |      |       |  |  |

|--------|---------------------------|------|-------|--|--|

| Symbol | MIN                       | ТҮР  | MAX   |  |  |

| А      | 0.8                       | 0.9  | 1.0   |  |  |

| A1     | 0.00                      | 0.02 | 0.05  |  |  |

| b      | 0.15                      | 0.20 | 0.25  |  |  |

| С      |                           | 0.2  |       |  |  |

| D      | 4.9                       | 5.0  | 5.1   |  |  |

| D2     | 3.25                      | 3.30 | 3.35  |  |  |

| E      | 4.9                       | 5.0  | 5.1   |  |  |

| E2     | 3.25                      | 3.30 | 3.35  |  |  |

| е      |                           | 0.4  |       |  |  |

|        | 0.35                      | 0.40 | 0.45  |  |  |

| у      | 0                         |      | 0.075 |  |  |

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 3.00

Page 32 of 32