November 2008

- Pletronics' FD5T Series is a quartz crystal controlled precision square wave generator with a programmable CMOS output

- Output frequency from 12 KHz to 230 MHZ

- Selectable low jitter or spread spectrum output.

- Device characteristics may be either factory or field programmable

- 1.8V, 2.5 or 3.3V LVCMOS outputs

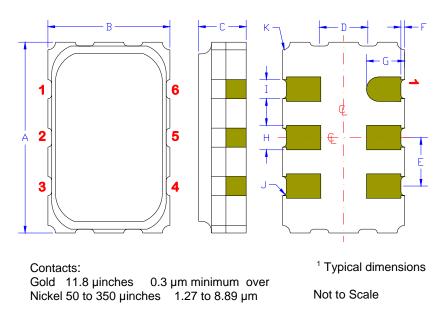

- 3.2 x 5 mm LCC Ceramic Package

- Low power

- This is a low cost, mass produced oscillator.

- Tape and Reel or cut tape packaging is available.

- Designed for high density SMD needs

- · Excellent frequency stability options

### Pletronics Inc. certifies this device is in accordance with the RoHS 6/6 (2002/95/EC) and WEEE (2002/96/EC) directives.

Pletronics Inc. guarantees the device does not contain the following: Cadmium, Hexavalent Chromium, Lead, Mercury, PBB's, PBDE's Weight of the Device: 0.09 grams Moisture Sensitivity Level: 1 As defined in J-STD-020C Second Level Interconnect code: e4

### **Absolute Maximum Ratings:**

| Parameter                            | Unit                               |  |  |  |  |  |

|--------------------------------------|------------------------------------|--|--|--|--|--|

| V <sub>DD</sub>                      | -0.5V to +2.5V                     |  |  |  |  |  |

| V <sub>DDOUT</sub>                   | -0.5V to +4.6V                     |  |  |  |  |  |

| Vi Input Voltage                     | -0.5V to V <sub>DD</sub> + 0.5V    |  |  |  |  |  |

| Vo Output Voltage                    | -0.5V to V <sub>DDOUT</sub> + 0.5V |  |  |  |  |  |

| lo Continuous Output Current         | ± 50 mA                            |  |  |  |  |  |

| Tj Maximum Junction Temperature      | 125°C                              |  |  |  |  |  |

| Thermal Resistance, Junction to Case | 50°C/Watt                          |  |  |  |  |  |

Product information is current as of publication date. The product conforms to specifications per the terms of the Pletronics standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 2008, Pletronics Inc.

November 2008

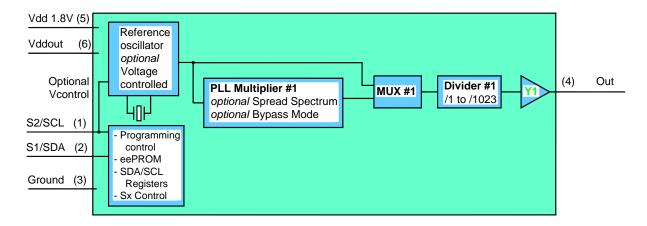

### **Description:**

The FD5T series Programmable CMOS Clock Oscillator is a modular PLL-based low cost, high-performance oscillator. The frequency range is from 12KHz to 230MHZ.

The FD5T base frequency, as noted in the device part number, is established during manufacture and is permanently fixed. For convenience, the divider for output OUT characteristics may be pre-programmed at the factory, or field programmed.

The FD5T has a separate output supply pin,  $V_{DDOUT}$ , for either 1.8, 2.5 or 3.3V output logic levels. The device supply,  $V_{DD}$  which provides power to all the internal circuits, is nominally 1.8V.

The deep M/N PLL divider ratio allows the generation of zero-ppm clocks for applications such as WLAN, BlueTooth, Ethernet, USB, IEEE1394, etc. from the base frequency.

The PLL supports Spread Spectrum Clocking (SSC). SSC may be programmed to be either center-spread or down-spread. This is an important technique to reduce electro-magnetic interference (EMI).

The device supports non-volatile eePROM programming for easy customization of the device. As shipped, the device is pre-programmed. Standard combinations are denoted by three characters in the device part number. However, the FD5T may be reprogrammed to a different configuration. Reprogramming may be either prior to assembly, or in-circuit via a 2-wire SDA/SCL I²C bus. In-circuit programming is not allowed if the VCXO function is needed.

Two programmable control inputs, S1 and S2, may be used to control various aspects of FD55T operation including selection of alternative frequency set(s), selection of SSC functionality, output tri-state and power-down.

#### **Reference Oscillator**

The Reference Oscillator is an AT cut quartz crystal based oscillator. This oscillator is very similar to the Pletronics SM77xxH product oscillator. This signal is the lowest jitter and can be an output or can be divided down by the Divider #1. The user may specify any frequency between 12MHz and 32MHz for this reference. All output frequencies are derived from (referenced to) this Reference Oscillator.

The VCXO input has a limited voltage range, the VCXO is associated with the internal 1.8V core. A resistor in series with the Vcontrol input will permit interfacing to 3.3V analog circuits, the voltage range that changes the frequency will still be limited but the larger voltages swings will not cause problems.

The VCXO function is only enabled (internally connected) if the part number indicates a VCXO specification. When the VCXO function is enabled the I<sup>2</sup>C programming mode will be disabled.

### **PLL Multipliers**

The PLL Multiplier can multiply the Reference Oscillator frequency from 1 (bypass mode) to any value that is <=230MHz (the lowest frequency is the Reference Oscillator frequency).

The PLL Multipliers can have two setup options, 0 or 1, depending on which option is chosen and set by the Sx control signals and the user's definitions are stored in eePROM.

#### **Spread Spectrum**

November 2008

Each PLL has its individual Spread Spectrum (SS) function that can be enabled. This permits the modulation of the output frequency by a user-set amount. The modulation can be centered on the output frequency or down side only. Which of the 1 of 8 SS settings is being used is set by the Sx input and the user definition. The value is a percentage of the output frequency that will be modulated.

| SS Option | Down Side Modulation | Centered Modulation |

|-----------|----------------------|---------------------|

| 0         | No SS                | No SS               |

| 1         | -0.25%               | <u>+</u> 0.25%      |

| 2         | -0.50%               | <u>+</u> 0.50%      |

| 3         | -0.75%               | <u>+</u> 0.75%      |

| 4         | -1.00%               | <u>+</u> 1.00%      |

| 5         | -1.25%               | <u>+</u> 1.25%      |

| 6         | -1.50%               | <u>+</u> 1.50%      |

| 7         | -2.00%               | <u>+</u> 2.00%      |

#### **Divider Section**

The dividers operate on the output of the PLL. The divider on the PLL can divide by 1 through 127, the value is user defined. There is only 1 setting allowed per divider. These are not set by the Sx input state.

The dividers add very little jitter to the output signals.

#### Multiplexers

MUX #1 selects the input to the Divider #1, this can be the reference oscillator signal or the output from PLL Multiplier #1. MUX #3 connect various divider outputs to the output buffer.

The device can make only one of the setting of connections shown in the block diagram (only one pattern stored in eePROM).

#### **Output Buffer**

The output buffer can have 3 modes of operation:

- 1) Tri State

- 2) Active Low

- 3) The signal output of the Multiplexer

There can be two options stored for the Output Buffer, State 0 and State 1. The four Sx input settings can have assigned one of the two Output Buffer states for each of Output Buffer sets.

#### **Control Inputs**

The two inputs, S1/SDA and S2/SCL can be configured in two ways.

- 1) Used as 2 user inputs to permit up to 4 states, Sx input setting.

- 2) The SDA and SCL become clock and data inputs to write to the FD5T internal setting memory. The interface follows the I<sup>2</sup>C protocol. If the SDA and SCL are not set then the internal eePROM sets the operation. (Not allowed if the VCXO function is specified.)

November 2008

### **PART NUMBER:**

| FD5 | 1 | 45 | T | L | Ε | -25.0M | -YYY | -XX |                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|---|----|---|---|---|--------|------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |   |    |   |   |   |        |      |     | Packaging code or blank T250 = 250 per Tape and Reel T500 = 500 per Tape and Reel T1K = 1000 per Tape and Reel                                                                                                                                                                                                                                                                                   |

|     |   |    |   |   |   |        |      |     | Configuration Number This is a 3 character alpha-numeric code issued by Pletronics that defines the FD5T function (the output pin functions, the available frequencies and the pin number assignments). Each configuration is given a unique value.                                                                                                                                              |

|     |   |    |   |   |   |        |      |     | Base Frequency (Crystal oscillator frequency) in MHZ                                                                                                                                                                                                                                                                                                                                             |

|     |   |    |   |   |   |        |      |     | Optional Enhanced Operating temperature Range Blank = Temp. range -20°C to +70°C E = Temp. range -40°C to +85°C                                                                                                                                                                                                                                                                                  |

|     |   |    |   |   |   |        |      |     | Blank = V <sub>DDOUT</sub> 3.3V, 2.5V and 1.8V device  L = V <sub>DDOUT</sub> 1.8V only high output drive level device                                                                                                                                                                                                                                                                           |

|     |   |    |   |   |   |        |      |     | Series Model                                                                                                                                                                                                                                                                                                                                                                                     |

|     |   |    |   |   |   |        |      |     | Frequency Stability for fixed frequency oscillator $45 = \pm 50 \text{ ppm}$ $15 = \pm 15 \text{ ppm}$ $44 = \pm 25 \text{ ppm}$ $10 = \pm 10 \text{ ppm}$ $20 = \pm 20 \text{ ppm}$ Frequency Pull Ability for VCXO option enabled $99 = \pm 100 \text{ ppm}$ Absolute Pull Range (APR) $75 = \pm 25 \text{ ppm}$ Absolute Pull Range (APR) $50 = \pm 50 \text{ ppm}$ Absolute Pull Range (APR) |

|     |   |    |   |   |   |        |      |     | 1 = 1 output 1 PLL version                                                                                                                                                                                                                                                                                                                                                                       |

|     |   |    |   |   |   |        |      |     | Series Model                                                                                                                                                                                                                                                                                                                                                                                     |

### Part Marking:

**PLE FD51** Marking Legend: PLE = Pletronics X = Model type

**ZZZ** = configuration YMD = Date of Manufacture **YMD** All other marking is internal factory codes (year-month-day)

### Codes for Date Code YMD

| Code | 8    | 9    | 0    | 1    | 2    | Code  | Α   | В   | С   | D   | Е   | F   | G   | Н   | 7   | K   | L   | M   |

|------|------|------|------|------|------|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Year | 2008 | 2009 | 2010 | 2011 | 2012 | Month | JAN | FEB | MAR | APR | MAY | JUN | JUL | AUG | SEP | OCT | NOV | DEC |

|      |      |      |      |      |      |       |     |     |     |     |     |     |     |     |     |     |     |     |

| Code | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | Α  | В  | С  | D  | Е  | F  | G  |

|------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| Day  | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

| Code | H  | J  | K  | L  | М  | N  | Р  | R  | Т  | U  | ٧  | W  | Х  | Υ  | Z  |    |

| Day  | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |    |

November 2008

### **Electrical Specification over the specified temperature range**

| Item                                          | Min                               | Max | Unit | Condition                                           |

|-----------------------------------------------|-----------------------------------|-----|------|-----------------------------------------------------|

| Base Frequency                                | 12                                | 32  | MHZ  |                                                     |

| Frequency Range OUT1                          | 0.0117                            | 230 | MHZ  | Base Frequency / (1 to 1023) -or- PLL1              |

| Frequency Range OUT2 - 7                      | 0.0945                            | 230 | MHZ  |                                                     |

| Frequency Accuracy "45"                       | -50                               | +50 | ppm  | For all supply voltages, load changes,              |

| "44"                                          | -25                               | +25 |      | aging for 1 year, shock, vibration and temperatures |

| " <b>20</b> "                                 | -20                               | +20 |      |                                                     |

| Recommended Operating Conditi                 | ons                               |     |      |                                                     |

| Device Supply Voltage V <sub>DD</sub>         | 1.7                               | 1.9 | V    |                                                     |

| Output Supply Voltage V <sub>DDOUT</sub>      | 1.7                               | 3.6 | V    |                                                     |

| Output Supply Voltage "L" V <sub>DDOUT</sub>  | 1.7                               | 1.9 | V    |                                                     |

| Low Level Input voltage                       |                                   | 30  | %    | of V <sub>DD</sub>                                  |

| High Level Input voltage                      | 70                                | -   | %    | of V <sub>DD</sub>                                  |

| Input Voltage Range, S1, S2                   | 0                                 | 3.6 | V    | V <sub>TH</sub> is 0.5 * V <sub>DD</sub>            |

| Input current for: S1, S2                     | 0                                 | 5   | μΑ   | $V_{IN} = V_{DD}$ ; $V_{DD} = 1.9V$                 |

|                                               | -4                                | 0   | μΑ   | $V_{IN} = 0.0V_{D}$ ; $V_{DD} = 1.9V$               |

| Output Current, V <sub>DDOUT</sub> = 3.3V     | -12                               | +12 | mA   |                                                     |

| Output Current, V <sub>DDOUT</sub> = 2.5V     | -10                               | +10 | mA   |                                                     |

| Output Current, V <sub>DDOUT</sub> = 1.8V     | -5                                | +5  | mA   |                                                     |

| Output Current "L", V <sub>DDOUT</sub> = 1.8V | -8                                | +8  | mA   |                                                     |

| Output Load, LVCMOS                           |                                   | 10  | pf   | Higher loads can be used                            |

| LVCMOS Output Parameters for \                | $I_{\text{DDOUT}} = 3.3 \text{V}$ |     |      |                                                     |

| Output High, $V_{DDOUT} = 3.3V$               | 2.9                               | -   | V    | I <sub>OH</sub> = -0.1 mA                           |

|                                               | 2.4                               | 1   | V    | I <sub>OH</sub> = -8.0 mA                           |

|                                               | 2.2                               | 1   | V    | I <sub>OH</sub> = -12.0 mA                          |

| Output Low, $V_{DDOUT} = 3.3V$                | -                                 | 0.1 | V    | I <sub>OH</sub> = +0.1 mA                           |

|                                               | -                                 | 0.5 | V    | I <sub>OH</sub> = +8.0 mA                           |

|                                               |                                   | 0.8 | V    | I <sub>OH</sub> = +12.0 mA                          |

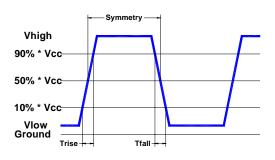

| Rise & Fall Time                              |                                   | 0.6 | nS   | V <sub>DDOUT</sub> = 3.3v, 20 - 80%, 10pF Load      |

| Output Symmetry                               | 45                                | 55  | %    | at 50% point of V <sub>DDOUT</sub>                  |

| Peak-to-Peak Jitter(1)(2)                     |                                   | 100 | pS   |                                                     |

| Cycle-to-Cycle Jitter <sup>(1)(2)</sup>       |                                   | 90  | pS   |                                                     |

November 2008

| Item                                    | Min                       | Max        | Unit | Condition                                      |

|-----------------------------------------|---------------------------|------------|------|------------------------------------------------|

| LVCMOS Output Parameters for            | V <sub>DDOUT</sub> = 2.5v |            |      |                                                |

| Output High, $V_{DDOUT} = 2.5V$         | 2.2                       |            | V    | I <sub>OH</sub> = -0.1 mA                      |

|                                         | 1.7                       |            | V    | I <sub>OH</sub> = -6.0 mA                      |

|                                         | 1.6                       |            | V    | I <sub>OH</sub> = -10.0 mA                     |

| Output Low, $V_{DDOUT} = 2.5V$          |                           | 0.1        | V    | I <sub>OH</sub> = +0.1 mA                      |

|                                         |                           | 0.5        | V    | I <sub>OH</sub> = +6.0 mA                      |

|                                         |                           | 0.7        | V    | I <sub>OH</sub> = +10.0 mA                     |

| Rise & Fall Time                        |                           | 0.6        | nS   | V <sub>DDOUT</sub> = 2.5v, 20 - 80%, 10pF Load |

| Output Symmetry                         | 45                        | 55         | %    | at 50% point of V <sub>DDOUT</sub>             |

| Peak-to-Peak Jitter(1)(2)               |                           | 100        | pS   |                                                |

| Cycle-to-Cycle Jitter(1)(2)             |                           | 90         | pS   |                                                |

| LVCMOS Output Parameters for            | V <sub>DDOUT</sub> = 1.8v |            |      |                                                |

| Output High, V <sub>DDOUT</sub> = 1.8V  | 1.6                       |            | V    | I <sub>OH</sub> = -0.1 mA                      |

|                                         | 1.4                       |            | V    | I <sub>OH</sub> = -3.0 mA                      |

|                                         | 1.1                       |            | V    | I <sub>OH</sub> = -6.0 mA                      |

| Output Low, V <sub>DDOUT</sub> = 1.8V   |                           | 0.1        | V    | I <sub>OH</sub> = +0.1 mA                      |

|                                         |                           | 0.3        | V    | I <sub>OH</sub> = +3.0 mA                      |

|                                         |                           | 0.6        | V    | I <sub>OH</sub> = +6.0 mA                      |

| Rise & Fall Time                        |                           | 0.9        | nS   | V <sub>DDOUT</sub> = 1.8v, 20 - 80%, 10pF Load |

| Output Symmetry                         | 45                        | 55         | %    | at 50% point of V <sub>DDOUT</sub>             |

| Peak-to-Peak Jitter(1)(2)               |                           | 140        | pS   |                                                |

| Cycle-to-Cycle Jitter <sup>(1)(2)</sup> |                           | 120        | pS   |                                                |

| LVCMOS Output Parameters for            | $V_{DDOUT} = 1.8v$        | "L" Versio | n    |                                                |

| Output High, $V_{DDOUT} = 1.8V$         | 1.6                       |            | V    | I <sub>OH</sub> = -0.1 mA                      |

|                                         | 1.4                       |            | V    | I <sub>OH</sub> = -4.0 mA                      |

|                                         | 1.1                       |            | V    | I <sub>OH</sub> = -8.0 mA                      |

| Output Low, V <sub>DDOUT</sub> = 1.8V   |                           | 0.1        | V    | I <sub>OH</sub> = +0.1 mA                      |

|                                         |                           | 0.3        | V    | I <sub>OH</sub> = +4.0 mA                      |

|                                         |                           | 0.6        | V    | I <sub>OH</sub> = +8.0 mA                      |

| Rise & Fall Time                        |                           | 0.7        | nS   | V <sub>DDOUT</sub> = 1.8v, 20 - 80%, 10pF Load |

| Output Symmetry                         | 45                        | 55         | %    | at 50% point of V <sub>DDOUT</sub>             |

| Peak-to-Peak Jitter(1)(2)               |                           | 140        | pS   |                                                |

| Cycle-to-Cycle Jitter <sup>(1)(2)</sup> |                           | 120        | pS   |                                                |

November 2008

| Item                                                                               | Min         | Max                    | Unit | Condition                                               |

|------------------------------------------------------------------------------------|-------------|------------------------|------|---------------------------------------------------------|

| VCXO Function                                                                      |             |                        |      |                                                         |

| Vcontrol Input Range Usable                                                        | 0.5         | V <sub>DD</sub> - 0.5V | V    | The slope is positive                                   |

| Vcontrol Input Range Allowed - Direct connect to Vcontrol - Limit current to ± 3mA | 0.0<br>-1.0 | V <sub>DD</sub> 4.0    | V    | The slope is positive<br>Recommend >=1K ohm to Vcontrol |

| Pull Ability specified in the P.N.                                                 |             |                        |      |                                                         |

| Linearity                                                                          | -10         | +10                    | %    |                                                         |

<sup>(1) 10,000</sup> cycles

Data is taken under the following conditions: 1-PLL; 27MHz Crystal, (measured at Out3).

### **Frequency Tolerance:**

For the FD5115T and the FD5110T devices, Pletronics recommends that the tight tolerance be required on the PLL outputs only. In this case the reference frequency output would only achieve ±25ppm tolerance. This will reduce the cost of the device.

<sup>(2)</sup> Jitter depends on the device configuration.

November 2008

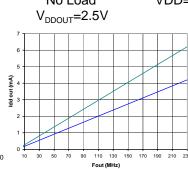

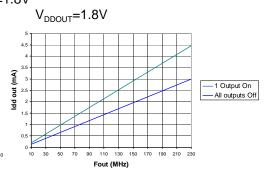

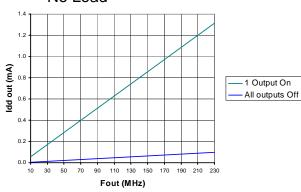

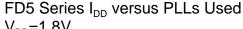

### $I_{\text{DDOUT}}$ Current for Various Number of Outputs On No Load VDD=1.8V

V<sub>DDOUT</sub>=3.3V

9

8

7

6

6

9

9

10

30

50

70

90

110

130

150

170

190

210

230

Fout (MHz)

FD51xxTL  $V_{DD} = V_{DDOUT} = 1.8V$ No Load

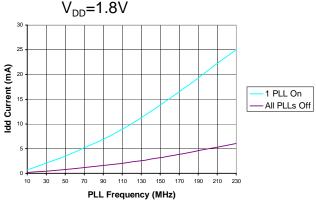

Phase noise of the reference signal, Out3. 25MHz Reference Frequency

RMS jitter is 1.4pS from 10Hz to 2MHz

Example of the PLL synthesizing a frequency.

25MHz Reference Frequency

Multiply by 8 to 200MHz

Divide the 200MHz PLL output by 8

Phase noise plot of the resulting 25MHz on Out 3

425-776-1880

November 2008

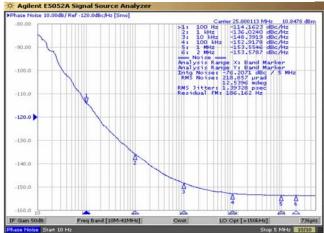

#### **Load Circuit and Test Waveform**

### **Reliability: Environmental Compliance**

| Parameter        | Condition                            |

|------------------|--------------------------------------|

| Mechanical Shock | MIL-STD-883 Method 2002, Condition B |

| Vibration        | MIL-STD-883 Method 2007, Condition A |

| Solderability    | MIL-STD-883 Method 2003              |

| Thermal Shock    | MIL-STD-883 Method 1011, Condition A |

### **ESD Rating**

| Model                | Minimum Voltage | Conditions              |  |  |  |  |

|----------------------|-----------------|-------------------------|--|--|--|--|

| Human Body Model     | 1500            | MIL-STD-883 Method 3115 |  |  |  |  |

| Charged Device Model | 1000            | JESD 22-C101            |  |  |  |  |

#### Package Labeling

Label is 1" x 2.6" (25.4mm x 66.7mm) Font is Courier New Bar code is 39-Full ASCII (Label will show FD55)

P/N: FD7745-25.0M-123

Customer P/N: 12345678

Qty: D/C 6MC5P

Label is 1" x 2.6" (25.4mm x 66.7mm) Font is Arial

RoHS Compliant

2nd LvL Interconnect

Category=e4

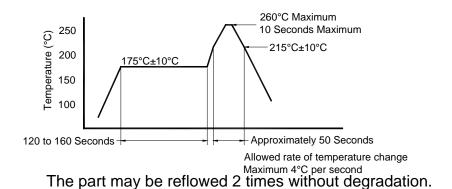

Max Safe Temp=260C for 10s 2X Max

November 2008

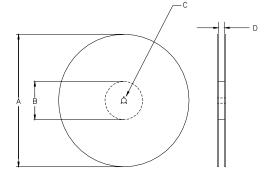

### Mechanical:

|                | Inches               | mm                 |

|----------------|----------------------|--------------------|

| Α              | 0.197 <u>+</u> 0.006 | 5.00 <u>+</u> 0.15 |

| В              | 0.125 <u>+</u> 0.006 | 3.20 <u>+</u> 0.15 |

| С              | 0.053 max            | 1.35 max           |

| D <sup>1</sup> | 0.050                | 1.27               |

| Ε¹             | 0.050                | 1.27               |

| F¹             | 0.004                | 0.10               |

| G¹             | 0.039                | 1.00               |

| H <sup>1</sup> | 0.025                | 0.63               |

| I <sup>1</sup> | 0.020                | 0.50               |

| J <sup>1</sup> | 0.004R               | 0.10R              |

| K <sup>1</sup> | 0.008R               | 0.20R              |

### **Pad Functions:**

| Pad | Function           | Note                                                                                                                      | _                                              |                        |  |  |  |  |  |

|-----|--------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------|--|--|--|--|--|

| 1   | S1/SDA             | Serial Data Clock (optional V control - VCXO)                                                                             | S2                                             | Input to select 1 of 4 |  |  |  |  |  |

| 2   | S2/SCL             | Serial Data                                                                                                               | preprogrammed functions the outputs (optional) |                        |  |  |  |  |  |

| 3   | Ground (GND)       |                                                                                                                           |                                                |                        |  |  |  |  |  |

|     |                    | Crystal reference frequency divided by 1 through 1023                                                                     |                                                |                        |  |  |  |  |  |

| 4   | Out (Y3)           | PLL1 frequency divided by 1 through 1023                                                                                  |                                                |                        |  |  |  |  |  |

| 5   | V <sub>DD</sub>    | 1.8V, powers internal circuitry of the oscillator. Bypass capacitor required near the package pin.                        |                                                |                        |  |  |  |  |  |

| 6   | V <sub>DDOUT</sub> | 1.8V, 2.5V or 3.3V supply for the output buffers. Sets CMOS output level. Bypass capacitor required near the package pin. |                                                |                        |  |  |  |  |  |

All unused inputs should be pulled high.

November 2008

### Reflow Cycle (typical for lead free-processing)

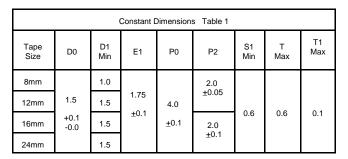

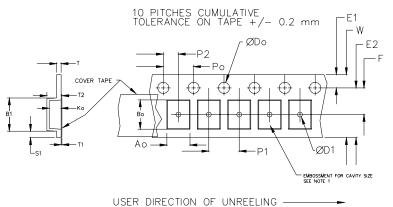

### Tape and Reel: available for quantities of 250 to 1000 per reel, cut tape for < 250

| Variable Dimensions Table 2 |           |        |                  |                  |           |          |                |  |  |

|-----------------------------|-----------|--------|------------------|------------------|-----------|----------|----------------|--|--|

| Tape<br>Size                | B1<br>Max | E2 Min | F                | P1               | T2<br>Max | W<br>Max | Ao, Bo &<br>Ko |  |  |

| 16 mm                       | 12.1      | 14.25  | 7.5 <u>+</u> 0.1 | 8.0 <u>+</u> 0.1 | 8.0       | 16.3     | Note 1         |  |  |

Note 1: Embossed cavity to conform to EIA-481-B

Not to scale

|   |        | REE                  |                      |                      |               |

|---|--------|----------------------|----------------------|----------------------|---------------|

| Α | inches | 7.0                  | 10.0                 | 13.0                 |               |

|   | mm     | 177.8                | 254.0                | 330.2                |               |

| В | inches | 2.50                 | 4.00                 | 3.75                 |               |

|   | mm     | 63.5                 | 101.6                | 95.3                 | Tape<br>Width |

| С | mm     | 13                   | wiain                |                      |               |

| D | mm     | 16.4<br>+2.0<br>-0.0 | 16.4<br>+2.0<br>-0.0 | 16.4<br>+2.0<br>-0.0 | 16.0          |

Reel dimensions may vary from the above

November 2008

#### **IMPORTANT NOTICE**

Pletronics Incorporated (PLE) reserves the right to make corrections, improvements, modifications and other changes to this product at any time. PLE reserves the right to discontinue any product or service without notice. Customers are responsible for obtaining the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to PLE's terms and conditions of sale supplied at the time of order acknowledgment.

PLE warrants performance of this product to the specifications applicable at the time of sale in accordance with PLE's limited warranty. Testing and other quality control techniques are used to the extent PLE deems necessary to support this warranty. Except where mandated by specific contractual documents, testing of all parameters of each product is not necessarily performed.

PLE assumes no liability for application assistance or customer product design. Customers are responsible for their products and applications using PLE components. To minimize the risks associated with the customer products and applications, customers should provide adequate design and operating safeguards.

PLE products are not designed, intended, authorized or warranted to be suitable for use in life support applications, devices or systems or other critical applications that may involve potential risks of death, personal injury or severe property or environmental damage. Inclusion of PLE products in such applications is understood to be fully at the risk of the customer. Use of PLE products in such applications requires the written approval of an appropriate PLE officer. Questions concerning potential risk applications should be directed to PLE.

PLE does not warrant or represent that any license, either express or implied, is granted under any PLE patent right, copyright, artwork or other intellectual property right relating to any combination, machine or process which PLE product or services are used. Information published by PLE regarding third-party products or services does not constitute a license from PLE to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from PLE under the patents or other intellectual property of PLE.

Reproduction of information in PLE data sheets or web site is permissible only if the reproduction is without alteration and is accompanied by associated warranties, conditions, limitations and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. PLE is not responsible or liable for such altered documents.

Resale of PLE products or services with statements different from or beyond the parameters stated by PLE for that product or service voids all express and implied warranties for the associated PLE product or service and is an unfair or deceptive business practice. PLE is not responsible for any such statements.

#### Contacting Pletronics Inc.

Pletronics Inc. Tel: 425-776-1880 19013 36<sup>th</sup> Ave. West Fax: 425-776-2760

Lynnwood, WA 98036-5761 USA E-mail: ple-sales@pletronics.com

URL: www.pletronics.com

Copyright © 2008 Pletronics Inc.