# L8576B Dual Ringing SLIC

# Features

- Two SLIC channels for multiple tip/ring interfaces

- On-chip balanced ringing generator, no ring relay required

- Single battery operation or optional automatic battery switch

- Quiet battery reversal for on-hook signaling

- Disconnect state

- Distortion-free, on-hook transmission

- 24 mA loop current limiter

- Ring trip detector

- Switchhook detector

- Immune to channel crosstalk and impulse noise

- Allows rail overvoltages for ease of protection

- Thermal protection

- 44-pin, surface-mount, plastic package (PLCC)

# **Applications**

- POTS for ISDN

- Terminal adapters (TA)

- Digital loop carrier (DLC) systems

- PABX

# Description

The Agere Systems Inc. L8576B electronic dual subscriber line interface circuit (SLIC) provides all the functions that are necessary to interface a codec to the tip and ring of a subscriber loop, integrating two battery feeds and ringing generators in one low-cost package. The L8576B device is optimized to meet the needs of short loop, customer premises applications and features balanced ringing from the single battery supply. The device is built using a 90 V complementary bipolar (CBIC) process. It is available in a 44-pin PLCC package.

# **Table of Contents**

## Contents

# Page Figures

## Page

| Features                            | .1 |

|-------------------------------------|----|

| Applications                        | .1 |

| Description                         | .1 |

| Pin Information                     | .5 |

| Functional Description              | .7 |

| General                             | .7 |

| Protection                          | .7 |

| Tip/Ring Drivers                    | .7 |

| Battery Operation                   |    |

| Transmit and Receive Interface      | .7 |

| Data Interface                      | .8 |

| Loop Current Detector               | .8 |

| Operating States                    | .8 |

| Absolute Maximum Ratings            | .9 |

| Electrical Characteristics1         | 0  |

| Test Configurations 1               | 4  |

| Applications1                       |    |

| Characteristic Curves1              | 5  |

| dc Design1                          | 17 |

| Power Ringing1                      |    |

| ac Design1                          |    |

| Use of an Auxiliary Battery Supply2 |    |

| Outline Diagram2                    |    |

| 44-Pin PLCC2                        |    |

| Ordering Information                | 26 |

# Tables

## Page

| Table 1. Pin Descriptions                  | 5  |

|--------------------------------------------|----|

| Table 2. Input State Coding                | 9  |

| Table 3. Operating Conditions and Powering | 10 |

| Table 4. Ring Trip Detector                | 10 |

| Table 5. Battery Feed                      | 11 |

| Table 6. Analog Signal Pins                | 12 |

| Table 7. ac Feed Characteristics           | 12 |

| Table 8. Isolation Between Channels        | 13 |

| Table 9. Data Interface and Logic          | 13 |

| Figure 1. Architectural Diagram                          | 3   |

|----------------------------------------------------------|-----|

| Figure 2. Typical 600 $\Omega$ Application Circuit (Only |     |

| One Channel Shown)                                       | . 4 |

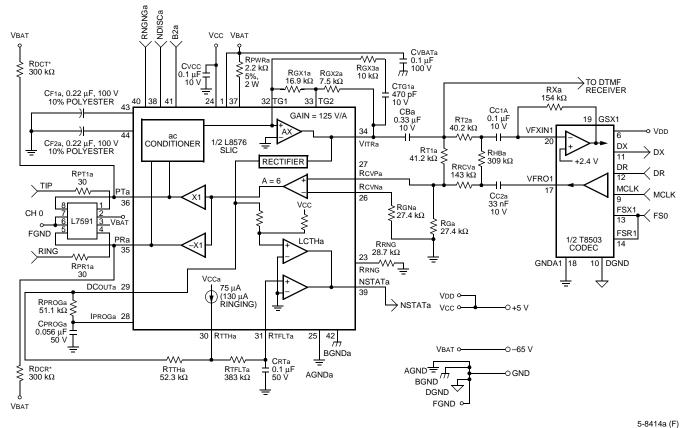

| Figure 3. 44-Pin PLCC Pin Diagram                        | 5   |

| Figure 4. Pretrip Circuit                                | 11  |

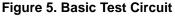

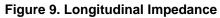

| Figure 5. Basic Test Circuit                             | 14  |

| Figure 6. Metallic PSRR                                  |     |

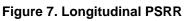

| Figure 7. Longitudinal PSRR                              | 14  |

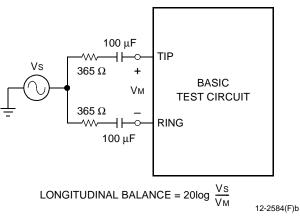

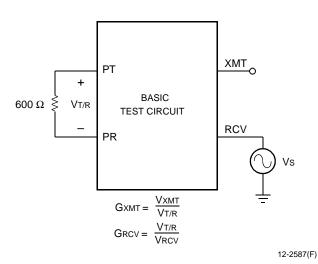

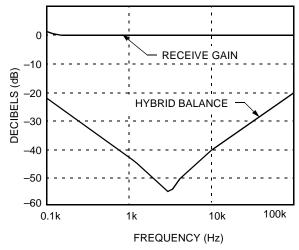

| Figure 8. Longitudinal Balance                           |     |

| Figure 9. Longitudinal Impedance                         | 15  |

| Figure 10. ac Gains                                      |     |

| Figure 11. Receive Gain and Hybrid Balance vs.           |     |

| Frequency                                                | 15  |

| Figure 12. Transmit Gain and Return Loss vs.             |     |

| Frequency                                                | 15  |

| Figure 13. Loop Current vs. Loop Voltage                 | 16  |

| Figure 14. Loop Current vs. Loop Resistance              | 16  |

| Figure 15. SLIC Power Dissipation vs. Loop               |     |

| Resistance (VBAT = -48 V)                                | 16  |

| Figure 16. SLIC Power Dissipation vs. Loop               |     |

| Resistance (VBAT = -65 V)                                | 16  |

| Figure 17. Loop Current vs. Loop Voltage                 | 17  |

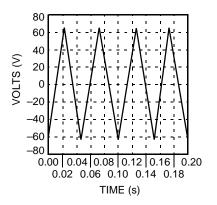

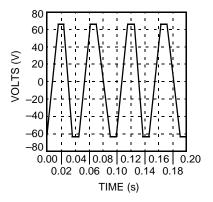

| Figure 18. Ringing Waveform Crest Factor = 1.6           | 18  |

| Figure 19. Ringing Waveform Crest Factor = 1.2           | 18  |

| Figure 20. ac Equivalent Circuit Using a T8503           |     |

| Codec                                                    | 20  |

| Figure 21. ac Interface Circuit Using First-             |     |

| Generation Codec (Blocking Capacitors                    |     |

| Not Shown)                                               | 22  |

| Figure 22. ac Interface Circuit Using First-             |     |

| Generation Codec (Including Blocking                     |     |

| Capacitors)                                              | 23  |

# **Description** (continued)

12-3362(F).c

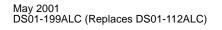

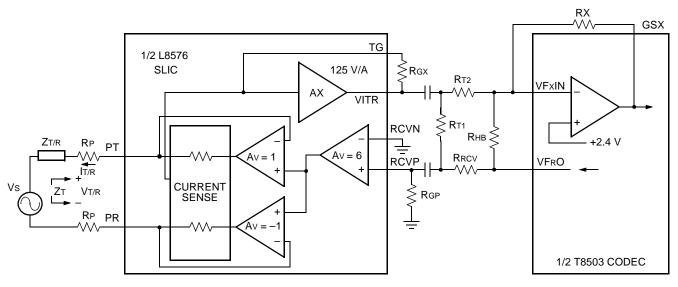

Figure 1. Architectural Diagram

# **Description** (continued)

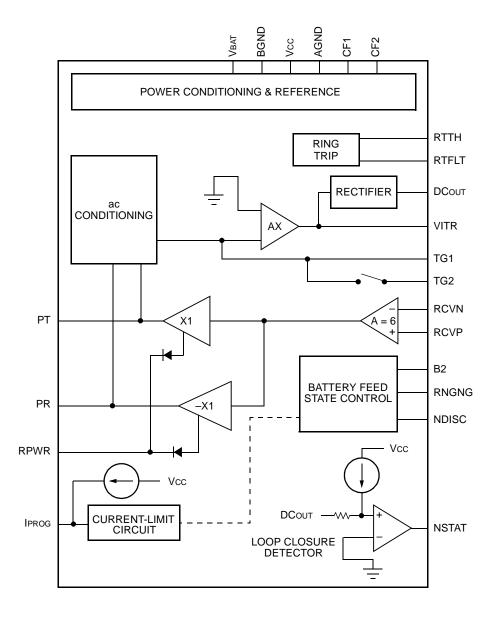

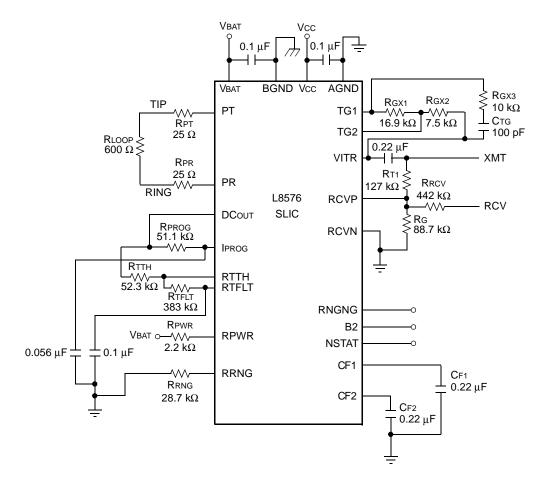

\* RDCT and RDCR (optional) are only required to keep the NSTAT output at a steady state during the disconnect state.

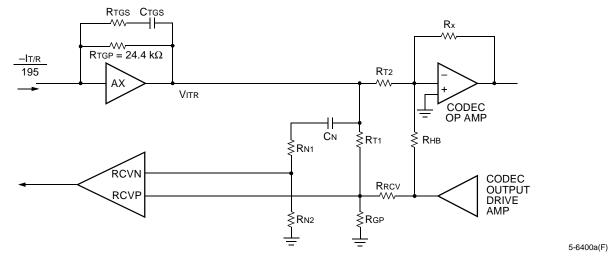

Notes: Tx = -2 dB. Rx = -4 dB.Termination = 600  $\Omega$ . Hybrid balance = 600  $\Omega$ . Ring trip optimized for 20 Hz.

#### Figure 2. Typical 600 $\Omega$ Application Circuit (Only One Channel Shown)

# **Pin Information**

#### Table 1. Pin Descriptions

| Pin,<br>Circuit<br>a | Pin,<br>Circuit<br>b | Symbol | Туре | Name/Function                                                                 |

|----------------------|----------------------|--------|------|-------------------------------------------------------------------------------|

| 1                    | 1                    | Vbat*  | _    | Office Battery Supply. Negative high-voltage power supply, nominally -65 V.   |

| 44                   | 2                    | CF2    | —    | Filter Capacitor 2. Connect 0.22 µF capacitor to AGND.                        |

| 43                   | 3                    | CF1    |      | Filter Capacitor 1. Connect 0.22 µF capacitor to AGND.                        |

| 42                   | 4                    | BGND*  | _    | Battery Ground. Ground return for the battery supply and fault ground.        |

| 41                   | 5                    | B2     | lu   | State Input. Refer to Operating States section. A pull-up device is included. |

\* On the printed-wiring board (PWB), make the leads to BGND and VBAT as wide as possible for thermal and electrical reasons. Also, maximize the amount of PWB copper on all leads connected to this device for the lowest operating temperature.

Note:  $I^{u}$  and  $O^{u}$  indicate a pull-up device is included on this lead.

12-3361(F).a

## Pin Information (continued)

| Table 1. Pin Descriptions (continued) |

|---------------------------------------|

|---------------------------------------|

| Pin,<br>Circuit<br>a | Pin,<br>Circuit<br>b | Symbol | Туре           | Name/Function                                                                                                                                                                                                                   |

|----------------------|----------------------|--------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40                   | 6                    | RNGNG  | lu             | <b>Ringing Input.</b> Refer to Operating States section. A pull-up device is included.                                                                                                                                          |

| 39                   | 7                    | NSTAT  | O <sup>u</sup> | <b>Loop Detector Output/Ring Trip Detector Output.</b> When low, this lead indicates an off-hook condition. When in ringing mode, a low output on this lead indicates a ring trip. A pull-up device is included.                |

| 38                   | 8                    | NDISC  | lu             | <b>Disconnect Input</b> . Refer to Operating States section. A pull-up device is included.                                                                                                                                      |

| 37                   | 9                    | RPWR   | —              | <b>Power Resistor.</b> Connect a resistor between this pin and VBAT. A 2.2 k $\Omega$ , 2 W resistor should be used for a VBAT of -68.5 V. See the Applications section to calculate resistor values for other VBAT potentials. |

| 36                   | 10                   | PT     | I/O            | <b>Protected Tip.</b> The input to the tip fault protection and output of tip current drive amplifier. Connect this pin to the tip of the loop through a 30 $\Omega$ overvoltage protection resistor.                           |

| 35                   | 11                   | PR     | I/O            | <b>Protected Ring.</b> The input to the ring fault protection and output of ring current drive amplifier. Connect this pin to the ring of the loop through a 30 $\Omega$ overvoltage protection resistor.                       |

| 34                   | 12                   | VITR   | 0              | <b>Transmit ac Output Voltage.</b> This output is a voltage that is directly proportional to the differential tip/ring current.                                                                                                 |

| 33                   | 13                   | TG2    | —              | <b>Transmit Gain 2.</b> Transmit gain and current limiting for ringing is set by the value of Rgx2. Rgx2 is connected between TG2 and VITR.                                                                                     |

| 32                   | 14                   | TG1    | —              | <b>Transmit Gain 1.</b> Transmit gain is set by the series resistor combination of Rgx1 and Rgx2 from this lead to TG2.                                                                                                         |

| 31                   | 15                   | RTFLT  | —              | <b>Ring Trip Filter.</b> Connect this lead to RTTH via a resistor and to AGND with a capacitor to filter the ring trip circuit to prevent spurious responses.                                                                   |

| 30                   | 16                   | RTTH   | —              | <b>Ring Trip Threshold.</b> Connect this lead to DCout via a resistor to set the ring trip threshold.                                                                                                                           |

| 29                   | 17                   | DCout  | 0              | <b>dc Voltage Out</b> . This output is a voltage that is directly proportional to the absolute value of the differential tip/ring current.                                                                                      |

| 28                   | 18                   | Iprog  | Ι              | <b>Current-Limit Program Input.</b> A resistor to DC <sub>OUT</sub> sets the dc current limit of the circuit.                                                                                                                   |

| 27                   | 19                   | RCVP   | Ι              | <b>Receive Signal Input (+).</b> This high-impedance input controls the ac differential voltage on tip/ring.                                                                                                                    |

| 26                   | 20                   | RCVN   | Ι              | <b>Receive Signal Input (–).</b> This high-impedance input controls the ac differential voltage on tip/ring.                                                                                                                    |

| 25                   | 21                   | AGND   | _              | Analog Signal Ground.                                                                                                                                                                                                           |

| 24                   | 22                   | Vcc    |                | Analog 5 V Power Supply.                                                                                                                                                                                                        |

| 23                   | 23                   | RRNG   |                | <b>Ringing Slope Resistor.</b> Connect this lead to AGND with a resistor to set the slope of the ringing waveform. Note that this pin is shared with both sections.                                                             |

\* On the printed-wiring board (PWB), make the leads to BGND and VBAT as wide as possible for thermal and electrical reasons. Also, maximize the amount of PWB copper on all leads connected to this device for the lowest operating temperature.

Note: I<sup>u</sup> and O<sup>u</sup> indicate a pull-up device is included on this lead.

# **Functional Description**

Refer to the architectural and application diagrams (Figures 1 and 2, respectively).

# General

The L8576B is a dual subscriber line interface circuit with each half of the device providing battery feed, supervision, and balanced ringing. It is designed to support short loops, typically on customer premises. The use of a single battery for both battery feed and ringing makes this device particularly advantageous where it is desirable to minimize power supply costs in small systems, such as terminal adapters. The tip and ring drive amplifiers are used with a very relaxed current limit to develop a trapezoidal, balanced ringing signal. Use of a nominal -65 V power supply allows for ringing of normal phones, whether equipped with a mechanical ringer, or a peak-detection type of ringing detector. While balanced ringing is not the norm worldwide, its use in short, customer premises loops is gaining popularity.

In addition to the ringing and battery functions, the L8576B device provides the ac receive and transmit paths. Also, integral within the device is an off-hook detection circuit and a ring trip detection circuit that have their outputs multiplexed on a single lead.

Thermal protection within the device is also provided, and an external resistor is used to drop the high battery voltage before applying loop current, thus allowing a significant portion of the power to be dissipated outside of the device. Removing much of this power makes it possible to incorporate two complete circuits in a 44-pin, surface-mount package.

## Protection

The L8576B contains some overvoltage protection in addition to the thermal protection within the device. This protection, along with the associated tip and ring protection resistors, may be sufficient in some benign environments. However, if power line cross or lightning protection is desired, the use of an external protection circuit (such as the L7591 device from Agere) is highly recommended.

The integrated thermal protection consists of a thermal shutdown circuit which places the tip/ring drivers in a high-impedance state when the temperature of the die exceeds 160 °C. In thermal shutdown, all supervision states are undefined.

# **Tip/Ring Drivers**

The L8576B has two tip/ring drivers whose outputs are PT and PR. Each driver operates as a current source capable of sinking or sourcing adequate ac signal bias current. In the normal talk operating mode, these drivers are current-limited at a nominal 24 mA to minimize the power dissipation of short loops. These amplifiers are also used to drive balanced ringing. During ringing, the current limit is raised to approximately 85 mA.

The external resistor connected to the RPWR pin is used to dissipate power externally and also to drop the battery voltage which is higher than normal in order to support balanced ringing. Note that this external power dissipation is present during both ringing or normal battery feed operation. Power limitations restrict the dual device to actively ringing only one channel at a time; thus, ringing cadence must be used to ensure that only one channel is actively ringing at any given instant of time. In other words, to ring both channels at the same time, ring each channel during the quiet interval of the other channel.

# **Battery Operation**

There are two VBAT inputs to the device. Pin 1 (VBAT) provides voltage to the entire SLIC and pins 9 and 37 (RPWR) provide voltage to the individual tip and ring amplifiers of each channel through RPWR resistors. A shared current sourcing scheme is employed within the device. For loop currents below 20 mA, the VBAT applied to pin 1 sources all of the loop current in addition to driving internal circuitry. For loop currents greater than 20 mA, loop current is primarily provided through the RPWR resistors and the pin 1 VBAT mainly powers internal circuitry. The RPWR resistors can be replaced by a lower-voltage auxiliary battery. Operation with an auxiliary battery is described in the Applications section of this document.

# **Transmit and Receive Interface**

The interface is suitable for direct coupling to a  $\pm 5$  V only codec. When interfacing a 5 V only codec, coupling capacitors are required.

The transmit interface circuitry couples the differential voltage on tip and ring to transmit output VITR. The inverting input of the driving amplifier is available on lead TG1, so connecting a resistance between VITR and TG1 allows adjustment of the transmit gain (transconductance).

# Functional Description (continued)

## Transmit and Receive Interface (continued)

A second gain setting is provided to accommodate ring trip. A switch is built into TG2. In ringing mode, TG1 and TG2 are internally connected, thus shorting out the external gain resistor RGX1. This provides a lower transmit gain for ringing since ring trip is accomplished by monitoring the voltage at DCout. This lower gain sets DCout at the appropriate level to accommodate the higher currents of the ring trip.

The receive interface circuitry couples the differential signal on receive inputs RCVP and RCVN to the tip/ring drivers.

## Data Interface

A 4-wire parallel interface (B2, RNGNG, NDISC, and NSTAT) is provided for each channel to control signals to and from the system controller. B2 controls the forward/reverse battery in normal talk mode while RNGNG enables the balanced ringing mode of operation, and NDISC performs a disconnect state. NSTAT reflects either the loop detector output or the ring trip detector output, depending on the mode of the section. It is the responsibility of the system controller to recognize ring trip detection and set RNGNG to a logic 0 state to terminate ringing. The system controller should also use RNGNG to set ringing cadence.

## **Loop Current Detector**

Each section of the device has an integral loop current detector set at a nominal 12 mA of dc current. This is used to detect off-hook transitions in the normal talk state. When current less than the current threshold (including no current) is flowing, NSTAT is at logic 1. When loop current exceeds 12 mA, the output NSTAT switches to a logic 0. No hysteresis is included.

# **Operating States**

The L8576B device has four operating states:

- Talk state—normal battery:

- Normal talk state.

- Battery feed is connected to the battery supply (VBAT).

- Both receive and transmit transmission paths are powered up.

- dc loop and instantaneous current limiters are powered up and active.

- NSTAT reflects the status of the switchhook detector.

- PR is negative with respect to PT.

- Talk state—reverse battery:

- Normal talk state.

- Battery feed is connected to the battery supply (VBAT).

- Both receive and transmit transmission paths are powered up.

- dc loop current limiter is powered up and active.

- NSTAT reflects the status of the switchhook detector.

- PR is positive with respect to PT.

- Ringing state:

- Normal ringing state.

- Both receive and transmit transmission paths are inactive.

- Balanced ringing is applied to PR and PT, in accordance with B2.

- Current limiter is set for ringing limit.

- NSTAT reflects the status of the ring trip detector.

- Only one channel should be in this state at a time to control power dissipation.

- Disconnect state:

- Tip and ring drive amplifiers are powered down.

- Pins PT and PR are high impedance (>100 k $\Omega$ ).

- NSTAT is undefined.

- PT and PR voltage is undefined.

# **Operating States** (continued)

These states are selected using three logic inputs, B2, RNGNG, and NDISC. B2 sets normal operation, either with forward or reverse battery. RNGNG overrides B2 and applies ringing with the polarity of tip and ring reversed on edges of the B2 signal. The slope of the waveform is determined by a resistor from RRNG to AGND. Logic input NDISC puts the device into a loop current denial state (disconnect). Tip and ring amplifiers are saturated against ground with about a 100  $\mu$ A current source. This creates a level in the loop current sensing circuitry that approaches a loop closed state. Some conditions on the tip and ring could cause the circuit to indicate loop closed even though the loop is open. This situation can be prevented by connecting a 300 k $\Omega$  resistor from VBAT to each of the outputs of the tip and ring amplifiers (see Figure 2). This will pull the amplifier output to about 30 V above VBAT, keeping the NSTAT output at a steady high (on-hook indication) level. If the disconnect state is not used or the NSTAT output during the disconnect state is not recognized or used, then the resistors are not needed.

Table 2 below summarizes the operating input state coding.

| NDISC | RNGNG | B2  | State                                                                                                                                                                               |

|-------|-------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | 0     | 1   | Forward Battery, Normal Talk, and Feed State. Pin PT is positive with respect to PR.                                                                                                |

| 1     | 0     | 0   | Reverse Battery, Normal Talk, and Feed State. Pin PT is negative with respect to PR.                                                                                                |

| 1     | 1     | 1↑  | <b>Ringing Is Applied to PT and PR.</b> On the transition, PT starts towards a positive volt-<br>age (with respect to PR). The endpoint of this state is PT at BGND and PR at VBAT. |

| 1     | 1     | 0↓  | <b>Ringing Is Applied to PT and PR.</b> On the transition, PT starts towards a negative voltage (with respect to PR). The endpoint of this state is PT at VBAT and PR at BGND.      |

| 0     | 0/1   | 0/1 | <b>Disconnect State.</b> The tip and ring amplifiers are turned off, and the SLIC goes into a high-impedance state (>100 k $\Omega$ ).                                              |

#### Table 2. Input State Coding

# **Absolute Maximum Ratings** (at TA = 25 °C)

Stresses in excess of the absolute maximum ratings can cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operational sections of the data sheet. Exposure to absolute maximum ratings for extended periods can adversely affect device reliability.

| Parameter                                  | Symbol | Min       | Тур | Max       | Unit |

|--------------------------------------------|--------|-----------|-----|-----------|------|

| 5 V dc Supplies                            | Vcc    | -0.5      |     | 7.0       | V    |

| Office Battery Supply                      | Vbat   | -75       |     | 0.5       | V    |

| Logic Input Voltage                        | —      | -0.5      |     | Vcc + 0.5 | V    |

| Logic Input Clamp Diode Current, per Pin   | —      | —         | ±20 | —         | mA   |

| Logic Output Voltage                       | —      | -0.5      | _   | Vcc + 0.5 | V    |

| Logic Output Current, per Pin              | —      | —         | ±35 | —         | mA   |

| Analog Input Voltage                       | —      | -7.0      | _   | 7.0       | V    |

| Maximum Junction Temperature               | —      | —         | 165 | —         | °C   |

| Storage Temperature Range                  | Tstg   | -40       |     | 125       | °C   |

| Relative Humidity Range (noncondensing)    | —      | 5         | _   | 95        | %    |

| Ground Potential Difference (BGND to AGND) | —      | —         | ±3  |           | V    |

| PT or PR Fault Voltage (dc)                | —      | Vват — 5  |     | 3         | V    |

| PT or PR Fault Voltage (10 µs x 1000 µs)   | —      | Vват – 15 | _   | 15        | V    |

Note: The IC can be damaged unless all ground connections are applied before, and removed after, all other connections. Furthermore, when powering the device, the user must guarantee that no external potential creates a voltage on any pin of the device that exceeds its ratings. For example, inductance in a supply lead could resonate with the supply filter capacitor to cause a destructive overvoltage.

# **Electrical Characteristics**

Generally, minimum and maximum values are testing requirements. However, some parameters may not be tested in production because they are guaranteed by design and device characterization. Typical values reflect the design center or nominal value of the parameter; they are for information only and are not a requirement. Minimum and maximum values apply across the entire temperature range (0 °C to 70 °C) and entire battery range (to -72 V). Unless otherwise specified, typical values are defined as 20 °C, Vcc = 5.0 V, V<sub>BAT</sub> = -68.5 V. Positive currents flow into the device.

| Table 3. O | perating | Conditions | and | Powering |

|------------|----------|------------|-----|----------|

|------------|----------|------------|-----|----------|

| Parameter                                            | Min              | Тур  | Max               | Unit |

|------------------------------------------------------|------------------|------|-------------------|------|

| Temperature Range                                    | 0                |      | 70                | °C   |

| Humidity Range                                       | 5                | —    | 95 <sup>1</sup>   | %RH  |

| Supply Voltages:                                     |                  |      |                   |      |

| Vcc                                                  | 4.75             | 5.0  | 5.25              | V    |

| VBAT                                                 | -24 <sup>2</sup> | -65  | -72               | V    |

| Loop Closure Threshold—Detection Range               | 9.5              | 12   | 14.5              | mA   |

| ac Termination Impedance Programming Range           | 300              | 600  | 1000 <sup>3</sup> | Ω    |

| On- and Off-hook 2-wire Signal Level                 | —                | 3.14 | —                 | dBm  |

| Power Supply—Powerup, No Loop Current (per section): |                  |      |                   |      |

| lcc                                                  | —                | 4.5  | 5.5               | mA   |

| Ibat (Vbat = $-65$ V)                                | —                | 3.0  | 4.0               | mA   |

| Total power (one channel, $VBAT = -65 V$ )           | —                | 230  | 290               | mW   |

| Power-supply Rejection (See Figures 6 and 7.):       |                  |      |                   |      |

| Vcc (1 kHz)                                          | 35               | —    | —                 | dB   |

| Vbat (500 Hz—3 kHz)                                  | 45               | —    | —                 | dB   |

| Thermal <sup>4</sup> :                               |                  |      |                   |      |

| Thermal Resistance (still air) Tj                    | —                | 47   | —                 | °C/W |

| Operating T <sub>j</sub>                             | —                | —    | 150               | °C   |

| Thermal Shutdown Temperature                         | —                | 160  | —                 | °C   |

1. Noncondensing.

2. The L8576B will operate below -24 V; -24 V is used for production test.

3. The termination impedance can be programmed up to 1200  $\Omega$ ; 1000  $\Omega$  are used for production test.

4. This parameter is not tested in production. It is guaranteed by design and device characterization.

#### Table 4. Ring Trip Detector<sup>1</sup>

| Parameter <sup>2</sup>                                                                                           | Min | Тур | Max | Unit  |

|------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Ringing Source:                                                                                                  |     |     |     |       |

| Frequency (f) RRNG = 28.7 k $\Omega$ , RTTH = 52.3 k $\Omega$                                                    | 17  | 20  | 23  | Hz    |

| Frequency (f) Contact Agere for Specific Component Values                                                        | 20  | —   | 50  | Hz    |

| C-message Weighted Noise (900 $\Omega$ )                                                                         | _   | _   | 90  | dBrnC |

| REN Load (1386 $\Omega$ + 40 $\mu$ F) with Loop Resistance = 30 $\Omega$ , RPT = 30 $\Omega$ , RPR = 30 $\Omega$ | _   | _   | 40  | Vrms  |

| Detection Interval:                                                                                              |     |     |     |       |

| 20 Hz                                                                                                            | —   | —   | 200 | ms    |

| ≥25 Hz                                                                                                           | —   | —   | 150 | ms    |

1. This table is provided for information purposes only.

2. These parameters are not tested in production.

10

## Electrical Characteristics (continued)

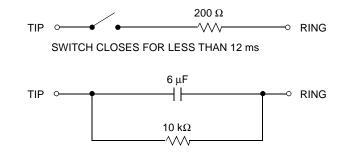

Pretrip will not occur for the circuits shown below, per GR-909, 4.5.9.

12-2572(F).d

#### Figure 4. Pretrip Circuit

#### Table 5. Battery Feed

| Parameter                                                                      | Min       | Тур | Max | Unit  |

|--------------------------------------------------------------------------------|-----------|-----|-----|-------|

| Loop Resistance Range <sup>1</sup>                                             |           |     |     |       |

| (3.17 dBm overload into 600 $\Omega$ ):                                        |           |     |     |       |

| $I_{LOOP} = 20 \text{ mA at } V_{BAT} = -65 \text{ V}$                         | 1000      | _   | —   | Ω     |

| Longitudinal Current Capability per Wire <sup>2</sup>                          | 8.5       | 15  |     | mArms |

| Current Limit <sup>3</sup> RLOOP = 100 $\Omega$ :                              |           |     |     |       |

| dc Loop                                                                        | 20        | 24  | 28  | mA    |

| Instantaneous <sup>4</sup>                                                     | 50        | 60  | 70  | mA    |

| Tip or Ring Drive Current = dc + Longitudinal + Signal Currents                | 65        | _   | _   | mA    |

| Signal Current                                                                 | 5         | _   |     | mArms |

| Powerup Open Loop Voltage Level                                                | Vbat + 10 |     |     | V     |

| Differential Voltage (RNGNG = 0, NDISC = 1, B2 = 1,                            |           |     |     |       |

| Vbat = -65 V)                                                                  |           |     |     |       |

| Disconnect State:                                                              |           |     |     |       |

| PT or PR Current (VBAT < VPT < 0 V)                                            | -1        |     | 1   | mA    |

| PT or PR Resistance (VBAT < VPT < 0 V)                                         | 100       | —   | —   | kΩ    |

| dc Feed Resistance                                                             | —         | 60  | 70  | Ω     |

| Longitudinal to Metallic Balance—IEEE <sup>5</sup> Standard 455 <sup>6</sup> : |           |     |     |       |

| 200 Hz to 1 kHz                                                                | 54        | 67  | —   | dB    |

| 1 kHz to 3 kHz                                                                 | 48        | 62  | —   | dB    |

| Metallic to Longitudinal (Harm) Balance <sup>7</sup> :                         |           |     |     |       |

| 200 Hz to 4 kHz                                                                | 35        | —   |     | dB    |

1. Assumes 2 x 30  $\Omega$  external protection resistors. Note the useful range of the device may be determined by the ringing or supervision range rather than the ac characteristics.

2. The longitudinal current is independent of dc loop current.

3. Current limit ILIM is programmed by a resistor, RPROG, from pin IPROG to pin DCout RPROG ( $k\Omega$ ) = 3.5 x (ILIM – 9.2) mA. The current limit has a slope vs. loop voltage of 6 k $\Omega$ . To control power dissipation, it is recommended that the default current limits be utilized, i.e., RPROG = 51.1 k $\Omega$  for 24 mA nominal loop current limit.

4. Instantaneous current limit minimizes inrush current at the onset of an off-hook condition. Inrush current is only limited when in the forward battery state. The device will settle into a dc loop current-limit value within 400 ms after off-hook.

5. IEEE is a registered trademark of The Institute of Electrical and Electronics Engineers, Inc.

6. Assumes the external protection resistors are matched to 1%.

7. This parameter is not tested during production. It is guaranteed by design and device characterization.

# Electrical Characteristics (continued)

#### Table 6. Analog Signal Pins

| Parameter                                                         | Min    | Тур  | Max    | Unit |

|-------------------------------------------------------------------|--------|------|--------|------|

| Differential PT/PR Current Sense (DCout)                          |        |      |        |      |

| Gain (PT/PR to DCout):                                            |        |      |        |      |

| Forward Battery (Rgx1 = 16.9 k $\Omega$ , Rgx2 = 7.5 k $\Omega$ ) | -235   | -250 | -265   | V/A  |

| Reverse Battery (Rgx1 = 16.9 k $\Omega$ , Rgx2 = 7.5 k $\Omega$ ) | 235    | 250  | 265    | V/A  |

| PT/PR to VITR Gain with                                           |        |      |        |      |

| Rgx1 = 16.9 kΩ, Rgx2 = 7.5 kΩ:                                    |        |      |        |      |

| Forward Battery                                                   |        | -125 | -129   | V/A  |

| Reverse Battery                                                   | 121    | 125  | 129    | V/A  |

| Loop Closure Detector Threshold:                                  |        |      |        |      |

| Programming Accuracy                                              | —      | —    | ±20    | %    |

| RCVN, RCVP:                                                       |        |      |        |      |

| Input Bias Current                                                |        | —    | -1.0   | μΑ   |

| Gain RCVP to PT/PR                                                | 11.62  | 12   | 12.38  | —    |

| Gain RCVN to PT/PR                                                | -11.62 | -12  | -12.38 | —    |

| RCVN, RCVP Input Compliance                                       | -2.5   |      | Vcc    | V    |

#### Table 7. ac Feed Characteristics

| Parameter <sup>1</sup>                                                    |       | Тур  | Max  | Unit |

|---------------------------------------------------------------------------|-------|------|------|------|

| ac Termination Impedance <sup>2</sup>                                     | 300   | 600  | 1000 | Ω    |

| Total Harmonic Distortion (200 Hz—4 kHz) <sup>3</sup> :                   |       |      |      |      |

| Off-hook                                                                  | —     | —    | 0.3  | %    |

| On-hook                                                                   | —     | —    | 1.0  | %    |

| Transmit Gain ( $f = 1 \text{ kHz}$ ) (See Figure 5.):                    |       |      |      |      |

| Transmit Accuracy in Percent                                              | -3.0  | 0    | 3.0  | %    |

| Transmit Accuracy in dB (relative to 2/3)                                 | -0.24 | 0    | 0.24 | dB   |

| Receive Gain ( $f = 1 \text{ kHz}$ ) (See Figure 5.):                     |       |      |      |      |

| Receive Accuracy in Percent                                               | -3.0  | 0    | 3.0  | %    |

| Receive Accuracy in dB                                                    |       | 0    | 0.24 | dB   |

| Tip/Ring Signal Level (600 Ω reference)                                   |       |      | 3.14 | dBm  |

| Gain vs. Frequency (transmit and receive; 1 kHz reference) <sup>3</sup> : |       |      |      |      |

| 200 Hz—3.4 kHz                                                            |       | 0    | 0.05 | dB   |

| 300 Hz—3.4 kHz                                                            | -0.30 | 0    | 0.05 | dB   |

| 3.4 kHz—20 kHz                                                            |       | -0.1 | 2.0  | dB   |

| 3.4 kHz—266 kHz                                                           |       | —    | 2.0  | dB   |

1. Requires external components connected as shown in the Applications section. Transmission characteristics are specified assuming a 600 Ω resistive termination and ±1% external resistors.

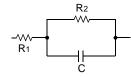

2. Transmission characteristics are specified assuming a 600  $\Omega$  resistive termination; however, feedback using external components allows the user to adjust the termination impedance from 600  $\Omega$ . Any complex impedance R1 + R2 || C between 300  $\Omega$  and 1000  $\Omega$  can be synthesized using external components.

3. This parameter is not tested in production. It is guaranteed by design and device characterization.

# Electrical Characteristics (continued)

#### Table 7. ac Feed Characteristics (continued)

| Parameter <sup>1</sup>                                                |       | Тур | Max  | Unit   |

|-----------------------------------------------------------------------|-------|-----|------|--------|

| Gain vs. Level (transmit and receive; 0 dBV reference) <sup>2</sup> : |       |     |      |        |

| –50 dB to +3 dB                                                       | -0.05 | 0   | 0.05 | dB     |

| Return Loss <sup>3</sup> :                                            |       |     |      |        |

| 200 Hz—500 Hz                                                         | 20    | 24  | —    | dB     |

| 500 Hz—3400 Hz                                                        | 26    | 29  | —    | dB     |

| Transhybrid Loss <sup>3</sup> :                                       |       |     |      |        |

| 200 Hz—500 Hz                                                         | 20    | 24  | —    | dB     |

| 500 Hz—2500 Hz                                                        | 26    | 29  | —    | dB     |

| 2500 Hz—3400 Hz                                                       | 26    | 29  | —    | dB     |

| Idle-channel Noise (Tip/Ring):                                        |       |     |      |        |

| Psophometric <sup>2</sup>                                             | —     |     | -77  | dBmp   |

| C-message                                                             | —     |     | 12   | dBrnC  |

| 3 kHz Flat <sup>2</sup>                                               | —     | —   | 20   | dBrn   |

| Idle-channel Noise (XMT):                                             |       |     |      |        |

| Psophometric <sup>2</sup>                                             | —     | _   | -77  | dBmp0  |

| C-message                                                             | —     |     | 12   | dBrnC0 |

| 3 kHz Flat <sup>2</sup>                                               | —     | —   | 20   | dBrn0  |

1. Requires external components connected as shown in Figure 2. Transmission characteristics are specified assuming a 600  $\Omega$  resistive termination and ±1% external resistors.

2. This parameter is not tested in production. It is guaranteed by design and device characterization.

3. Return loss and transhybrid loss are functions of device gain accuracies and the external hybrid circuit. Guaranteed performance assumes 1% tolerance components.

#### **Table 8. Isolation Between Channels**

| Parameter <sup>1</sup>                                                                                                                            | Min | Тур | Max | Unit   |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|--------|

| Interchannel Small-signal Crosstalk. (Both channels in forward or reverse battery state.) (2-wire to 2-wire, 2-wire to 4-wire, 4-wire to 4-wire.) | —   | -90 | -80 | dB     |

| Impulse Noise. (One channel ringing, other channel in forward or reverse battery state.)                                                          | _   | 40  | 47  | dBrnC0 |

1. These parameters are not tested in production. They are guaranteed by design and device characterization.

#### Table 9. Data Interface and Logic

| Parameter <sup>1</sup>                                                                                 |     | Min | Тур | Max  | Unit |

|--------------------------------------------------------------------------------------------------------|-----|-----|-----|------|------|

| High-level Input Voltage (B2, RNGNG, and NDISC)                                                        | Vін | 2   | _   | Vcc  | V    |

| Low-level Input Voltage (B2, RNGNG, and NDISC)                                                         |     | 0   | _   | 0.7  | V    |

| Input Bias Current (high) (B2, RNGNG, and NDISC)                                                       |     | -40 | _   | -100 | μΑ   |

| Input Bias Current (low) (B2, RNGNG, and NDISC)                                                        |     | -75 |     | -200 | μΑ   |

| High-level Output Voltage (NSTAT, open collector with inter-<br>nal pull-up resistor):                 |     |     |     |      |      |

| (lout = -20 μA)                                                                                        | Vон | 2.4 | 4.3 | Vcc  | V    |

| $(IOUT = -1 \ \mu A)$                                                                                  | Vон | —   | 5.0 | _    | V    |

| Low-level Output Voltage (NSTAT, open collector with internal pull-up resistor) (Iout = $200 \ \mu$ A) | Vol | 0   | 0.2 | 0.4  | V    |

1. All logic voltages are referenced to AGND.

# **Test Configurations**

12-3360(F)a

Figure 6. Metallic PSRR

# Test Configurations (continued)

Figure 10. ac Gains

# Applications

# **Characteristic Curves**

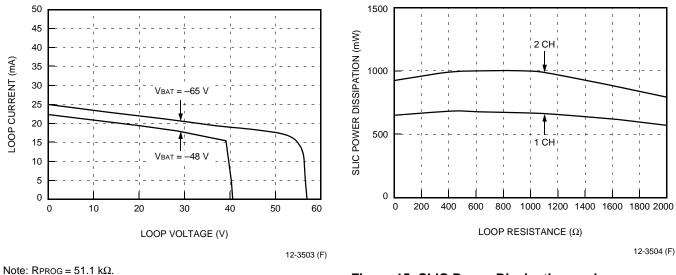

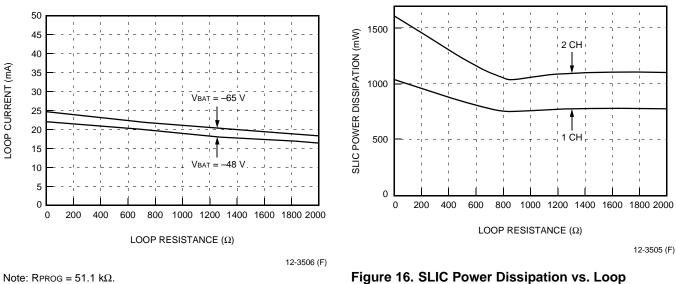

Figures 11—16 display typical room temperature readings.

12-3507(F)

Note: Gain is normalized to 0 dB.

#### Figure 11. Receive Gain and Hybrid Balance vs. Frequency

Note: Gain is normalized to 0 dB.

Figure 12. Transmit Gain and Return Loss vs. Frequency

## Characteristic Curves (continued)

Figure 13. Loop Current vs. Loop Voltage

Figure 14. Loop Current vs. Loop Resistance

Figure 15. SLIC Power Dissipation vs. Loop Resistance (VBAT = -48 V)

Resistance (VBAT = -65 V)

50

45

40

35

30

25 20

15

10

5

0

0

LOOP CURRENT (mA)

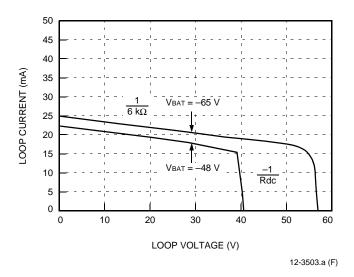

#### dc Design

#### **Battery Feed**

The dc feed characteristic can be described by:

$$V_{T/R} = \frac{(|V_{BAT}| - V_{OH}) \times R_L}{R_L + 2R_P + R_{dc}}$$

$$I_L = \frac{|V_{BAT}| - V_{OH}}{R_L + 2R_P + R_{dc}}$$

Where:

$I_{L} = dc loop current.$

$V_{T/R} = dc loop voltage.$

|VBAT| = battery voltage magnitude.

VoH = overhead voltage. This is the difference between the battery voltage and the open loop tip/ring voltage.

RL = loop resistance, not including protection resistors.

$R_P$  = protection resistor value.

$R_{dc} = SLIC$  internal dc feed resistance.

The design begins by drawing the desired dc template. An example is shown in Figure 17.

Figure 17. Loop Current vs. Loop Voltage

Starting from the on-hook condition and going through to a short circuit, the curve passes through two regions:

Region 1: On-hook and low loop currents. In this region, the slope corresponds to the dc resistance of the SLIC, Rdc (typically 60  $\Omega$ ). The open circuit voltage is the battery voltage less the overhead voltage of the device, VoH (default is 7.1 V typical). These values are suitable for most applications.

Agere Systems Inc.

Region 2: Current limit. The dc current is limited to a value determined by external resistor R<sub>PROG</sub>. This region of the dc template has a high resistance (6 k $\Omega$ ).

Calculate the external resistor as follows:

$$\mathsf{R}_{\mathsf{PROG}}(\mathsf{k}\Omega) = 3.5 \text{ x} (\mathsf{I}_{\mathsf{LIM}} - 9.2) \text{ mA}^*$$

To control power dissipation, it is recommended that a 51.1 k $\Omega$  RPROG resistor be used to set a default currentlimit value of 24 mA.

#### Rpwr

The RPWR resistors dissipate the excess power associated with a single power supply, short-loop application. The resistor provides VBAT to tip and ring amplifiers. There is one resistor associated with each channel. The value of RPWR is dependent upon the battery potential and the current-limit value. The value of RPWR can be determined by using the following equation:

$$\mathsf{R}_{\mathsf{PWR}} = \frac{|\mathsf{V}_{\mathsf{BAT}}| - 22.3}{\mathsf{I}_{\mathsf{LIM}} - 0.003}$$

Power dissipation of the resistor is:

$W_{RPWR} = (I_{LIM} - 0.003)^2 R_{PWR}.$

For the recommended –68.5 V VBAT and 24 mA ILIM design, a 2.2 k $\Omega$ , 2 W resistor is suitable. 2 W resistors are available as surface-mount components.

#### **Overhead Voltage**

In order to drive an on-hook ac signal, the SLIC must set up the tip and ring voltage to a value less than the battery voltage. The amount that the open loop voltage is decreased relative to the battery is referred to as the overhead voltage and is expressed as:

$$VOH = |VBAT| - (VPT - VPR)$$

Without this buffer voltage, amplifier saturation will occur and the signal will be clipped. The L8576 is automatically set at the factory to allow undistorted on-hook transmission of a 3.17 dBm signal into a 900  $\Omega$  loop impedance.

The drive amplifiers are capable of 4 Vrms minimum (VAMP). So, the maximum signal the device can guarantee is:

$$V_{T/R} = 4 V \left( \frac{|Z_{T/R}|}{|Z_{T/R}| + 2R_P} \right)$$

For normal forward or reverse battery operation, overhead voltage is internally set to about 8 V. In ringing mode, the overhead voltage is automatically decreased to about 4 V to permit passage of a larger ring signal.

<sup>\*</sup> During the balanced ringing mode, the current limit is increased from the value predicted by this equation by a factor of 3.5.

# dc Design (continued)

## **Off-Hook Detection**

The loop closure comparator has built-in longitudinal rejection, eliminating the need for an external 60 Hz filter. The loop closure detection threshold is internally set at 12 mA.

# **Power Ringing**

The L8576B is designed to generate a balanced trapezoidal power ring signal to tip and ring. Because the L8576B generates the power ringing signal, no ring relay is needed in this mode of operation. Alternatively, the L8576B SLIC can be used in a battery-backed, unbalanced ringing application. In this case, the ring signal is generated by a central ring generator and is bused to individual tip/ring pairs. A ringing relay is used during ringing to disconnect the L8576B from, and apply the ring generator to, the tip and ring pair.

This section discusses in detail the use of the L8576B in the balanced mode of operation.

## **Crest Factor**

The balanced ring signal is generated by simply toggling between the powerup forward and reverse battery states. The state change is done by applying a square wave (whose frequency is the desired ring frequency) to logic input B2. Capacitors CF1 and CF2 and resistor RRNG are used to control or ramp the speed of the transition of the battery reverse, thus shaping the balanced ring signal. Setting capacitor CF1 = CF2 =  $0.22 \,\mu\text{F}$  and setting RRNG to 28.7 k $\Omega$  provides a crest factor of 1.3 for a 20 Hz ring frequency. This satisfies the Telcordia\* GR-909 requirement of ringing waveform crest factor between 1.2 and 1.6. Crest factor is defined as the peak to rms voltage ratio of the ring signal. Ringing waveforms of crest factors 1.6 and 1.2 are shown in Figures 18 and 19. The crest factor can be adjusted by the value of RRNG and will be influenced slightly by the value of VBAT. The CF1 and CF2 capacitors should not be changed because these affect the dc feedback loop stability in current limit. An RRNG value of 22.6 kΩ will lower the crest factor to about 1.2 with a -65 V or -72 V battery for a 20 Hz ring frequency. Likewise, an RRNG value of 34.8 k $\Omega$  will raise the crest factor to about 1.4. For ring frequencies greater than 20 Hz, the RRNG value should be lowered until the desirable crest factor is achieved. Note the RRNG is common to both sections of the device.

CF1 and CF2 must exhibit a stable capacitance value over its voltage range to ensure a properly shaped waveform. Do not use a ceramic capacitor for CF1 and CF2; use a capacitor with a polyester, polypropylene, polycarbonate, or polystyrene dielectric.

12-3346a (F)

Notes: Slew rate = 5.65 V/ms. trise = tfall = 23 ms. pwidth = 2 ms. period = 50 ms.

#### Figure 18. Ringing Waveform Crest Factor = 1.6

12-3347a (F)

Notes: Slew rate = 10.83 V/ms. trise = tfall = 12 ms. pwidth = 13 ms. period = 50 ms.

#### Figure 19. Ringing Waveform Crest Factor = 1.2

\* Telcordia is a registered trademark of Telcordia Technologies, Inc.

## Power Ringing (continued)

#### **Power Ringing Load**

Telcordia GR-909 specifies that a minimum 40 Vrms must be delivered to a 5 REN ringing load of 1386  $\Omega$  + 40  $\mu$ F. For 5 REN load, it is recommended that VBAT be set to -68.5 Vdc. During the power ring state, the dc current limit is automatically boosted by a factor of 3.5 over the current limit set by resistor RPROG. Both of these factors are necessary to ensure delivery of 40 Vrms to the North American 5 REN ringing load of 1386  $\Omega$  + 40  $\mu$ F.

## **Ring Trip**

Ring trip is accomplished by filtering the voltage seen at node DCout and applying it to the integrated ring trip comparator. DCout is a voltage proportional to the tip/ ring current, and under short dc loop conditions, onhook ringing current and off-hook current provide sufficient voltage differential at DCout to distinguish that a ring trip condition has occurred. The ring trip comparator threshold is set via a resistor between the ring trip comparator and DCout.

The output of NSTAT is automatically set to detect ring trip during the balanced ring mode. During quiet intervals of ringing, the output of NSTAT is automatically determined by the loop closure detector.

Refer to Figure 2 for the following discussion.

Capacitor CRT in conjunction with resistor RTFLT form a single-pole, low-pass filter that smooths the voltage seen at DCout. The pole of the filter will influence both the ripple seen at DCout and the speed of the transition of the voltage at DCout from the pretrip to the tripped level.

To determine the low-pass pole:

$$f(Hz) = \frac{1}{2\pi(RTFLT)(CRT)}$$

Using the recommended 383 k $\Omega$  RTFLT resistor and the 0.1  $\mu F$  CRT capacitor, the low-pass pole is set at 4.15 Hz.

The loop current at ring trip is given by:

$$I_{LOOP(TRIP)} = 7.76 \text{ mA} \left( \frac{\text{RTTH}}{\text{Rgx2}} \right)$$

Using the recommended 52.3 k $\Omega$  RTTH resistor and the 7.5 k $\Omega$  RGx<sub>2</sub> resistor in a 20 Hz ringing application, the ring trip threshold current is set for 54 mA.

#### **Reference Design for ISDN TA Applications**

For a complete reference design, please refer to the *POTS for ISDN, WLL, and FITL/FITH Applications, Featuring Ringing SLIC Solutions* Application Note, which provides a detailed discussion of the reference design functionality. The design presented utilizes a dc to dc converter and requires only a +5 V and a +12 V supply to operate. The schematic in Figure 2 of this document portrays the SLIC and codec portions of that design.

## ac Design

There are four key ac design parameters. **Termination impedance** is the impedance looking into the 2-wire port of the line card. It is set to match the impedance of the telephone loop in order to minimize signal reflections back to the telephone set. **Transmit gain** is measured from the 2-wire port to the PCM highway, while **receive gain** is measured from the PCM highway to the 2-wire port or telephone loop. Finally, the **hybrid balance** circuit cancels the unwanted amount of the received signal that appears at the transmit port.

May 2001

# Applications (continued)

# ac Design (continued)

# **Example 1, Real Termination**

The following design equations refer to the circuit in Figure 20. Use these to synthesize real termination impedance.

## **Termination impedance:**

$$Z_{t} = \frac{V_{T/R}}{-I_{T/R}}$$

$$Z_{t} = 2R_{P} + \frac{1500}{1 + \frac{R_{T1}}{R_{GP}} + \frac{R_{T1}}{R_{RCV}}}$$

**Receive gain:**

$$G_{RCV} = \frac{V_{T/R}}{V_{FRO}}$$

$$G_{RCV} = \frac{12}{\left(1 + \frac{R_{RCV}}{R_{T1}} + \frac{R_{RCV}}{R_{GP}}\right)\left(1 + \frac{Z_t}{Z_{T/R}}\right)}$$

Transmit gain:

$$G_{TX} = \frac{V_{GSX}}{V_{T/R}}$$

$$G_{TX} = \frac{R_X}{R_{T2}} \times \frac{125}{Z_{T/R}}$$

Hybrid balance:

$$h_{\text{bal}} = 20 \text{log} \left( \frac{\text{VGSX}}{\text{VT/R}} \right)$$

To optimize the hybrid balance, the sum of the currents at the VFxIN input of the codec op amp should be set to 0. The following expressions assume the hybrid balance network is the same as the termination impedance:

$$\mathsf{R}_{\mathsf{H}\mathsf{B}} = \frac{\mathsf{R}_{\mathsf{X}}}{\mathsf{G}_{\mathsf{R}\mathsf{C}\mathsf{V}} \times \mathsf{G}_{\mathsf{T}\mathsf{X}}}$$

$$h_{\text{bal}} = 20 \log \left( \frac{Rx}{R_{\text{HB}}} - G_{\text{RCV}} \times G_{\text{T}x} \right)$$

12-2554.0 (F)

Figure 20. ac Equivalent Circuit Using a T8503 Codec

ac Design (continued)

#### **Example 2, Complex Termination**

The gain shaping required of a complex termination impedance can be synthesized using the internal AX amplifier. The following discussion and equations present a method for selecting proper component values for the SLIC/codec interface when using a complex termination.

Complex termination is usually of the form:

5-6396(F)

To work with this application, convert termination to the form:

5-6397(F)

where:

$R_1' = R_1 + R_2$

$$R_2' = \frac{R_1}{R_2} (R_1 + R_2)$$

$$C' = \left(\frac{R_2}{R_1 + R_2}\right)^2 C$$

For the following discussion, refer to Figure 21.

RTGP/RTGS/CTGS (ZTG): These components give gain shaping to get good gain flatness. These components are a scaled version of the specified complex termination impedance. Note for pure (600  $\Omega$ ) resistive terminations, components RTGS and CTGS are not used. Resistor RTGP is used and is the series resistance combination of RGX1 and RGX2 or 24.4 k $\Omega$ .  $Rx/RT_2$ : With other components set, the transmit gain (for complex and resistive terminations) Rx and  $RT_2$  are varied to give specified transmit gain.

RT1/RRCV/RGP: For both complex and resistive terminations, the ratio of these resistors set the receive gain. For resistive terminations, the ratio of these resistors set the return loss characteristic. For complex terminations, the ratio of these resistors set the low-frequency return loss characteristic.

CN/RN1/RN2: For complex terminations, these components provide high-frequency compensation to the return loss characteristic. For resistive terminations, these components are not used. RCVN is connected to ground via a resistor.

RHB: Sets hybrid balance for all terminations.

#### **Set Z**TG — gain shaping:

ZTG = RTGP || RTGS + CTGS which is a scaled version of ZT/R (the specified termination resistance) in the R1' || R2' + C' form.

$\mathsf{R}_{\mathsf{TGP}}$  must be 24.4 k $\Omega$  to set SLIC transconductance to 125 V/A.

$R_{TGP} = 24.4 \ k\Omega$

At dc, CTGS and C' are open.

$R_{TGP} = M \times R1'$

where M is the scale factor.

$$M = \frac{24.4 \text{ k}\Omega}{\text{R}_{1'}}$$

It can be shown:

RTGS = M x R2'

and

$$C_{TGS} = \frac{C'}{M}$$

## ac Design (continued)

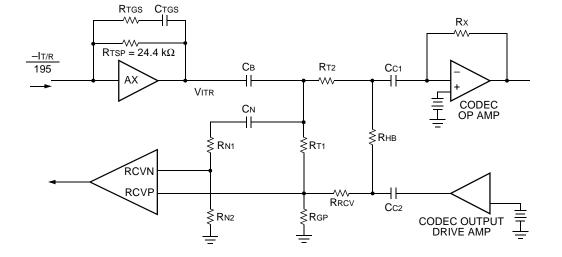

Figure 21. ac Interface Circuit Using First-Generation Codec (Blocking Capacitors Not Shown)

#### **Transmit Gain**

Transmit gain will be specified as a gain from T/R to PCM, Tx (dB). Since PCM is referenced to 600  $\Omega$  and assumed to be 0 dB, and in the case of T/R being referenced to some complex impedance other than 600  $\Omega$  resistive, the effects of the impedance transformation must be taken into account.

Again specified complex termination impedance at T/R is of the form:

5-6396(F)

First calculate the equivalent resistance of this network at the midband frequency of 1000 Hz.

Req =

$$\sqrt{\left(\frac{(2 \pi f)^2 C 1^2 R 1 R 2^2 + R 1 + R 2}{1 + (2 \pi f)^2 R 2^2 C 1^2}\right)^2 + \left(\frac{2 \pi f R 2^2 C 1}{1 + (2 \pi f)^2 R 2^2 C 1^2}\right)^2}$$

Using REQ, calculate the desired transmit gain, taking into account the impedance transformation:

Tx (dB) = Tx (specified[dB]) + 20log  $\sqrt{\frac{600}{REQ}}$

$T_{X (specified[dB])}$  is the specified transmit gain. 600  $\Omega$  is the impedance at the PCM and REQ is the impedance at

the T/R. 20log  $\sqrt{\frac{600}{R_{EQ}}}$  represents the power loss/gain

due to the impedance transformation.

Note in the case of a 600  $\Omega$  pure resistive termination

at T/R 20log

$$\sqrt{\frac{600}{\text{REQ}}} = 20 \log \sqrt{\frac{600}{600}} = 0$$

Thus, there is no power loss/gain due to impedance transformation and Tx (dB) = Tx (specified[dB]).

Finally, convert Tx (dB) to a ratio, GTx:

$$Tx (dB) = 20 \log GTx$$

The ratio of  $Rx/R_{T2}$  is used to set the transmit gain:

$$\frac{Rx}{R_{T2}} = G_{TX} x \frac{195}{M}$$

with a dual Agere codec such as T8503

$$Rx < 200 \ k\Omega$$

#### ac Design (continued)

#### **Receive Gain**

Ratios of RRCV, RT1, RGP will set both the low-frequency termination and receive gain for the complex case. In the complex case, additional high-frequency compensation, via CN, RN1, and RN2, is needed for the return loss characteristic. For resistive termination, CN, RN1, and RN2 are not used and RCVN is tied to ground and a resistor.

Determine the receive gain, GRCV, taking into account the impedance transformation in a manner similar to transmit gain.

Rx (dB) = Rx (specified[dB]) + 20log

$$\sqrt{\frac{\text{REQ}}{600}}$$

$Rx (dB) = 20 \log GRCV$

Then:

$$G_{RCV} = \frac{6}{1 + \frac{R_{RCV}}{R_{T1}} + \frac{R_{RCV}}{R_{GP}}}$$

and low-frequency termination

$$Z_{\text{TER(low)}} = \frac{1500}{1 + \frac{R_{\text{T1}}}{R_{\text{GP}}} + \frac{R_{\text{T1}}}{R_{\text{RCV}}}} + 2R_{\text{P}}$$

ZTER(low) is the specified termination impedance assuming low frequency (C or C´ is open).

RP is the series protection resistor.

These two equations are best solved using a computer spreadsheet.

Next, solve for the high-frequency return loss compensation circuit, CN, RN1, and RN2:

$$C_{N X} R_{N2} = \frac{2R_{P}}{1500} C_{TGS X} R_{TGP}$$

$$R_{N1} = R_{N2} \left[ \frac{1500}{2R_{P}} \left( \frac{R_{TGS}}{R_{TGP}} \right) - 1 \right]$$

There is an input offset voltage associated with nodes R<sub>CVN</sub>, R<sub>CVP</sub>. To minimize the effect of the mismatch of this voltage at T/R, the equivalent resistance to ac ground at R<sub>CVN</sub> should be approximately equal to that at R<sub>CVP</sub>. Refer to Figure 22 (schematic with dc blocking capacitors). To meet this requirement, R<sub>N2</sub> = R<sub>GP</sub> || R<sub>T1</sub>.

#### Hybrid Balance

Set the hybrid cancellation via RHB.

$$\mathsf{R}_{\mathsf{HB}} = \frac{\mathsf{R}_{\mathsf{X}}}{\mathsf{G}_{\mathsf{RCV}} \times \mathsf{G}_{\mathsf{TX}}}$$

If a +5 V only codec such as an Agere T8503 is used, dc blocking capacitors must be added as shown in Figure 22. This is because the codec is referenced to +2.5 V and the SLIC to ground. With the ac coupling, a dc bias at T/R is eliminated and power associated with this bias is not consumed.

5-8413 (F)

#### Figure 22. ac Interface Circuit Using First-Generation Codec (Including Blocking Capacitors)

## ac Design (continued)

Typically, values of 0.1  $\mu$ F to 0.47  $\mu$ F capacitors are used for dc blocking. The addition of blocking capacitors will cause a shift in the return loss and hybrid balance frequency response toward higher frequencies, degrading the lower-frequency response. The lower the value of the blocking capacitor, the more pronounced the effect is, but the cost of the capacitor is lower. It may be necessary to scale resistor values higher to compensate for the low-frequency response. This effect is best evaluated via simulation. A *PSPICE*\* model for the L8576B is available.

Design equation calculations seldom yield standard component values. Conversion from the calculated value to standard value may have an effect on the ac parameters. This effect should be evaluated and optimized via simulation.

# Use of an Auxiliary Battery Supply

A second lower-voltage battery supply can be used with the L8576B in order to lower the overall power consumption on a short-loop design. For long loops, any power savings will be negated, since long loops are supplied by the main battery voltage. The auxiliary battery would be connected to pins 9 and 37 in lieu of the RPWR resistors. When the external RPWR resistors are removed, more power will be dissipated in the SLIC so internal SLIC power dissipation must be examined.

#### First, determine the auxiliary battery voltage:

The auxiliary battery should be set 8 V greater than the maximum tip/ring loop voltage on the longest allowed loop, when both channels are off-hook and in current limit.

Aux Bat(MAX) = [(ILIM x RLOOP) + VOH] TOLVBAT

Where:

ILIM = dc current limit set by RPROG (usually 0.024).

RLOOP = maximum loop resistance supported (telephone plus line resistance plus protection resistors).

$V_{OH} = overhead voltage.$

TOLVBAT = battery tolerance, for a battery tolerance of  $\pm 5\%$ , use 1.1.

For example, using the recommended 24 mA current limit, an overhead voltage of 8 V, and a maximum loop length of 550  $\Omega$ , the maximum auxiliary battery voltage is 23.3 V.

#### Next, calculate the power dissipated in the SLIC:

Components of the SLIC power dissipation are quiescent power of Vcc and VBAT and loop current associated with VBAT and Aux Bat. These can be calculated as follows:

$W_{VCC(quiescent)} = V_{CC} \times I_{CC(Max)(quiescent)} \times 2$  channels.

$W_{VBAT(quiescent)} = |V_{BAT(Max)}| \times I_{BAT(Max)(quiescent)} \times 2 \text{ channels.}$

$W_{VBAT(loop current)} = (|V_{BAT(Max)}| - 4 V) \times 3 \text{ mA } x \text{ 2 channels.}$

WAux Bat(loop current) = (|Aux Bat(Max)| - 4 V) x (ILIM - 3 mA) x 2 channels.

Where:

4 V is the minimum overhead voltage, and 3 mA is VBAT's contribution to loop current.

For example, substituting values from the data sheet:

$\label{eq:Vcc} \begin{array}{l} Vcc = 5 \ V \\ ICC(Max)(quiescent) = 5.5 \ mA \\ VBAT(Max) = -70 \ V \\ IBAT(Max)(quiescent) = 4 \ mA \\ Aux \ Bat(Max) = -23.3 \ V \\ ILIM = 24 \ mA \end{array}$

The following powers are calculated:

$\begin{array}{l} {\sf W}_{\sf VCC}({\sf quiescent})=5 \ x \ 0.0055 \ x \ 2=0.055 \\ {\sf W}_{\sf VBAT}({\sf quiescent})=|-70| \ x \ 0.004 \ x \ 2=0.56 \\ {\sf W}_{\sf VBAT}({\sf loop \ current})=(|-70|-4) \ x \ 0.003 \ x \ 2=0.396 \\ {\sf W}_{\sf Aux \ Bat}({\sf loop \ current})=(|-23.3|-4) \ x \ (0.024-0.003) \ x \ 2=0.8106 \\ \end{array}$

The sum of the four powers is 1.822 W.

#### Finally, calculate the maximum ambient temperature allowed for the calculated power dissipation:

$T_{A(max)} = T_j - (R_{\theta JA} x P_{DISS SLIC(max)})$

The L8576's 44-pin PLCC exhibits a 43 °C/W thermal resistance if in an enclosure with natural airflow. The maximum operating temperature of the SLIC is 150 °C. Thermal shutdown occurs typically at 160 °C.

For example:

$$T_{A(max)} = 150 - (43 \times 1.822)$$

$$= 150 - 78.4$$

$$= 71.7 \text{ °C}$$

The above scenario would allow operation up to 70 °C.

\* PSPICE is a registered trademark of Cadence Design Systems, Inc.

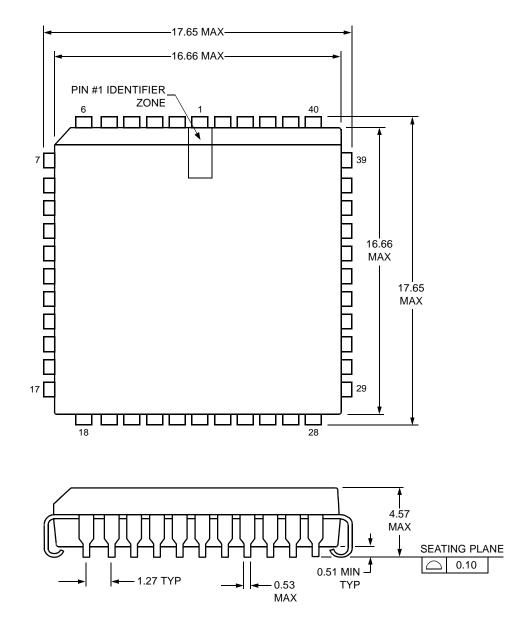

# **Outline Diagram**

# 44-Pin PLCC

Dimensions are in millimeters.

5-2506(F).r8

## **Ordering Information**

| Device Part No. | Description | Package                                 | Comcode   |

|-----------------|-------------|-----------------------------------------|-----------|

| LUCL8576BP-D    | Dual SLIC   | 44-Pin PLCC (Dry-bagged)                | 108131285 |

| LUCL8576BP-DT   | Dual SLIC   | 44-Pin PLCC (Tape and Reel, Dry-bagged) | 108131293 |

For additional information, contact your Agere Systems Account Manager or the following: INTERNET: http://www.agere.com E-MAIL: docmaster@micro.lucent.com N. AMERICA: Agere Systems Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, PA 18109-3286 1-800-372-2447, FAX 610-712-4106 (In CANADA: 1-800-553-2448, FAX 610-712-4106) ASIA PACIFIC: Agere Systems Singapore Pte. Ltd., 77 Science Park Drive, #03-18 Cintech III, Singapore 118256 Tel. (65) 778 8833, FAX (65) 777 7495 CHINA: Agere Systems (Shanghai) Co., Ltd., 33/F Jin Mao Tower, 88 Century Boulevard Pudong, Shanghai 200121 PRC Tel. (86) 21 50471212, FAX (86) 21 50472266 JAPAN: Agere Systems Japan Ltd., 7-18, Higashi-Gotanda 2-chome, Shinagawa-ku, Tokyo 141, Japan Tel. (81) 3 5421 1600, FAX (81) 3 5421 1700 Data Requests: DATALINE: Tel. (44) 7000 582 368, FAX (44) 1189 328 148 EUROPE: Technical Inquiries: GERMANY: (49) 89 95086 0 (Munich), UNITED KINGDOM: (44) 1344 865 900 (Ascot), FRANCE: (33) 1 40 83 68 00 (Paris), SWEDEN: (46) 8 594 607 00 (Stockholm), FINLAND: (358) 9 3507670 (Helsinki), ITALY: (39) 02 6608131 (Milan), SPAIN: (34) 1 807 1441 (Madrid)

Agere Systems Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application.

Copyright © 2001 Agere Systems Inc. All Rights Reserved