## SRI4K

# 13.56 MHz short-range contactless memory chip with 4096-bit EEPROM and anticollision functions

#### **Features**

- ISO 14443-2 Type B air interface compliant

- ISO 14443-3 Type B frame format compliant

- 13.56 MHz carrier frequency

- 847 kHz subcarrier frequency

- 106 Kbit/second data transfer

- 8 bit Chip\_ID based anticollision system

- 2 count-down binary counters with automated antitearing protection

- 64-bit Unique Identifier

- 4096-bit EEPROM with write protect feature

- Read\_block and Write\_block (32 bits)

- Internal tuning capacitor

- 1million erase/write cycles

- 40-year data retention

- Self-timed programming cycle

- 5 ms typical programming time

Contents SRI4K

# **Contents**

| 1    | Desc | cription                                                            |

|------|------|---------------------------------------------------------------------|

| 2    | Sign | al description                                                      |

|      | 2.1  | AC1, AC0 8                                                          |

| 3    | Data | transfer 9                                                          |

|      | 3.1  | Input data transfer from the reader to the SRI4K (request frame) 9  |

|      |      | 3.1.1 Character transmission format for request frame               |

|      |      | 3.1.2 Request start of frame                                        |

|      |      | 3.1.3 Request end of frame                                          |

|      | 3.2  | Output data transfer from the SRI4K to the reader (answer frame) 11 |

|      |      | 3.2.1 Character transmission format for answer frame                |

|      |      | 3.2.2 Answer start of frame                                         |

|      |      | 3.2.3 Answer end of frame                                           |

|      | 3.3  | Transmission frame                                                  |

|      | 3.4  | CRC 13                                                              |

| 4    | Mem  | ory mapping14                                                       |

|      | 4.1  | Resettable OTP area                                                 |

|      | 4.2  | 32-bit binary counters                                              |

|      | 4.3  | EEPROM area                                                         |

|      | 4.4  | System area                                                         |

|      |      | 4.4.1 OTP_Lock_Reg                                                  |

|      |      | 4.4.2 Fixed Chip_ID (Option)                                        |

| 5    | SRI4 | K operation19                                                       |

| 6    | SRI4 | K states 20                                                         |

|      | 6.1  | Power-off state                                                     |

|      | 6.2  | Ready state                                                         |

|      | 6.3  | Inventory state                                                     |

|      | 6.4  | Selected state                                                      |

|      | 6.5  | Deselected state                                                    |

|      |      |                                                                     |

| 2/45 |      |                                                                     |

|          | 6.6    | Deactivated state 20                     |

|----------|--------|------------------------------------------|

| 7        | Antic  | ollision                                 |

|          | 7.1    | Description of an anticollision sequence |

| 8        | SRI4   | Commands                                 |

|          | 8.1    | Initiate() command                       |

|          | 8.2    | Pcall16() command                        |

|          | 8.3    | Slot_marker(SN) command                  |

|          | 8.4    | Select(Chip_ID) command                  |

|          | 8.5    | Completion() command                     |

|          | 8.6    | Reset_to_inventory() command             |

|          | 8.7    | Read_block(Addr) command                 |

|          | 8.8    | Write_block (Addr, Data) command         |

|          | 8.9    | Get_UID() command                        |

|          | 8.10   | Power-on state                           |

| 9        | Maxir  | num rating                               |

| 10       | DC ar  | nd ac parameters                         |

| 11       | Part r | numbering                                |

| Appendix | A IS   | 6O-14443 Type B CRC calculation          |

| Appendix | B S    | RI4K command summary                     |

| Revision | histor | y                                        |

List of tables SRI4K

# List of tables

| Table 1.  | Signal names                    | . 7 |

|-----------|---------------------------------|-----|

| Table 2.  | Bit description                 |     |

| Table 3.  | SRI4K memory mapping            |     |

| Table 4.  | Standard anticollision sequence |     |

| Table 5.  | Command code                    |     |

| Table 6.  | Absolute maximum ratings        | 37  |

| Table 7.  | Operating conditions            |     |

| Table 8.  | DC characteristics              |     |

| Table 9.  | AC characteristics              |     |

| Table 10. | Ordering information scheme     | 40  |

|           | Document revision history       |     |

SRI4K List of figures

# **List of figures**

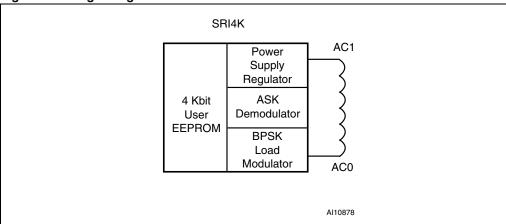

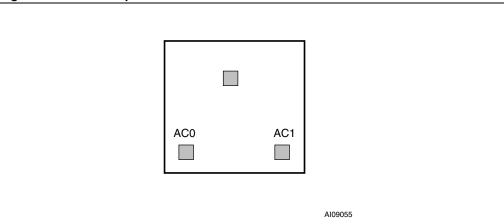

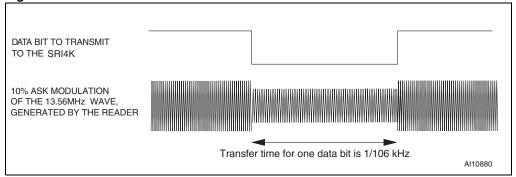

| Figure 1.  | Logic diagram                                              | 7    |

|------------|------------------------------------------------------------|------|

| Figure 2.  | Die floor plan                                             | 8    |

| Figure 3.  | 10% ASK modulation of the received wave                    | 9    |

| Figure 4.  | SRI4K request frame character format                       | 9    |

| Figure 5.  | Request start of frame                                     | . 10 |

| Figure 6.  | Request end of frame                                       |      |

| Figure 7.  | Wave transmitted using BPSK subcarrier modulation          | . 11 |

| Figure 8.  | Answer start of frame                                      | . 11 |

| Figure 9.  | Answer end of frame                                        | . 12 |

| Figure 10. | Example of a complete transmission frame                   | . 12 |

| Figure 11. | CRC transmission rules                                     |      |

| Figure 12. | Resettable OTP area (addresses 0 to 4)                     | . 15 |

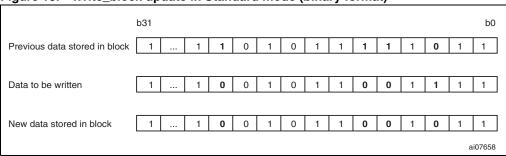

| Figure 13. | Write_block update in Standard mode (binary format)        | . 15 |

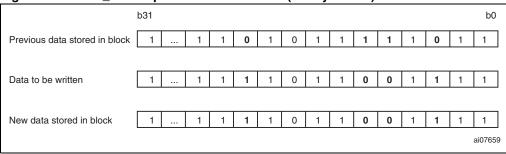

| Figure 14. | Write_block update in Reload mode (binary format)          | . 15 |

| Figure 15. | Binary counter (addresses 5 to 6)                          | . 16 |

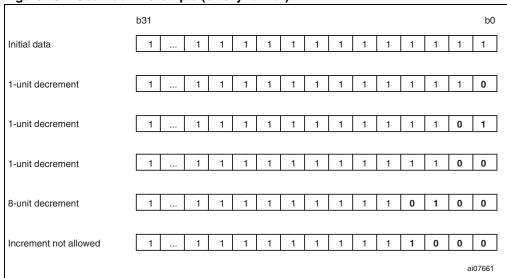

| Figure 16. | Countdown example (binary format)                          | . 16 |

| Figure 17. | EEPROM (addresses 7 to 127)                                | . 17 |

| Figure 18. | System area                                                | . 18 |

| Figure 19. | State transition diagram                                   | . 21 |

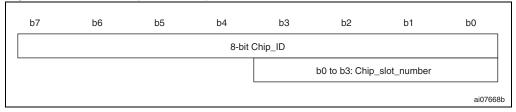

| Figure 20. | SRI4K Chip_ID description                                  | . 22 |

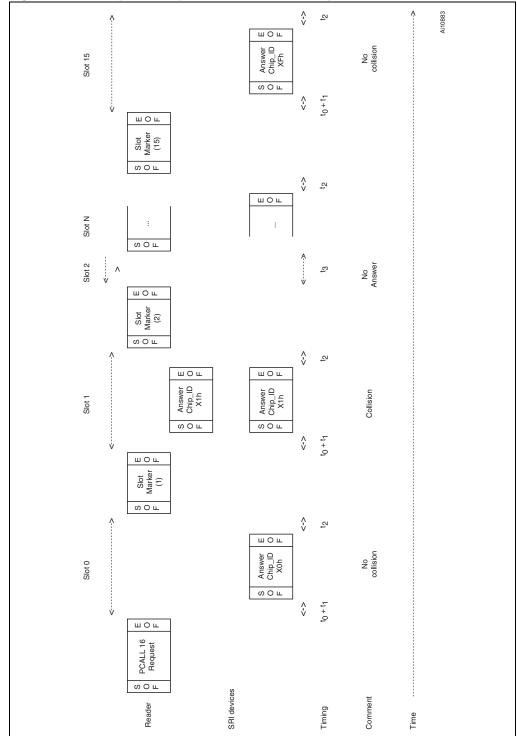

| Figure 21. | Description of a possible anticollision sequence           | . 23 |

| Figure 22. | Example of an anticollision sequence                       | . 25 |

| Figure 23. | Initiate request format                                    | . 27 |

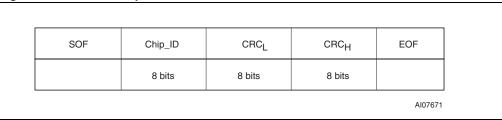

| Figure 24. | Initiate response format                                   | . 27 |

| Figure 25. | Initiate frame exchange between reader and SRI4K           | . 27 |

| Figure 26. | Pcall16 request format                                     | . 28 |

| Figure 27. | Pcall16 response format                                    |      |

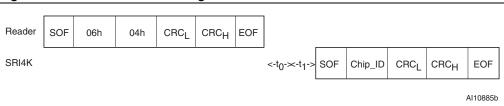

| Figure 28. | Pcall16 frame exchange between reader and SRI4K            | . 28 |

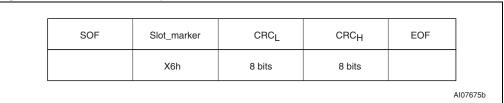

| Figure 29. | Slot_marker request format                                 |      |

| Figure 30. | Slot_marker response format                                | . 29 |

| Figure 31. | Slot_marker frame exchange between reader and SRI4K        | . 29 |

| Figure 32. | Select request format                                      | . 30 |

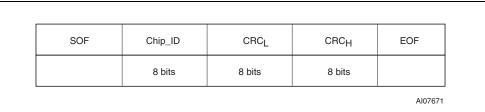

| Figure 33. | Select response format                                     | . 30 |

| Figure 34. | Select frame exchange between reader and SRI4K             | . 30 |

| Figure 35. | Completion request format                                  | . 31 |

| Figure 36. | Completion response format                                 | . 31 |

| Figure 37. | Completion frame exchange between reader and SRI4K         |      |

| Figure 38. | Reset_to_inventory request format                          | . 32 |

| Figure 39. | Reset_to_inventory response format                         |      |

| Figure 40. | Reset_to_inventory frame exchange between reader and SRI4K | . 32 |

| Figure 41. | Read_block request format                                  | . 33 |

| Figure 42. | Read_block response format                                 | . 33 |

| Figure 43. | Read_block frame exchange between reader and SRI4K         |      |

| Figure 44. | Write_block request format                                 |      |

| Figure 45. | Write_block response format                                |      |

| Figure 46. | Write_block frame exchange between reader and SRI4K        |      |

| Figure 47. | Get_UID request format                                     |      |

| Figure 48. | Get_UID response format                                    | . 35 |

| -          |                                                            |      |

<u>577</u>

| Figure 49. | 64-bit unique identifier of the SRI4K            | 36 |

|------------|--------------------------------------------------|----|

| Figure 50. | Get_UID frame exchange between reader and SRI4K  | 36 |

| Figure 51. | SRI4K synchronous timing, transmit and receive   | 39 |

| Figure 52. | Initiate frame exchange between reader and SRI4K | 42 |

SRI4K

| 9          |                                                            |    |

|------------|------------------------------------------------------------|----|

| Figure 51. | SRI4K synchronous timing, transmit and receive             | 39 |

| Figure 52. | Initiate frame exchange between reader and SRI4K           | 42 |

| Figure 53. | Pcall16 frame exchange between reader and SRI4K            | 42 |

| Figure 54. | Slot_marker frame exchange between reader and SRI4K        | 42 |

| Figure 55. | Select frame exchange between reader and SRI4K             | 42 |

| Figure 56. | Completion frame exchange between reader and SRI4K         | 42 |

| Figure 57. | Reset_to_inventory frame exchange between reader and SRI4K | 43 |

| Figure 58. | Read_block frame exchange between reader and SRI4K         | 43 |

| Figure 59. | Write_block frame exchange between reader and SRI4K        | 43 |

| Figure 60. | Get_UID frame exchange between reader and SRI4K            | 43 |

|            |                                                            |    |

6/45

List of figures

SRI4K Description

## 1 Description

The SRI4K is a contactless memory, powered by an externally transmitted radio wave. It contains a 4096-bit user EEPROM fabricated with STMicroelectronics CMOS technology. The memory is organized as 128 blocks of 32 bits. The SRI4K is accessed via the 13.56 MHz carrier. Incoming data are demodulated and decoded from the received amplitude shift keying (ASK) modulation signal and outgoing data are generated by load variation using bit phase shift keying (BPSK) coding of a 847 kHz subcarrier. The received ASK wave is 10% modulated. The data transfer rate between the SRI4K and the reader is 106 kbit/s in both reception and emission modes.

The SRI4K follows the ISO 14443 part 2 type B recommendation for the radio-frequency power and signal interface.

Figure 1. Logic diagram

The SRI4K is specifically designed for short range applications that need re-usable products. The SRI4K includes an anticollision mechanism that allows it to detect and select tags present at the same time within range of the reader. The anticollision is based on a probabilistic scanning method using slot markers. Using the STMicroelectronics single chip coupler, CRX14, it is easy to design a reader and build a contactless system.

Table 1. Signal names

| Signal names | Description  |

|--------------|--------------|

| AC1          | Antenna coil |

| AC0          | Antenna coil |

Signal description SRI4K

The SRI4K contactless EEPROM can be randomly read and written in block mode (each block containing 32 bits). The instruction set includes the following nine commands:

- Read\_block

- Write\_block

- Initiate

- Pcall16

- Slot marker

- Select

- Completion

- Reset\_to\_inventory

- Get\_UID

The SRI4K memory is organized in three areas, as described in *Figure 3*. The first area is a resettable OTP (one time programmable) area in which bits can only be switched from 1 to 0. Using a special command, it is possible to erase all bits of this area to 1. The second area provides two 32-bit binary counters which can only be decremented from FFFF FFFFh to 0000 0000h, and gives a capacity of 4,294,967,296 units per counter. The last area is the EEPROM memory. It is accessible by block of 32 bits and includes an auto-erase cycle during each Write\_block command.

## 2 Signal description

## 2.1 AC1, AC0

The pads for the Antenna Coil. AC1 and AC0 must be directly bonded to the antenna.

SRI4K Data transfer

## 3 Data transfer

# 3.1 Input data transfer from the reader to the SRI4K (request frame)

The reader must generate a 13.56 MHz sinusoidal carrier frequency at its antenna, with enough energy to "remote-power" the memory. The energy received at the SRI4K's antenna is transformed into a supply voltage by a regulator, and into data bits by the ASK demodulator. For the SRI4K to decode correctly the information it receives, the reader must 10% amplitude-modulate the 13.56 MHz wave before sending it to the SRI4K. This is represented in *Figure 3*. The data transfer rate is 106 Kbits/s.

Figure 3. 10% ASK modulation of the received wave

## 3.1.1 Character transmission format for request frame

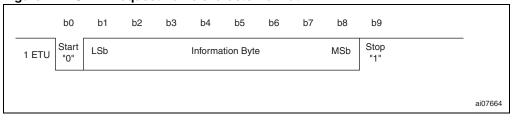

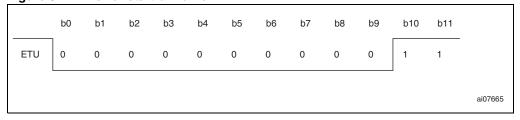

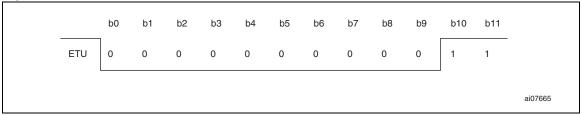

The SRI4K transmits and receives data bytes as 10-bit characters, with the least significant bit ( $b_0$ ) transmitted first, as shown in *Figure 4*. Each bit duration, an ETU (elementary time unit), is equal to 9.44  $\mu$ s (1/106 kHz).

These characters, framed by a start of frame (SOF) and an end of frame (EOF), are put together to form a command frame as shown in *Figure 10*. A frame includes an SOF, commands, addresses, data, a CRC and an EOF as defined in the ISO 14443-3 Type B Standard. If an error is detected during data transfer, the SRI4K does not execute the command, but it does not generate an error frame.

Figure 4. SRI4K request frame character format

Data transfer SRI4K

Table 2. Bit description

| Bit                              | Description                                      | Value                                                             |

|----------------------------------|--------------------------------------------------|-------------------------------------------------------------------|

| b <sub>0</sub>                   | Start bit used to synchronize the transmission   | b <sub>0</sub> = 0                                                |

| b <sub>1</sub> to b <sub>8</sub> | Information byte (command, address or data)      | The information byte is sent with the least significant bit first |

| b <sub>9</sub>                   | Stop bit used to indicate the end of a character | b <sub>9</sub> = 1                                                |

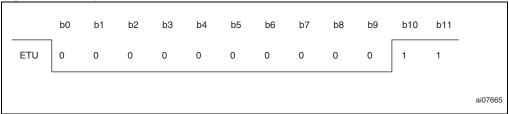

### 3.1.2 Request start of frame

The SOF described in *Figure 5* is composed of:

- one falling edge,

- followed by 10 ETUs at logic-0,

- followed by a single rising edge,

- followed by at least 2 ETUs (and at most 3) at logic-1.

Figure 5. Request start of frame

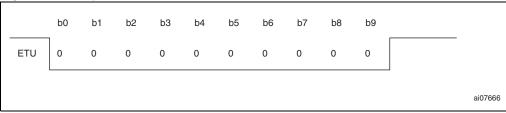

## 3.1.3 Request end of frame

The EOF shown in *Figure 6* is composed of:

- one falling edge,

- followed by 10 ETUs at logic-0,

- followed by a single rising edge.

Figure 6. Request end of frame

**77**

SRI4K Data transfer

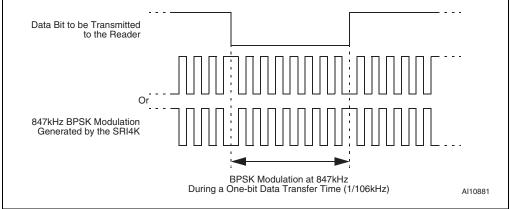

# 3.2 Output data transfer from the SRI4K to the reader (answer frame)

The data bits issued by the SRI4K use retro-modulation. Retro-modulation is obtained by modifying the SRI4K current consumption at the antenna (load modulation). The load modulation causes a variation at the reader antenna by inductive coupling. With appropriate detector circuitry, the reader is able to pick up information from the SRI4K. To improve load-modulation detection, data is transmitted using a BPSK encoded, 847 kHz subcarrier frequency  $f_s$  as shown in *Figure 7*, and as specified in the ISO 14443-2 Type B Standard.

Figure 7. Wave transmitted using BPSK subcarrier modulation

#### 3.2.1 Character transmission format for answer frame

The character format is the same as for input data transfer (*Figure 4*). The transmitted frames are made up of an SOF, data, a CRC and an EOF (*Figure 10*). As with an input data transfer, if an error occurs, the reader does not issue an error code to the SRI4K, but it should be able to detect it and manage the situation. The data transfer rate is 106 Kbits/second.

#### 3.2.2 Answer start of frame

The SOF described in Figure 8 is composed of:

- followed by 10 ETUs at logic-0

- followed by 2 ETUs at logic-1

Figure 8. Answer start of frame

Data transfer SRI4K

#### 3.2.3 Answer end of frame

The EOF shown in Figure 9 is composed of:

- followed by 10 ETUs at logic-0,

- followed by 2 ETUs at logic-1.

Figure 9. Answer end of frame

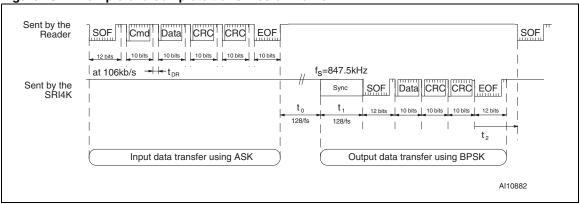

### 3.3 Transmission frame

Between the request data transfer and the answer data transfer, all ASK and BPSK modulations are suspended for a minimum time of  $t_0 = 128/f_{\rm S}$ . This delay allows the reader to switch from Transmission to Reception mode. It is repeated after each frame. After  $t_0$ , the 13.5 6MHz carrier frequency is modulated by the SRI4K at 847 kHz for a period of  $t_1 = 128/f_{\rm S}$  to allow the reader to synchronize. After  $t_1$ , the first phase transition generated by the SRI4K forms the start bit ('0') of the answer SOF. After the falling edge of the answer EOF, the reader waits a minimum time,  $t_2$ , before sending a new request frame to the SRI4K.

SRI4K Data transfer

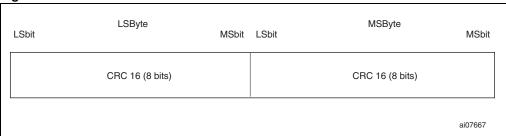

#### 3.4 CRC

The 16-bit CRC used by the SRI4K is generated in compliance with the ISO14443 Type B recommendation. For further information, please see *Appendix A*. The initial register contents are all 1s: FFFFh.

The two-byte CRC is present in every request and in every answer frame, before the EOF. The CRC is calculated on all the bytes between SOF (not included) and the CRC field.

Upon reception of a request from a reader, the SRI4K verifies that the CRC value is valid. If it is invalid, the SRI4K discards the frame and does not answer the reader.

Upon reception of an answer from the SRI4K, the reader should verify the validity of the CRC. In case of error, the actions to be taken are the reader designer's responsibility.

The CRC is transmitted with the least significant byte first and each byte is transmitted with the least significant bit first.

Figure 11. CRC transmission rules

Memory mapping SRI4K

# 4 Memory mapping

The SRI4K is organized as 128 blocks of 32 bits as shown in *Table 3*. All blocks are accessible by the Read\_block command. Depending on the write access, they can be updated by the Write\_block command. A Write\_block updates all the 32 bits of the block.

Table 3. SRI4K memory mapping

| Block | MSB                             | 32-b                | it block                        |          | LSB                  | Description        |  |

|-------|---------------------------------|---------------------|---------------------------------|----------|----------------------|--------------------|--|

| Addr  | b <sub>31</sub> b <sub>24</sub> | , b <sub>23</sub> b | o <sub>16</sub> b <sub>15</sub> | $b_8b_7$ | $b_0$                | Description        |  |

| 0     |                                 |                     |                                 |          |                      |                    |  |

| 1     |                                 |                     |                                 |          |                      |                    |  |

| 2     |                                 |                     | Resettable OTP bits             |          |                      |                    |  |

| 3     |                                 | 32 bits E           | Boolean area                    |          |                      |                    |  |

| 4     |                                 | 32 bits E           | Boolean area                    |          |                      |                    |  |

| 5     |                                 | 32 bits bi          | inary counter                   |          |                      | Count down         |  |

| 6     |                                 | 32 bits bi          | inary counter                   |          |                      | counter            |  |

| 7     |                                 | Us                  | er area                         |          |                      |                    |  |

| 8     |                                 | Us                  | er area                         |          |                      |                    |  |

| 9     |                                 | Us                  | er area                         |          |                      | •                  |  |

| 10    |                                 | Us                  | er area                         |          |                      |                    |  |

| 11    |                                 | Lockable<br>EEPROM  |                                 |          |                      |                    |  |

| 12    |                                 |                     |                                 |          |                      |                    |  |

| 13    |                                 |                     |                                 |          |                      |                    |  |

| 14    |                                 |                     |                                 |          |                      |                    |  |

| 15    |                                 |                     |                                 |          |                      |                    |  |

| 16    |                                 | Us                  | er area                         |          |                      |                    |  |

|       |                                 | Us                  | er area                         |          |                      | EEPROM             |  |

| 127   |                                 | Us                  | er area                         |          |                      |                    |  |

|       | T                               |                     |                                 |          |                      | Г                  |  |

| 255   | OTP_Lock_Reg                    | ST F                | Reserved                        |          | d Chip_ID<br>Option) | System OTP<br>bits |  |

| UID0  |                                 | 64 hita             | s UID area                      |          |                      | ROM                |  |

| UID1  | 1                               |                     | HOIVI                           |          |                      |                    |  |

SRI4K Memory mapping

#### 4.1 Resettable OTP area

In this area contains five individual 32-bit Boolean words (see *Figure 12* for a map of the area). A Write\_block command will not erase the previous contents of the block as the write cycle is not preceded by an auto-erase cycle. This feature can be used to reset selected bits from 1 to 0. All bits previously at 0 remain unchanged. When the 32 bits of a block are all at 0, the block is empty, and cannot be updated any more. See *Figure 13* and *Figure 14* for examples of the result of the Write\_block command in the resettable OTP area.

Figure 12. Resettable OTP area (addresses 0 to 4)

| MSb<br>b31 | b24 b23 | 32-bit block<br>b16 b15 | b8 b7                                                                           | LSb<br>b0                                                                       | Description                                                                     |

|------------|---------|-------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

|            |         | 32-bit Boolean area     |                                                                                 |                                                                                 |                                                                                 |

|            |         | 32-bit Boolean area     |                                                                                 |                                                                                 | B Walde                                                                         |

|            |         | 32-bit Boolean area     |                                                                                 |                                                                                 | Resettable<br>OTP bit                                                           |

|            |         | 32-bit Boolean area     |                                                                                 |                                                                                 |                                                                                 |

|            |         | 32-bit Boolean area     |                                                                                 |                                                                                 |                                                                                 |

|            | D31     | D31                     | 32-bit Boolean area 32-bit Boolean area 32-bit Boolean area 32-bit Boolean area | 32-bit Boolean area 32-bit Boolean area 32-bit Boolean area 32-bit Boolean area | 32-bit Boolean area 32-bit Boolean area 32-bit Boolean area 32-bit Boolean area |

Figure 13. Write\_block update in Standard mode (binary format)

The five 32-bit blocks making up the resettable OTP area can be erased in one go by adding an auto-erase cycle to the Write\_block command. An auto-erase cycle is added each time the SRI4K detects a Reload command. The Reload command is implemented through a specific update of the 32-bit binary counter located at block address 6 (see "Section 4.2: 32-bit binary counters" for details).

Figure 14. Write\_block update in Reload mode (binary format)

Memory mapping SRI4K

## 4.2 32-bit binary counters

The two 32-bit binary counters located at block addresses 5 and 6, respectively, are used to count down from 2<sup>32</sup> (4096 million) to 0. The SRI4K uses dedicated logic that only allows the update of a counter if the new value is lower than the previous one. This feature allows the application to count down by steps of 1 or more. The initial value in Counter 5 is FFFF FFFEh and is FFFF FFFFh in Counter 6. When the value displayed is 0000 0000h, the counter is empty and cannot be reloaded. The counter is updated by issuing the Write\_block command to block address 5 or 6, depending on which counter is to be updated. The Write\_block command writes the new 32-bit value to the counter block address. *Figure 16* shows examples of how the counters operate.

The counter programming cycles are protected by automated antitearing logic. This function allows the counter value to be protected in case of power down within the programming cycle. In case of power down, the counter value is not updated and the previous value continues to be stored.

Figure 15. Binary counter (addresses 5 to 6)

| Block<br>Address        | MSb<br>b31 | b24 b23 | 32-bit block<br>b16 b15 | b8 b7 | LSb<br>b0 | Description |  |  |

|-------------------------|------------|---------|-------------------------|-------|-----------|-------------|--|--|

| 5                       |            |         | 32-bit binary counter   |       |           | Count down  |  |  |

| 6 32-bit binary counter |            |         |                         |       | Counter   |             |  |  |

Figure 16. Countdown example (binary format)

The counter with block address 6 controls the Reload command used to reset the resettable OTP area (addresses 0 to 4). Bits  $b_{31}$  to  $b_{21}$  act as an 11-bit Reload counter; whenever one of these 11 bits is updated, the SRI4K detects the change and adds an Erase cycle to the Write\_block command for locations 0 to 4 (see the "*Resettable OTP area*" paragraph). The Erase cycle remains active until a Power-off or a Select command is issued. The SRI4K's resettable OTP area can be reloaded up to 2 047 times ( $2^{11}$ -1).

SRI4K Memory mapping

### 4.3 EEPROM area

The 121 blocks between addresses 7 and 127 are EEPROM blocks of 32 bits each (484 bytes in total). (See *Figure 17* for a map of the area.) These blocks can be accessed using the Read\_block and Write\_block commands. The Write\_block command for the EEPROM area always includes an auto-erase cycle prior to the write cycle.

Blocks 7 to 15 can be write-protected. Write access is controlled by the 8 bits of the OTP\_Lock\_Reg located at block address 255 (see "*OTP\_Lock\_Reg*" for details). Once protected, these blocks (7 to 15) cannot be unprotected.

Figure 17. EEPROM (addresses 7 to 127)

| Block<br>address | MSb<br>b31 | b24 b23 | 32-bit block<br>b16 b15 | b8 b7 | LSb<br>b0 | Description        |

|------------------|------------|---------|-------------------------|-------|-----------|--------------------|

| 7                |            |         | User area               |       |           |                    |

| 8                |            |         | User area               |       |           |                    |

| 9                |            |         | User area               |       |           |                    |

| 10               |            |         | User area               |       |           |                    |

| 11               |            |         | User area               |       |           | Lockable<br>EEPROM |

| 12               |            |         | User area               |       |           |                    |

| 13               |            |         | User area               |       |           |                    |

| 14               |            |         | User area               |       |           |                    |

| 15               |            |         | User area               |       |           |                    |

| 16               |            |         | User area               |       |           |                    |

|                  |            |         | User area               |       |           | EEPROM             |

| 127              |            |         | User area               |       |           |                    |

## 4.4 System area

This area is used to modify the settings of the SRI4K. It contains 3 registers: OTP\_Lock\_Reg, Fixed Chip\_ID and ST Reserved. See *Figure 18* for a map of this area.

A Write\_block command in this area will not erase the previous contents. Selected bits can thus be set from 1 to 0. All bits previously at 0 remain unchanged. Once all the 32 bits of a block are at 0, the block is empty and cannot be updated any more.

Memory mapping SRI4K

Figure 18. System area

| Block MSb |        |         | 32-bit block |    |    | LSb            | Description |  |

|-----------|--------|---------|--------------|----|----|----------------|-------------|--|

| address   | b31    | b24 b23 | b16 b15      | b8 | b7 | b0             | Description |  |

| 255       | OTP_Lo | ck_Reg  | ST reserved  |    |    | Chip_ID ption) |             |  |

#### 4.4.1 OTP Lock Reg

The 8 bits,  $b_{31}$  to  $b_{24}$ , of the System area (block address 255) are used as OTP\_Lock\_Reg bits in the SRI4K. They control the write access to the 9 EEPROM blocks with addresses 7 to 15 as follows:

- When b<sub>24</sub> is at 0, blocks 7 and 8 are write-protected

- When b<sub>25</sub> is at 0, block 9 is write-protected

- When b<sub>26</sub> is at 0, block 10 is write-protected

- When b<sub>27</sub> is at 0, block 11 is write-protected

- When b<sub>28</sub> is at 0, block 12 is write-protected

- When b<sub>29</sub> is at 0, block 13 is write-protected

- When b<sub>30</sub> is at 0, block 14 is write-protected

- When b<sub>31</sub> is at 0, block 15 is write-protected.

The OTP\_Lock\_Reg bits cannot be erased. Once write-protected, EEPROM blocks behave like ROM blocks and cannot be unprotected.

#### 4.4.2 Fixed Chip\_ID (Option)

The SRI4K is provided with an anticollision feature based on a random 8-bit Chip\_ID. Prior to selecting an SRI4K, an anticollision sequence has to be run to search for the Chip\_ID of the SRI4K. This is a very flexible feature, however the searching loop requires time to run.

For some applications, much time could be saved by knowing the value of the SRI4K Chip\_ID beforehand, so that the SRI4K can be identified and selected directly without having to run an anticollision sequence. This is why the SRI4K was designed with an optional mask setting used to program a fixed 8-bit Chip\_ID to bits  $b_7$  to  $b_0$  of the system area. When the fixed Chip\_ID option is used, the random Chip\_ID function is disabled.

SRI4K operation

## 5 SRI4K operation

All commands, data and CRC are transmitted to the SRI4K as 10-bit characters using ASK modulation. The start bit of the 10 bits,  $b_0$ , is sent first. The command frame received by the SRI4K at the antenna is demodulated by the 10% ASK demodulator, and decoded by the internal logic. Prior to any operation, the SRI4K must have been selected by a Select command. Each frame transmitted to the SRI4K must start with a start of frame, followed by one or more data characters, two CRC bytes and the final end of frame. When an invalid frame is decoded by the SRI4K (wrong command or CRC error), the memory does not return any error code.

When a valid frame is received, the SRI4K may have to return data to the reader. In this case, data is returned using BPSK encoding, in the form of 10-bit characters framed by an SOF and an EOF. The transfer is ended by the SRI4K sending the 2 CRC bytes and the EOF.

SRI4K states SRI4K

#### 6 SRI4K states

The SRI4K can be switched into different states. Depending on the current state of the SRI4K, its logic will only answer to specific commands. These states are mainly used during the anticollision sequence, to identify and to access the SRI4K in a very short time. The SRI4K provides 6 different states, as described in the following paragraphs and in *Figure 19*.

#### 6.1 Power-off state

The SRI4K is in Power-off state when the electromagnetic field around the tag is not strong enough. In this state, the SRI4K does not respond to any command.

## 6.2 Ready state

When the electromagnetic field is strong enough, the SRI4K enters the Ready state. After Power-up, the Chip\_ID is initialized with a random value. The whole logic is reset and remains in this state until an Initiate() command is issued. Any other command will be ignored by the SRI4K.

## 6.3 Inventory state

The SRI4K switches from the Ready to the Inventory state after an Initiate() command has been issued. In Inventory state, the SRI4K will respond to any anticollision commands: Initiate(), Pcall16() and Slot\_marker(), and then remain in the Inventory state. It will switch to the Selected state after a Select(Chip\_ID) command is issued, if the Chip\_ID in the command matches its own. If not, it will remain in Inventory state.

#### 6.4 Selected state

In Selected state, the SRI4K is active and responds to all Read\_block(), Write\_block() and Get\_UID() commands. When an SRI4K has entered the Selected state, it no longer responds to anticollision commands. So that the reader can access another tag, the SRI4K can be switched to the Deselected state by sending a Select(Chip\_ID2) with a Chip\_ID that does not match its own, or it can be placed in Deactivated state by issuing a Completion() command. Only one SRI4K can be in Selected state at a time.

#### 6.5 Deselected state

Once the SRI4K is in Deselected state, only a Select(Chip\_ID) command with a Chip\_ID matching its own can switch it back to Selected state. All other commands are ignored.

#### 6.6 Deactivated state

When in this state, the SRI4K can only be turned off. All commands are ignored.

57

SRI4K states

Power-off Out of On field field Ready Chip\_ID<sub>8bits</sub> = RND Initiate() Out of Initiate() or Pcall16() or Slot\_marker(SN) or field Inventory Out of Select(wrong Chip\_ID) field Select(Chip\_ID) Reset\_to\_inventory() Out of field Out of field Select(Chip\_ID) Selected Completion() Deselected Deactivated Select( ≠ Chip\_ID) Select(Chip\_ID) Read\_block()

Write\_block()

Get\_UID()

Figure 19. State transition diagram

47

Al10879b

Anticollision SRI4K

## 7 Anticollision

The SRI4K provides an anticollision mechanism that searches for the Chip\_ID of each device that is present in the reader field range. When known, the Chip\_ID is used to select an SRI4K individually, and access its memory. The anticollision sequence is managed by the reader through a set of commands described in *Section 5: SRI4K operation*:

- Initiate()

- Pcall16()

- Slot\_marker().

The reader is the master of the communication with one or more SRI4K device(s). It initiates the tag communication activity by issuing an Initiate(), Pcall16() or Slot\_marker() command to prompt the SRI4K to answer. During the anticollision sequence, it might happen that two or more SRI4K devices respond simultaneously, so causing a collision. The command set allows the reader to handle the sequence, to separate SRI4K transmissions into different time slots. Once the anticollision sequence has completed, SRI4K communication is fully under the control of the reader, allowing only one SRI4K to transmit at a time.

The Anticollision scheme is based on the definition of time slots during which the SRI4K devices are invited to answer with minimum identification data: the Chip\_ID. The number of slots is fixed at 16 for the Pcall16() command. For the Initiate() command, there is no slot and the SRI4K answers after the command is issued. SRI4K devices are allowed to answer only once during the anticollision sequence. Consequently, even if there are several SRI4K devices present in the reader field, there will probably be a slot in which only one SRI4K answers, allowing the reader to capture its Chip\_ID. Using the Chip\_ID, the reader can then establish a communication channel with the identified SRI4K. The purpose of the anticollision sequence is to allow the reader to select one SRI4K at a time.

The SRI4K is given an 8-bit Chip\_ID value used by the reader to select only one among up to 256 tags present within its field range. The Chip\_ID is initialized with a random value during the Ready state, or after an Initiate() command in the Inventory state.

The four least significant bits  $(b_0 to b_3)$  of the Chip\_ID are also known as the Chip\_slot\_number. This 4-bit value is used by the Pcall16() and Slot\_marker() commands during the anticollision sequence in the Inventory state.

Figure 20. SRI4K Chip\_ID description

Each time the SRI4K receives a Pcall16() command, the Chip\_slot\_number is given a new 4-bit random value. If the new value is 0000<sub>b</sub>, the SRI4K returns its whole 8-bit Chip\_ID in its answer to the Pcall16() command. The Pcall16() command is also used to define the slot number 0 of the anticollision sequence. When the SRI4K receives the Slot\_marker(SN) command, it compares its Chip\_slot\_number with the Slot\_number parameter (SN). If they match, the SRI4K returns its Chip\_ID as a response to the command. If they do not, the SRI4K does not answer. The Slot\_marker(SN) command is used to define all the anticollision slot numbers from 1 to 15.

SRI4K Anticollision

Figure 21. Description of a possible anticollision sequence

1. The value X in the answer Chip\_ID means a random hexadecimal character from 0 to F.

**577**

Anticollision SRI4K

## 7.1 Description of an anticollision sequence

The anticollision sequence is initiated by the Initiate() command which triggers all the SRI4K devices that are present in the reader field range, and that are in Inventory state. Only SRI4K devices in Inventory state will respond to the Pcall16() and Slot\_marker(SN) anticollision commands.

A new SRI4K introduced in the field range during the anticollision sequence will not be taken into account as it will not respond to the Pcall16() or Slot\_marker(SN) command (Ready state). To be considered during the anticollision sequence, it must have received the Initiate() command and entered the Inventory state.

*Table 4* shows the elements of a standard anticollision sequence. (See *Figure 22* for an example.)

Table 4. Standard anticollision sequence

|         |         | idard articomsion sequence                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Step 1  | Init:   | Send Initiate().  If no answer is detected, go to step1.  If only 1 answer is detected, select and access the SRI4K. After accessing the SRI4K, deselect the tag and go to step1.  If a collision (many answers) is detected, go to step2.                                                                                                                                                                                                      |

| Step 2  | Slot 0  | Send Pcall16().  — If no answer or collision is detected, go to step3.  — If 1 answer is detected, store the Chip_ID, Send Select() and go to step3.                                                                                                                                                                                                                                                                                            |

| Step 3  | Slot 1  | Send Slot_marker(1).  — If no answer or collision is detected, go to step4.  — If 1 answer is detected, store the Chip_ID, Send Select() and go to step4.                                                                                                                                                                                                                                                                                       |

| Step 4  | Slot 2  | Send Slot_marker(2).  — If no answer or collision is detected, go to step5.  — If 1 answer is detected, store the Chip_ID, Send Select() and go to step5.                                                                                                                                                                                                                                                                                       |

| Step N  | Slop N  | Send Slot_marker(3 up to 14)  — If no answer or collision is detected, go to stepN+1.  — If 1 answer is detected, store the Chip_ID, Send Select() and go to stepN+1.                                                                                                                                                                                                                                                                           |

| Step 17 | Slot 15 | Send Slot_marker(15).  - If no answer or collision is detected, go to step18.  - If 1 answer is detected, store the Chip_ID, Send Select() and go to step18.                                                                                                                                                                                                                                                                                    |

| Step 18 |         | All the slots have been generated and the Chip_ID values should be stored into the reader memory. Issue the Select(Chip_ID) command and access each identified SRI4K one by one. After accessing each SRI4K, switch them into Deselected or Deactivated state, depending on the application needs.  — If collisions were detected between Step2 and Step17, go to Step2.  — If no collision was detected between Step2 and Step17, go to Step1. |

After each Slot\_marker() command, there may be several, one or no answers from the SRI4K devices. The reader must handle all the cases and store all the Chip\_IDs, correctly decoded. At the end of the anticollision sequence, after Slot\_marker(15), the reader can start working with one SRI4K by issuing a Select() command containing the desired Chip\_ID. If a collision is detected during the anticollision sequence, the reader has to generate a new sequence in order to identify all unidentified SRI4K devices in the field. The anticollision sequence can stop when all SRI4K devices have been identified.

SRI4K Anticollision

Figure 22. Example of an anticollision sequence

| Command        | Tag 1      | Tag 2   | Tag 3      | Tag 4   | Tag 5   | Tag 6   | Tag 7      | Tag 8   | Commonts                                                                  |

|----------------|------------|---------|------------|---------|---------|---------|------------|---------|---------------------------------------------------------------------------|

| Command        | Chip_ID    | Chip_ID | Chip_ID    | Chip_ID | Chip_ID | Chip_ID | Chip_ID    | Chip_ID | Comments                                                                  |

| READY State    | 28h        | 75h     | 40h        | 01h     | 02h     | FEh     | A9h        | 7Ch     | Each tag gets a random Chip_ID  Each tag get a new random Chip_ID         |

| INITIATE ()    | 40h        | 13h     | 3Fh        | 4Ah     | 50h     | 48h     | 52h        | 7Ch     | All tags answer: collisions All CHIP_SLOT_NUMBERs get                     |

| PCALL16()      | 45h        | 12h     | 30h<br>30h | 43h     | 55h     | 43h     | 53h        | 73h     | a new random value Slot0: only one answer                                 |

| SELECT(30h)    |            |         | 30h        |         |         |         |            |         | Tag3 is identified                                                        |

| SLOT_MARKER(1) |            |         |            |         |         |         |            |         | Slot1: no answer                                                          |

| SLOT_MARKER(2) |            | 12h     |            |         |         |         |            |         | Slot2: only one answer                                                    |

| SELECT(12h)    |            | 12h     |            |         |         |         |            |         | Tag2 is identified                                                        |

| SLOT_MARKER(3) |            |         |            | 43h     |         | 43h     | 53h        | 73h     | Slot3: collisions                                                         |

| SLOT_MARKER(4) |            |         |            |         |         |         |            |         | Slot4: no answer                                                          |

| SLOT_MARKER(5) | 45h        |         |            |         | 55h     |         |            |         | Slot5: collisions                                                         |

| SLOT_MARKER(6) |            |         |            |         |         |         |            |         | Slot6: no answer                                                          |

| SLOT_MARKER(N) |            |         |            |         |         |         |            |         | SlotN: no answer                                                          |

| SLOT_MARKER(F) |            |         |            |         |         |         |            |         | SlotF: no answer                                                          |

| PCALL16()      | 40h<br>40h |         |            | 41h     | 53h     | 42h     | 50h<br>50h | 74h     | All CHIP_SLOT_NUMBERs get<br>a new random value<br>Slot0: collisions      |

| SLOT_MARKER(1) |            |         |            | 41h     |         |         |            |         | Slot1: only one answer                                                    |

| SELECT(41h)    |            |         |            | 41h     |         |         |            |         | Tag4 is identified                                                        |

| SLOT_MARKER(2) |            |         |            |         |         | 42h     |            |         | Slot2: only one answer                                                    |

| SELECT(42h)    |            |         |            |         |         | 42h     |            |         | Tag6 is identified                                                        |

| SLOT_MARKER(3) |            |         |            |         | 53h     |         |            |         | Slot3: only one answer                                                    |

| SELECT(53h)    |            |         |            |         | 53h     |         |            |         | Tag5 is identified                                                        |

| SLOT_MARKER(4) |            |         |            |         |         |         |            | 74h     | Slot4: only one answer                                                    |

| SELECT(74h)    |            |         |            |         |         |         |            | 74h     | Tag8 is identified                                                        |

| SLOT_MARKER(N) |            |         |            |         |         |         |            |         | SlotN: no answer                                                          |

| PCALL16()      | 41h        |         |            |         |         |         | 50h<br>50h |         | All CHIP_SLOT_NUMBERs get<br>a new random value<br>Slot0: only one answer |

| SELECT(50h)    |            |         |            |         |         |         | 50h        |         | Tag7 is identified                                                        |

| SLOT_MARKER(1) | 41h        |         |            |         |         |         |            |         | Slot1: only one answer but already found for tag4                         |

| SLOT_MARKER(N) |            |         |            |         |         |         |            |         | SlotN: no answer                                                          |

| PCALL16()      | 43h        |         |            |         |         |         |            |         | All CHIP_SLOT_NUMBERs get<br>a new random value<br>Slot0: only one answer |

| SLOT_MARKER(3) | 43h        |         |            |         |         |         |            |         | Slot3: only one answer                                                    |

| SELECT(43h)    | 43h        | ]       |            |         |         |         |            |         | Tag1 is identified                                                        |

|                |            |         |            |         |         |         |            |         | All tags are identified                                                   |

<u>577</u>

SRI4K commands SRI4K

## 8 SRI4K commands

See the paragraphs below for a detailed description of the commands available on the SRI4K. The commands and their hexadecimal codes are summarized in *Table 5*. A brief is given in *Appendix B*.

Table 5. Command code

| Hexadecimal code | Command                 |

|------------------|-------------------------|

| 06h-00h          | Initiate()              |

| 06h-04h          | Pcall16()               |

| x6h              | Slot_marker (SN)        |

| 08h              | Read_block(Addr)        |

| 09h              | Write_block(Addr, Data) |

| 0Bh              | Get_UID()               |

| 0Ch              | Reset_to_inventory      |

| 0Eh              | Select(Chip_ID)         |

| 0Fh              | Completion()            |

SRI4K SRI4K commands

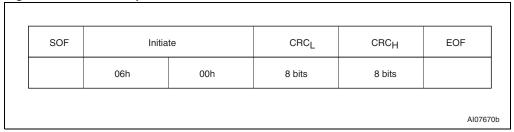

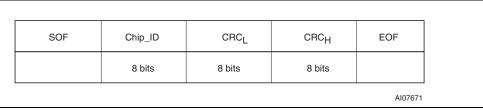

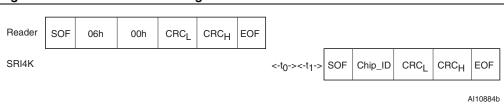

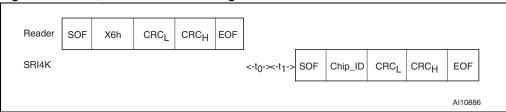

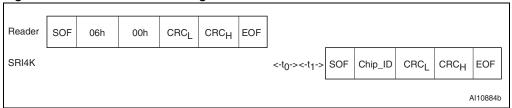

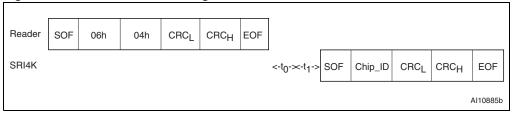

## 8.1 Initiate() command

Command code = 06h - 00h

Initiate() is used to initiate the anticollision sequence of the SRI4K. On receiving the Initiate() command, all SRI4K devices in Ready state switch to Inventory state, set a new 8-bit Chip\_ID random value, and return their Chip\_ID value. This command is useful when only one SRI4K in Ready state is present in the reader field range. It speeds up the Chip\_ID search process. The Chip\_slot\_number is not used during Initiate() command access.

Figure 23. Initiate request format

Request parameter:

No parameter

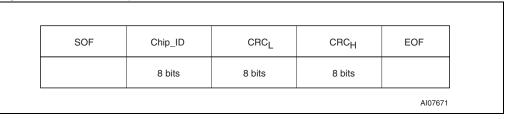

Figure 24. Initiate response format

Response parameter:

Chip\_ID of the SRI4K

Figure 25. Initiate frame exchange between reader and SRI4K

SRI4K commands SRI4K

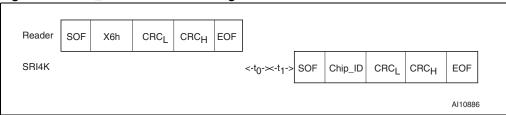

## 8.2 Pcall16() command

Command code = 06h - 04h

The SRI4K must be in Inventory state to interpret the Pcall16() command.

On receiving the Pcall16() command, the SRI4K first generates a new random Chip\_slot\_number value (in the 4 least significant bits of the Chip\_ID). Chip\_slot\_number can take on a value between 0 an 15 (1111 $_{\rm b}$ ). The value is retained until a new Pcall16() or Initiate() command is issued, or until the SRI4K is powered off. The new Chip\_slot\_number value is then compared with the value  $0000_{\rm b}$ . If they match, the SRI4K returns its Chip\_ID value. If not, the SRI4K does not send any response.

The Pcall16() command, used together with the Slot\_marker() command, allows the reader to search for all the Chip\_IDs when there are more than one SRI4K device in Inventory state present in the reader field range.

Figure 26. Pcall16 request format

| SOF | Pcall | 16  | CRCL   | CRC <sub>H</sub> | EOF    |

|-----|-------|-----|--------|------------------|--------|

|     | 06h   | 04h | 8 bits | 8 bits           |        |

|     | 1     |     | I      | ı                | AI0767 |

Request parameter:

No parameter

Figure 27. Pcall16 response format

Response parameter:

• Chip\_ID of the SRI4K

Figure 28. Pcall16 frame exchange between reader and SRI4K

SRI4K SRI4K commands

## 8.3 Slot\_marker(SN) command

Command code = x6h

The SRI4K must be in Inventory state to interpret the Slot\_marker(SN) command.

The Slot\_marker byte code is divided into two parts:

- b<sub>3</sub> to b<sub>0</sub>: 4-bit command code with fixed value 6.

- b<sub>7</sub> to b<sub>4</sub>: 4 bits known as the Slot\_number (SN). They assume a value between 1 and

15. The value 0 is reserved by the Pcall16() command.

On receiving the Slot\_marker() command, the SRI4K compares its Chip\_slot\_number value with the Slot\_number value given in the command code. If they match, the SRI4K returns its Chip\_ID value. If not, the SRI4K does not send any response.

The Slot\_marker() command, used together with the Pcall16() command, allows the reader to search for all the Chip\_IDs when there are more than one SRI4K device in Inventory state present in the reader field range.

Figure 29. Slot\_marker request format

Request parameter:

x: Slot number

Figure 30. Slot\_marker response format

Response parameters:

Chip\_ID of the SRI4K

Figure 31. Slot\_marker frame exchange between reader and SRI4K

SRI4K commands SRI4K

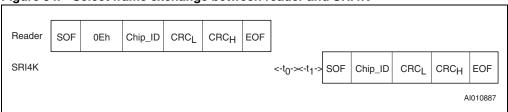

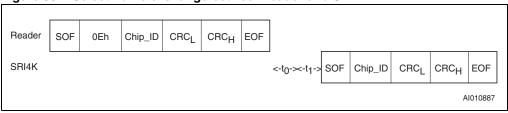

## 8.4 Select(Chip\_ID) command

Command code = 0Eh

The Select() command allows the SRI4K to enter the Selected state. Until this command is issued, the SRI4K will not accept any other command, except for Initiate(), Pcall16() and Slot\_marker(). The Select() command returns the 8 bits of the Chip\_ID value. An SRI4K in Selected state, that receives a Select() command with a Chip\_ID that does not match its own is automatically switched to Deselected state.

Figure 32. Select request format

| SOF | Select | Chip_ID | CRCL   | CRCH   | EOF     |

|-----|--------|---------|--------|--------|---------|

|     | 0Eh    | 8 bits  | 8 bits | 8 bits |         |

|     |        |         |        |        | AI07677 |

#### Request parameter:

• 8-bit Chip\_ID stored during the anticollision sequence

Figure 33. Select response format

#### Response parameters:

Chip\_ID of the selected tag. Must be equal to the transmitted Chip\_ID

Figure 34. Select frame exchange between reader and SRI4K

SRI4K SRI4K commands

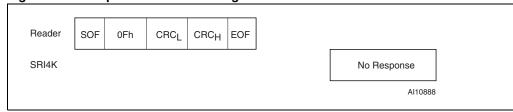

## 8.5 Completion() command

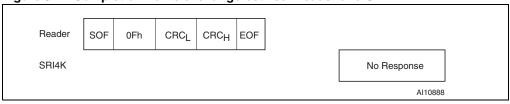

Command code = 0Fh

On receiving the Completion() command, an SRI4K in Selected state switches to Deactivated state and stops decoding any new commands. The SRI4K is then locked in this state until a complete reset (tag out of the field range). A new SRI4K can thus be accessed through a Select() command without having to remove the previous one from the field. The Completion() command does not generate a response.

All SRI4K devices not in Selected state ignore the Completion() command.

Figure 35. Completion request format

|   | SOF | Completion | CRCL   | CRCH   | EOF |          |

|---|-----|------------|--------|--------|-----|----------|

|   |     | 0Fh        | 8 bits | 8 bits |     |          |

| • |     |            |        |        |     | Al07679b |

Request parameters:

No parameter

Figure 36. Completion response format

Figure 37. Completion frame exchange between reader and SRI4K

SRI4K commands SRI4K

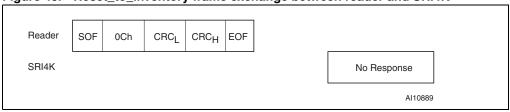

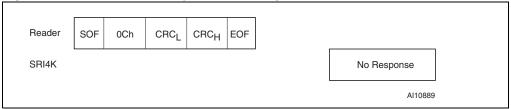

## 8.6 Reset\_to\_inventory() command

Command code = 0Ch

On receiving the Reset\_to\_inventory() command, all SRI4K devices in Selected state revert to Inventory state. The concerned SRI4K devices are thus resubmitted to the anticollision sequence. This command is useful when two SRI4K devices with the same 8-bit Chip\_ID happen to be in Selected state at the same time. Forcing them to go through the anticollision sequence again allows the reader to generates new Pcall16() commands and so, to set new random Chip\_IDs.

The Reset\_to\_inventory() command does not generate a response.

All SRI4K devices that are not in Selected state ignore the Reset\_to\_inventory() command.

Figure 38. Reset\_to\_inventory request format

| SOF | RESET_TO_INVENTORY | CRCL   | CRCH   | EOF |

|-----|--------------------|--------|--------|-----|

|     | 0Ch                | 8 bits | 8 bits |     |

|     |                    |        |        |     |

Request parameter:

No parameter

Figure 39. Reset\_to\_inventory response format

Figure 40. Reset\_to\_inventory frame exchange between reader and SRI4K

SRI4K SRI4K commands

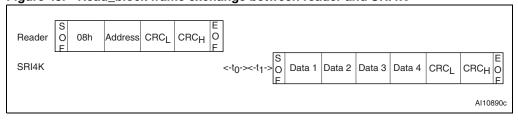

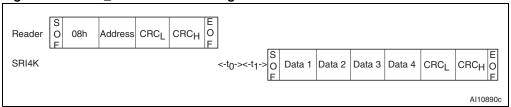

## 8.7 Read\_block(Addr) command

Command code = 08h

On receiving the Read\_block command, the SRI4K reads the desired block and returns the 4 data bytes contained in the block. Data bytes are transmitted with the least significant byte first and each byte is transmitted with the least significant bit first.

The address byte gives access to the 128 blocks of the SRI4K (addresses 0 to 127). Read\_block commands issued with a block address above 127 will not be interpreted and the SRI4K will not return any response, except for the System area located at address 255.

The SRI4K must have received a Select() command and be switched to Selected state before any Read\_block() command can be accepted. All Read\_block() commands sent to the SRI4K before a Select() command is issued are ignored.

Figure 41. Read\_block request format

| SOI NEAU_DIOUK Address CHOL CHOH | EOF | EOF | CRCH   | CRCL   | Address | Read_block | SOF |

|----------------------------------|-----|-----|--------|--------|---------|------------|-----|

| 08h 8 blts 8 bits 8 bits         |     |     | 8 bits | 8 bits | 8 blts  | 08h        |     |

#### Request parameter:

Address: block addresses from 0 to 127, or 255

Figure 42. Read\_block response format

| SOF | Data 1 | Data 2 | Data 3 | Data 4 | CRCL   | CRCH   | EOF |

|-----|--------|--------|--------|--------|--------|--------|-----|

|     | 8 blts | 8 blts | 8 blts | 8 blts | 8 bits | 8 blts |     |

#### Response parameters:

- Data 1: Less significant data byte

- Data 2: Data byte

- Data 3: Data byte

- Data 4: Most significant data byte

Figure 43. Read\_block frame exchange between reader and SRI4K

**SRI4K commands** SRI4K

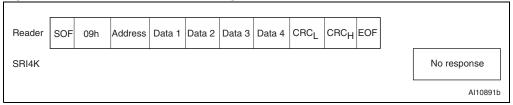

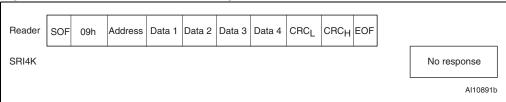

#### 8.8 Write\_block (Addr, Data) command

Command code = 09h

On receiving the Write\_block command, the SRI4K writes the 4 bytes contained in the command to the addressed block, provided that the block is available and not writeprotected. Data bytes are transmitted with the least significant byte first, and each byte is transmitted with the least significant bit first.

The address byte gives access to the 128 blocks of the SRI4K (addresses 0 to 127). Write block commands issued with a block address above 127 will not be interpreted and the SRI4K will not return any response, except for the System area located at address 255.

The result of the Write block command is submitted to the addressed block. See the following Figures for a complete description of the Write\_block command:

- Figure 12: Resettable OTP area (addresses 0 to 4).

- Figure 15: Binary counter (addresses 5 to 6).

- Figure 17: EEPROM (addresses 7 to 127).

The Write\_block command does not give rise to a response from the SRI4K. The reader must check after the programming time, t<sub>W</sub>, that the data was correctly programmed. The SRI4K must have received a Select() command and be switched to Selected state before any Write\_block command can be accepted. All Write\_block commands sent to the SRI4K before a Select() command is issued, are ignored.

Figure 44. Write\_block request format

| SOF | Write_block | Address | Data 1 | Data 2 | Data 3 | Data 4 | CRCL   | CRCH   | EOF      |

|-----|-------------|---------|--------|--------|--------|--------|--------|--------|----------|

|     | 09h         | 8 blts  | 8 blts | 8 blts | 8 blts | 8 blts | 8 bits | 8 blts |          |

|     |             |         |        |        |        | •      |        |        | A107687h |

- Request parameters:

- Address: block addresses from 0 to 127, or 255

- Data 1: Less significant data byte

- Data 2: Data byte

- Data 3: Data byte

- Data 4: Most significant data byte.

Figure 45. Write\_block response format

SRI4K SRI4K commands

Figure 46. Write\_block frame exchange between reader and SRI4K

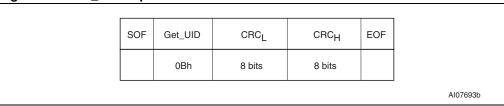

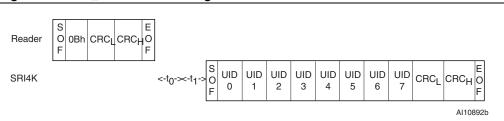

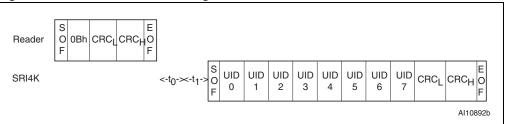

## 8.9 Get\_UID() command

Command code = 0Bh

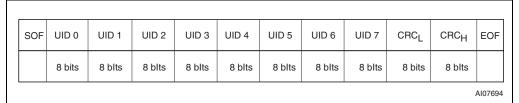

On receiving the Get\_UID command, the SRI4K returns its 8 UID bytes. UID bytes are transmitted with the least significant byte first, and each byte is transmitted with the least significant bit first.

The SRI4K must have received a Select() command and be switched to Selected state before any Get\_UID() command can be accepted. All Get\_UID() commands sent to the SRI4K before a Select() command is issued, are ignored.

Figure 47. Get\_UID request format

#### Request parameter:

No parameter

Figure 48. Get\_UID response format

Response parameters:

- UID 0: Less significant UID byte

- UID 1 to UID 6: UID bytes

- UID 7: Most significant UID byte.

SRI4K commands SRI4K

#### **Unique identifier (UID)**

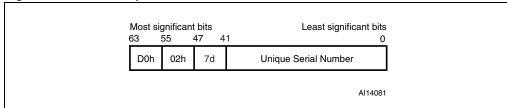

Members of the SRI4K family are uniquely identified by a 64-bit unique identifier (UID). This is used for addressing each SRI4K device uniquely after the anticollision loop. The UID complies with ISO/IEC 15963 and ISO/IEC 7816-6. It is a read-only code, and comprises (as summarized in *Figure 49*):

- an 8-bit prefix, with the most significant bits set to D0h

- an 8-bit IC manufacturer code (ISO/IEC 7816-6/AM1) set to 02h (for STMicroelectronics)

- a 6-bit IC code set to 00 0111b = 7d for SRI4K

- a 42-bit unique serial number

Figure 49. 64-bit unique identifier of the SRI4K

Figure 50. Get\_UID frame exchange between reader and SRI4K

#### 8.10 Power-on state

After power-on, the SRI4K is in the following state:

- It is in the low-power state.

- It is in Ready state.

- It shows highest impedance with respect to the reader antenna field.

- It will not respond to any command except Initiate().

SRI4K Maximum rating

# 9 Maximum rating

Stressing the device above the rating listed in the absolute maximum ratings table may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality documents.

Table 6. Absolute maximum ratings

| Symbol                              | Parameter                                      |                              |            | Max. | Unit   |

|-------------------------------------|------------------------------------------------|------------------------------|------------|------|--------|

| T <sub>STG</sub> , t <sub>STG</sub> | Storage conditions                             | Wafer                        | 15         | 25   | °C     |

|                                     | Storage conditions                             | (kept in its antistatic bag) |            | 23   | months |

| I <sub>CC</sub>                     | Supply current on AC0 / AC1                    |                              | -20        | 20   | mA     |

| V <sub>MAX</sub>                    | Input voltage on AC0 / AC1                     |                              | <b>-</b> 7 | 7    | V      |

| V <sub>ESD</sub>                    | Electrostatic discharge voltage <sup>(1)</sup> | Machine model                | -100       | 100  | V      |

|                                     |                                                | Human body model             | -1000      | 1000 | V      |

<sup>1.</sup> Mil. Std. 883 - Method 3015

#### DC and ac parameters 10

Table 7. Operating conditions

| Symbol         | Parameter                     | Min. | Max. | Unit |

|----------------|-------------------------------|------|------|------|

| T <sub>A</sub> | Ambient operating temperature |      | 85   | °C   |

#### Table 8. DC characteristics

| Symbol           | Parameter                        | Condition               | Min | Тур | Max | Unit |

|------------------|----------------------------------|-------------------------|-----|-----|-----|------|

| V <sub>CC</sub>  | Regulated voltage                |                         | 2.5 |     | 3.5 | V    |

| I <sub>CC</sub>  | Supply current (active in read)  | V <sub>CC</sub> = 3.0 V |     |     | 100 | μΑ   |

| I <sub>CC</sub>  | Supply current (active in write) | V <sub>CC</sub> = 3.0 V |     |     | 250 | μΑ   |

| V <sub>RET</sub> | Retromodulation induced voltage  | ISO 10373-6             | 20  |     |     | mV   |

| C <sub>TUN</sub> | Internal tuning capacitor        | 13.56 MHz               |     | 64  |     | pF   |

AC characteristics<sup>(1)</sup> Table 9.

| Symbol                              | Parameter                                          | Condition                      |               | Max | Unit |

|-------------------------------------|----------------------------------------------------|--------------------------------|---------------|-----|------|

| f <sub>CC</sub>                     | External RF signal frequency                       |                                | 13.553 13.567 |     | MHz  |

| MI <sub>CARRIER</sub>               | Carrier modulation index                           | MI=(A-B)/(A+B)                 | 8             | 14  | %    |

| t <sub>RFR</sub> , t <sub>RFF</sub> | 10% Rise and Fall times                            |                                | 0.8           | 2.5 | μs   |

| t <sub>RFSBL</sub>                  | Minimum pulse width for Start bit                  | ETU = 128/f <sub>CC</sub>      | 9.44          |     | μs   |

| t <sub>JIT</sub>                    | ASK modulation data jitter                         | Coupler to SRI4K               | -2            | +2  | μs   |

| t <sub>MIN CD</sub>                 | Minimum time from carrier generation to first data |                                | 5             |     | ms   |

| f <sub>S</sub>                      | Subcarrier frequency                               | f <sub>CC</sub> /16            | 847.5         |     | kHz  |

| t <sub>0</sub>                      | Antenna reversal delay                             | 128/f <sub>S</sub>             | 151           |     | μs   |

| t <sub>1</sub>                      | Synchronization delay                              | 128/f <sub>S</sub>             | 151           |     | μs   |

| t <sub>2</sub>                      | Answer to new request delay                        | 14 ETU                         | 132           |     | μs   |

| t <sub>DR</sub>                     | Time between request characters                    | Coupler to SRI4K               | 0             | 57  | μs   |

| t <sub>DA</sub>                     | Time between answer characters                     | SRI4K to coupler               | 0             |     | μs   |

|                                     |                                                    | With no auto-erase cycle (OTP) |               | 3   | ms   |

| t <sub>W</sub>                      | Programming time for write                         | With auto-erase cycle (EEPROM) |               | 5   | ms   |

|                                     |                                                    | Binary counter decrement       |               | 7   |      |

All timing measurements were performed on a reference antenna with the following characteristics: External size: 75 mm x 48 mm Number of turns: 3 Width of conductor: 1 mm Space between 2 conductors: 0.4 mm Value of the coil: 1.4  $\mu$ H Tuning Frequency: 14.4 MHz.

SRI4K DC and ac parameters

ASK Modulated signal from the Reader to the Contactless device  $f_{CC}$ t<sub>RFSBL</sub>  $t_{\mathsf{MIN}\;\mathsf{CD}}$ FRAME Transmission between the reader and the contactless device FRAME Transmitted by the reader in ASK 847KHz FRAME Transmitted by the SRI4K in BPSK Data jitter on FRAME Transmitted by the reader in ASK  $t_{\mathsf{JIT}}$ START  $t_{\mathsf{RFSBL}}$  $t_{\mathsf{RFSBL}}$  $t_{RFSBL}$  $t_{\mathsf{RFSBL}}$  $t_{\mathsf{RFSBL}}$ AI10893

Figure 51. SRI4K synchronous timing, transmit and receive

Part numbering SRI4K

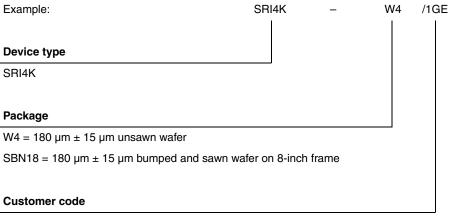

## 11 Part numbering

Table 10. Ordering information scheme

1GE = generic product

xxx = customer code after personalization

Note: Devices are shipped from the factory with the memory content bits erased to 1.

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST sales office.

## Appendix A ISO-14443 Type B CRC calculation

```

#include <stdio.h>

#include <stdlib.h>

#include <string.h>

#include <ctype.h>

#define BYTE unsigned char

#define USHORT unsigned short

unsigned short UpdateCrc(BYTE ch, USHORT *lpwCrc)

ch = (ch^{(BYTE)}((*lpwCrc) \& 0x00FF));

ch = (ch^{(ch << 4))};

*lpwCrc = (*lpwCrc >> 8)^((USHORT)ch <<

8) ^((USHORT)ch<<3) ^((USHORT)ch>>4);

return(*lpwCrc);

void ComputeCrc(char *Data, int Length, BYTE *TransmitFirst, BYTE

*TransmitSecond)

BYTE chBlock; USHORTt wCrc;

wCrc = 0xFFFF; // ISO 3309

do

chBlock = *Data++;

UpdateCrc(chBlock, &wCrc);

} while (--Length);

wCrc = \sim wCrc; // ISO 3309

*TransmitFirst = (BYTE) (wCrc & 0xFF);

*TransmitSecond = (BYTE) ((wCrc >> 8) & 0xFF);

return;

}

int main(void)

BYTE BuffCRC_B[10] = \{0x0A, 0x12, 0x34, 0x56\}, First, Second, i;

printf("Crc-16 G(x) = x^16 + x^12 + x^5 + 1");

printf("CRC_B of [ ");

for (i=0; i<4; i++)

printf("%02X ",BuffCRC_B[i]);

ComputeCrc(BuffCRC_B, 4, &First, &Second);

printf("] Transmitted: %02X then %02X.", First, Second);

return(0);

```

# Appendix B SRI4K command summary

Figure 52. Initiate frame exchange between reader and SRI4K

Figure 53. Pcall16 frame exchange between reader and SRI4K

Figure 54. Slot\_marker frame exchange between reader and SRI4K

Figure 55. Select frame exchange between reader and SRI4K

Figure 56. Completion frame exchange between reader and SRI4K

Figure 57. Reset\_to\_inventory frame exchange between reader and SRI4K

Figure 58. Read\_block frame exchange between reader and SRI4K

Figure 59. Write\_block frame exchange between reader and SRI4K

Figure 60. Get\_UID frame exchange between reader and SRI4K

Revision history SRI4K

# **Revision history**

Table 11. Document revision history

| Date        | Version | Changes                                                                                                                                                                                                                                                                                                                                                                  |  |

|-------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 13-Jan-2005 | 1.0     | First issue                                                                                                                                                                                                                                                                                                                                                              |  |

| 01-Sep-2005 | 2.0     | Updated initial counter values in 32-bit binary counters on page 16.                                                                                                                                                                                                                                                                                                     |  |

| 10-Apr-2007 | 3       | Document reformatted. Small text changes.  All antennas are ECOPACK® compliant.  Unique identifier (UID) on page 36 added. C <sub>TUN</sub> min and max values removed, typical value added in Table 8: DC characteristics.  Space removed between t0 and t1 in the "frame exchange between Reader and SRI4K" Figures (see Appendix B: SRI4K command summary on page 42. |  |