### Description

The  $\mu$ PD6307 can directly drive any multiplexed LCD organized with up to 32 rows. It is easily cascaded to 128 rows.

#### Features

- ☐ High voltage output 21 V maximum

- □ Directly controllable by the μPD72030

□ CMOS technology

- ☐ Single 5 V ±10% power supply

### **Ordering Information**

| Part Number | Package Type                             |

|-------------|------------------------------------------|

| µPD6307G-F  | 54-pin plastic miniflat                  |

| μPD6307G-R  | 54-pin plastic miniflat (inverted leads) |

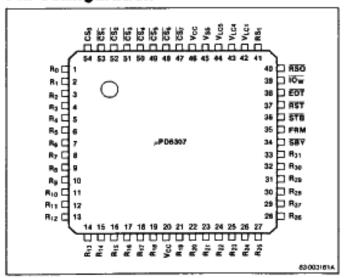

### Pin Configuration

#### Pin Identification

| No.            | Symbol                            | Function                                      |  |  |

|----------------|-----------------------------------|-----------------------------------------------|--|--|

| 1-19.<br>21-23 | R <sub>0</sub> -R <sub>31</sub>   | Row drive output                              |  |  |

| 20             | V <sub>CC</sub>                   | Positive power supply                         |  |  |

| 34             | SBY                               | Standby input                                 |  |  |

| 35             | FRM                               | Frame input                                   |  |  |

| 36             | STB                               | Strobe input                                  |  |  |

| 37             | RST                               | Reset input                                   |  |  |

| 38             | EOT                               | End of transfer input                         |  |  |

| 39             | iow                               | 1/0 write input                               |  |  |

| 40, 41         | RS <sub>0</sub> . RS <sub>1</sub> | Row select input                              |  |  |

| 42-44          | VLC1, VLC4, VLC5                  | LCD drive supply                              |  |  |

| 45             | V <sub>SS</sub>                   | Ground                                        |  |  |

| 46             | VCC (- VLCO)                      | Positive power supply and<br>LCD drive supply |  |  |

| 47-54          | CS7-CS0                           | Chip select output                            |  |  |

#### Pin Functions

# Ro-R31 (Row Drive Output)

LCD row drive output.

# CS<sub>0</sub>-CS<sub>7</sub> (Chip Select)

Column driver chip select. These outputs are generated by the CS counter and RSn-RS1.

# V<sub>LC1</sub>, V<sub>LC4</sub>, V<sub>LC5</sub> (LCD Drive Supply)

Reference voltages used to drive Ro-R31.

# RS<sub>0</sub>, RS<sub>1</sub> (Row Select)

This input selects the row driver cascade connection. It enables expansion to 128 row drive outputs and 32 CS outputs, as shown in table 1.

### FRM (Frame)

A high level input to this pin displays a positive frame and a low level input displays a negative frame. At the falling or rising edge of the signal, the row counter is cleared and the row driver is started from Ro.

### STB (Strobe)

Row drive strobe input. One STB pulse input at the timing interval causes the display of the next row.

### IOW (I/O Write)

This input increments the CS counter signal following 10 low level IOW pulses.

### EOT (End of Transfer)

This input clears the CS counter when it goes active low.

### RST (Reset)

This is the row driver reset input. A low input clears the internal counter and row outputs Ro-Ra1, and sets the CS<sub>0</sub>-CS<sub>7</sub> outputs to a high level.

# SBY (Standby)

This is the standby input. A low level input to this pin sets the row outputs R<sub>0</sub>-R<sub>31</sub> to V<sub>LC0</sub>. Before entering standby mode, set all column driver display data to high level.

# V<sub>CC</sub> (= V<sub>LC0</sub>) (Power Supply and LCD Drive Supply)

Connect the 5 V power supply between V<sub>CC</sub> and V<sub>SS</sub> for logic circuit operation. This pin is also used for the row drive voltage output.

# V<sub>SS</sub> (Ground)

Ground.

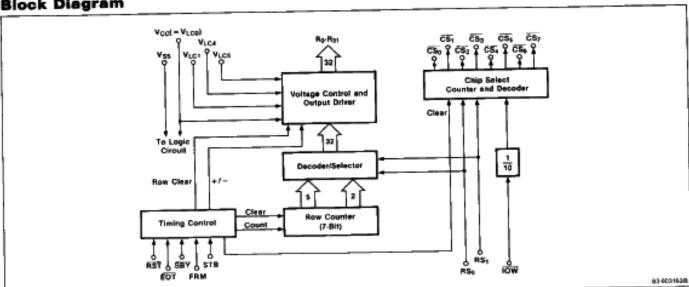

# **Block Diagram**

### **Functional Description**

### **Timing Control Circuit**

This circuit controls the timing for each internal block. FRM, RS<sub>0</sub>, RS<sub>1</sub>, RST, and SBY are sampled at the leading edge of STB, and then supplied to other internal circuits.

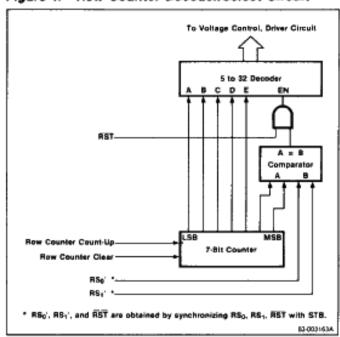

#### Row Counter Decoder/Select Circuit

As shown in figure 1, this circuit consists of a 7-bit counter, a comparator, and a 5 to 32 decoder. The 7-bit counter can accommodate 128 rows. The comparator acts to clear R<sub>0</sub>-R<sub>31</sub> if the upper two bits of the counter do not match RS<sub>0</sub> and RS<sub>1</sub>. If they match, one of R<sub>0</sub>-R<sub>31</sub>, indicated by the lower five bits of the row counter, is selected and the rest are cleared. RS<sub>0</sub> and RS<sub>1</sub> allow for cascading as shown in table 1. Table 2 shows the row select logic.

Figure 1. Row Counter Decoder/Select Circuit

Table 1. RSo and RS1 Row Cascading

| RSO | RS <sub>1</sub> | Row Signal                        | Chip Select                        |

|-----|-----------------|-----------------------------------|------------------------------------|

| 0   | 0               | R <sub>0</sub> -R <sub>31</sub>   | ₹\$ <sub>0</sub> -₹\$ <sub>7</sub> |

| 0   | 1               | R <sub>32</sub> -R <sub>63</sub>  | CS <sub>8</sub> -CS <sub>15</sub>  |

| 1   | 0               | R <sub>64</sub> -R <sub>95</sub>  | CS <sub>16</sub> -CS <sub>23</sub> |

| 1   | 1               | R <sub>96*</sub> R <sub>127</sub> | <u>CS₂4-CS₃1</u>                   |

Table 2. Row Select Logic

| EN | ŧ | D | c | В |   | Selected<br>Row Signal |

|----|---|---|---|---|---|------------------------|

| 1  | 0 | 0 | 0 | 0 | 0 | Ro                     |

| 1  | 0 | 0 | 0 | 0 | 1 | R <sub>1</sub>         |

| 1  | + | + | + | + | + | Rn                     |

| 1  | 1 | 1 | 1 | 1 | 0 | R <sub>30</sub>        |

| 1  | 1 | 1 | 1 | 1 | 1 | R <sub>31</sub>        |

| 0  | × | х | х | × | х | None                   |

### **Voltage Control Driver Circuit**

This circuit generates the row signals for AC drive of the LCD panel. A low level  $\overline{RST}$  clears the output. A low level  $\overline{SSY}$  sets the output  $V_{LC0}$ . Table 2 shows the  $R_0$ - $R_{31}$  output levels.

Table 2. Ro-R31 Outputs Levels

| Function | + (FRM = 1)      | - (FRM = 0)      |

|----------|------------------|------------------|

| Select   | V <sub>LC5</sub> | V <sub>LQ0</sub> |

| Clear    | V <sub>LC4</sub> | V <sub>LC1</sub> |

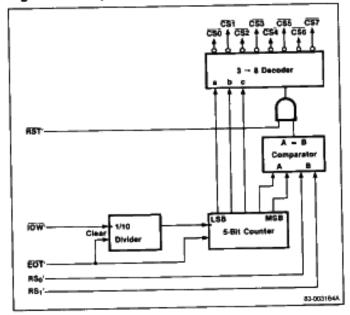

#### Chip Select Counter/Decoder Circuit

This circuit, shown in figure 2, generates the column driver  $\overline{CS}$  signal. This circuit has a 5-bit counter to generate up to 32  $\overline{CS}$  signals. The 5-bit counter is incremented once for every 10  $\overline{IOW}$  (active low) pulses. If the upper two bits of the chip select counter do not match  $RS_0$  and  $RS_1$ , all the  $\overline{CS_0}$ - $\overline{CS_7}$  outputs are set to high level. If they match, one of  $\overline{CS_0}$ - $\overline{CS_7}$  (indicated by the lower three bits of the chip select counter) goes low. If  $\overline{RST}$  is low,  $\overline{CS_0}$ - $\overline{CS_7}$  become high level. Table 3 shows the chip select logic.

Figure 2. Chip Select Counter/Decoder Circuit

Table 3. Chip Select Logic

| EN | c   | b |   | Chip Select      |

|----|-----|---|---|------------------|

| 1  | 0   | 0 | 0 | CS₀              |

| 1  | . 0 | 0 | 1 | CS <sub>1</sub>  |

| 1  | 0   | 1 | 0 | CS <sub>2</sub>  |

| 1  | 0   | 1 | 1 | CS <sub>3</sub>  |

| 1  | 1   | 0 | 0 | CS₄_             |

| 1  | 1   | 0 | 1 | ₹5 <sub>5</sub>  |

| 1  | 1   | 1 | 0 | Ĉ\$ <sub>6</sub> |

| 1  | 1   | 1 | 1 | CS <sub>7</sub>  |

| 0  | ×   | Х | X | Disabled         |