# INTEGRATED CIRCUITS

Product data Supersedes data of 2001 Apr 24 File under Integrated Circuits, Standard Analog 2001 Aug 22

### NE56605-42

#### **GENERAL DESCRIPTION**

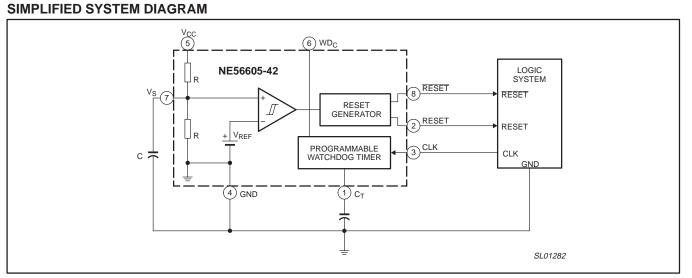

The NE56605-42 is designed to generate a reset signal, at a threshold voltage of 4.2 V, for a variety of microprocessor and logic systems. Accurate reset signals are generated during momentary power interruptions, or whenever power supply voltages sag to intolerable levels. The NE56605-42 has a built-in Watchdog Timer to monitor the microprocessor and ensure it is operating properly. Any abnormal system operations due to microprocessor malfunctions are terminated by the watchdog's generating a system reset. The NE56605-42 has a watchdog monitoring time of 10 ms (typical).

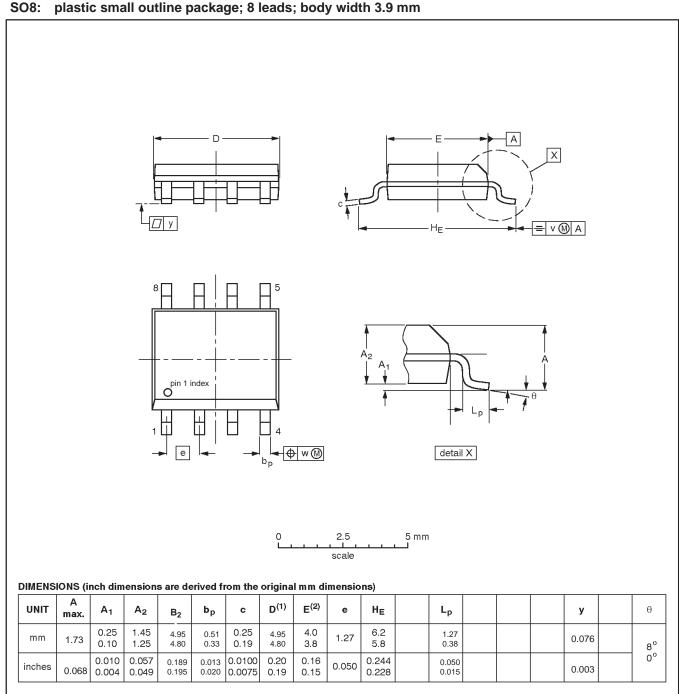

The NE56605-42 is offered in the SO8 surface mount package.

### FEATURES

- Both positive and negative logic reset output signals are available

- Accurate threshold detection

- Internal power-on reset delay

- Internal watchdog timer programmable with external capacitor

- Watchdog monitoring time of 10 ms

- Reset assertion with V<sub>CC</sub> down to 0.8 V<sub>DC</sub> (typical)

- Few external components required.

### APPLICATIONS

- Microcomputer systems

- Logic systems.

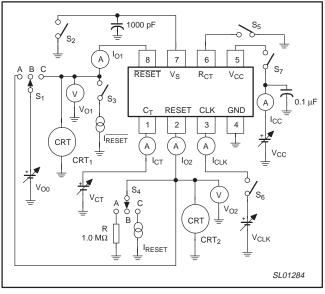

Figure 1. Simplified system diagram.

### **ORDERING INFORMATION**

| TYPE NUMBER | PACKAGE |                                                           | TEMPERATURE   |

|-------------|---------|-----------------------------------------------------------|---------------|

|             | NAME    | DESCRIPTION                                               | RANGE         |

| NE56605-42D | SO8     | plastic small outline package; 8 leads; body width 3.9 mm | –20 to +70 °C |

### NE56605-42

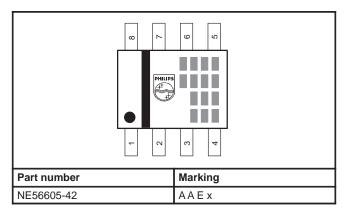

#### Part number marking

The package is marked with a four letter code in the first line to the right of the logo. The first three letters designate the product. The fourth letter, represented by 'x', is a date tracking code. The remaining two or three lines of characters are internal manufacturing codes.

#### PIN DESCRIPTION

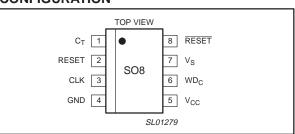

#### PIN SYMBOL DESCRIPTION 1 t<sub>WDM</sub>, t<sub>WDR</sub>, t<sub>PR</sub> adjustment pin. $C_T$ t<sub>WDM</sub>, t<sub>WDR</sub>, t<sub>PR</sub> times are dependent on the value of external C<sub>T</sub> capacitor used. See Figure 18 (Timing Diagram) for definition of t<sub>WDM</sub>, t<sub>WDR</sub>, t<sub>PR</sub> times. RESET 2 Reset HIGH output pin. 3 CLK Clock input pin from logic system for watchdog timer. 4 GND Circuit ground. 5 Power supply pin for circuit. V<sub>CC</sub> 6 WD<sub>C</sub> Watchdog timer control pin. The watchdog timer is enabled when this pin is unconnected, and disabled when this pin is connected to ground. 7 $V_{S}$ Detection threshold adjustment pin. The detection threshold can be increased by connecting this pin to $V_{CC}$ with a pull-up resistor. The detection threshold can be decreased by connecting this pin to ground with a pull-down resistor. 8 RESET Reset LOW output pin.

#### MAXIMUM RATINGS

| SYMBOL            | PARAMETER                   | MIN. | MAX. | UNIT |

|-------------------|-----------------------------|------|------|------|

| V <sub>CC</sub>   | Power supply voltage        | -0.3 | 10   | V    |

| V <sub>S</sub>    | V <sub>S</sub> pin voltage  | -0.3 | 10   | V    |

| V <sub>CLK</sub>  | CLK pin voltage             | -0.3 | 10   | V    |

| V <sub>OH</sub>   | RESET and RESET pin voltage | -0.3 | 10   | V    |

| T <sub>oper</sub> | Operating temperature       | -20  | 70   | °C   |

| T <sub>stg</sub>  | Storage temperature         | -40  | 125  | °C   |

| Р                 | Power dissipation           | -    | 250  | mW   |

### 2001 Aug 22 Downloaded from <u>Elcodis.com</u> electronic components distributor

# PIN CONFIGURATION

Figure 2. Pin configuration.

### DC ELECTRICAL CHARACTERISTICS

Characteristics measured with V<sub>CC</sub> = 5.0 V, and T<sub>amb</sub> = 25 °C, unless otherwise specified. See Figure 23 (Test circuit 1) for test configuration used for DC parameters.

| SYMBOL                          | PARAMETER                                      | CONDITIONS                                                                     | MIN. | TYP.  | MAX. | UNIT |

|---------------------------------|------------------------------------------------|--------------------------------------------------------------------------------|------|-------|------|------|

| I <sub>CC</sub>                 | Supply current during watchdog timer operation |                                                                                | _    | 0.7   | 1.0  | mA   |

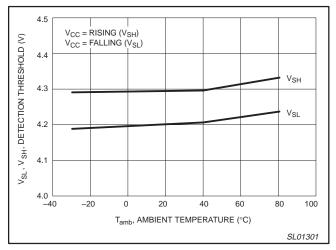

| V <sub>SL</sub>                 | Reset detection threshold                      | $V_{S}$ = open; $V_{CC}$ = falling                                             | 4.05 | 4.20  | 4.35 | V    |

| V <sub>SH</sub>                 | Reset detection threshold                      | $V_S$ = open; $V_{CC}$ = rising                                                | 4.15 | 4.30  | 4.45 | V    |

| $\Delta V_{S} / \Delta T_{amb}$ | Temperature coefficient of reset threshold     | $-20 \text{ °C} \le T_{amb} \le 70 \text{ °C}$                                 | -    | ±0.01 | -    | %/°C |

| V <sub>hys</sub>                | Reset threshold hysteresis                     | $V_{HYS} = V_{SH} \text{ (rising } V_{CC}) - V_{SL} \text{ (falling } V_{CC})$ | 50   | 100   | 150  | mV   |

| V <sub>TH</sub>                 | CLK input threshold                            |                                                                                | 0.8  | 1.2   | 2.0  | V    |

| I <sub>IH</sub>                 | CLK input current, HIGH-level                  | V <sub>CLK</sub> = 5.0 V                                                       | -    | 0     | 1.0  | μΑ   |

| I <sub>IL</sub>                 | CLK input current, LOW-level                   | V <sub>CLK</sub> = 0 V                                                         | -20  | -10   | -3.0 | μA   |

| V <sub>OH1</sub>                | Output voltage, HIGH-level                     | I <sub>RESET</sub> = –5.0 μA; V <sub>S</sub> = open                            | 4.5  | 4.8   | -    | V    |

| V <sub>OH2</sub>                | 1                                              | $I_{RESET}$ current = -5.0 mA; $V_{S}$ = 0 V                                   | 4.5  | 4.8   | -    | V    |

| V <sub>OL1</sub>                | Output voltage, LOW-level                      | $I_{\overline{RESET}} = 3.0 \text{ mA}; \text{ V}_{S} = 0 \text{ V}$           | -    | 0.2   | 0.4  | V    |

| V <sub>OL2</sub>                | 1                                              | $I_{\overline{RESET}} = 10 \text{ mA}; \text{ V}_{\text{S}} = 0 \text{ V}$     | _    | 0.3   | 0.5  | V    |

| V <sub>OL3</sub>                | 1                                              | I <sub>RESET</sub> = 0.5 mA; V <sub>S</sub> = open                             | -    | 0.2   | 0.4  | V    |

| V <sub>OL4</sub>                | 1                                              | I <sub>RESET</sub> = 1.0 mA; V <sub>S</sub> = open                             | -    | 0.3   | 0.5  | V    |

| I <sub>OL1</sub>                | Output sink current                            | $V_{RESET} = 1.0 \text{ V}; \text{ V}_{S} = 0 \text{ V}$                       | 10   | 16    | -    | mA   |

| I <sub>OL2</sub>                | 1                                              | V <sub>RESET</sub> = 1.0 V; V <sub>S</sub> = open                              | 1.0  | 2.0   | -    | mA   |

| I <sub>CT1</sub>                | C <sub>T</sub> charge current                  | $V_{CT} = 1.0 V$ ; $WD_{C} = open during watchdog operation$                   | -8   | -12   | -24  | μA   |

| I <sub>CT2</sub>                | ]                                              | V <sub>CT</sub> = 1.0 V;<br>during power-on reset operation                    | -0.8 | -1.2  | -2.4 | μA   |

| V <sub>CCL1</sub>               | Supply voltage to assert reset operation       | $\frac{V_{RESET}}{RESET} = 0.4 \text{ V};$                                     | _    | 0.8   | 1.0  | V    |

| V <sub>CCL2</sub>               |                                                | $V_{RESET} = V_{CC} - 0.1 V;$<br>1 M $\Omega$ resistor (pin 2 to GND)          | _    | 0.8   | 1.0  | V    |

### NE56605-42

### AC ELECTRICAL CHARACTERISTICS

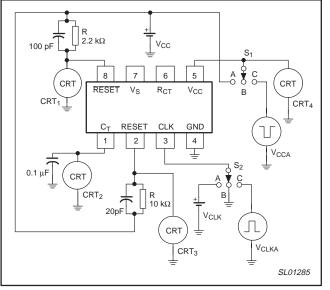

Characteristics measured with  $V_{CC} = 5.0 \text{ V}$ , and  $T_{amb} = 25 \text{ °C}$ , unless otherwise specified. See Figure 24 (Test circuit 2) for test configuration used for AC parameters.

| SYMBOL            | PARAMETER                                      | CONDITIONS                                                                              | MIN. | TYP. | MAX. | UNIT |

|-------------------|------------------------------------------------|-----------------------------------------------------------------------------------------|------|------|------|------|

| t <sub>P1</sub>   | Minimum power supply pulse width for detection | 4.0 V $\leq$ negative-going V <sub>CC</sub> pulse $\leq$ 5.0 V                          | 8.0  | -    | -    | μs   |

| t <sub>CLKW</sub> | Clock input pulse width                        |                                                                                         | 3.0  | -    | -    | μs   |

| t <sub>CLK</sub>  | Clock input cycle                              |                                                                                         | 20   | -    | -    | μs   |

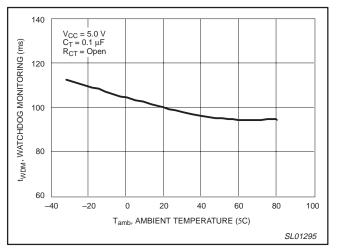

| t <sub>WDM</sub>  | Watchdog monitoring time (Notes 1, 6)          | $C_T = 0.1 \ \mu F; R_{CT} = open$                                                      | 5.0  | 10   | 15   | ms   |

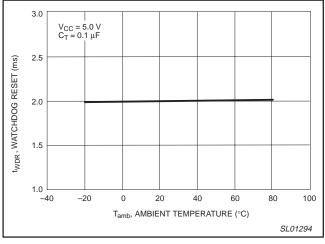

| t <sub>WDR</sub>  | Watchdog reset time (Notes 2, 6)               | $C_T = 0.1 \ \mu F$                                                                     | 1.0  | 2.0  | 3.0  | ms   |

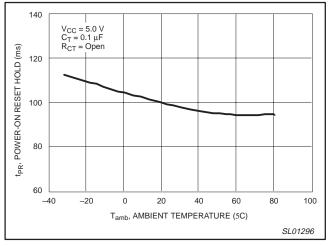

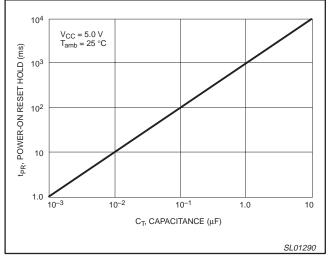

| t <sub>PR</sub>   | Power-on reset delay time (Notes 3, 6)         | $V_{CC}$ = rising from 0 V; $C_T$ = 0.1 $\mu$ F                                         | 50   | 100  | 150  | ms   |

| t <sub>PD1</sub>  | RESET, RESET propagation delay time            | $\overline{\text{RESET}}$ : R <sub>L1</sub> = 2.2 k $\Omega$ ; C <sub>L1</sub> = 100 pF | -    | 2.0  | 10   | μs   |

| t <sub>PD2</sub>  | (Note 4)                                       | RESET: $R_{L2}$ = 10 kΩ; $C_{L2}$ = 20 pF                                               | -    | 3.0  | 10   | μs   |

| t <sub>R1</sub>   | RESET, RESET rise time (Note 5)                | $\overline{\text{RESET}}$ : R <sub>L1</sub> = 2.2 k $\Omega$ ; C <sub>L1</sub> = 100 pF | -    | 1.0  | 1.5  | μs   |

| t <sub>R2</sub>   | ]                                              | RESET: $R_{L2}$ = 10 kΩ; $C_{L2}$ = 20 pF                                               | -    | 1.0  | 1.5  | μs   |

| t <sub>F1</sub>   | RESET, RESET fall time (Note 5)                | $\overline{\text{RESET}}$ : R <sub>L1</sub> = 2.2 kΩ; C <sub>L1</sub> = 100 pF          | -    | 0.1  | 0.5  | μs   |

| t <sub>F2</sub>   | ]                                              | RESET: R <sub>L2</sub> = 10 kΩ; C <sub>L2</sub> = 20 pF                                 | _    | 0.5  | 1.0  | μs   |

NOTES:

1. 'Watchdog monitoring time' is the duration from the last pulse (negative-going edge) of the timer clear clock pulse until reset output pulse occurs (see Figure 18). A reset signal is output if a clock pulse is not input during this time.

2. 'Watchdog reset time' is the reset pulse width (see Figure 18).

'Power-on reset delay time' is the duration measured from the time V<sub>CC</sub> exceeds the upper detection threshold (V<sub>SH</sub>) and power-on reset release is experienced (RESET output HIGH; RESET output LOW).

'RESET, RESET propagation delay time' is the duration from when the supply voltage sags below the lower detection threshold (V<sub>SL</sub>) and reset occurs (RESET output LOW, RESET output HIGH).

5. RESET, RESET rise and fall times are measured at 10% and 90% output levels.

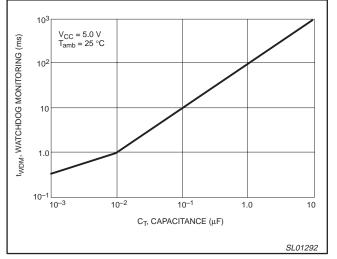

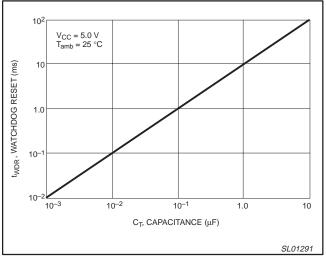

Watchdog monitoring time (t<sub>WDM</sub>), watchdog reset time (t<sub>WDR</sub>), and power-on reset delay time (t<sub>PR</sub>) during power-on can be modified by varying the C<sub>T</sub> capacitance. The times can be approximated by applying the following formula. The recommended range for C<sub>T</sub> is 0.001 μF to 10 μF.

Formula 1. Calculation for approximate  $t_{PR}$ ,  $t_{WDM}$ , and  $t_{WDR}$  values:

$\begin{array}{l} t_{PR} \ (ms) \approx 1000 \times C_T \ (\mu F) \\ t_{WDM} \ (ms) \approx 100 \times C_T \ (\mu F) \\ t_{WDR} \ (ms) \approx 20 \times C_T \ (\mu F) \end{array}$

Example: When  $C_T = 0.1 \ \mu F$  and  $WD_C =$  open:

t<sub>PR</sub> ≈ 100 ms t<sub>WDM</sub> ≈ 10 ms t<sub>WDR</sub> ≈ 2.0 ms

### NE56605-42

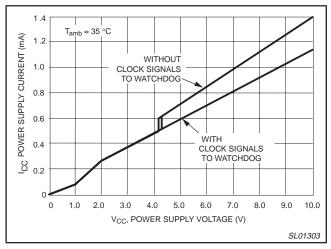

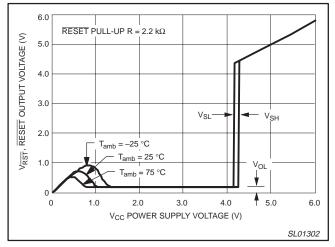

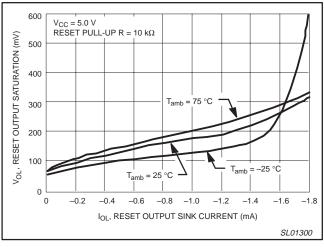

### TYPICAL PERFORMANCE CURVES

Figure 3. Power supply current versus voltage.

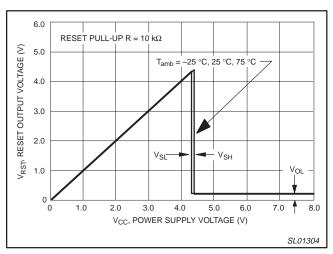

Figure 5. RESET output voltage versus supply voltage.

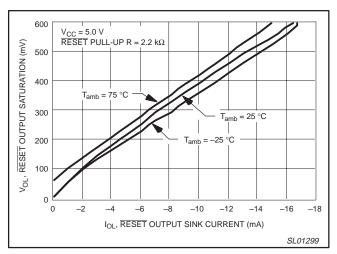

Figure 7. RESET saturation versus sink current.

Figure 4. RESET output voltage versus supply voltage.

Figure 6. Detection threshold versus temperature.

Figure 8. RESET saturation versus sink current.

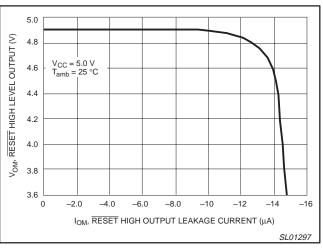

#### 5.2 $V_{CC} = 5.0 V$ $T_{amb} = 25 °C$ V<sub>OM</sub>, RESET HIGH LEVEL OUTPUT (V) 5.0 4.8 4.6 4.4 4.2 4.0 0 -2 -4 -6 -8 -10 -12 -14 -16 -18 $I_{\mbox{OM}},$ RESET HIGH OUTPUT LEAKAGE CURRENT ( $\mu A)$ SL01298

Figure 9. RESET HIGH-level voltage versus current.

Figure 11. Power-on reset hold time versus temperature.

Figure 13. Watchdog reset time versus temperature.

Figure 10. RESET HIGH-level voltage versus current.

Figure 12. Watchdog monitoring time versus temperature.

Figure 14. Power-on reset hold time versus C<sub>T</sub>.

Figure 16. Watchdog reset time versus C<sub>T</sub>.

Figure 15. Watchdog reset time versus C<sub>T</sub>.

### NE56605-42

### **TECHNICAL DESCRIPTION**

### **General discussion**

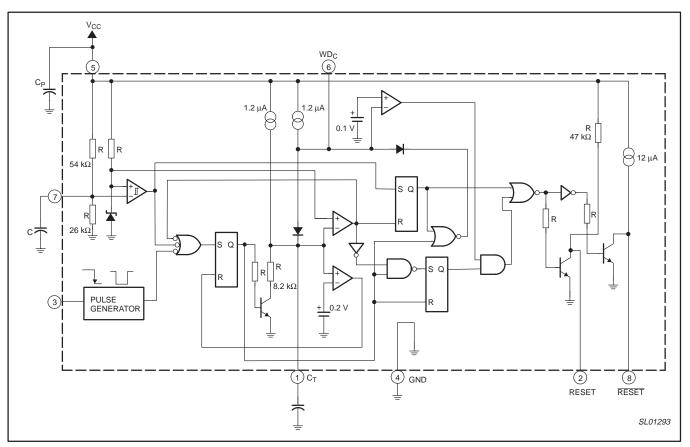

The NE56605-42 combines a watchdog timer and an undervoltage reset function in a single SO8 surface mount package. This provides a space-saving solution for maintaining proper operation of typical 5.0 volt microprocessor-based logic systems. Either function, or both, can force the microprocessor into a reset.

While the watchdog monitors the microprocessor operation, the undervoltage reset monitors the supply voltage to the microprocessor. If the microprocessor clock signal ceases or becomes erratic, the NE56605-42 outputs a reset signal to the microprocessor. If the microprocessor supply voltage sags to 4.2 volts or less, the NE56605-42 outputs a reset signal for the duration of the supply voltage deficiency. The undervoltage reset signal allows the microprocessor to shut down in an orderly manner to avoid system corruption. In addition to a single reset output, the NE56605-42 has complementary RESET and RESET outputs for system use. The undervoltage detection threshold incorporates hysteresis to prevent generating erratic resets.

The watchdog timer requires a pulse input. Normally this signal comes from the system microprocessor's clock. For operation, an

external capacitor (C<sub>T</sub>) must be connected from Pin 1 to ground. Normally a 0.1  $\mu$ F capacitor is used for C<sub>T</sub>. The C<sub>T</sub> capacitor and a fixed internal resistance establish the required minimum frequency of watchdog input signal for the device to **not** output a reset signal. In the absence of a watchdog input pulse, the C<sub>T</sub> capacitor charges to the 0.2 volt threshold of the internal comparator, causing a reset signal to be output. If microprocessor clock signals are received within the required interval, no watchdog reset signal will be output. Grounding the watchdog control pin (WD<sub>C</sub>, Pin 6) disables the watchdog function. Removing the ground from Pin 6, allowing it to float, enables the watchdog function has no effect on the undervoltage detection function.

Although the temperature coefficient of detection threshold is specified over a temperature of -20 °C to +70 °C, the device will support operation in excess of this temperature range. See the supporting curves for performance over the full temperature range of -30 °C to +85 °C. Some degradation in performance will be experienced at the temperature extremes and the system designer should take this into account.

Figure 17. Functional diagram.

#### Product data

### NE56605-42

#### **Timing diagram**

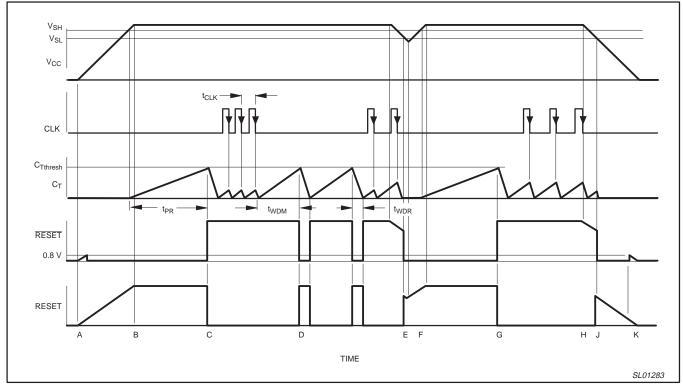

The timing diagram shown in Figure 18 depicts the operation of the device. Letters indicate events on the TIME axis.

A: At start-up 'A', the V<sub>CC</sub> and RESET voltages begin to rise. Also the RESET voltage initially rises, but then abruptly returns to a LOW state. This is due to V<sub>CC</sub> reaching the level (approximately 0.8 V) that activates the internal bias circuitry, asserting RESET.

**B:** Just before 'B', the C<sub>T</sub> voltage starts to ramp up. This is caused by, and coincident to, V<sub>CC</sub> reaching the threshold level of V<sub>SH</sub>. At this level the device is in full operation. The RESET output continues to rise as V<sub>CC</sub> rises above V<sub>SH</sub>. This is normal.

**C:** At 'C', V<sub>CC</sub> is above the undervoltage detect threshold, and C<sub>T</sub> has ramped up to its upper detect level. At this point, the device removes the hold on the resets. RESET goes HIGH while RESET goes LOW. Also, an internal ramp discharge transistor activates, discharging C<sub>T</sub>.

In a microprocessor-based system these events remove the reset from the microprocessor, allowing it to function normally. The system must send clock signals to the Watchdog Timer often enough to prevent  $C_T$  from ramping up to the  $C_T$  threshold, to prevent reset signals from being generated. Each clock signal discharges  $C_T$ .

**C–D:** Midway between 'C' and 'D', the CLK signals cease allowing the C<sub>T</sub> voltage to ramp up to its upper threshold at 'D'. At this time, reset signals are generated (RESET goes LOW; RESET goes HIGH). The device attempts to come out of reset as the C<sub>T</sub> voltage is discharged and finally does come out of reset when CLK signals are re-established after two attempts of C<sub>T</sub>.

**E–F:** Immediately before 'E', falling V<sub>CC</sub> causes the RESET signal to sag. CLK signals are still being received, C<sub>T</sub> is within normal operating range, and reset signals are not output. V<sub>CC</sub> continues to sag until the V<sub>SL</sub> undervoltage threshold is reached. At that time, reset signals are generated (RESET goes LOW; RESET goes HIGH).

At 'E', V<sub>CC</sub> starts to rise, and the Reset voltage rises with V<sub>CC</sub>. However, C<sub>T</sub> voltage does not start to ramp up until 'F' when V<sub>CC</sub> reaches the V<sub>SH</sub> upper threshold.

**G:** The reset outputs are released at 'G' when  $C_T$  reaches the upper threshold level again. After 'G', normal CLK signals are received, but at a lower frequency than those following event 'C'. The frequency is above the minimum frequency required to keep the device from outputting reset signals.

**G–H:** At 'H',  $V_{CC}$  is normal, CLK signals are being received, and no reset signals are output. At event 'H', the  $V_{CC}$  starts falling, causing RESET to also fall.

J: At event 'J', V<sub>CC</sub> sags to the point where the V<sub>SL</sub> undervoltage threshold point is reached, and at that level reset signals are output (RESET to a LOW state, and RESET to a HIGH state). As the V<sub>CC</sub> voltage falls lower, the Reset voltage falls lower.

**K:** At event 'K', the V<sub>CC</sub> voltage has deteriorated to a level where normal internal circuit bias is no longer able to maintain a  $\overrightarrow{\text{RESET}}$ , and as a result may exhibit a slight rise to something less than 0.8 V. As V<sub>CC</sub> decays even further,  $\overrightarrow{\text{RESET}}$  also decreases to zero.

Figure 18. Timing diagram.

NE56605-42

# System reset with built-in watchdog timer

#### Application information

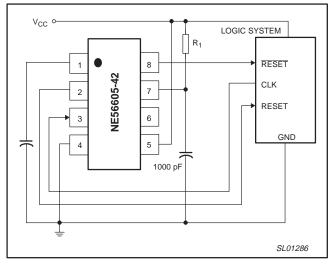

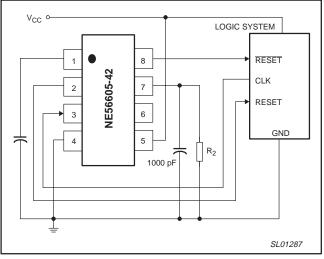

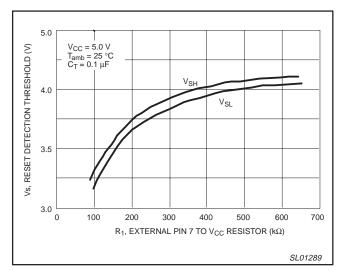

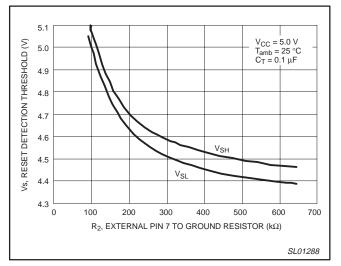

The detection threshold voltage can be adjusted by externally influencing the internal divider reference voltage. Figures 19 and 21 show a method to lower and raise the threshold voltage. Figures 20 and 22 show the influence of the pull-down and pull-up resistors on the threshold voltage. The use of a capacitor (1000 pF or larger) from Pin 7 to ground is recommended to filter out noise from being imposed on the threshold voltages.

Figure 19. Circuit to lower detection threshold.

Figure 21. Circuit to raise detection threshold.

The Reset Detection Threshold can be decreased by connecting an external resistor  $R_1$  from Pin 7 to  $V_{CC}$ , as shown in Figure 19. See Figure 20 to determine the approximate value of  $R_1$  to use.

The Reset Detection Threshold can be increased by connecting an external resistor  $R_2$  from Pin 7 to ground, as shown in Figure 21. See Figure 22 to determine the approximate value of  $R_2$  to use.

Figure 20. Reset detection threshold versus external R<sub>1</sub>.

Figure 22. Reset detection threshold versus external R<sub>2</sub>.

#### Parametric testing

DC and AC Characteristics can be tested using the circuits shown in Figures 23 and 24. Associated switch and power supply settings are shown in Table 1 and Table 2, respectively.

Figure 23. Test Circuit 1 (DC parameters).

| Table 1. DC characte | ristics Test Circuit 1 | switch and powe | supply settings |

|----------------------|------------------------|-----------------|-----------------|

|----------------------|------------------------|-----------------|-----------------|

|                                            |                   | _              |                |                       |                |                       | -              |                       |                 |                  |                 |         |         |                                    |

|--------------------------------------------|-------------------|----------------|----------------|-----------------------|----------------|-----------------------|----------------|-----------------------|-----------------|------------------|-----------------|---------|---------|------------------------------------|

| Parameter                                  | Symbol            | S <sub>1</sub> | S <sub>2</sub> | <b>S</b> <sub>3</sub> | S <sub>4</sub> | <b>S</b> <sub>5</sub> | S <sub>6</sub> | <b>S</b> <sub>7</sub> | V <sub>CC</sub> | V <sub>CLK</sub> | V <sub>CT</sub> | IRESET  | IRESET  | Read                               |

| Power supply current                       | I <sub>CC</sub>   | В              | OFF            | OFF                   | В              | OFF                   | ON             | ON                    | 5.0 V           | 5.0 V            | 0 V             | -       | -       | I <sub>CC</sub>                    |

| Reset threshold (LOW) (Note 1)             | V <sub>SL</sub>   | В              | OFF            | OFF                   | В              | ON                    | ON             | ON                    | 5.0 to 4.0 V    | 3.0 V            | 3.0 V           | -       | -       | V <sub>O1</sub> , CRT <sub>1</sub> |

| Reset threshold (HIGH) (Note 2)            | V <sub>SH</sub>   | В              | OFF            | OFF                   | В              | ON                    | ON             | ON                    | 4.0 to 5.0 V    | 3.0 V            | 3.0 V           | -       | -       | $V_{O1}, CRT_1$                    |

| Clock input threshold (Note 3)             | V <sub>TH</sub>   | В              | OFF            | OFF                   | В              | OFF                   | ON             | ON                    | 5.0 V           | 0 to 3.0 V       | 1.0V            | -       | -       | I <sub>CLK</sub>                   |

| Clock input current (HIGH)                 | I <sub>TH</sub>   | В              | OFF            | OFF                   | В              | OFF                   | ON             | ON                    | 5.0 V           | 5.0 V            | 0 V             | -       | -       | I <sub>CLK</sub>                   |

| Clock input current (LOW)                  | I <sub>TL</sub>   | В              | OFF            | OFF                   | В              | OFF                   | ON             | ON                    | 5.0 V           | 0 V              | 0 V             | -       | -       | I <sub>CLK</sub>                   |

| Reset output voltage (HIGH)                | V <sub>OH1</sub>  | В              | OFF            | ON                    | В              | ON                    | ON             | ON                    | 5.0 V           | 5.0 V            | 3.0 V           | –5.0 μA | -       | V <sub>O1</sub>                    |

|                                            | V <sub>OH2</sub>  | В              | ON             | OFF                   | С              | ON                    | ON             | ON                    | 5.0 V           | 5.0 V            | 3.0 V           | -       | –5.0 μA | V <sub>O2</sub>                    |

| Reset output voltage (LOW)                 | V <sub>OL1</sub>  | В              | ON             | ON                    | В              | ON                    | ON             | ON                    | 5.0 V           | 5.0 V            | 3.0 V           | 3.0 mA  | -       | V <sub>O1</sub>                    |

|                                            | V <sub>OL2</sub>  | В              | ON             | ON                    | В              | ON                    | ON             | ON                    | 5.0 V           | 5.0 V            | 3.0 V           | 10 mA   | -       | V <sub>O1</sub>                    |

|                                            | V <sub>OL3</sub>  | В              | OFF            | OFF                   | С              | ON                    | ON             | ON                    | 5.0 V           | 5.0 V            | 3.0 V           | -       | 0.5 mA  | V <sub>O2</sub>                    |

|                                            | V <sub>OL4</sub>  | В              | OFF            | OFF                   | С              | ON                    | ON             | ON                    | 5.0 V           | 5.0 V            | 3.0 V           | -       | 1.0 mA  | V <sub>O2</sub>                    |

| Reset output sink current                  | I <sub>OL1</sub>  | С              | ON             | OFF                   | В              | ON                    | ON             | ON                    | 5.0 V           | 5.0 V            | 3.0 V           | -       | -       | I <sub>O1</sub>                    |

| (Note 4)                                   | I <sub>OL2</sub>  | А              | OFF            | OFF                   | В              | ON                    | ON             | ON                    | 5.0 V           | 5.0 V            | 3.0 V           | -       | -       | I <sub>O2</sub>                    |

| C <sub>T</sub> charge current 1            | I <sub>CT1</sub>  | В              | OFF            | OFF                   | В              | OFF                   | OFF            | ON                    | 5.0 V           | -                | 1.0 V           | -       | -       | I <sub>CT</sub>                    |

| C <sub>T</sub> charge current 2            | I <sub>CT2</sub>  | В              | OFF            | OFF                   | В              | ON                    | OFF            | ON                    | 5.0 V           | -                | 1.0 V           | -       | -       | I <sub>CT</sub>                    |

| Minimum power supply for RESET (Note 5)    | V <sub>CCL1</sub> | В              | OFF            | ON                    | В              | ON                    | ON             | ON                    | 0 to 2.0 V      | 0 V              | 0 V             | -       | -       | V <sub>O1</sub> , V <sub>CC</sub>  |

| Minimum power supply for<br>RESET (Note 6) | V <sub>CCL2</sub> | В              | ON             | OFF                   | A              | ON                    | ON             | ON                    | 0 to 2.0 V      | 0 V              | 0 V             | -       | -       | V <sub>O2</sub> , V <sub>CC</sub>  |

#### NOTES:

1. Decrease  $V_{CC}$  from 5.0 V to 4.0 V and note the  $V_{CC}$  value when  $V_{O1}$  (observed on CRT<sub>1</sub>) transitions to an abrupt LOW state. 2. Increase  $V_{CC}$  from 4.0 V to 5.0 V and note the  $V_{CC}$  value when  $V_{O1}$  (observed on CRT<sub>1</sub>) transitions to an abrupt HIGH state. 3. Increase the Clock voltage ( $V_{CLK}$ ) from 0 V to 3.0 V and observe the value of  $V_{CLK}$  when  $I_{CLK}$  transitions to an abrupt increase.

4. Measured with  $V_{OO} = 1.0$  V.

5. Increase V<sub>CC</sub> from 0 V to 2.0 V and note the V<sub>CC</sub> value when V<sub>O1</sub> (observed on CRT<sub>1</sub>) transitions to an abrupt LOW state. The V<sub>O1</sub> value

will initially track the  $V_{CC}$  voltage increase until the internal circuit bias becomes active, at which time the  $V_{O1}$  value will return to a LOW state. 6. Increase  $V_{CC}$  from 0 V to 2.0 V and note the  $V_{CC}$  value when  $V_{O2}$  (observed on CRT<sub>2</sub>) starts to track the  $V_{CC}$  voltage.

### NE56605-42

Figure 24. Test Circuit 2 (AC parameters).

### Table 2. Switch and power supply settings, AC parameters

| Parameter                                          | Symbol            | S <sub>1</sub> | S <sub>2</sub> | V <sub>CCA</sub> | V <sub>CC</sub> | V <sub>CLKA</sub>                                                                                                                                                                                                             | V <sub>CLK</sub> | CRT     |

|----------------------------------------------------|-------------------|----------------|----------------|------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------|

| V <sub>CC</sub> pulse width for detection (Note 1) | t <sub>P1</sub>   | С              | С              | 5.0 V<br>4.0 V   | -               | $\begin{array}{c} 1.4 \text{ V} \\ 0 \text{ V} \end{array} \xrightarrow{\bullet} \begin{array}{c} t_2 \\ \bullet \end{array} \xrightarrow{\bullet} \begin{array}{c} \\ \bullet \end{array} \xrightarrow{\bullet} \end{array}$ | -                | 1, 2, 3 |

| Clock input pulse width (Note 2)                   | t <sub>CLKW</sub> | A              | С              | -                | 5.0 V           |                                                                                                                                                                                                                               | -                | 1, 2, 3 |

| Clock input cycle<br>(Note 3)                      | t <sub>CLK</sub>  | A              | С              | -                | 5.0 V           |                                                                                                                                                                                                                               | -                | 1, 2, 3 |

| Watchdog monitoring time                           | t <sub>WDM</sub>  | A              | A              | -                | 5.0 V           | _                                                                                                                                                                                                                             | 5.0 V            | 1, 2, 3 |

| Watchdog reset time                                | t <sub>WDR</sub>  | A              | А              | -                | 5.0 V           | -                                                                                                                                                                                                                             | 5.0 V            | 1, 2, 3 |

| Power-on reset delay time                          | t <sub>PR</sub>   | B to A         | А              | -                | 5.0 V           | -                                                                                                                                                                                                                             | 5.0 V            | 1, 2, 3 |

| RESET, RESET<br>propagation delay time             | t <sub>PD1</sub>  | С              | В              | 5.0 V<br>4.0 V   | -               | _                                                                                                                                                                                                                             | 0 V              | 1, 2    |

|                                                    | t <sub>PD2</sub>  | С              | В              | 5.0 V<br>4.0 V   | -               | -                                                                                                                                                                                                                             | 0 V              | 2, 3    |

| RESET, RESET rise time                             | t <sub>R1</sub>   | А              | А              | -                | 5.0 V           | -                                                                                                                                                                                                                             | 5.0 V            | 1       |

|                                                    | t <sub>R2</sub>   | А              | А              | -                | 5.0 V           | -                                                                                                                                                                                                                             | 5.0 V            | 3       |

| RESET, RESET fall time                             | t <sub>F1</sub>   | А              | А              | -                | 5.0 V           | -                                                                                                                                                                                                                             | 5.0 V            | 1       |

|                                                    | t <sub>F2</sub>   | A              | А              | -                | 5.0 V           | -                                                                                                                                                                                                                             | 5.0 V            | 3       |

NOTES:

1.  $t_1 = 8.0 \ \mu s.$ 2.  $t_2 = 3.0 \ \mu s.$ 3.  $t_3 = 20 \ \mu s.$

### NE56605-42

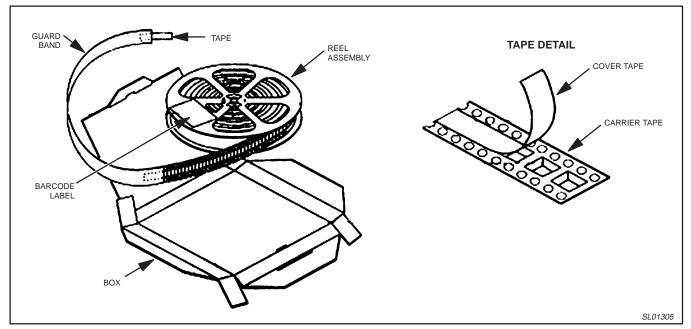

### **PACKING METHOD**

The NE56605-42 is packed in reels, as shown in Figure 25.

Figure 25. Tape and reel packing method

#### Notes

1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

2. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE | REFERENCES |        |      |  |  |  |  |  |  |

|---------|------------|--------|------|--|--|--|--|--|--|

| VERSION | IEC        | JEDEC  | EIAJ |  |  |  |  |  |  |

| SO8     | 076E03     | MS-012 |      |  |  |  |  |  |  |

### NE56605-42

#### Data sheet status

| Data sheet status <sup>[1]</sup> | Product<br>status <sup>[2]</sup> | Definitions                                                                                                                                                                                                                                                                                                            |

|----------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective data                   | Development                      | This data sheet contains data from the objective specification for product development.<br>Philips Semiconductors reserves the right to change the specification in any manner without notice.                                                                                                                         |

| Preliminary data                 | Qualification                    | This data sheet contains data from the preliminary specification. Supplementary data will be published at a later date. Philips Semiconductors reserves the right to change the specification without notice, in order to improve the design and supply the best possible product.                                     |

| Product data                     | Production                       | This data sheet contains data from the product specification. Philips Semiconductors reserves the right to make changes at any time in order to improve the design, manufacturing and supply. Changes will be communicated according to the Customer Product/Process Change Notification (CPCN) procedure SNW-SQ-650A. |

[1] Please consult the most recently issued data sheet before initiating or completing a design.

[2] The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com.

#### Definitions

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

**Application information** — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### **Disclaimers**

Life support — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

**Right to make changes** — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

#### Contact information

For additional information please visit http://www.semiconductors.philips.com. Fax: +3

Fax: +31 40 27 24825

© Koninklijke Philips Electronics N.V. 2001 All rights reserved. Printed in U.S.A.

Date of release: 10-01

For sales offices addresses send e-mail to: sales.addresses@www.semiconductors.philips.com

Document order number:

9397 750 08733

Let's make things better.

HILIPS

Semiconductors

Philips