### **CD1284**

IEEE 1284-Compatible Parallel Interface Controller with Two High-Speed Asynchronous Serial Ports

### **Datasheet**

### **Product Features**

### **Parallel Port (Peripheral-side)**

High-speed, bidirectional, multi-protocol parallel port:

- Hardware implementation of all modes of the IEEE STD (Standard) 1284 specification (including automatic negotiation)

- —Centronics®-compatible mode

- -Reverse Byte mode

- -Reverse Nibble mode

- —ECP (extended capabilities port) mode with run-length encoding/decoding

- -EPP (enhanced parallel port) mode

- —Up to 2-Mbytes/sec. transfer rate in ECP and EPP modes

- 64-byte parallel FIFO with DMA interface

#### **Two Serial UARTs**

- Serial channel asynchronous protocol support to 115.2 kbps (register-setcompatible and functionally identical to CD1400)

- Twelve-byte FIFOs for each transmitter and receiver with programmable threshold for receive FIFO interrupt generation

- —Improved interrupt schemes: Good Data™ interrupts eliminate the need for character status check

- User-programmable and automatic flow control for serial channels

- Special character recognition and generation.

- —Special character processing, particularly useful for UNIX® environments, optionally handled automatically by the serial channels.

- —Six modem control signals per channel (DTR, DSR, RTS, CTS, CD, and RI)

Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The CD1284 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2001

\*Third-party brands and names are the property of their respective owners.

| 2.0       Conventions         2.1       Abbreviations         2.2       Acronyms         3.0       Pin Information         3.1       Pin Diagram         3.2       Pin List         4.0       Register Summary         4.1       Register Summary Tables         4.2       Register Usage         5.0       Functional Description         5.1       Device Architecture         5.2       CPU Interface         5.2.1       Read Cycles         5.2.2       Write Cycles         5.2.3       Service-Acknowledge Cycles         5.2.4       DMA Cycles         5.3.1       Interrupts         5.3.2       DMAREQ* as Parallel Interrupt Source         5.3.3       Serial Service Requests Polling         5.3.4       Daisy-Chaining Service Requests with CD1400s         5.4       Parallel Port Service Requests         5.4.1       Hardware-Activated Context Switch, Parallel         5.5.2       Serial Data Reception and Transmission         5.5.1       Receiver Operation | 15<br>17<br>17<br>18     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 2.2   Acronyms   3.0   Pin Information   3.1   Pin Diagram   3.2   Pin List   4.0   Register Summary   4.1   Register Summary   4.1   Register Usage   4.2   Register Usage   5.0   Functional Description   5.1   Device Architecture   5.2   CPU Interface   5.2.1   Read Cycles   5.2.2   Write Cycles   5.2.3   Service-Acknowledge Cycles   5.2.4   DMA Cycles   5.2.4   DMA Cycles   5.2.4   DMA Cycles   5.3.1   Interrupts   5.3.1   Interrupts   5.3.2   DMAREQ* as Parallel Interrupt Source   5.3.3   Serial Service Request Polling   5.3.4   Daisy-Chaining Service Requests with CD1400s   5.4   Parallel Port Service Requests   5.4.1   Hardware-Activated Context Switch, Parallel   5.4.2   Software-Activated Context Switch, Parallel   5.5   Serial Data Reception and Transmission   5.5.1   Receiver Operation                                                                                                                                                   | 15<br>17<br>18<br>24     |

| 2.2   Acronyms   3.0   Pin Information   3.1   Pin Diagram   3.2   Pin List   4.0   Register Summary   4.1   Register Summary   4.1   Register Usage   4.2   Register Usage   5.0   Functional Description   5.1   Device Architecture   5.2   CPU Interface   5.2.1   Read Cycles   5.2.2   Write Cycles   5.2.3   Service-Acknowledge Cycles   5.2.4   DMA Cycles   5.2.4   DMA Cycles   5.2.4   DMA Cycles   5.3.1   Interrupts   5.3.1   Interrupts   5.3.2   DMAREQ* as Parallel Interrupt Source   5.3.3   Serial Service Request Polling   5.3.4   Daisy-Chaining Service Requests with CD1400s   5.4   Parallel Port Service Requests   5.4.1   Hardware-Activated Context Switch, Parallel   5.4.2   Software-Activated Context Switch, Parallel   5.5   Serial Data Reception and Transmission   5.5.1   Receiver Operation                                                                                                                                                   | 15<br>17<br>18<br>24     |

| 3.0       Pin Information         3.1       Pin Diagram         3.2       Pin List         4.0       Register Summary         4.1       Register Summary Tables         4.2       Register Usage         5.0       Functional Description         5.1       Device Architecture         5.2       CPU Interface         5.2.1       Read Cycles         5.2.2       Write Cycles         5.2.3       Service-Acknowledge Cycles         5.2.4       DMA Cycles         5.3       Serial Port Service Requests         5.3.1       Interrupts         5.3.2       DMAREQ* as Parallel Interrupt Source         5.3.3       Serial Service Request Polling         5.3.4       Daisy-Chaining Service Requests with CD1400s         5.4       Parallel Port Service Requests         5.4.1       Hardware-Activated Context Switch, Parallel         5.4.2       Software-Activated Context Switch, Parallel         5.5.1       Receiver Operation                                       | .17<br>.17<br>.18<br>.24 |

| 3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | .17<br>.18<br>.24        |

| 4.0 Register Summary  4.1 Register Summary Tables.  4.2 Register Usage  5.0 Functional Description.  5.1 Device Architecture.  5.2 CPU Interface  5.2.1 Read Cycles  5.2.2 Write Cycles  5.2.3 Service-Acknowledge Cycles  5.2.4 DMA Cycles  5.3 Serial Port Service Requests  5.3.1 Interrupts  5.3.2 DMAREQ* as Parallel Interrupt Source  5.3.3 Serial Service Request Polling  5.3.4 Daisy-Chaining Service Requests with CD1400s.  5.4 Parallel Port Service Requests  5.4.1 Hardware-Activated Context Switch, Parallel  5.4.2 Software-Activated Context Switch, Parallel  5.5 Serial Data Reception and Transmission  5.5.1 Receiver Operation                                                                                                                                                                                                                                                                                                                                  | .18<br>.24<br>.24        |

| 4.0 Register Summary  4.1 Register Summary Tables  4.2 Register Usage  5.0 Functional Description  5.1 Device Architecture  5.2 CPU Interface  5.2.1 Read Cycles  5.2.2 Write Cycles  5.2.3 Service-Acknowledge Cycles  5.2.4 DMA Cycles  5.3 Serial Port Service Requests  5.3.1 Interrupts  5.3.2 DMAREQ* as Parallel Interrupt Source  5.3.3 Serial Service Request Polling  5.3.4 Daisy-Chaining Service Requests with CD1400s  5.4 Parallel Port Service Requests  5.4.1 Hardware-Activated Context Switch, Parallel  5.4.2 Software-Activated Context Switch, Parallel  5.5 Serial Data Reception and Transmission  5.5.1 Receiver Operation                                                                                                                                                                                                                                                                                                                                      | .24                      |

| 4.1 Register Summary Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .24                      |

| 5.0 Functional Description  5.1 Device Architecture 5.2 CPU Interface 5.2.1 Read Cycles 5.2.2 Write Cycles 5.2.3 Service-Acknowledge Cycles 5.2.4 DMA Cycles 5.3 Serial Port Service Requests 5.3.1 Interrupts 5.3.2 DMAREQ* as Parallel Interrupt Source 5.3.3 Serial Service Request Polling 5.3.4 Daisy-Chaining Service Requests with CD1400s 5.4 Parallel Port Service Requests 5.4.1 Hardware-Activated Context Switch, Parallel 5.4.2 Software-Activated Context Switch, Parallel 5.5 Serial Data Reception and Transmission 5.5.1 Receiver Operation                                                                                                                                                                                                                                                                                                                                                                                                                            |                          |

| 5.0 Functional Description.  5.1 Device Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |

| 5.1 Device Architecture  5.2 CPU Interface  5.2.1 Read Cycles  5.2.2 Write Cycles  5.2.3 Service-Acknowledge Cycles  5.2.4 DMA Cycles  5.3 Serial Port Service Requests  5.3.1 Interrupts  5.3.2 DMAREQ* as Parallel Interrupt Source  5.3.3 Serial Service Request Polling  5.3.4 Daisy-Chaining Service Requests with CD1400s  5.4 Parallel Port Service Requests  5.4.1 Hardware-Activated Context Switch, Parallel  5.4.2 Software-Activated Context Switch, Parallel  5.5 Serial Data Reception and Transmission  5.5.1 Receiver Operation                                                                                                                                                                                                                                                                                                                                                                                                                                         |                          |

| 5.2 CPU Interface 5.2.1 Read Cycles 5.2.2 Write Cycles 5.2.3 Service-Acknowledge Cycles 5.2.4 DMA Cycles 5.3 Serial Port Service Requests 5.3.1 Interrupts 5.3.2 DMAREQ* as Parallel Interrupt Source 5.3.3 Serial Service Request Polling 5.3.4 Daisy-Chaining Service Requests with CD1400s 5.4 Parallel Port Service Requests 5.4.1 Hardware-Activated Context Switch, Parallel 5.4.2 Software-Activated Context Switch, Parallel 5.5 Serial Data Reception and Transmission 5.5.1 Receiver Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |

| 5.2.1 Read Cycles 5.2.2 Write Cycles 5.2.3 Service-Acknowledge Cycles 5.2.4 DMA Cycles 5.3 Serial Port Service Requests 5.3.1 Interrupts 5.3.2 DMAREQ* as Parallel Interrupt Source 5.3.3 Serial Service Request Polling 5.3.4 Daisy-Chaining Service Requests with CD1400s 5.4 Parallel Port Service Requests 5.4.1 Hardware-Activated Context Switch, Parallel 5.4.2 Software-Activated Context Switch, Parallel 5.5 Serial Data Reception and Transmission 5.5.1 Receiver Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                          |

| 5.2.2 Write Cycles 5.2.3 Service-Acknowledge Cycles 5.2.4 DMA Cycles.  5.3 Serial Port Service Requests 5.3.1 Interrupts 5.3.2 DMAREQ* as Parallel Interrupt Source 5.3.3 Serial Service Request Polling 5.3.4 Daisy-Chaining Service Requests with CD1400s  5.4 Parallel Port Service Requests 5.4.1 Hardware-Activated Context Switch, Parallel 5.4.2 Software-Activated Context Switch, Parallel 5.5 Serial Data Reception and Transmission 5.5.1 Receiver Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          |

| 5.2.3 Service-Acknowledge Cycles 5.2.4 DMA Cycles  5.3 Serial Port Service Requests 5.3.1 Interrupts 5.3.2 DMAREQ* as Parallel Interrupt Source. 5.3.3 Serial Service Request Polling 5.3.4 Daisy-Chaining Service Requests with CD1400s 5.4 Parallel Port Service Requests 5.4.1 Hardware-Activated Context Switch, Parallel 5.4.2 Software-Activated Context Switch, Parallel 5.5 Serial Data Reception and Transmission 5.5.1 Receiver Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |

| 5.2.4 DMA Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          |

| 5.3 Serial Port Service Requests 5.3.1 Interrupts 5.3.2 DMAREQ* as Parallel Interrupt Source 5.3.3 Serial Service Request Polling 5.3.4 Daisy-Chaining Service Requests with CD1400s 5.4 Parallel Port Service Requests 5.4.1 Hardware-Activated Context Switch, Parallel 5.4.2 Software-Activated Context Switch, Parallel 5.5 Serial Data Reception and Transmission 5.5.1 Receiver Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                          |

| 5.3.1 Interrupts 5.3.2 DMAREQ* as Parallel Interrupt Source 5.3.3 Serial Service Request Polling 5.3.4 Daisy-Chaining Service Requests with CD1400s 5.4 Parallel Port Service Requests 5.4.1 Hardware-Activated Context Switch, Parallel 5.4.2 Software-Activated Context Switch, Parallel 5.5 Serial Data Reception and Transmission 5.5.1 Receiver Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                          |

| 5.3.2 DMAREQ* as Parallel Interrupt Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                          |

| 5.3.3 Serial Service Request Polling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |

| 5.3.4 Daisy-Chaining Service Requests with CD1400s  5.4 Parallel Port Service Requests  5.4.1 Hardware-Activated Context Switch, Parallel  5.4.2 Software-Activated Context Switch, Parallel  5.5 Serial Data Reception and Transmission  5.5.1 Receiver Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          |

| 5.4 Parallel Port Service Requests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          |

| 5.4.1 Hardware-Activated Context Switch, Parallel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                          |

| 5.5 Serial Data Reception and Transmission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                          |

| 5.5.1 Receiver Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | .49                      |

| · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | .49                      |

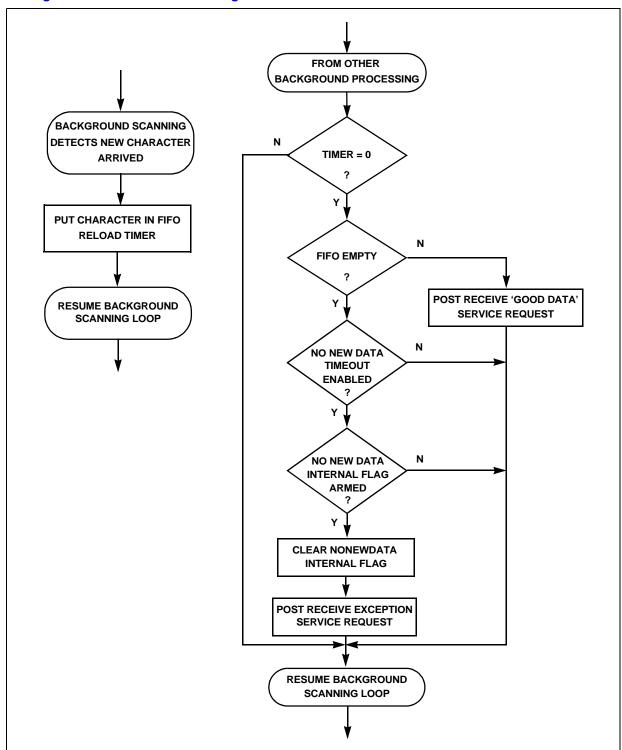

| FFO Develor Time Or all                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | .50                      |

| 5.5.2 Receiver Timer Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                          |

| 5.5.3 Receive Exceptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |

| 5.5.4 Transmitter Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                          |

| 5.6 Flow Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          |

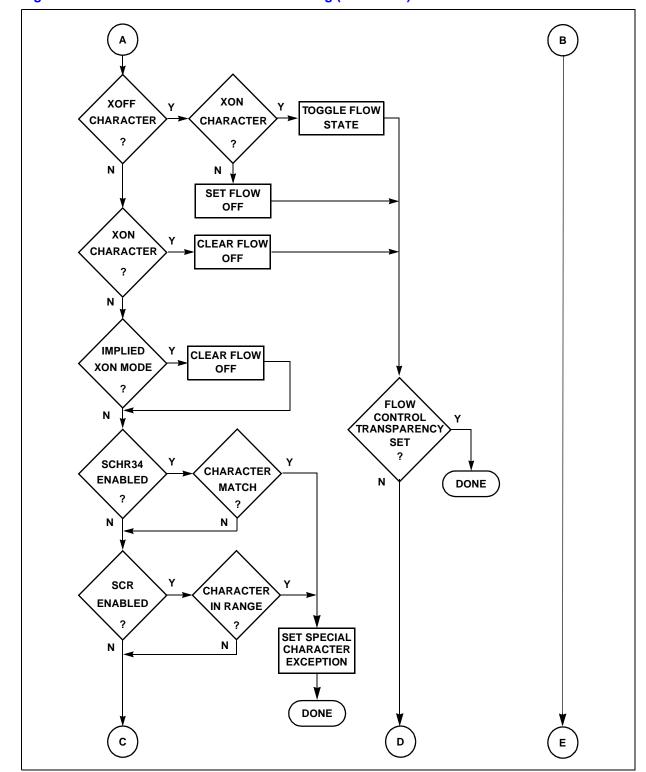

| 5.6.1 In-Band Flow Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                          |

| 5.6.2 Receiver In-Band Flow Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |

| 5.6.3 Out-of-Band Flow Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                          |

| 5.6.4 Modem Signals and General-Purpose I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                          |

| 5.7.1 UNIX, Character Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          |

| 5.7.2 Non-UNIX, Receive Special Character Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |

| 5.7.2 Non-ONIX, Neceive Special Character Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |

| 5.8.1 Line Terminating Characters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                          |

| 5.8.2 Embedded Transmit Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          |

| 5.8.3 Send Special Character Command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |

| 5.9 Baud Rate Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |

3

### CD1284 — IEEE 1284-Compatible Parallel Interface Controller

|     | 5.10 | Serial Diagnostic Facilities — Loopback                       | 73  |

|-----|------|---------------------------------------------------------------|-----|

|     | 5.11 | Parallel Port FIFO and Data Pipeline Overview                 | 73  |

|     |      | 5.11.1 IEEE STD 1284 Protocols                                | 73  |

|     |      | 5.11.2 Bus Interface                                          | 74  |

|     |      | 5.11.3 Parallel Port FIFO                                     | 74  |

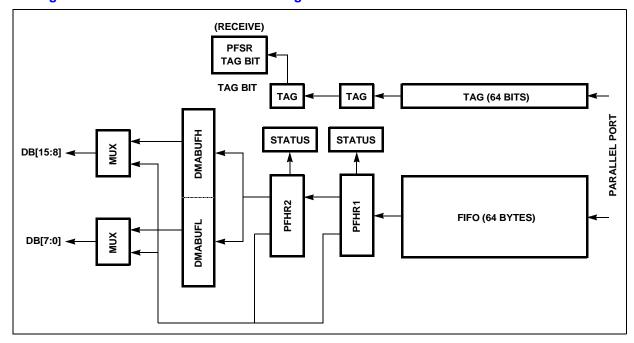

|     |      | 5.11.4 Receive Direction                                      | 75  |

|     |      | 5.11.5 Receiving Compressed Data                              | 75  |

|     |      | 5.11.6 Stale Data (Stale, OneChar, and Timeout Status Bits)   |     |

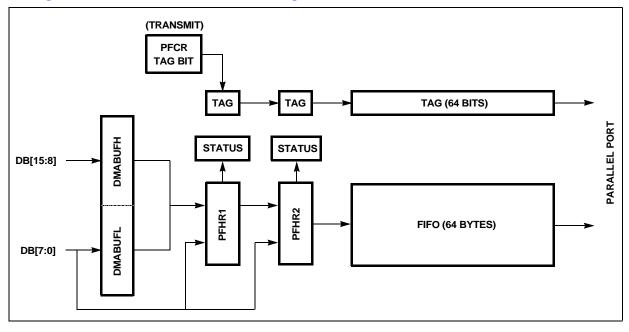

|     |      | 5.11.7 Transmit Direction                                     |     |

|     | 5.12 | CD1284 Parallel Port Overview                                 | 77  |

|     |      | 5.12.1 Terminology                                            | 77  |

|     |      | 5.12.2 Signal Names                                           | 77  |

|     |      | 5.12.3 State Machine                                          | 78  |

|     |      | 5.12.4 Configuration                                          | 78  |

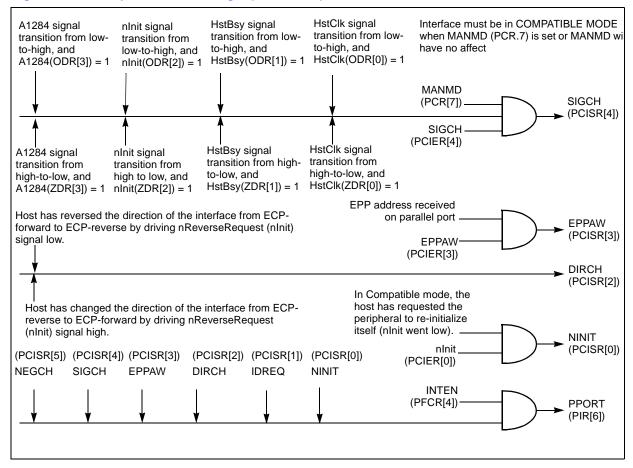

|     |      | 5.12.5 Interrupts                                             | 79  |

|     |      | 5.12.6 Manual Mode                                            | 79  |

|     |      | 5.12.7 Control Signals                                        | 79  |

|     |      | 5.12.8 Parallel Port Interface to the FIFO                    |     |

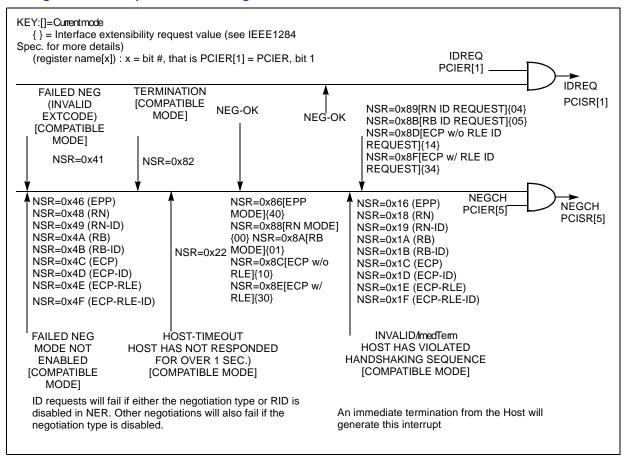

|     |      | 5.12.9 1284 Negotiations                                      |     |

|     |      | 5.12.10 Data Transfers                                        |     |

|     |      | 5.12.11 Compatible Mode Status                                |     |

|     | 5.13 | 1284 Parallel Protocol Support                                |     |

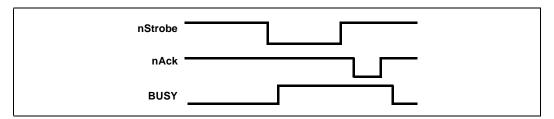

|     |      | 5.13.1 Compatibility Mode                                     |     |

|     |      | 5.13.2 Reverse-Nibble and Reverse-Byte Modes                  |     |

|     |      | 5.13.3 ID Request                                             |     |

|     |      | 5.13.4 ECP Mode                                               | 82  |

|     |      | 5.13.5 EPP Mode                                               | 83  |

|     | 5.14 | Protocol Timing                                               | 83  |

|     | 5.15 | General-Purpose I/O Port                                      |     |

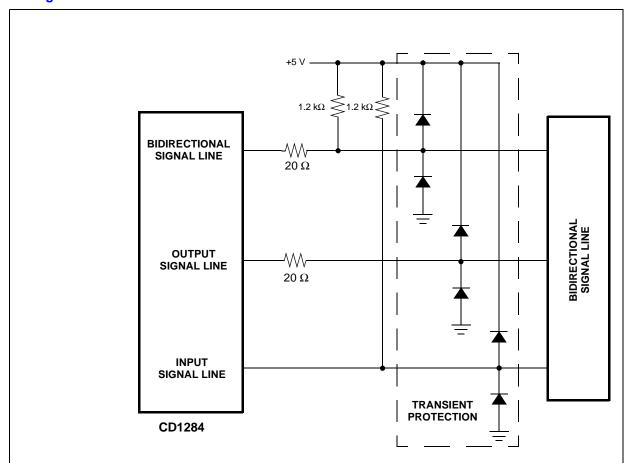

|     | 5.16 | Parallel Port Interface                                       |     |

|     | 5.17 | Hardware Configurations                                       | 86  |

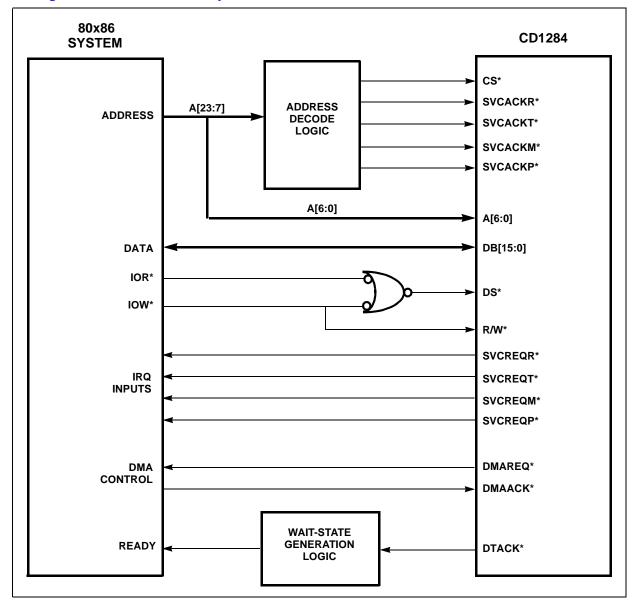

|     |      | 5.17.1 Interfacing to an Intel, Microprocessor-Based System   | 86  |

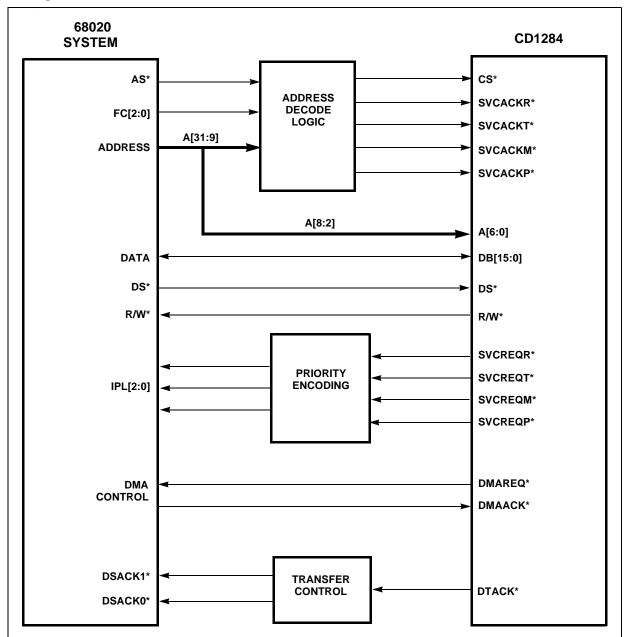

|     |      | 5.17.2 Interfacing to a Motorola, Microprocessor-Based System |     |

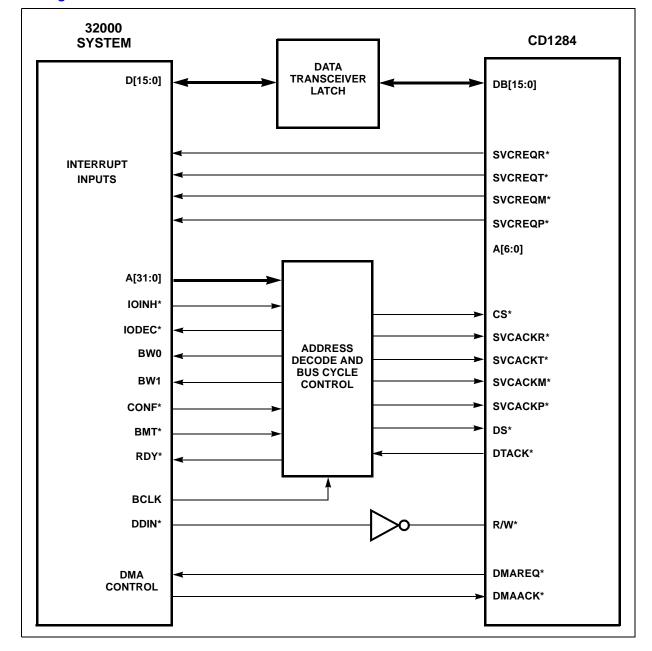

|     |      | 5.17.3 Interfacing to a National Semiconductor,               |     |

|     |      | Microprocessor-Based System86                                 |     |

| 6.0 | Prog | gramming                                                      | 90  |

|     | 6.1  | Overview                                                      |     |

|     | 6.2  | Initialization                                                |     |

|     | 0.2  | 6.2.1 Device Reset                                            |     |

|     |      | 6.2.2 Global Function Initialization                          |     |

|     |      | 6.2.3 Serial Channel Initialization                           |     |

|     | 6.3  | Serial Poll Mode Examples                                     |     |

|     | 0.5  | 6.3.1 Polling Routine Examples                                |     |

|     | 6.4  | Hardware-Activated Service Examples                           |     |

|     | 0.4  | 6.4.1 Serial Receive Service                                  |     |

|     |      | 6.4.2 Serial Transmit Service                                 |     |

|     |      | 6.4.3 Modem Service                                           |     |

|     | 6.5  | Parallel Channel Service Routines                             |     |

|     | 0.5  | 6.5.1 Software-Activated Service Examples (Poll)              |     |

|     |      | 0.0.1 Johnware-Molivated Dervice Examples (Full)              | 100 |

|     |      | 6.5.2          | Hardware-Activated Service Examples                             | 102 |

|-----|------|----------------|-----------------------------------------------------------------|-----|

|     | 6.6  | Baud           | Rate Derivation                                                 | 102 |

|     | 6.7  | Baud           | Rate Tables                                                     | 103 |

|     | 6.8  | ASCII          | Code Tables                                                     |     |

|     |      | 6.8.1          | Hexadecimal — Character                                         |     |

|     |      | 6.8.2          | Decimal — Character                                             | 107 |

| 7.0 | Deta | ailed Re       | gister Descriptions                                             | 108 |

|     | 7.1  | Globa          | l Registers                                                     |     |

|     |      | 7.1.1          | Channel Access Register                                         |     |

|     |      | 7.1.2          | Global Firmware Revision Code Register                          |     |

|     |      | 7.1.3          | General-Purpose I/O Direction Register                          |     |

|     |      | 7.1.4          | General-Purpose I/O Register                                    | 109 |

|     |      | 7.1.5          | Modem Interrupting Channel Register                             | 109 |

|     |      | 7.1.6          | Modem Interrupt Register                                        | 110 |

|     |      | 7.1.7          | Parallel Interrupt Register                                     |     |

|     |      | 7.1.8          | Prescaler Period Register                                       |     |

|     |      | 7.1.9          | Receive Interrupting Channel Register                           |     |

|     |      | 7.1.10         | 3                                                               |     |

|     |      | 7.1.11         |                                                                 |     |

|     |      | 7.1.12         |                                                                 |     |

|     |      | 7.1.13         | , G                                                             |     |

|     | 7.2  |                | l Registers                                                     |     |

|     |      | 7.2.1          | Modem Interrupt Status Register                                 |     |

|     |      | 7.2.2          | Modem Interrupt Vector Register                                 |     |

|     |      | 7.2.3          | Parallel Interrupt Vector Register                              |     |

|     |      | 7.2.4          | Receive Data/Status Registers                                   |     |

|     |      | 7.2.5          | Receive Interrupt Vector Register                               |     |

|     |      | 7.2.6          | Transmit Data Register                                          |     |

|     |      | 7.2.7          | Transmit Interrupt Vector Register                              |     |

|     | 7.0  | 7.2.8          | End of Service Request Register                                 |     |

|     | 7.3  |                | nel Registers                                                   |     |

|     |      | 7.3.1<br>7.3.2 | Channel Command Register                                        |     |

|     | 7.4  |                | Channel Control Status Registerel Registers — Parallel Pipeline |     |

|     | 7.4  | 7.4.1          | ·                                                               |     |

|     |      | 7.4.1          | Channel Option Register 1Channel Option Register 2              |     |

|     |      | 7.4.2          | Channel Option Register 3                                       |     |

|     |      | 7.4.3          | Channel Option Register 4                                       |     |

|     |      | 7.4.4<br>7.4.5 | Channel Option Register 5                                       |     |

|     |      | 7.4.6          | Local Interrupt Vector Register                                 |     |

|     |      | 7.4.7          | LNext Character Register                                        |     |

|     | 7.5  |                | m Change Option Registers                                       |     |

|     | 7.5  | 7.5.1          | Modem Change Option Register 1                                  |     |

|     |      | 7.5.2          | Modern Change Option Register 2                                 |     |

|     |      | 7.5.2          | Modern Signal Value Register 1                                  |     |

|     |      | 7.5.4          | Modern Signal Value Register 2                                  |     |

|     |      | 7.5.5          | Receive Baud Rate Period Register                               |     |

|     |      | 7.5.6          | Receive Clock Option Register                                   |     |

|     |      | 7.5.7          | Received Data Count Register                                    |     |

|     |      |                |                                                                 |     |

### CD1284 — IEEE 1284-Compatible Parallel Interface Controller

|     | 7.5.8   | Receive Timeout Period Register                         | 133 |

|-----|---------|---------------------------------------------------------|-----|

| 7.6 | Special | l Character Registers                                   | 133 |

|     | 7.6.1   | Special Character Register 1                            | 133 |

|     | 7.6.2   | Special Character Register 2                            | 133 |

|     | 7.6.3   | Special Character Register 3                            | 134 |

|     | 7.6.4   | Special Character Register 4                            |     |

|     | 7.6.5   | Received Character Range Detection                      |     |

|     | 7.6.6   | Special Character Range — High                          |     |

|     | 7.6.7   | Special Character Range — Low                           |     |

|     | 7.6.8   | Serial Service Request Enable Register                  |     |

|     | 7.6.9   | Transmit Baud Rate Period Register                      |     |

|     | 7.6.10  | Transmit Clock Option Register                          |     |

| 7.7 |         | el Registers — Parallel Pipeline                        |     |

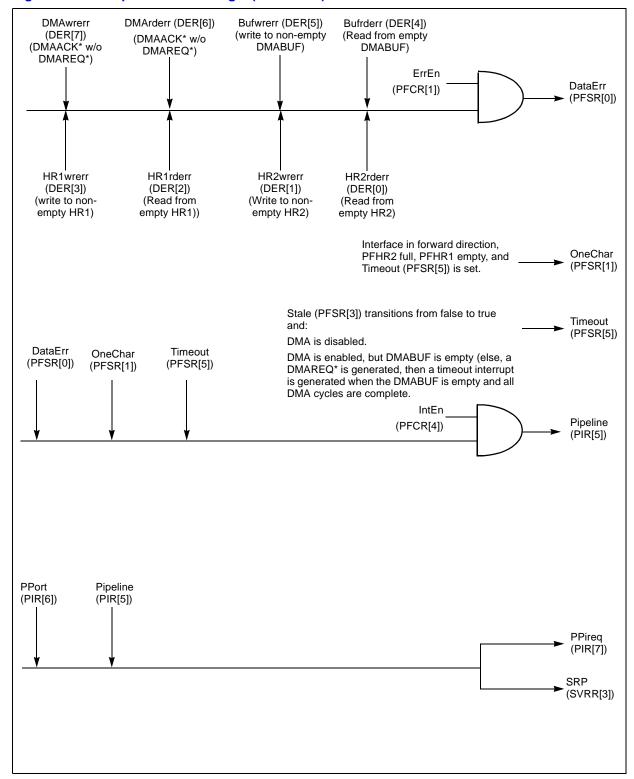

|     | 7.7.1   | Data Error Register                                     |     |

|     | 7.7.2   | DMA Buffer Data Register — High                         |     |

|     | 7.7.3   | DMA Buffer Data Register — Low                          |     |

|     | 7.7.4   | Firmware Revision Code Holding Register Status Register |     |

|     | 7.7.5   | Local Interrupt Vector Register                         |     |

|     | 7.7.6   | Parallel Auxiliary Control Register                     |     |

|     | 7.7.7   | Parallel Channel Reset Register                         |     |

|     | 7.7.8   | Parallel FIFO Control Register                          |     |

|     | 7.7.9   | Parallel FIFO Empty Pointer Register                    |     |

|     | 7.7.10  | Parallel FIFO Fill Pointer Register                     |     |

|     | 7.7.11  | Parallel FIFO Holding Register 1                        |     |

|     | 7.7.12  | Parallel FIFO Holding Register 2                        |     |

|     | 7.7.13  | Parallel FIFO Quantity Register                         | 143 |

|     | 7.7.14  | Parallel FIFO Status Register                           | 143 |

|     | 7.7.15  | Parallel FIFO Threshold Register                        | 144 |

|     | 7.7.16  | Run Length Count Register                               | 144 |

|     | 7.7.17  | Stale Data Timer Count Register                         | 145 |

|     | 7.7.18  | Stale Data Timer Period Register                        | 145 |

| 7.8 | Channe  | el Registers — Parallel Port                            | 146 |

|     | 7.8.1   | EPP Address Register                                    | 146 |

|     | 7.8.2   | Host Timeout Value Register                             | 146 |

|     | 7.8.3   | Input Value Register                                    |     |

|     | 7.8.4   | Manual Data Register                                    | 148 |

|     | 7.8.5   | Negotiation Enable Register                             | 148 |

|     | 7.8.6   | Negotiation Status Register                             | 148 |

|     | 7.8.7   | Ones Detect Register                                    | 149 |

|     | 7.8.8   | Output Value Register                                   | 150 |

|     | 7.8.9   | Parallel Channel Interrupt Enable Register              | 150 |

|     | 7.8.10  | Parallel Channel Interrupt Status Register              | 150 |

|     | 7.8.11  | Parallel Configuration Register                         |     |

|     | 7.8.12  | Special Command Register                                |     |

|     | 7.8.13  | Short Pulse Register                                    | 153 |

| 7.9 | Pin Cor | ntrol Registers                                         | 154 |

|     | 7.9.1   | Signal Status Register                                  | 154 |

|     | 7.9.2   | Zeros Detect Register                                   | 154 |

### IEEE 1284-Compatible Parallel Interface Controller — CD1284

| 8.0   | Electrical Specifications     | 155               |

|-------|-------------------------------|-------------------|

|       | 8.1 Absolute Maximum Ratings  | 155<br>157<br>157 |

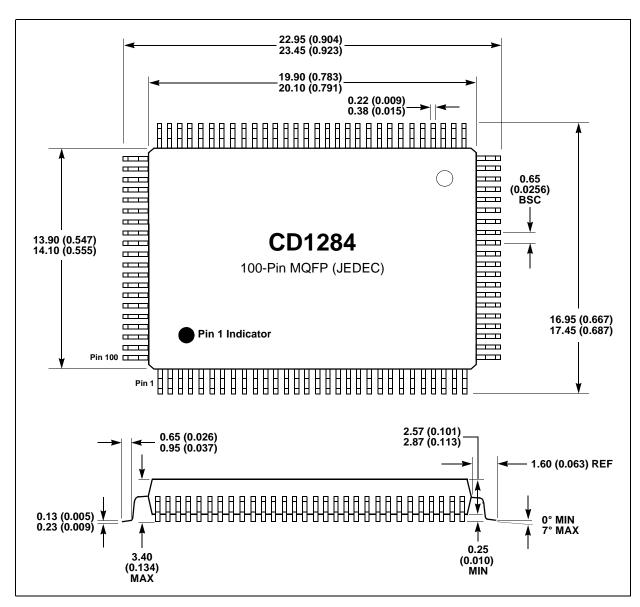

| 9.0   | Package Dimensions            | 169               |

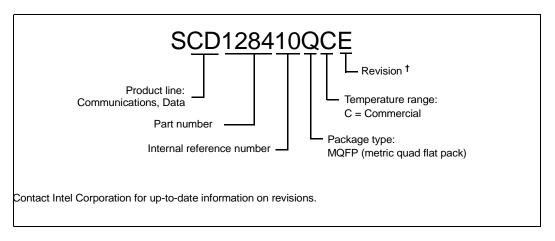

| 10.0  | Ordering Information          | 170               |

| 11.0  | Appendix A                    | 171               |

|       | 11.1 Commonly Asked Questions | 171               |

| 12.0  | Appendix B                    | 172               |

| Index |                               | 173               |

### CD1284 — IEEE 1284-Compatible Parallel Interface Controller

## **Figures**

| 1  | Functional Block Diagram                                          | 11  |

|----|-------------------------------------------------------------------|-----|

| 2  | CD1284 Sample System Block Diagram                                | 14  |

| 3  | CD1284 Functional Block Diagram                                   | 32  |

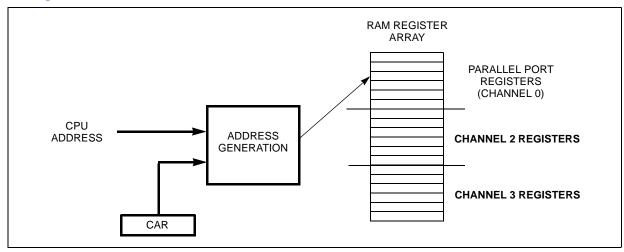

| 4  | Internal Address Generation                                       |     |

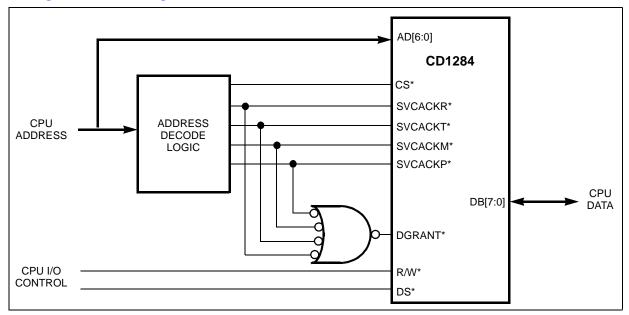

| 5  | Control Signal Generation                                         | 38  |

| 6  | CD1284 Daisy-Chain Connections                                    | 42  |

| 7  | Interrupt Generation Logic                                        | 45  |

| 8  | FIFO Timer Processing                                             |     |

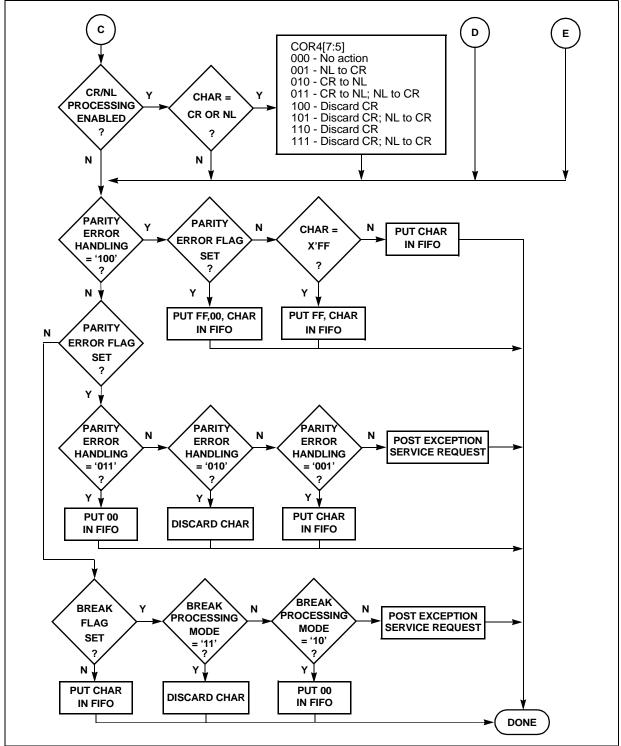

| 9  | CD1284 Receive Character Processing                               |     |

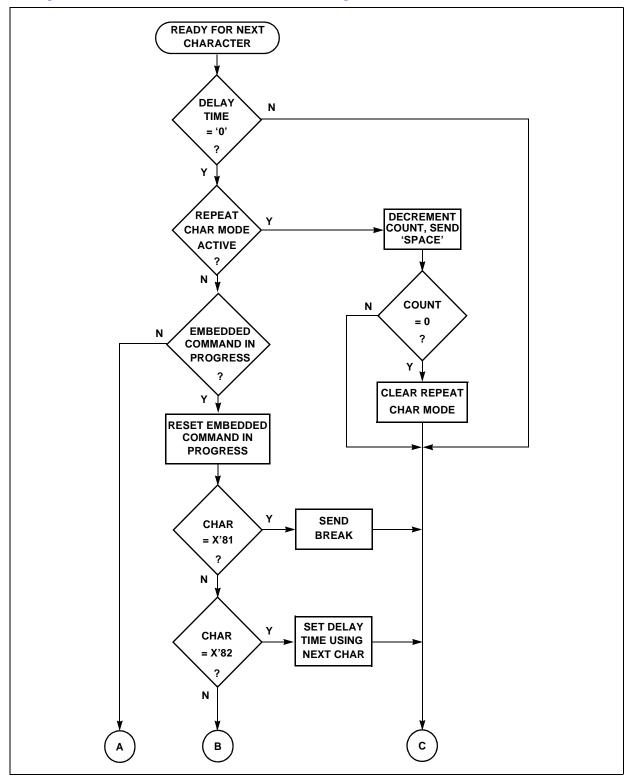

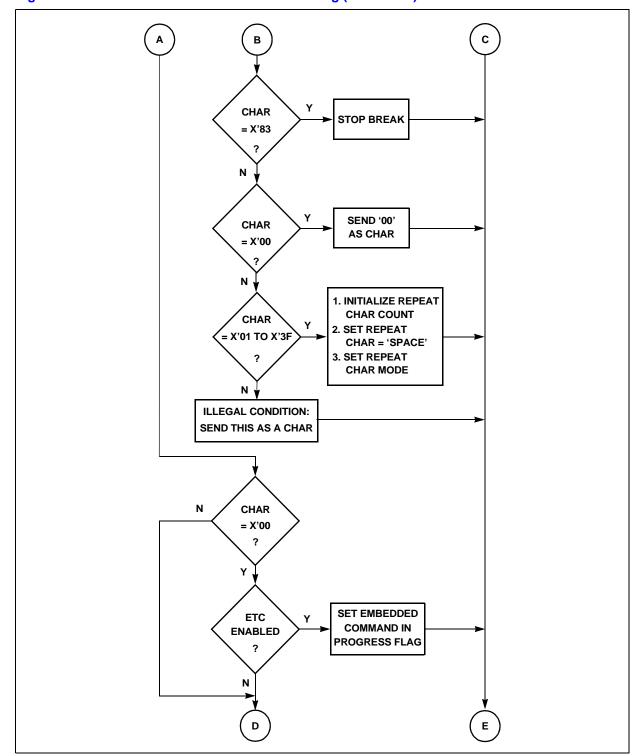

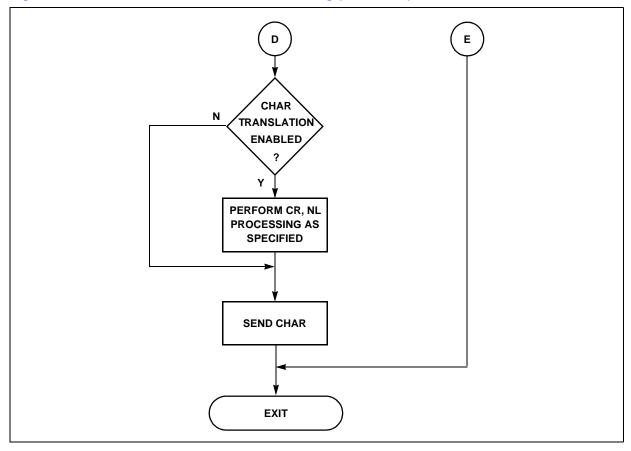

| 10 | CD1284 Transmit Character Processing                              | 70  |

| 11 | FIFO Data Path Functional Diagram — Receive                       | 78  |

| 12 | FIFO Data Path Functional Diagram — Transmit                      | 80  |

| 13 | Cable Connection                                                  | 85  |

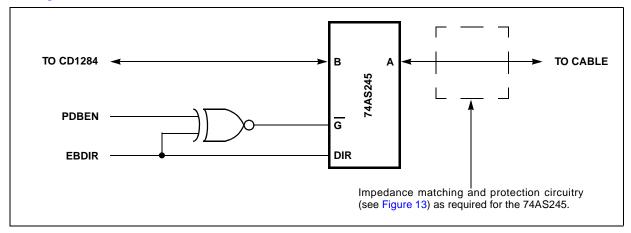

| 14 | External Buffer Control                                           | 86  |

| 15 | Intel, 80x86 Family Interface                                     | 87  |

| 16 | Motorola, 68020 Interface                                         | 8   |

| 17 | National Semiconductor, 32000 Interface                           | 89  |

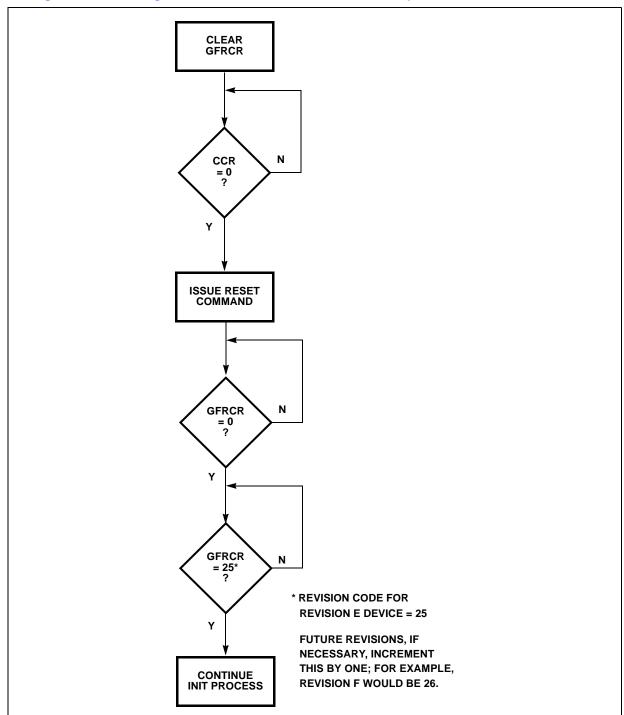

| 18 | Flow Diagram of CD1284 Master Initialization Sequence             | 92  |

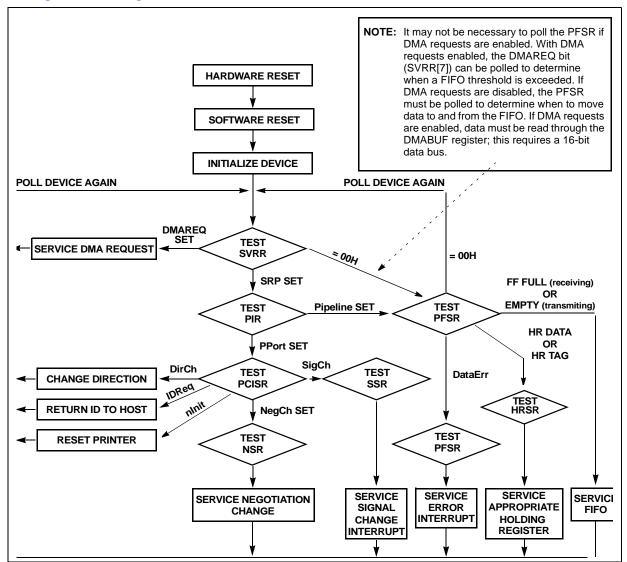

| 19 | Polling Flow Chart                                                | 100 |

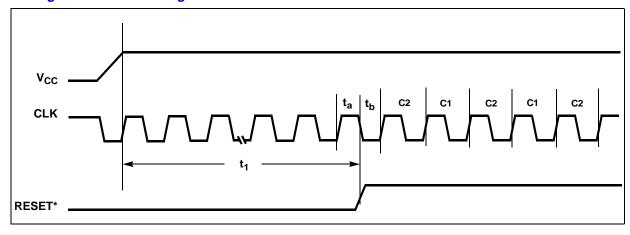

| 20 | Reset Timing                                                      | 158 |

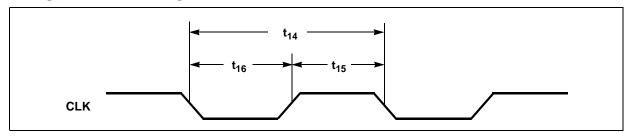

| 21 | Clock Timing                                                      | 159 |

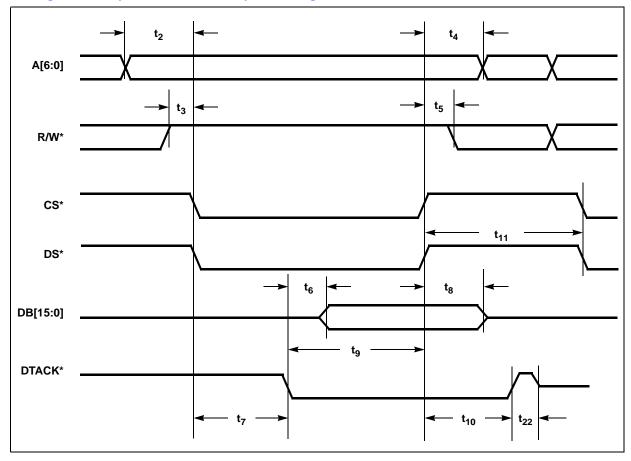

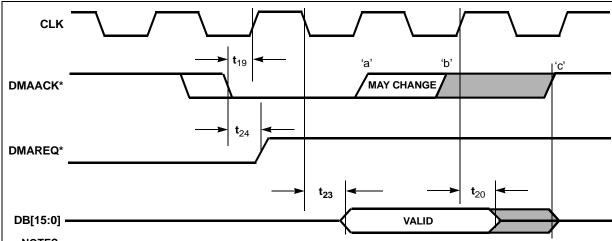

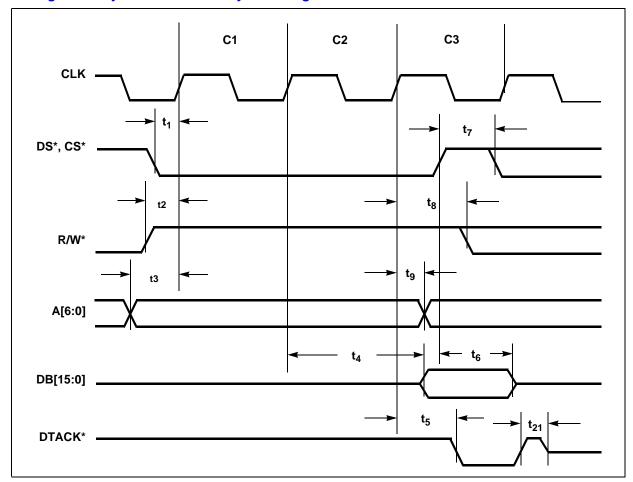

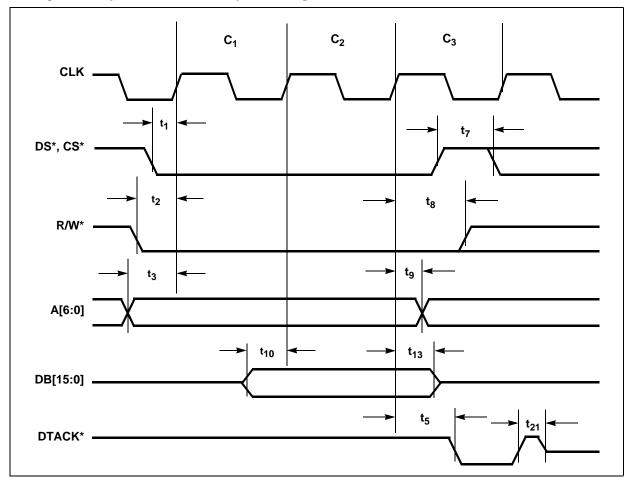

| 22 | Asynchronous Read Cycle Timing                                    | 159 |

| 23 | Asynchronous Write Cycle Timing                                   | 160 |

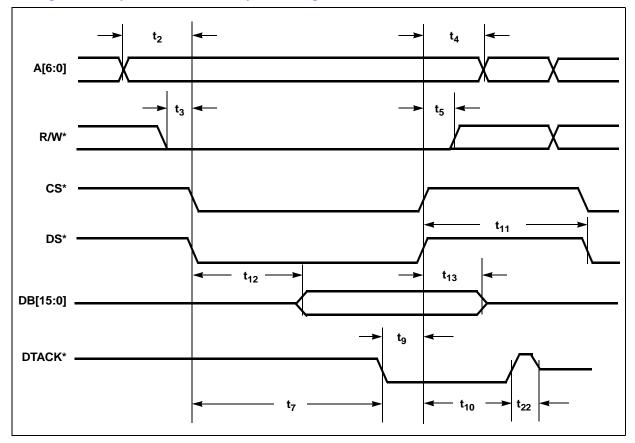

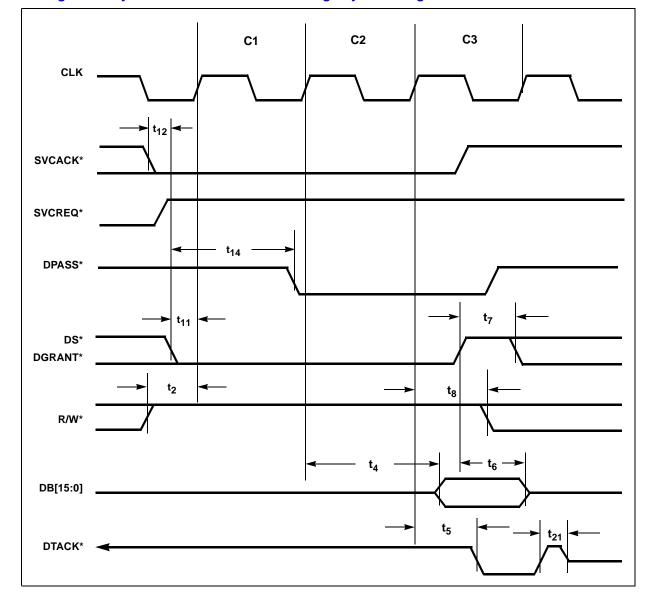

| 24 | Asynchronous Service Acknowledge Cycle Timing                     | 161 |

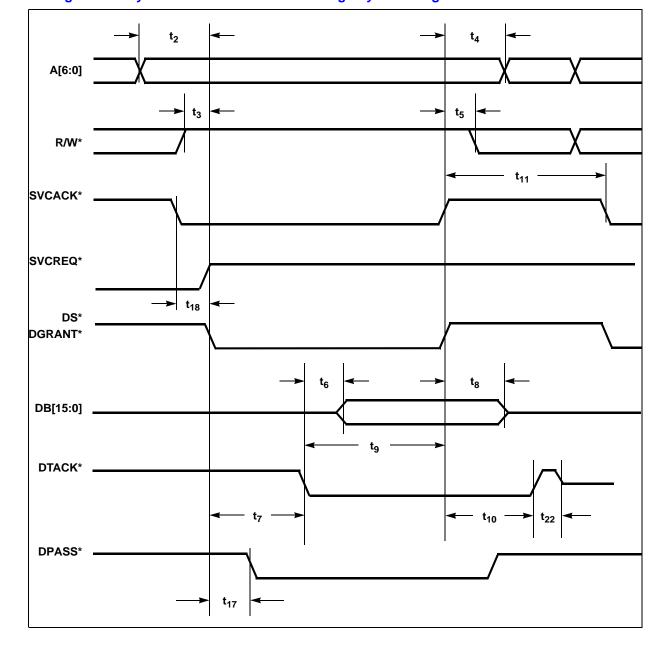

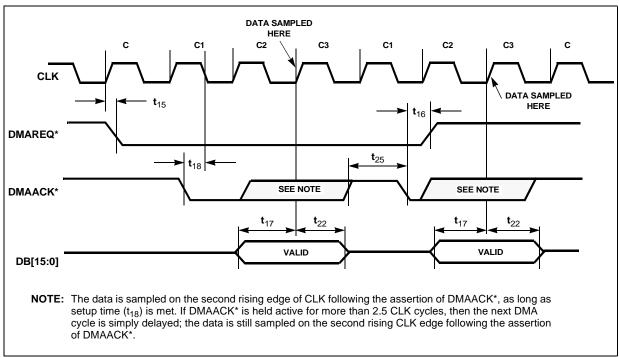

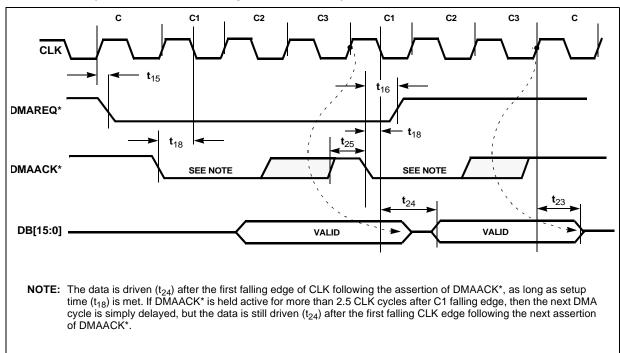

| 25 | Asynchronous DMA Read Cycle Timing                                |     |

| 26 | Asynchronous DMA Read Cycle Timing (Two Back-to-Back DMA Reads)   | 162 |

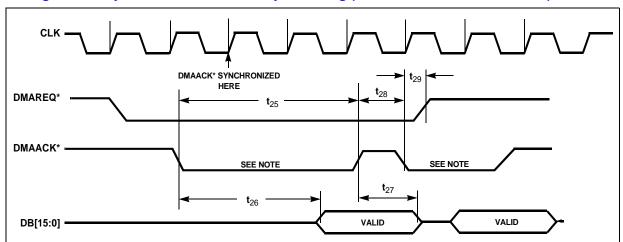

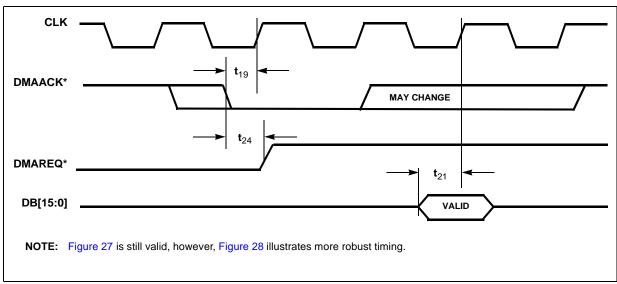

| 27 | Asynchronous DMA Write Cycle Timing                               |     |

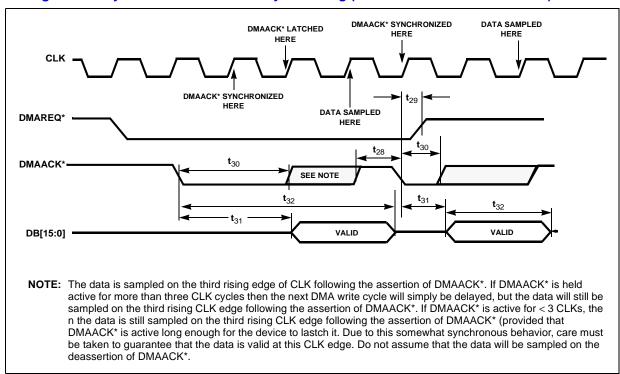

| 28 | Asynchronous DMA Write Cycle Timing (Two Back-to-Back DMA Writes) | 163 |

| 29 | Synchronous Read Cycle Timing                                     | 165 |

| 30 | Synchronous Write Cycle Timing                                    | 166 |

| 31 | Synchronous Service Acknowledge Cycle Timing                      | 167 |

| 32 | Synchronous DMA Write Cycle Timing                                |     |

|    | (Two Back-to-Back 3-Cycle DMA Writes)                             | 168 |

| 33 | Synchronous DMA Read Cycle Timing                                 |     |

|    | (Two Back-to-Back 3-Cycle DMA Reads)                              |     |

| 34 | UART to RS232 and IR Port Interface Motherboard Example Schematic | 172 |

### IEEE 1284-Compatible Parallel Interface Controller — CD1284

## Tables

| 1  | Pin Descriptions                         | 20  |

|----|------------------------------------------|-----|

| 2  | Global Registers                         |     |

| 3  | Virtual Registers — Serial               | 24  |

| 4  | Virtual Registers — Serial and Parallel  | 24  |

| 5  | Channel Registers — Serial               | 25  |

| 6  | Channel Registers — Parallel Pipeline    |     |

|    | (Selected by Channel 0 in CAR)           | 26  |

| 7  | Channel Registers — Parallel Port        |     |

|    | (Selected by Channel 0 in CAR)           |     |

| 8  | Global Registers                         |     |

| 9  | Virtual Registers                        |     |

| 10 | Virtual Registers — Serial and Parallel  |     |

| 11 | Channel Registers — Serial               | 28  |

| 12 | Channel Registers — Parallel Pipeline    |     |

|    | (Selected by Channel 0 in CAR)           | 29  |

| 13 | Channel Registers — Parallel Port        |     |

|    | (Selected by Channel 0 in CAR)           |     |

| 14 | Request-Type Bit Assignments             |     |

| 15 | CCSR[6:5] Encoding                       |     |

| 16 | CCSR[2:1] Encoding                       |     |

| 17 | COR Control Bits                         |     |

| 18 | Out-of-Band Pin Connections              |     |

| 19 | Modem Control Pin Functions              |     |

| 20 | Signal Names                             |     |

| 21 | System Clock Settings                    |     |

| 22 | Baud Rate Constants — CLK = 25 MHz       |     |

| 23 | Baud Rate Constants — CLK = 20.2752 MHz  |     |

| 24 | Baud Rate Constants — CLK = 20.00 MHz    |     |

| 25 | Baud Rate Constants — CLK = 18.432 MHz   |     |

| 26 | Baud Rate Constants — CLK = 16 MHz       |     |

| 27 | Asynchronous Timing Reference Parameters |     |

| 28 | Synchronous Timing Reference Parameters  | 164 |

# **Revision History**

| Revision | Date     | Description      |

|----------|----------|------------------|

| 1.0      | May 2001 | Initial release. |

SERIAL PORT #1

**SERIAL**

PORT #2

GENERAL-PURPOSE I/ O PORT Compression/ Control Level-2 Decompression DMA State Electrical 64 Bytes CONTROL DATA Mover LOCAL CPU INTERFACE Machine Interface DATA PIPELINE **FIFO** IEEE1284 PERIPHERAL PARALLEL PORT

REGISTERS AND FIFO

RAM

**MODIFIED CD1400 CORE**

Figure 1. Functional Block Diagram

MPU

### 1.0 Overview

Ideal for printers, scanners, tape drives, set-top boxes, and data acquisition applications, the CD1284 is a multi-function interface controller that implements a high-speed, multi-protocol parallel port and two asynchronous serial ports. The device has both programmed I/O and DMA operation (parallel port only), providing flexibility in local CPU interface design and high-speed data transfers between the device and main memory.

The parallel port implements all modes of the *IEEE STD 1284 Standard Signaling Method for Bidirectional Parallel Peripheral Interface for Personal Computers* specification, including EPP, ECP, Reverse Byte, Reverse Nibble, and Compatible. Data transfer rates (up to 2 Mbytes/sec.) are achievable on the parallel port when the device operates with a 25-MHz clock. The parallel port data and control signals implement the IEEE STD 1284-defined Level-2 interface in drive type (symmetrical), current capability (±14 mA), slew rate (0.4 V/ns), and 0.8 V hysteresis ( 2.0 V to +7.0 V protection is not implemented).

The two serial ports implement the standard asynchronous protocol. Functionally, the serial ports are identical and register-set-compatible with the CD1400. The table below, shows the differences between the CD1283 and CD1284.

| Device | Number of<br>Serial Channels | Number of<br>Parallel Channels |

|--------|------------------------------|--------------------------------|

| CD1283 | 0                            | 1                              |

| CD1284 | 2                            | 1                              |

Also included is a general-purpose port that provides eight bits of individual direction programmable I/O that can be used for status and control of external functions.

#### **Theory of Operation**

The CD1284 is an efficient high-performance communications controller using an on-chip RISC processor, which off-loads much of the work of sending and receiving data from the CPU. Specifically for data communications applications, the RISC processor employs a high-performance architecture developed by Intel. This internal CPU executes all instructions in one clock cycle, and uses a windowed architecture to ensure zero-overhead context switching for each type of internal interrupt. The processor is transparent to the user and does not require any programming. It manages all serial data movement between the CPU and the two serial channels and provides a flexible interrupt interface for the parallel channel. The parallel channel, being separate and having its own intelligence, implements a very high-speed, peripheral-side parallel data interface.

Each of the serial channels consist of separate 12- byte receive and transmit FIFOs. The parallel channel has a single 64-byte FIFO to support the higher speeds obtainable on the parallel data port. The serial receive FIFOs all have programmable thresholds to minimize interrupt latency requirements. The parallel port FIFO has a programmable DMA threshold in both the receive and transmit directions. The deep FIFOs reduce both the number of interrupt requests made of the CPU and the time required to service them. The time required to service the requests is reduced by four unique vectors that provide internal interrupt conditions. Whether it is receive, transmit, modem signal change, or parallel port, the system spends less time determining the source of the interrupt. The serial receive interrupt service time is further reduced by providing two types of receive vectors: one for 'good' data and the other for 'exception' data. The CPU does not spend

#### IEEE 1284-Compatible Parallel Interface Controller — CD1284

time determining the status of every character. When the receive vector signifies good data, the CPU removes the data from the FIFO. Checking status is not necessary. Exception data (framing error, overrun, break, etc.) causes an interrupt with a vector that the CPU can immediately identify and manage.

The RISC processor is assisted in the process of sending and receiving serial data by specialized hardware called 'bit engines'. These logic blocks perform the actual task of sending and receiving the individual bits of a character, thus removing the task of timing the bit duration from the on-chip processor. The processor assembles the bits into characters and tests various parameters (for example, parity, framing, etc.) then places the characters in the FIFO. Since it is managing every character, special character processing is possible such as looking for and responding to flow-control characters (XON/XOFF) and performing UNIX®-style character substitutions and range checking. This reduces interrupt overhead by automatically performing many of the operations that the CPU normally does. Flow-control, for example, can be performed without CPU involvement. Those operations can be completely removed from its responsibility.

The CD1284 can be daisy-chained with other CD1284 or CD1400 devices to implement larger and more complex systems. The Fair Share feature assures equal access for service requests across multiple devices (Fair Share is not implemented on a parallel port interrupt request).

The parallel channel within the CD1284 implements all protocols defined for the peripheral side by the IEEE STD 1284. This specification defines four bidirectional protocols that allow a peripheral device to communicate with a host system (IBM® PC or equivalent) through the parallel printer channel. The modes include Reverse Nibble, Reverse Byte (IBM® PS/2® style), ECP, and EPP (as implemented on the Intel® 80386SL processor). ECP and EPP both operate at data rates as high as 2 Mbytes/sec.

The IEEE 1284 port is implemented as two functional blocks: a data pipeline, which includes the 64-byte FIFO and the DMA interface, and a high-speed state-machine, which controls the parallel port and implements the slave-side IEEE 1284 protocols. The internal RISC processor assists the parallel channel by providing interrupt generation, acknowledgment functions, and a data interface to the Parallel Port registers.

As defined in the IEEE 1284 specification, the CD1284 in ECP mode, provides RLE (run length encoded) data compression in both directions. This data compression is performed automatically (if enabled) and is capable of compressing long strings (up to 128 bytes) of identical data into a two-byte sequence (command/count and data). Since it is common for bit patterns to have large amounts of identical data, the CD1284 greatly reduces data transmission times in printer applications.

EPP mode defines a means of sending address and data over the parallel channel much like a processor address and data interface. This has found widespread use in LAN and SCSI interface adapters that provide these services on laptop computers.

The following figure shows a possible configuration for a CD1284 in a laser-printer application. In this example, the CD1284 provides a parallel and serial data interface to a host system or server. It also provides a serial channel for control communication with the printer console, as well as general-purpose I/O for static control/status.

**HIGH-SPEED**

➤ SERIAL CHANNEL #1 (RS-232, INFRARED)

CONTROL PROCESSOR

GP I/O:

CD1284

RAM

ADDRESS BUS

DATA BUS

IEEE 1284

PARALLEL CHANNEL

HIGH-SPEED SERIAL CHANNEL #2

LASER PRINTER CONSOLE

Figure 2. CD1284 Sample System Block Diagram

**INTERNAL STATUS**

AND CONTROL

### 2.0 Conventions

### 2.1 Abbreviations

| Symbol | Units of Measure                 |

|--------|----------------------------------|

| °C     | degree Celsius                   |

| Hz     | hertz (cycles per second)        |

| Kbyte  | kilobyte (1,024 bytes)           |

| kHz    | kilohertz                        |

| kΩ     | kilohm                           |

| Mbyte  | megabyte (1,048,576 bytes)       |

| MHz    | megahertz (1,000 kilohertz)      |

| μF     | microfarad                       |

| μs     | microsecond (1,000 nanoseconds)  |

| mA     | milliampere                      |

| ms     | millisecond (1,000 microseconds) |

| ns     | nanosecond                       |

| pV     | picovolt                         |

The use of 'tbd' indicates values that are 'to be determined', 'n/a' designates 'not available', and 'N/C' indicates a pin that is a 'no connect'.

### 2.2 Acronyms

| Acronym | Definition                              |

|---------|-----------------------------------------|

|         | (Sheet 1 of 2)                          |

| AC      | alternating current                     |

| BIOS    | basic input/output system               |

| CISC    | complex instruction set computer        |

| CMOS    | complementary metal-oxide semiconductor |

| DC      | direct current                          |

| DMA     | direct-memory access                    |

| DRAM    | dynamic random-access memory            |

| ECP     | extended capibilities port              |

| EPP     | enhanced parallel port                  |

| FIFO    | first in/first out                      |

| GPIO    | general-purpose IO                      |

### CD1284 — IEEE 1284-Compatible Parallel Interface Controller

| Acronym        | Definition                                               |  |  |

|----------------|----------------------------------------------------------|--|--|

| (Sheet 2 of 2) |                                                          |  |  |

| HCMOS          | high-performance complementary metal-oxide semiconductor |  |  |

| HDLC           | high-level data link control                             |  |  |

| IC             | integrated circuit                                       |  |  |

| IDC            | instruction and data cache                               |  |  |

| ISA            | industry standard architecture                           |  |  |

| LSB            | least-significant bit                                    |  |  |

| MPU            | microprocessing unit                                     |  |  |

| MSB            | most-significant bit                                     |  |  |

| PIO            | programmed I/O                                           |  |  |

| PPP            | point-to-point protocol                                  |  |  |

| MQFP           | metric quad flat pack                                    |  |  |

| RAM            | random-access memory                                     |  |  |

| RLE            | run-length encoded                                       |  |  |

| R/W            | read/write                                               |  |  |

| SDLC           | synchronous data link control                            |  |  |

| SRAM           | static random-access memory                              |  |  |

| SWI            | software interrupt instruction                           |  |  |

| TLB            | translation look-aside buffer                            |  |  |

| TTB            | translation table base                                   |  |  |

| TTL            | transitor-transitor logic                                |  |  |

| VRAM           | video random-access memory                               |  |  |

| WB             | write buffer                                             |  |  |

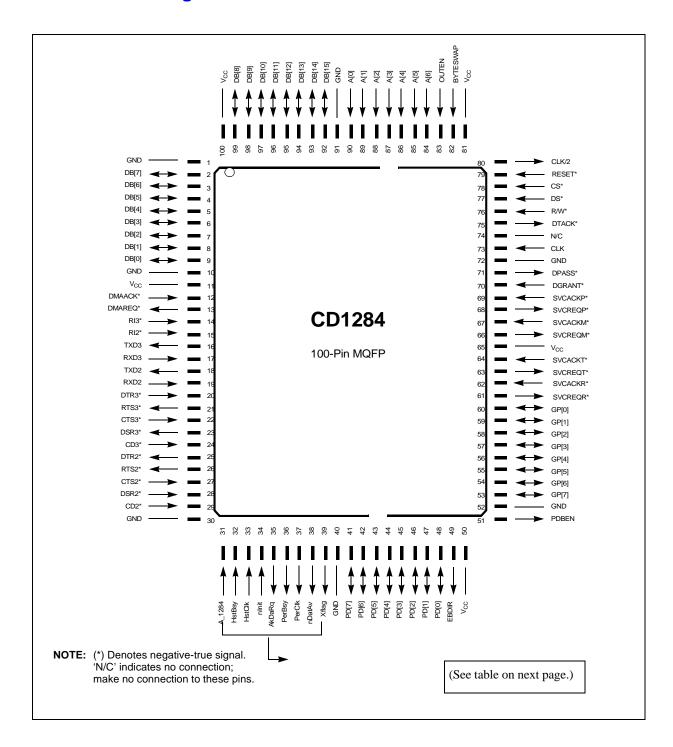

### 3.0 Pin Information

### 3.1 Pin Diagram

| Pin<br>Names | Compati-<br>bility | Reverse<br>Nibble<br>Mode | Reverse<br>Byte<br>Mode | ECP Mode | EPP<br>Mode |  |  |  |  |  |

|--------------|--------------------|---------------------------|-------------------------|----------|-------------|--|--|--|--|--|

| Inputs       |                    |                           |                         |          |             |  |  |  |  |  |

| A_128<br>4   | SLCTIN*            | A_1284                    | A_1284                  | A_1284   | nAStrb      |  |  |  |  |  |

| HstBsy       | AUTOFD*            | HstBsy                    | HstBsy                  | HstAck   | nDStrb      |  |  |  |  |  |

| HstClk       | STROBE*            | STROBE* HstClk HstClk     |                         | HstClk   | nWrite      |  |  |  |  |  |

| nInit        | INIT*              | INIT* nInit nInit nRevReq |                         | nlnit    |             |  |  |  |  |  |

|              |                    | Outp                      | outs                    |          |             |  |  |  |  |  |