40Pin Flash Disk Module Min.8MB ~ Max.512MB, True IDE Interface Mode, 3.3V / 5.0V Operating Part No. HFDOM40B-xxxSx

# **1. PRODUCT OVERVIEW**

### **GENERAL DESCRIPTION**

The HFDOM40B-xxxSx series 40Pin Flash Disk Module is a flash technology based with True IDE interface flash memory card. It is constructed with flash disk controller chip and NAND-type (Samsung) flash memory device. The HFDOM40B-xxxSx series operates in both 3.3-Volt and 5.0-Volt power supplies. It comes in capacity of 8, 16, 32, 64, 128, 192, 256 MB and up to 512 MB formatted 40Pin type .

By optimizing flash memory management, the life of this HFDOM40B-xxxSx series can be extended to its maximum level. Because the ECC function is included, the correctness of data transfer between the HFDOM40B-xxxSx series and a True IDE compatible interface device can be guaranteed.

The HFDOM40B-xxxSx series is fully compatible with applications such as CPU card / board, set top box, industry / military PC / Notebook, security equipment, measuring instrument and embedded systems.

## FEATURES

- True IDE compatible host interface

- Direct plug in for 3.5" IDE Connectors

- 40 pin 2.54mm IDE Connector

- Very high performance, very low power consumption

- Automatic error correction

- Support 3 power save mode : stop/idle/active

- Support for CIS implemented with 256 bytes of attribute memory

- 3.3V/5.0V operation voltage

- Host data transfer rate : 20MB/s

- Flash data transfer rate : 10MB/s

- Host Interface bus width : 8/16 bit Access

- Flash Interface bus width : 8 bit Access

- Capacity : Min. 8MB ~ Max. 384MB

- MTBF : 1,000,000 hours, minimum 30,000 insertions

- Operating vibration : 15G peak to peak maximum

- Operating shock : 1,000G maximum

## **PRODUCT SPECIFICATIONS**

#### Capacities :

8, 16, 32, 64, 128, 192, 256 and up to 512 MB (formatted)

Operating Voltage: 3.3V / 5.0V ±10%

#### Power consumptions :

| Read mode  | 30 mA (typ), 50 Ma (Max) |

|------------|--------------------------|

| Write mode | 30 mA (typ), 70 Ma (Max) |

| Stop mode  | 30 uA (typ)              |

#### Environment conditions :

| Maakaniaal aanditiana . |                  |

|-------------------------|------------------|

| Relative humidity       | 95%(Max)         |

| Storage temperature     | - 25°C to + 85°C |

| Operating temperature   | 0°C to + 60°C    |

|                         |                  |

#### Mechanical conditions :

Weight : Maximum 9.0g

# **ELECTRICAL SPECIFICATIONS**

### Table 1.1 Absolute Maximum Ratings

| Symbol           | Parameter           | Ratings        | Unit |

|------------------|---------------------|----------------|------|

| V <sub>DD</sub>  | Supply voltage      | - 0.3 to + 7.0 | V    |

| V <sub>IN</sub>  | Input voltage       | - 0.3 to + 7.0 | V    |

| I <sub>IN</sub>  | DC input current    | - 10           | mA   |

| T <sub>STG</sub> | Storage temperature | - 20 to + 85   | °C   |

### **Table 1.2 Recommended Operating Conditions**

| Symbol          | Parameter                         |      | Ratings      | Unit |

|-----------------|-----------------------------------|------|--------------|------|

|                 |                                   | 5V   | 4.75 to 5.25 | V    |

| V <sub>DD</sub> | V <sub>DD</sub> DC Supply voltage | 3.3V | 3.0 to 3.6   | V    |

| Ta              | Storage temperature               |      | - 20 to +70  | °C   |

### **Table 1.3 DC Characteristics**

(Ta=0°C to 70°C, V<sub>DD</sub>=3.0 to 5.3V)

| Symbol          | Parameter                 | Min. | Тур. | Max. | Unit |

|-----------------|---------------------------|------|------|------|------|

| I <sub>DD</sub> | Operating Current         |      | 30   | 70   | mA   |

| I <sub>ds</sub> | Stop Current              |      | 50   | 150  | μA   |

| V <sub>DD</sub> | High Level Output Voltage | 2.4  |      |      | V    |

| V <sub>DD</sub> | Low Level Output Voltage  |      |      | 0.4  | V    |

## CAPACITY SPECIFICATIONS

#### Table 1.4 Capacity Specifications

| Part Number    | Capacity (Unformatted)   | Total Sector | Cylinders | Heads | Sectors |

|----------------|--------------------------|--------------|-----------|-------|---------|

| HFDOM40B-016Sx | 15,990,784 <b>bytes</b>  | 31,232       | 61        | 16    | 32      |

| HFDOM40B-032Sx | 32,243,712 <b>bytes</b>  | 62,976       | 123       | 16    | 32      |

| HFDOM40B-064Sx | 65,536,000 <b>bytes</b>  | 128,000      | 250       | 16    | 32      |

| HFDOM40B-128Sx | 131,858,432 <b>bytes</b> | 257,536      | 503       | 16    | 32      |

| HFDOM40B-192Sx | 196,608,000 <b>bytes</b> | 384,000      | 750       | 16    | 32      |

| HFDOM40B-256Sx | 265,027,584 <b>bytes</b> | 517,632      | 1011      | 16    | 32      |

| HFDOM40B-384Sx | 395,837,440 <b>bytes</b> | 773,120      | 1510      | 16    | 32      |

| HFDOM40B-512Sx | 531,890,176 <b>bytes</b> | 1,038,848    | 2029      | 16    | 32      |

# PHYSYCAL SPECIFICATIONS

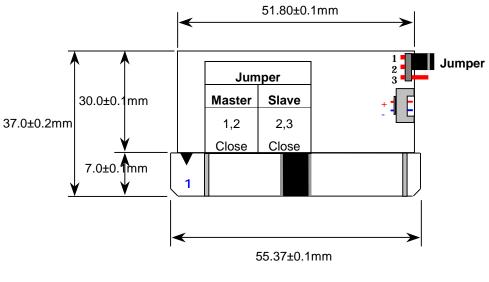

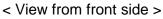

< View from connector side >

Figure 1.1 40 pin Type Flash Disk Module Dimensions

### INSTALLTION GUIDE

#### 1) Setting Method

- ① Make sure your computer is turned off before you open the case.

- Plug the carefully into the 40pin IDE slot on your computer.

Caution: Make sure to align pin1 on host adapter interface connector with pin 1 on your Flash Disk Module. Pin 1 is indicated by a triangle on the Flash Disk Module connector.

- The Flash Disk Module is used power connector cable of the computer.

Caution: If you need to remove your Flash Disk Module, use both hands to pull it out carefully.

- ④ Check all cable connections and then replace your computer cover.

### 2) BIOS setting Method

Before you format or partition your new drive, you must configure your computer's BIOS so that the computer can recognize your new drive.

- ① Turn your computer on. As your computer start up, watch the screen for a message describing how to run the system setup program on the screen (sometimes called BIOS or CMOS setup). This is usually done by pressing a special key, such as **Delete**, **Esc** or **F1** during startup. See your computer manual for details. Press the appropriate key to run the system setup program.

- ② If your BIOS provides automatic drive detection (an "AUTO" drive type), select this option. (We recommend to use Normal / CHS mode to partition your Flash Disk Module to get the maximum formatted capacity.)

This allows your computer to configure itself automatically for your new drive. *If your BIOS dose not provide "AUTO" drive detection, select "User-defined" drive setting and enter the CHS values from the table.* BIOS Settings (see specification) Capacity Cylinders Heads Sectors(unformatted)

③ Save the settings and exit the System Setup program. (your computer will automatically reboot) After you configure your computer, you can use the standard DOS commands to partition and format your Flash Disk Module, as described below.

### 3) Formatting Method

To partition your new Flash Disk Module with Microsoft DOS program :

- ① Insert a bootable DOS diskette into your diskette drive and restart your computer.

- Insert a DOS program diskette that contains the FDISK.EXE and FORMAT.COM programs into your diskette drive. Use the same DOS version that is on your bootable diskette. At the A:\> prompt, type "FDISK" and press Enter.

- ③ Select "Create DOS partition or logical DOS drive" by pressing 1. Then press Enter.

- ④ Select "Create primary DOS partition" by pressing 1 again. Then press Enter. Create your first drive partition. If you are creating a partition that will be used to boot your computer (drive C), make sure that the partition is marked active.

- S Create an extended partition and additional logical drives as necessary, until all the space on your new hard drive has been partitioned.

- When the partitioning is complete, FDISK reboots your computer.

Caution: Make sure to use the correct drive letters so that you do not format a drive that already contains data.

- At the A:\> prompt, type "format c:/s", where c is the letter of your first new partition, Repeat the format process for all the new partitions you have created.

- 8 After you format your drive, it is ready to use.

# 2. PIN INFORMATION

## PIN ASSIGNMENTS AND PIN TYPE

| Table 2.1 Pin Assig | nment and Pin | type |

|---------------------|---------------|------|

|                     |               |      |

| Pin | Signal             | Pin Type | Pin | Signal   | Pin Type |

|-----|--------------------|----------|-----|----------|----------|

| 1   | /RESET             | I        | 2   | GND      | Ground   |

| 3   | D07                | I/O      | 4   | D08      | I/O      |

| 5   | D06                | I/O      | 6   | D09      | I/O      |

| 7   | D05                | I/O      | 8   | D10      | I/O      |

| 9   | D04                | I/O      | 10  | D11      | I/O      |

| 11  | D03                | I/O      | 12  | D12      | I/O      |

| 13  | D02                | I/O      | 14  | D13      | I/O      |

| 15  | D01                | I/O      | 16  | D14      | I/O      |

| 17  | D00                | I/O      | 18  | D15      | I/O      |

| 19  | GND                | DC       | 20  | Key Pin  |          |

| 21  | Reserved           |          | 22  | GND      | Ground   |

| 23  | /IOW               | I        | 24  | GND      | Ground   |

| 25  | /IOR               | I        | 26  | GND      | Ground   |

| 27  | IORDY              | 0        | 28  | Reserved |          |

| 29  | Reserved           |          | 30  | GND      | Ground   |

| 31  | IRQ                | 0        | 32  | /IOIS16  | 0        |

| 33  | A01                | I        | 34  | /PDIAG   | I/O      |

| 35  | A00                | I        | 36  | A02      | I        |

| 37  | /CS0               | I        | 38  | /CS1     | I        |

| 39  | /DASP( <b>LED)</b> | I/O      | 40  | GND      | Ground   |

# **Signal Descriptions**

### Table 2.2 Signal Descriptions

| Signal Name         | Dir. | Pin                             | Description                                                                                                                                                                                                                                                                |

|---------------------|------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A[2:0]              | I    | 33,35,36                        | In True IDE Mode only A[2:0] are used to select the one of eight registers in the Task File, the remaining address lines should be grounded by the host.                                                                                                                   |

| -PDIAG              | I/O  | 34                              | This input / output is the Pass Diagnostic signal in the Master / Slave handshake protocol.                                                                                                                                                                                |

| -DASP( <b>LED</b> ) | I/O  | 39                              | This signal used either to drive an <b>LED</b> whenever the Disk Module is being accessed or as indication of a second drive present. This signal is active low when the Disk Module is busy.                                                                              |

| -CS0, -CS1          | Ι    | 37,38                           | CS0 is the chip select for the task file registers while CS2 is used to select the Alternate Status Register and the Device Control Register.                                                                                                                              |

|                     |      | 3,4,5,6,<br>7,8,9,10,           | All Task File operations occur in byte mode on the low order bus D00-D07 while all data transfers are 16 bit using D00-D15.                                                                                                                                                |

| D[15:00]            | I/O  | 11,12,13,<br>14,15,16,<br>17,18 |                                                                                                                                                                                                                                                                            |

| GND                 |      | 2,19,22,<br>24,26,<br>30,40,    | Ground.                                                                                                                                                                                                                                                                    |

| -IOR                | I    | 25                              | This is an I/O Read strobe generated by the host.                                                                                                                                                                                                                          |

| -IOW                | I    | 23                              | The I/O Write strobe pulse is used to clock I/O data on the Card Data bus into the Storage Card controller registers when the Storage Card is configured to use the I/O interface. The clocking will occur on the negative to positive edge of the signal (trailing edge). |

| IRQ                 | 0    | 31                              | In True IDE Mode signal is the active high Interrupt Request to the host.                                                                                                                                                                                                  |

| -RESET              | Ι    | 1                               | This input pin is the active low hardware reset from the host.                                                                                                                                                                                                             |

| IORDY               | 0    | 27                              | This output signal may be used as IORDY.                                                                                                                                                                                                                                   |

| -IOIS16             | 0    | 32                              | This output signal is asserted low when this device is expecting a word data transfer cycle.                                                                                                                                                                               |

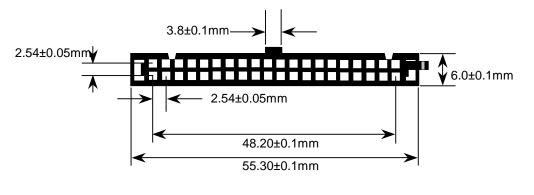

# **BLOCK DIAGRAM**

CONTROLLER

Figure 2.1 Flash Disk Module Block Diagram

# 3. INTERFACE BUS TIMING

### **ACCESS SPCIFICATIONS**

### **IDE MODE I/O ACCESS SPECIFICATIONS**

In this True IDE Mode the Flash Disk Module protocol and configuration are disabled and only I/O operations to the Task File and Data Register are allowed. In this mode no Memory or Attribute Registers are accessible to the host.

| Mode                   | -CE2 | -CE1 | A2-A0 | -IORD | -IOWR | D15 - D8     | D7 – D0       |

|------------------------|------|------|-------|-------|-------|--------------|---------------|

| Invalid Mode           | L    | L    | x     | x     | x     | High Z       | High Z        |

| Standby Mode           | Н    | Н    | x     | x     | х     | High Z       | High Z        |

| Task File Write        | Н    | L    | 1-7h  | н     | L     | Don't Care   | Data In       |

| Task File Read         | н    | L    | 1-7h  | L     | Н     | High Z       | Data Out      |

| Data Register Write    | н    | L    | 0     | н     | L     | Odd Byte in  | Even Byte in  |

| Data Register Read     | н    | L    | 0     | L     | Н     | Odd Byte out | Even Byte out |

| Control Register Write | L    | н    | 6h    | н     | L     | Don't Care   | Control In    |

| All Status Read        | L    | н    | 6h    | L     | Н     | High Z       | Status Out    |

#### Table 3.1 IDE Mode I/O Access Mode

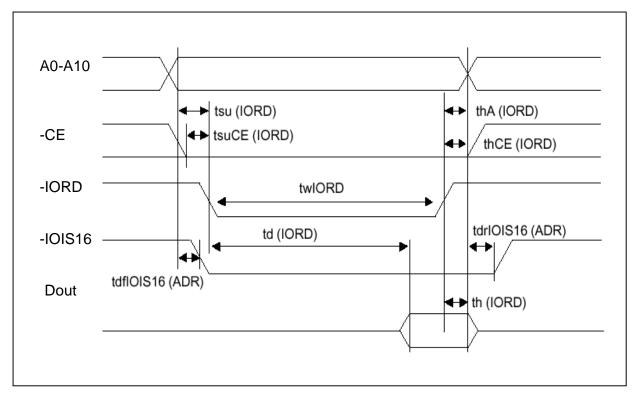

### Table 3.2 IDE Mode I/O Read Timing

| Parameter                         | Symbol          | IEEE Symbol | Min. ns | Max. ns |

|-----------------------------------|-----------------|-------------|---------|---------|

| Data Delay after IORD             | td (IORD)       | tIGLQV      |         | 100     |

| Data Hold following IORD          | th (IORD)       | tIGHQX      | 0       |         |

| IORD Width Time                   | tw (IORD)       | tIGLIGH     | 165     |         |

| Address Setup before IORD         | tsuA (IORD)     | tAVIGL      | 70      |         |

| Address Hold following IORD       | thA (IORD)      | tIGHAX      | 20      |         |

| CE Setup before IORD              | tsuCE (IORD)    | tELIGL      | 5       |         |

| CE Hold following IORD            | thCE (IORD)     | tIGHEH      | 20      |         |

| IOIS16 Delay Falling from Address | tdfIOIS16 (ADR) | tAVISL      |         | 35      |

| IOIS16 Delay Rising from Address  | tdrlOIS16 (ADR) | tAVISH      |         | 35      |

NOTE: The maximum load on -IOIS16 is 1 LSTTL with 50pF total load. All times are in nanoseconds. Minimum time from

-WAIT high to -IORD high is Onsec, but minimum -IORD width must still be met.

Figure 3.1 IDE Mode I/O Read Timing Example

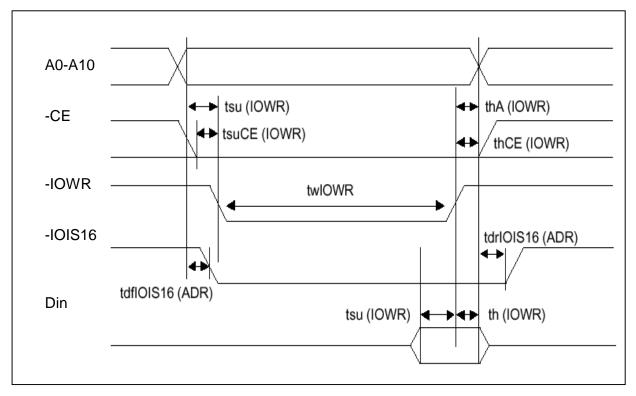

|                                   | Ĭ              |             |         |         |

|-----------------------------------|----------------|-------------|---------|---------|

| Parameter                         | Symbol         | IEEE Symbol | Min. ns | Max. ns |

| Data Setup before IOWR            | tsu(IOWR)      | tDVIWH      | 60      |         |

| Data Hold following IOWR          | th(IOWR)       | tIWHDX      | 30      |         |

| IOWR Width Time                   | twl(OWR)       | tIWLIWH     | 165     |         |

| Address Setup before IOWR         | tsuA(IOWR)     | tAVIWL      | 70      |         |

| Address Hold following IOWR       | thA(IOWR)      | tIWHAX      | 20      |         |

| CE Setup before IOWR              | tsuCE(IOWR)    | tELIWL      | 5       |         |

| CE Hold following IOWR            | thCE(IOWR)     | tIWHEH      | 20      |         |

| IOIS16 Delay Falling from Address | tdfIOIS16(ADR) | tAVISL      |         | 35      |

| IOIS16 Delay Rising from Address  | tdrIOIS16(ADR) | tAVISH      |         | 35      |

#### Table 3.3 IDE Mode I/O Write Timing

NOTE: The maximum load on -IOIS16 is 1 LSTTL with 50pF total load. All times are in nanoseconds. Minimum time from

-WAIT high to -IOWR high is Onsec, but minimum -IOWR width must still be met.

Figure 3.2 IDE Mode I/O Write Timing Example

| NO | Parts          | Size            | Capacity | Media transfer<br>mode | Chip Number | Operation<br>Mode |

|----|----------------|-----------------|----------|------------------------|-------------|-------------------|

| 1  | HFDOM40B-016S1 | 55.3x29.0x0.8mm | 16Mbyte  | BYTE                   | 1           | True IDE          |

| 2  | HFDOM40B-032S1 | 55.3x29.0x0.8mm | 32Mbyte  | BYTE                   | 1           | True IDE          |

| 3  | HFDOM40B-032S2 | 55.3x29.0x0.8mm |          | BYTE                   | 2           | True IDE          |

| 4  | HFDOM40B-064S1 | 55.3x29.0x0.8mm | 64Mbyte  | BYTE                   | 1           | True IDE          |

| 5  | HFDOM40B-064S2 | 55.3x29.0x0.8mm |          | BYTE                   | 2           | True IDE          |

| 6  | HFDOM40B-128S1 | 55.3x29.0x0.8mm | 128Mbyte | BYTE                   | 1           | True IDE          |

| 7  | HFDOM40B-128S2 | 55.3x29.0x0.8mm |          | BYTE                   | 2           | True IDE          |

| 8  | HFDOM40B-192S3 | 55.3x29.0x0.8mm | 192Mbyte | BYTE                   | 3           | True IDE          |

| 9  | HFDOM40B-256S2 | 55.3x29.0x0.8mm | 256Mbyte | BYTE                   | 2           | True IDE          |

| 10 | HFDOM40B-384S3 | 55.3x29.0x0.8mm | 384Mbyte | BYTE                   | 3           | True IDE          |

| 11 | HFDOM40B-512S4 | 55.3x29.0x0.8mm | 512Mbyte | BYTE                   | 4           | True IDE          |

# **Ordering Infomation**