# 54F407 Data Access Register

#### **General Description**

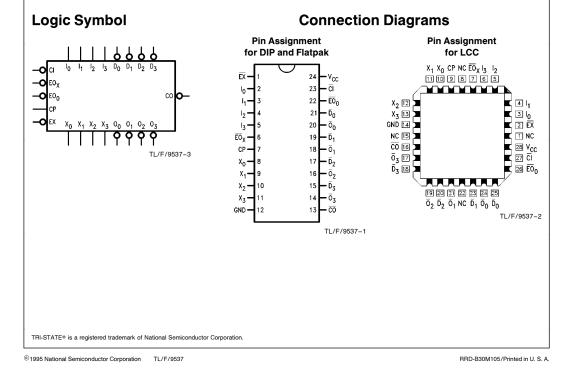

The 'F407 Data Access Register (DAR) performs memory address arithmetic for RAM resident stack applications. It contains three 4-bit registers intended for Program Counter (R<sub>0</sub>), Stack Pointer (R<sub>1</sub>), and Operand Address (R<sub>2</sub>). The 'F407 implements 16 instructions which allow either pre- or post-decrement/increment and register-to-register transfer in a single clock cycle. It is expandable in 4-bit increments and can operate at a 30 MHz microinstruction rate on a 16-bit word. The TRI-STATE® outputs are provided for bus-oriented applications. The 'F407 is fully compatible with all TTL families.

#### Features

- High-speed—greater than a 30 MHz microinstruction rate

- Three 4-bit registers

- 16 instructions for register manipulation

- Two separate output ports, one transparent

- Relative addressing capability

- TRI-STATE Outputs

- Optional pre- or post- arithmetic

- Expandable in multiples of four bits

- 24-pin slim package

- 9407 replacement

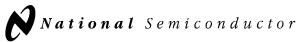

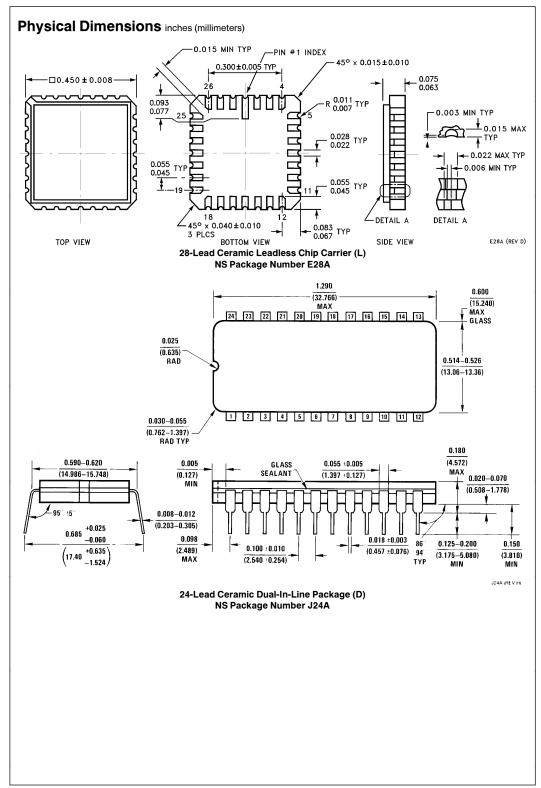

| Military           | Package<br>Number | Package Description                           |

|--------------------|-------------------|-----------------------------------------------|

| 54F407DM (Note 1)  | J24A              | 24-Lead Ceramic Dual-In-Line                  |

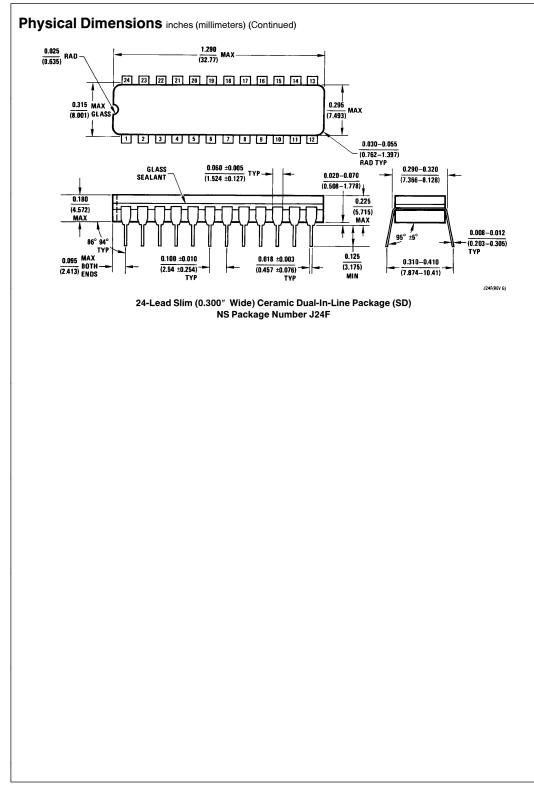

| 54F407SDM (Note 1) | J24F              | 24-Lead (0.300" Wide) Ceramic Dual-In-Line    |

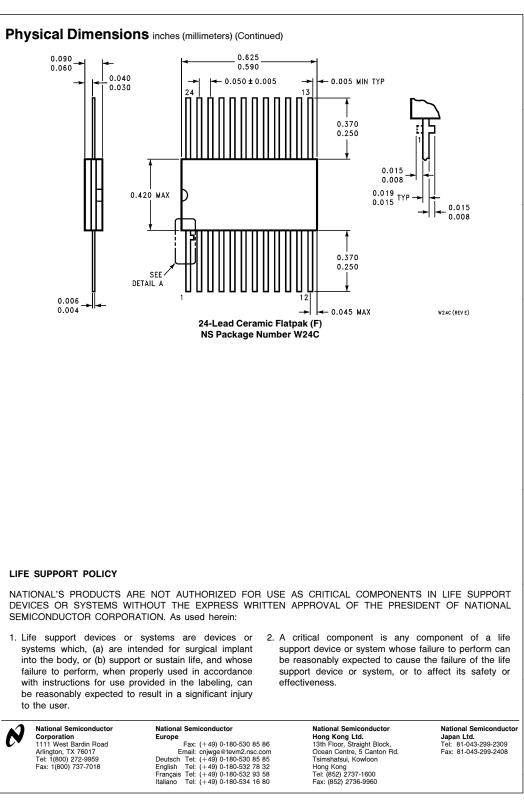

| 54F407FM (Note 1)  | W24C              | 24-Lead Cerpack                               |

| 54F407FM (Note 1)  | E28A              | 28-Lead Ceramic Leadless Chip Carrier, Type C |

Note 1: Military grade device with environmental and burn-in processing. Use suffix = DMQB, FMQB and LMQB.

54F407 Data Access Register

December 1994

#### **Unit Loading/Fan Out**

|                                   |                                          |                       | 54F                                                                               |  |

|-----------------------------------|------------------------------------------|-----------------------|-----------------------------------------------------------------------------------|--|

| Pin Names                         | Description                              | U.L.<br>HIGH/LOW      | Input I <sub>IH</sub> /I <sub>IL</sub><br>Output I <sub>OH</sub> /I <sub>OL</sub> |  |

| $\overline{D}_0 - \overline{D}_3$ | Data Inputs (Active LOW)                 | 1.0/0.67              | 20 µA/−0.4 mA                                                                     |  |

| I <sub>0</sub> -I <sub>3</sub>    | Instruction Word Inputs                  | 1.0/0.67              | 20 µA/−0.4 mA                                                                     |  |

| CI                                | Carry Input (Active LOW)                 | 1.0/0.67              | 20 µA/−0.4 mA                                                                     |  |

| CO                                | Carry Output (Active LOW)                | 20/13.3 (0.67)        | 0.4 mA/8 mA (4 mA)                                                                |  |

| CP                                | Clock Input (L-H Edge-Triggered)         | 1.0/0.67              | 20 µA/−0.4 mA                                                                     |  |

| EX                                | Execute Input (Active LOW)               | 1.0/0.67              | $20 \mu\text{A}/-0.4 \text{mA}$                                                   |  |

| EOX                               | Address Output Enable Input (Active LOW) | 1.0/0.67              | $20 \mu\text{A}/-0.4 \text{mA}$                                                   |  |

| EO <sub>0</sub>                   | Data Output Enable Input (Active LOW)    | 1.0/0.67              | $20 \mu\text{A}/-0.4 \text{mA}$                                                   |  |

| X <sub>0</sub> -X <sub>3</sub>    | Address Outputs                          | 284 (100)/26.7 (13.3) | -5.7 mA (2 mA)/16 mA (8 mA)                                                       |  |

| $\overline{O}_0 - \overline{O}_3$ | Data Outputs (Active LOW)                | 284 (100)/26.7 (13.3) | -5.7 mA (2 mA)/16 mA (8 mA)                                                       |  |

#### **Functional Description**

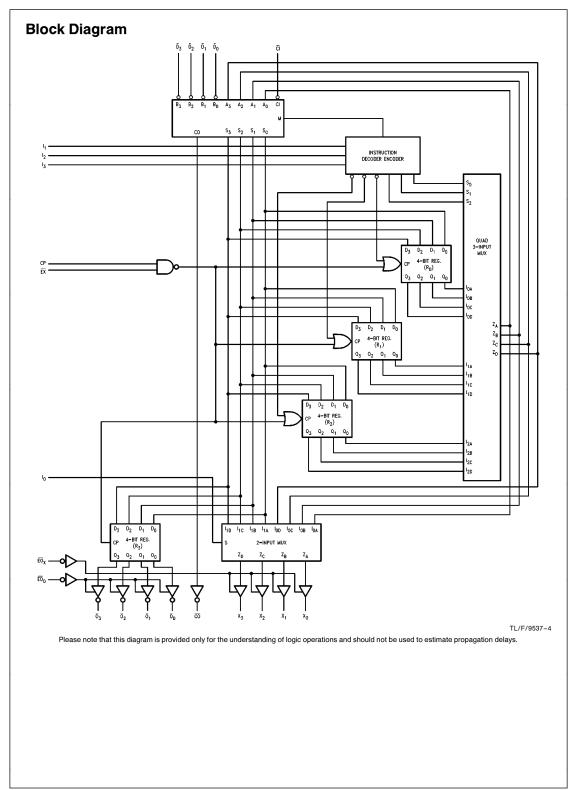

The 'F407 contains a 4-bit slice of three Registers (R<sub>0</sub>-R<sub>2</sub>), a 4-bit Adder, a TRI-STATE Address Output Buffer (X<sub>0</sub>-X<sub>3</sub>) and a separate Output Register with TRI-STATE buffers ( $\overline{O}_0-\overline{O}_3$ ), allowing output of the register contents on the data bus (refer to the Block Diagram). The DAR performs sixteen instructions, selected by  $l_0-l_3$ , as listed in the Function Table.

The 'F407 operates on a single clock. CP and  $\overline{\text{EX}}$  are inputs to a 2-input, active LOW AND gate. For normal operation  $\overline{\text{EX}}$  is brought LOW while CP is HIGH. A microcycle starts as the clock goes HIGH. Data inputs  $\overline{\mathbb{D}}_0-\overline{\mathbb{D}}_3$  are applied to the Adder as one of the operands. Three of the four instruction lines  $(I_1-I_2-I_3)$  select which of the three registers, if any, is to be used as the other operand. The LOW-to-HIGH CP transition writes the result from the Adder into a register  $(R_0-R_2)$  and into the output register provided  $\overline{\text{EX}}$  is LOW. If

the I<sub>0</sub> instruction input is HIGH, the multiplexer routes the result from the Adder to the TRI-STATE Buffer controlling the address bus (X<sub>0</sub>-X<sub>3</sub>), independent of  $\overline{\text{EX}}$  and CP. The 'F407 is organized as a 4-bit register slice. The active LOW  $\overline{\text{CI}}$  and  $\overline{\text{CO}}$  lines allow ripple-carry expansion over longer word lengths.

In a typical application, the register utilization in the DAR may be as follows:  ${\sf R}_0$  is the Program Counter (PC),  ${\sf R}_1$  is the Stack Pointer (SP) for memory resident stacks and  ${\sf R}_2$  contains the operand address. For an instruction Fetch, PC can be gated on the X-Bus while it is being incremented (i.e., D-Bus = 1). If the fetched instruction calls for an effective address for execution, which is displaced from the PC, the displacement can be added to the PC and loaded into  ${\sf R}_2$  during the next microcycle.

|                |                |                |                | Function Table                                  |                                                              |

|----------------|----------------|----------------|----------------|-------------------------------------------------|--------------------------------------------------------------|

|                | Instru         | iction         |                | <b>Combinatorial Function</b>                   | Sequential Function Occurring                                |

| I <sub>3</sub> | l <sub>2</sub> | l <sub>1</sub> | l <sub>0</sub> | Available on the X-Bus                          | on the Next Rising CP Edge                                   |

| L              | L              | L              | L              | R <sub>0</sub>                                  | $ m R_0$ Plus D Plus Cl $ ightarrow$ $ m R_0$ and 0-Register |

| L              | L              | L              | H              | R <sub>0</sub> Plus D Plus Cl                   |                                                              |

| L              | L              | н              | L              | R <sub>0</sub>                                  | $R_0$ Plus D Plus Cl $\rightarrow R_1$ and 0-Register        |

| L              | L              | н              | H              | R <sub>0</sub> Plus D Plus Cl                   |                                                              |

| L              | н              | L              | L              | R <sub>0</sub>                                  | $R_0$ Plus D Plus Cl $\rightarrow R_2$ and 0-Register        |

| L              | н              | L              | H              | R <sub>0</sub> Plus D Plus Cl                   |                                                              |

| L              | H              | H              | L              | R <sub>1</sub>                                  | $R_1$ Plus D Plus Cl $\rightarrow R_1$ and 0-Register        |

| L              | H              | H              | H              | R <sub>1</sub> Plus D Plus Cl                   |                                                              |

| H              | L              | L              | L              | R <sub>2</sub>                                  | D Plus Cl $\rightarrow$ R <sub>2</sub> and 0-Register        |

| H              | L              | L              | H              | D Plus Cl                                       |                                                              |

| H              | L              | H              | L              | R <sub>0</sub>                                  | D Plus Cl $\rightarrow$ R <sub>0</sub> and 0-Register        |

| H              | L              | H              | H              | D Plus Cl                                       |                                                              |

| H<br>H         | H<br>H         | L              | L              | R <sub>2</sub><br>R <sub>2</sub> Plus D Plus Cl | $ m R_2$ Plus D Plus Cl $ ightarrow  m R_2$ and 0-Register   |

| H              | H              | H              | L              | R <sub>1</sub>                                  | D Plus Cl $\rightarrow$ R <sub>1</sub> and 0-Register        |

| H              | H              | H              | H              | D Plus Cl                                       |                                                              |

H = HIGH Voltage Level L = LOW Voltage Level

### Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

| Storage Temperature                                              | -65°C to +150°C                      |

|------------------------------------------------------------------|--------------------------------------|

| Ambient Temperature under Bias                                   | -55°C to +125°C                      |

| Junction Temperature under Bias                                  | -55°C to +175°C                      |

| V <sub>CC</sub> Pin Potential to<br>Ground Pin                   | -0.5V to +7.0V                       |

| Input Voltage (Note 2)                                           | -0.5V to $+7.0V$                     |

| Input Current (Note 2)                                           | -30 mA to $+5.0$ mA                  |

| Voltage Applied to Output<br>in HIGH State (with $V_{CC} = 0V$ ) |                                      |

| Standard Output                                                  | -0.5V to V <sub>CC</sub>             |

| TRI-STATE Output                                                 | -0.5V to $+5.5V$                     |

| Current Applied to Output<br>in LOW State (Max)                  | twice the rated I <sub>OL</sub> (mA) |

in LOW State (Max) twice the rated I<sub>OL</sub> (mA) Note 1: Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.

Note 2: Either voltage limit or current limit is sufficient to protect inputs.

## **DC Electrical Characteristics**

# Recommended Operating Conditions

| Free Air Ambient Temperature |  |

|------------------------------|--|

| Military                     |  |

Supply Voltage Military -55°C to +125°C +4.5V to +5.5V

| Symbol           | Parame                               | tor                                                | 54F        |     |      | Units | Vcc | Conditions                                                                                                                                      |  |

|------------------|--------------------------------------|----------------------------------------------------|------------|-----|------|-------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Symbol           | Farame                               | ter                                                | Min        | Тур | Max  | Units | vcc | Conditions                                                                                                                                      |  |

| V <sub>IH</sub>  | Input HIGH Voltage                   |                                                    | 2.0        |     |      | V     |     | Recognized as a HIGH Signal                                                                                                                     |  |

| VIL              | Input LOW Voltage                    |                                                    |            |     | 0.8  | V     |     | Recognized as a LOW Signal                                                                                                                      |  |

| V <sub>CD</sub>  | Input Clamp Diode Vo                 | oltage                                             |            |     | -1.5 | V     | Min | $I_{IN} = -18 \text{ mA}$                                                                                                                       |  |

| V <sub>OH</sub>  | Output HIGH<br>Voltage               | 54F 10% V <sub>CC</sub><br>54F 10% V <sub>CC</sub> | 2.4<br>2.4 |     |      | V     | Min | $\begin{split} I_{OH} &= -0.4 \text{ mA } (\overline{CO}) \\ I_{OH} &= -2 \text{ mA } (X_0 - X_3, \overline{O}_0 - \overline{O}_3) \end{split}$ |  |

| V <sub>OL</sub>  | Output LOW<br>Voltage                | 54F 10% V <sub>CC</sub><br>54F 10% V <sub>CC</sub> | 0.5<br>0.5 |     |      | V     | Min | $\begin{split} I_{OL} &= 4 \text{ mA } (\overline{CO}) \\ I_{OL} &= 8 \text{ mA } (X_0 - X_3, \overline{O}_0 - \overline{O}_3) \end{split}$     |  |

| I <sub>IH</sub>  | Input HIGH Current                   | 54F                                                |            |     | 20.0 | μA    | Max | $V_{IN} = 2.7V$                                                                                                                                 |  |

| I <sub>BVI</sub> | Input HIGH Current<br>Breakdown Test | 54F                                                |            |     | 100  | μA    | Max | $V_{IN} = 7.0V$                                                                                                                                 |  |

| ICEX             | Output HIGH<br>Leakage Current       | 54F                                                |            |     | 250  | μΑ    | Max | $V_{OUT} = V_{CC}$                                                                                                                              |  |

| IIL              | Input LOW Current                    |                                                    |            |     | -0.4 | mA    | Max | $V_{IN} = 0.5V$                                                                                                                                 |  |

| I <sub>OZH</sub> | Output Leakage Curr                  | ent                                                |            |     | 50   | μA    | Max | $V_{OUT} = 2.7V (X_0 - X_3, \overline{O}_0 - \overline{O}_3)$                                                                                   |  |

| I <sub>OZL</sub> | Output Leakage Curr                  | ent                                                |            |     | -50  | μA    | Max | $V_{OUT} = 0.5V (X_0 - X_3, \overline{O}_0 - \overline{O}_3)$                                                                                   |  |

| IOS              | Output Short-Circuit (               | Current                                            | -30        |     | -100 | mA    | Max | $V_{OUT} = 0V$                                                                                                                                  |  |

| Icc              | Power Supply Curren                  | t                                                  |            | 90  | 145  | mA    | Max |                                                                                                                                                 |  |

|                                      |                                                                                    | 5            | 4F                          |       |             |

|--------------------------------------|------------------------------------------------------------------------------------|--------------|-----------------------------|-------|-------------|

| Symbol                               | Parameter                                                                          |              | <sub>C</sub> = Mil<br>50 pF | Units | Fig.<br>No. |

|                                      |                                                                                    | Min          | Мах                         |       |             |

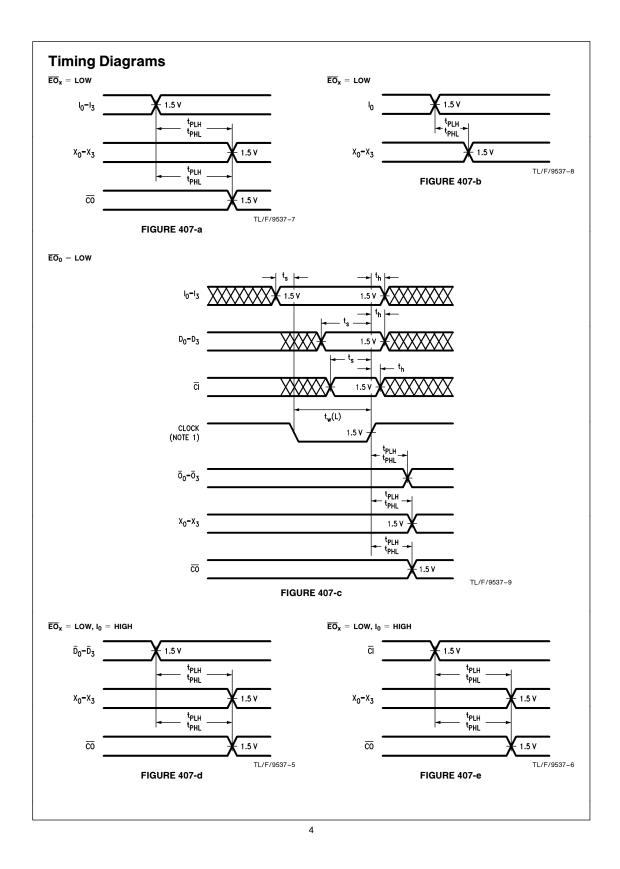

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>CP to O <sub>n</sub> (Note 1)                                 | 7.0<br>4.0   | 24.0<br>15.0                | ns    | 407-c       |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay, $I_0$ LOW $I_1-I_3$ to $X_0-X_3$                                | 7.5<br>8.0   | 21.0<br>25.0                | ns    | 407-a       |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay, $I_0$ HIGH $I_1-I_3$ to $X_0-X_3$                               | 8.5<br>6.5   | 50.0<br>35.0                | ns    | 407-a       |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay, I <sub>0</sub> LOW<br>CP to X <sub>n</sub>                      | 7.0<br>8.5   | 24.0<br>28.0                | ns    | 407-b       |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay, I <sub>0</sub> HIGH<br>CP to X <sub>n</sub>                     | 16.0<br>11.5 | 43.0<br>36.5                | ns    | 407-b       |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay $\overline{D}_n$ to $X_n$                                        | 6.5<br>3.0   | 29.0<br>20.5                | ns    | 407-d       |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>CI to X <sub>n</sub>                                          | 4.0<br>4.5   | 22.0<br>14.0                | ns    | 407-e       |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>I <sub>0</sub> to X <sub>n</sub>                              | 4.0<br>3.0   | 14.5<br>19.5                | ns    | 407-b       |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>CP to CO                                                      | 9.0<br>6.5   | 33.0<br>38.0                | ns    | 407-a       |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>CI to CO                                                      | 3.0<br>3.0   | 11.0<br>10.0                | ns    | 407-е       |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay $\overline{D}_n$ to $\overline{CO}$                              | 3.0<br>3.5   | 10.0<br>10.0                | ns    | 407-d       |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay $I_1 - I_3$ to $\overline{CO}$                                   | 8.0<br>6.0   | 23.0<br>32.5                | ns    | 407-a       |

| t <sub>PZH</sub><br>t <sub>PZL</sub> | Enable Time<br>$\overline{EO}_0$ to $\overline{O}_n$ or $\overline{EO}_x$ to $X_n$ | 4.5<br>3.5   | 26.0<br>16.0                | ns    |             |

Note 1: The internal clock is generated from CP and EX. The internal Clock is HIGH if EX or CP is HIGH, LOW if EX and CP are LOW.

|                                                                                                                                   |                                                                                                                                                 | 5            | 4F                                                                |                                                                      |          |

|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------------------------------------------------------|----------------------------------------------------------------------|----------|

| Symbol                                                                                                                            | Parameter                                                                                                                                       |              | c = Mil<br>50 pF                                                  | Units                                                                | Fig      |

|                                                                                                                                   |                                                                                                                                                 | Min          | Max                                                               |                                                                      |          |

| t <sub>cw</sub>                                                                                                                   | Clock Period                                                                                                                                    | 36.0         |                                                                   | ns                                                                   |          |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L)                                                                                          | Setup Time, HIGH or LOW<br>I1-I3 to Negative-Going CP                                                                                           | 4.5<br>4.5   |                                                                   | 20                                                                   | 407      |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L)                                                                                          | Hold Time, HIGH or LOW<br>I1-I3 to Positive-Going CP                                                                                            | 0<br>0       |                                                                   | - ns                                                                 | 407      |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L)                                                                                          | Setup Time, HIGH or LOW $\overline{D}_n$ or $\overline{C}_1$ to Negative-Going CP                                                               | 18.5<br>18.5 |                                                                   |                                                                      |          |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L)                                                                                          | Hold Time, HIGH or LOW<br>D <sub>n</sub> or Cl to<br>Negative-Going Clock                                                                       | 0            |                                                                   | ns                                                                   | 407      |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L)                                                                                          | Setup Time, HIGH or LOW<br>Cl to Positive-Going CP                                                                                              | 14.5<br>14.5 |                                                                   | 20                                                                   | 407      |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L)                                                                                          | Hold Time, HIGH or LOW<br>Cl to Positive-Going CP                                                                                               | 0<br>0       |                                                                   | - ns                                                                 | 407      |

| t <sub>w</sub> (H)<br>t <sub>w</sub> (L)                                                                                          | Clock Pulse Width<br>HIGH or LOW                                                                                                                | 8.5<br>8.5   |                                                                   | ns                                                                   | 407      |

| rdering I<br>e device numl<br>fined as follow                                                                                     | nformation<br>per is used to form part of a simplified purs:<br>54F 4<br>ure Range Family                                                       | DT D M QB    | — Special Varia<br>QB = Milita                                    | tions<br>ıry grade device wi                                         | th       |

| rdering I<br>e device numl<br>fined as follow<br>Temperatu<br>54F = N<br>Device Typ<br>Package C<br>D = Ce<br>SD = Sli            | nformation<br>ber is used to form part of a simplified purs:<br>ure Range Family                                                                |              | – Special Varia<br>QB = Milita<br>envir<br>proce<br>– Temperature | tions<br>Iry grade device wi<br>onmental and burn<br>əssing          | th<br>in |

| rdering I<br>e device numl<br>fined as follow<br>Temperatu<br>54F = N<br>Device Typ<br>Package C<br>D = Ce<br>SD = Sli<br>F = Fla | nformation<br>ber is used to form part of a simplified purs:<br>ure Range Family                                                                |              | – Special Varia<br>QB = Milita<br>envir<br>proce<br>– Temperature | tions<br>Iry grade device wi<br>onmental and burn<br>essing<br>Range | th<br>in |

| rdering I<br>e device numl<br>fined as follow<br>Temperatu<br>54F = N<br>Device Typ<br>Package C<br>D = Ce<br>SD = Sli<br>F = Fla | nformation<br>ber is used to form part of a simplified pures:<br><u>54F</u> 4<br>wilitary<br>De<br>code<br>cramic DIP<br>m Ceramic DIP<br>atpak |              | – Special Varia<br>QB = Milita<br>envir<br>proce<br>– Temperature | tions<br>Iry grade device wi<br>onmental and burn<br>essing<br>Range | th<br>in |

| rdering I<br>e device numl<br>fined as follow<br>Temperatu<br>54F = N<br>Device Typ<br>Package C<br>D = Ce<br>SD = Sli<br>F = Fla | nformation<br>ber is used to form part of a simplified pures:<br><u>54F</u> 4<br>wilitary<br>De<br>code<br>cramic DIP<br>m Ceramic DIP<br>atpak |              | – Special Varia<br>QB = Milita<br>envir<br>proce<br>– Temperature | tions<br>Iry grade device wi<br>onmental and burn<br>essing<br>Range | th<br>in |

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications