#### Preliminary Data Sheet October 2000

# microelectronics group

# TFRA08C13 OCTAL T1/E1 Framer

### Features

- Eight independent T1/E1 transmit and receive framers.

- Internal DS1 transmit clock synthesis—no external oscillator necessary.

- Comprehensive alarm reporting and performance monitoring:

- Programmable automatic and on-demand alarm transmission.

- Automatic facility data link:

- Automatic transmission of ESF performance report message.

- Common 2.048 Mbits/s, 4.096 Mbits/s, or 8.192 Mbits/s TDM highway.

- Dual- or single-rail line-side I/O.

- Supports one second polling interval for performance monitoring.

- *IEEE*\* Std. 1149.1 JTAG boundary scan.

- 3.3 V low-power CMOS with 5 V tolerant inputs.

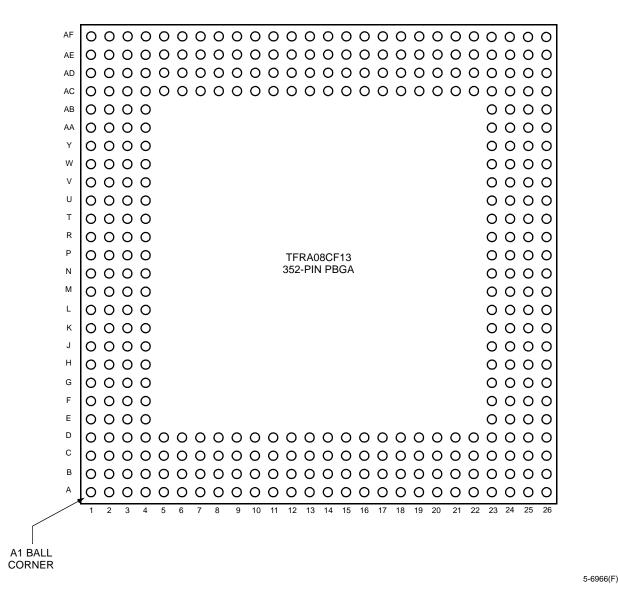

- Available in 352-pin PBGA.

#### **T1/E1 Framer Features**

- Supports T1 framing modes ESF, D4, SLC<sup>®</sup>-96, T1DM DDS.

- Supports G.704 basic and CRC-4 multiframe format E1 framing and procedures consistent with G.706.

- Supports unframed transmission format.

- T1 signaling modes: transparent; ESF 2-state, 4-state, and 16-state; D4 2-state and 4-state; SLC-96 2-state, 4-state, 9-state, and 16-state. E1 signaling modes: transparent and CAS.

- Alarm reporting and performance monitoring per AT&T, ANSI<sup>†</sup>, and ITU-T standards.

- Programmable, independent transmit and receive system interfaces at a 2.048 MHz, 4.096 MHz, or 8.192 MHz data rate.

## **Facility Data Link Features**

- HDLC or transparent mode.

- Automatic transmission of the ESF performance report messages (PRM).

- Detection of the ESF PRM.

- Detection of the ANSI ESF FDL bit-oriented codes.

- 64-byte FIFO in both transmit and receive directions.

- Programmable FIFO full and empty level interrupt.

- User-programmable microprocessor interface.

### **Microprocessor Interface**

- 33 MHz read and write access.

- 12-bit address, 8-bit data interface.

- Intel<sup>‡</sup> or Motorola<sup>§</sup> style control interfaces.

- Directly addressable internal registers.

- Programmable interrupts.

## Applications

- DS3 and E3 port cards for narrowband DXCs.

- Multiservice switches.

- High density DS1 and E1 port cards.

- Frame relay access devices.

- Byte-synchronous SDH/SONET mapping.

- SONET and SDH drop alignment.

- IP and packet routers.

- \* *IEEE* is a registered trademark of The Institute of Electrical and Electronics Engineers, Inc.

- † ANSI is a registered trademark of American National Standards Institute, Inc.

- ‡ Intel is a registered trademark of Intel Corporation.

- § Motorola is a registered trademark of Motorola, Inc.

Page

# **Table of Contents**

#### Contents

| Features                                                                                    | 1  |

|---------------------------------------------------------------------------------------------|----|

| T1/E1 Framer Features                                                                       | 1  |

| Facility Data Link Features                                                                 | 1  |

| Microprocessor Interface                                                                    | 1  |

| Applications                                                                                | 1  |

| Feature Descriptions                                                                        | 10 |

| T1/E1 Framer Feature Descriptions                                                           | 10 |

| Functional Description                                                                      | 11 |

| Pin Information                                                                             | 15 |

| LIU-Framer Interface                                                                        |    |

| LIU-Framer Physical Interface                                                               |    |

| Line Encoding.                                                                              | 31 |

| DS1: Zero Code Suppression (ZCS)                                                            | 31 |

| CEPT: High-Density Bipolar of Order 3 (HDB3)                                                |    |

| Frame Formats                                                                               |    |

| T1 Framing Structures                                                                       |    |

| T1 Loss of Frame Alignment (LFA)                                                            | 41 |

| T1 Frame Recovery Alignment Algorithms                                                      |    |

| T1 Robbed-Bit Signaling                                                                     | 43 |

| CEPT 2.048 Basic Frame, CRC-4 Time Slot 0, and Signaling Time Slot 16 Multiframe Structures |    |

| CEPT 2.048 Basic Frame Structure                                                            |    |

| CEPT Loss of Basic Frame Alignment (LFA)                                                    | 48 |

| CEPT Loss of Frame Alignment Recovery Algorithm                                             | 48 |

| CEPT Time Slot 0 CRC-4 Multiframe Structure                                                 |    |

| CEPT Loss of CRC-4 Multiframe Alignment (LTS0MFA)                                           | 50 |

| CEPT Loss of CRC-4 Multiframe Alignment Recovery Algorithms                                 | 51 |

| CEPT Time Slot 16 Multiframe Structure                                                      | 55 |

| CEPT Loss of Time Slot 16 Multiframe Alignment (LTS16MFA)                                   | 56 |

| CEPT Loss of Time Slot 16 Multiframe Alignment Recovery Algorithm                           | 56 |

| CEPT Time Slot 0 FAS/NOT FAS Control Bits                                                   |    |

| FAS/NOT FAS Si- and E-Bit Source                                                            | 56 |

| NOT FAS A-Bit (CEPT Remote Frame Alarm) Sources                                             | 57 |

| NOT FAS Sa-Bit Sources                                                                      | 57 |

| Sa Facility Data Link Access                                                                | 58 |

| NOT FAS Sa Stack Source and Destination                                                     | 59 |

| CEPT Time Slot 16 X0—X2 Control Bits                                                        |    |

| Signaling Access                                                                            | 61 |

| Transparent Signaling                                                                       | 61 |

| DS1: Robbed-Bit Signaling                                                                   | 61 |

| CEPT: Time Slot 16 Signaling                                                                | 62 |

| Auxiliary Framer I/O Timing                                                                 | 63 |

| Alarms and Performance Monitoring                                                           | 67 |

| Interrupt Generation                                                                        | 67 |

| Alarm Definition                                                                            | 67 |

| Event Counters Definition                                                                   |    |

| Loopback and Transmission Modes                                                             | 75 |

| Line Test Patterns                                                                          |    |

| Receive Line Pattern Monitor—Using Register FRM_SR7                                         |    |

| Automatic and On-Demand Commands                                                            |    |

| Facility Data Link                                                                          |    |

## Contents

## Page

| Receive Facility Data Link Interface                              |     |

|-------------------------------------------------------------------|-----|

| Transmit Facility Data Link Interface                             |     |

| HDLC Operation                                                    |     |

| Transparent Mode                                                  |     |

| Diagnostic Modes                                                  |     |

| Phase-Lock Loop Circuit                                           |     |

| Framer-System Interface                                           |     |

| DS1 Modes                                                         |     |

| CEPT Modes                                                        |     |

| Receive Elastic Store                                             |     |

| Transmit Elastic Store                                            |     |

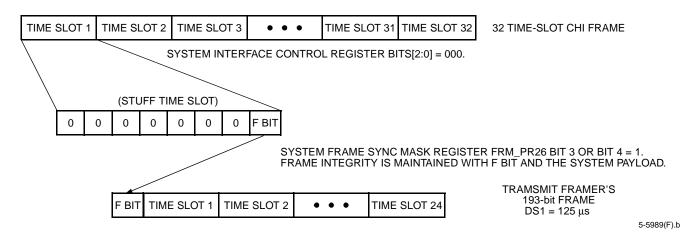

| Concentration Highway Interface                                   |     |

| CHI Parameters                                                    |     |

| CHI Frame Timing                                                  |     |

| CHI Offset Programming                                            |     |

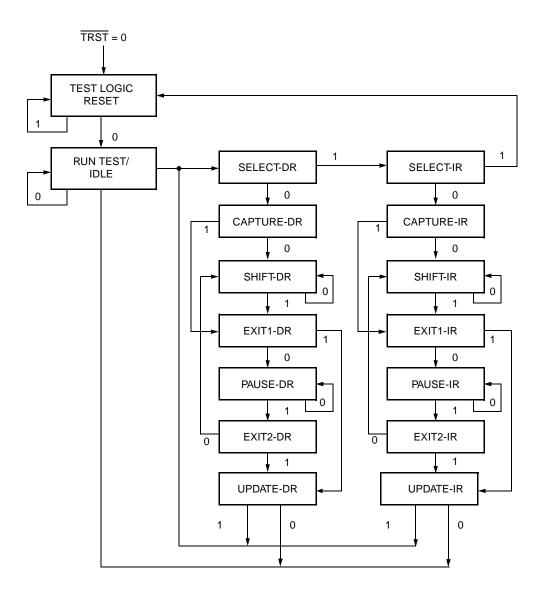

| JTAG Boundary-Scan Specification                                  |     |

| Principle of the Boundary Scan                                    |     |

| Test Access Port Controller                                       |     |

| Instruction Register                                              |     |

| Boundary-Scan Register                                            |     |

| BYPASS Register                                                   |     |

| DCODE Register                                                    |     |

| 3-State Procedures                                                |     |

| Microprocessor Interface                                          |     |

| Overview                                                          |     |

| Microprocessor Configuration Modes                                |     |

| Microprocessor Interface Pinout Definitions                       |     |

| Microprocessor Clock (MPCLK) Specifications                       |     |

| Microprocessor Interface Register Address Map                     |     |

| I/O Timing                                                        |     |

| Reset                                                             | 118 |

| Hardware Reset (Pin C19)                                          |     |

| Software Reset/Software Restart                                   |     |

| Interrupt Generation                                              |     |

| Register Architecture                                             |     |

| Global Register Architecture                                      |     |

| Global Register Structure                                         |     |

| Framer Block Interrupt Status Register (GREG0)                    |     |

| Framer Block Interrupt Enable Register (GREG1)                    |     |

| FDL Block Interrupt Status Enable Register (GREG2)                |     |

| FDL Block Interrupt Enable Register (GREG3)                       |     |

| Global Control Register (GREG4)                                   |     |

| Device ID and Version Registers (GREG5—GREG7)                     |     |

| Global Control Register (GREG8)                                   |     |

| Global PLLCK Control Register (GREG9)                             |     |

| Framer Register Architecture                                      |     |

| Framer Status/Counter Registers                                   |     |

| Framer Parameter/Control Registers                                |     |

| FDL Register Architecture                                         |     |

| FDL Parameter/Control Registers ((A00—A0E); (A20—A2E); (B00—B0E); |     |

| (B20—B2E) (C00—C0E); (C20—C2E); (D00—D0E); (D20—D2E))             | 169 |

Lucent Technologies Inc.

#### Contents

| Register Maps                                                          | 176 |

|------------------------------------------------------------------------|-----|

| Global Registers                                                       | 176 |

| Framer Parameter/Control Registers (Read-Write)                        |     |

| Receive Framer Signaling Registers (Read-Only)                         |     |

| Framer Unit Parameter Register Map                                     |     |

| Transmit Signaling Registers (Read/Write)                              | 183 |

| Facility Data Link Parameter/Control and Status Registers (Read-Write) | 184 |

| Absolute Maximum Ratings                                               | 185 |

| Operating Conditions                                                   | 185 |

| Handling Precautions                                                   | 185 |

| Electrical Characteristics                                             | 186 |

| Logic Interface Characteristics                                        | 186 |

| Power Supply Bypassing                                                 |     |

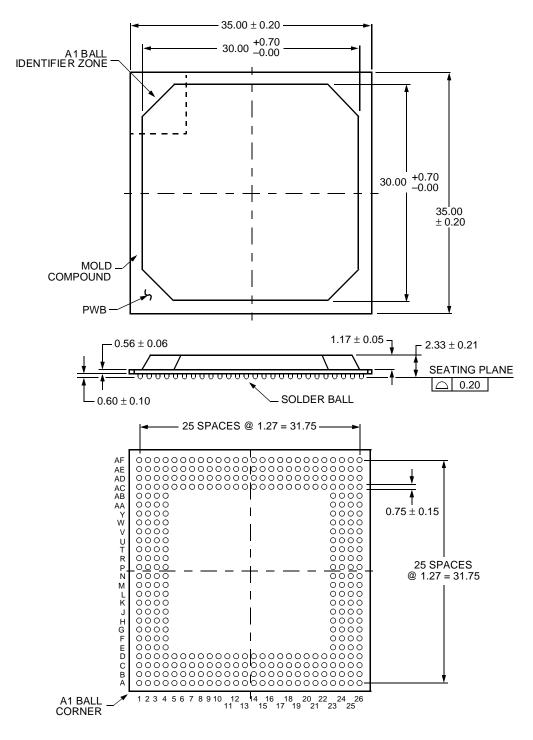

| Outline Diagram                                                        | 187 |

| 352-Pin PBGA                                                           | 187 |

| Ordering Information                                                   | 188 |

## Figures

# Page

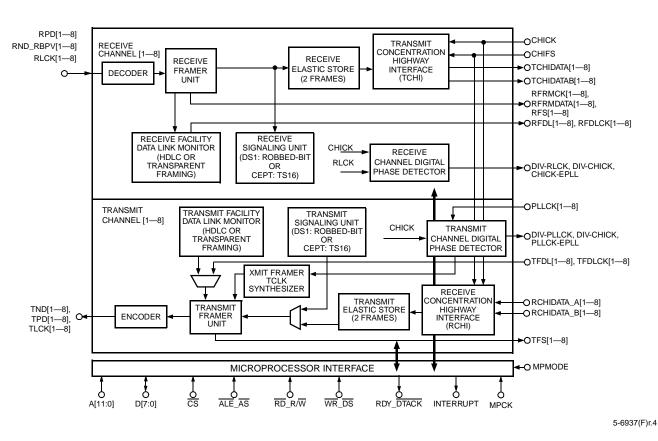

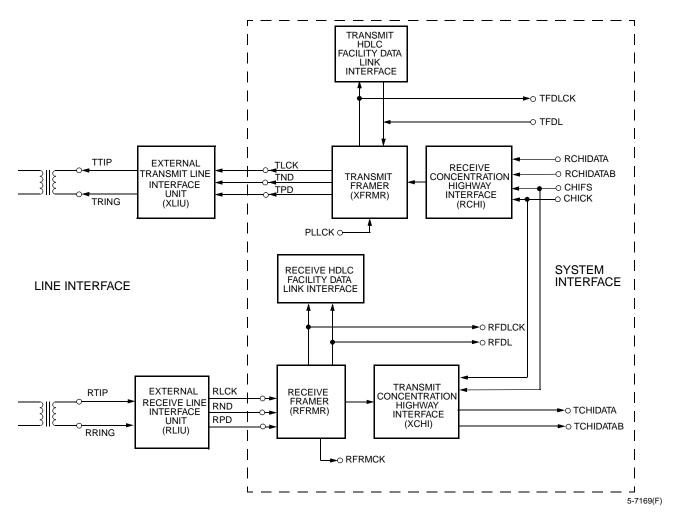

| Figure 1. TFRA08C13 Block Diagram (One of Eight Channels)                                     | 11       |

|-----------------------------------------------------------------------------------------------|----------|

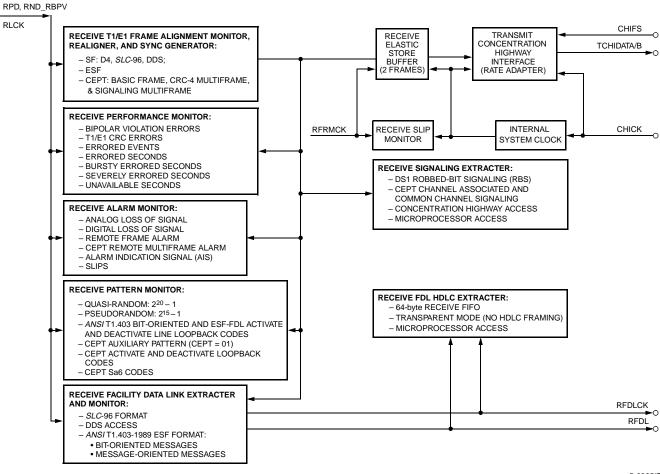

| Figure 2. TFRA08C13 Block Diagram: Receive Section (One of Eight Channels)                    | 13       |

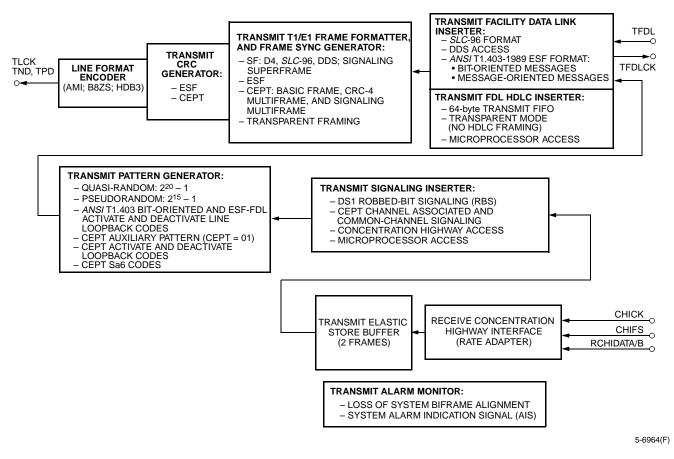

| Figure 3. TFRA08C13 Block Diagram: Transmit Section (One of Eight Channels)                   | 14       |

| Figure 4. Pin Assignment                                                                      |          |

| Figure 5. Block Diagram of Framer Line Interface                                              |          |

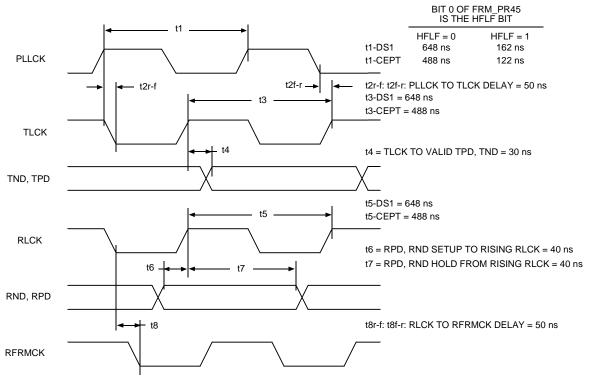

| Figure 6. Transmit Framer TLCK to TND, TPD and Receive Framer RND, RPD to RLCK Timing         | 30       |

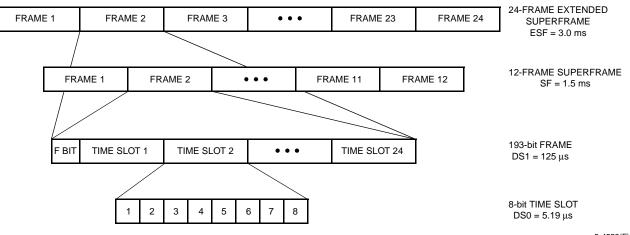

| Figure 7. T1 Frame Structure                                                                  |          |

| Figure 8. T1 Transparent Frame Structure                                                      |          |

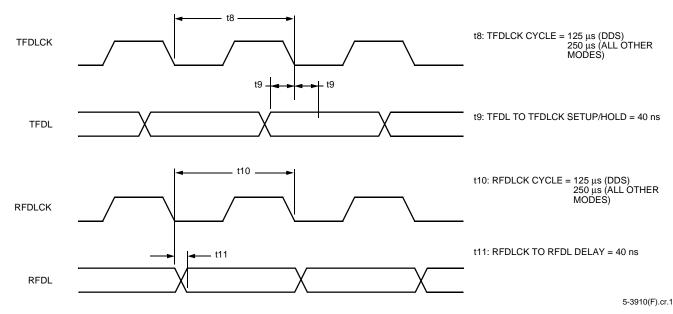

| Figure 9. T7633 Facility Data Link Access Timing of the Transmit and Receive Framer Sections  |          |

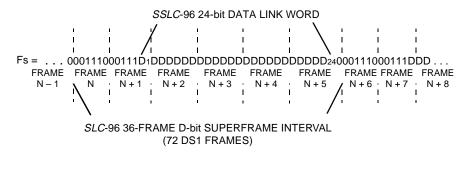

| Figure 10. SLC-96 Frame Format                                                                | 37       |

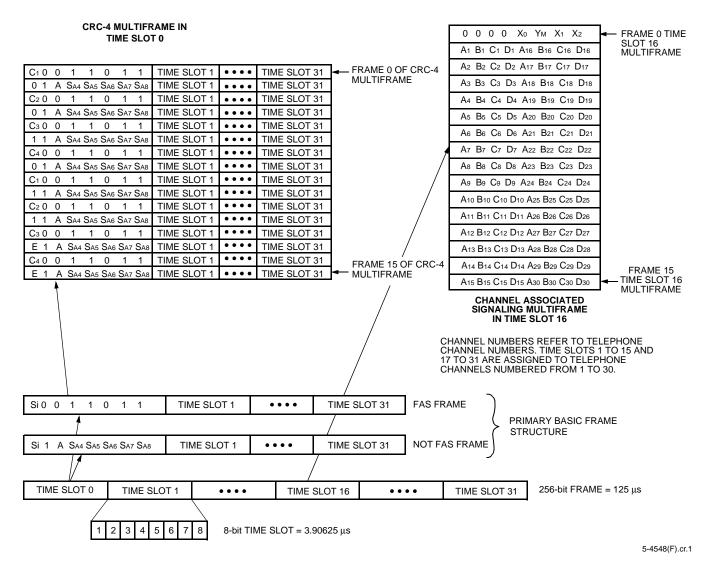

| Figure 11. ITU 2.048 Basic Frame, CRC-4 Multiframe, and Channel Associated                    |          |

| Signaling Multiframe Structures                                                               | 45       |

| Figure 12. CEPT Transparent Frame Structure                                                   |          |

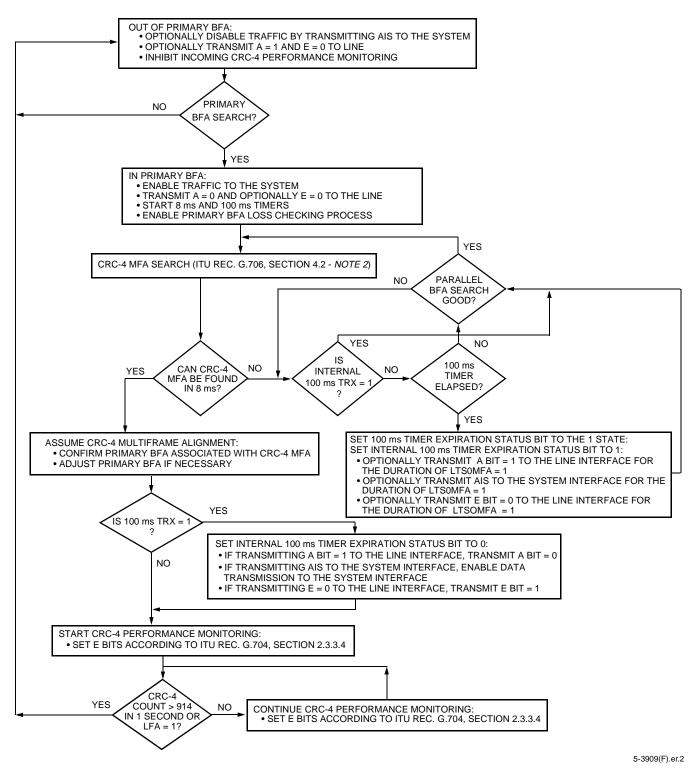

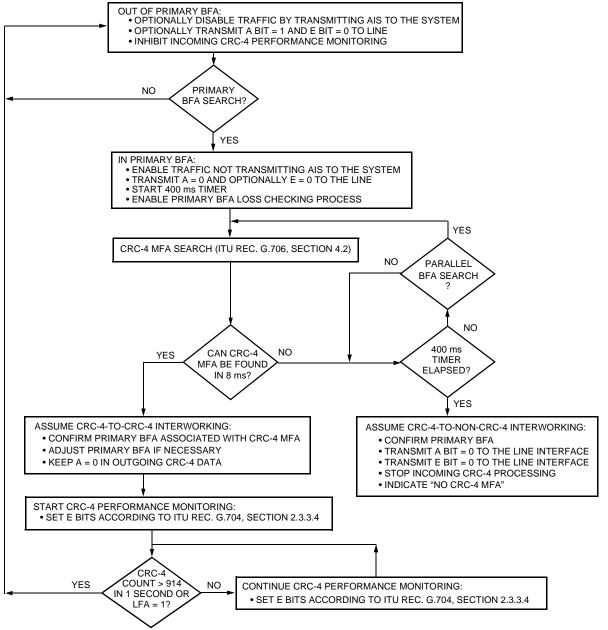

| Figure 13. Receive CRC-4 Multiframe Search Algorithm Using the 100 ms Internal Timer          | 52       |

| Figure 14. Receive CRC-4 Multiframe Search Algorithm for Automatic, CRC-4/Non-CRC-4 Equipment |          |

| Interworking as Defined by ITU (From ITU Rec. G.706, Annex B.2.2 - 1991)                      | 54       |

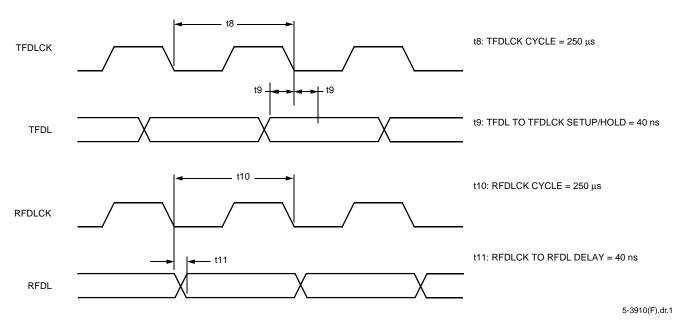

| Figure 15. Facility Data Link Access Timing of the Transmit and Receive                       |          |

| Framer Sections in the CEPT Mode                                                              |          |

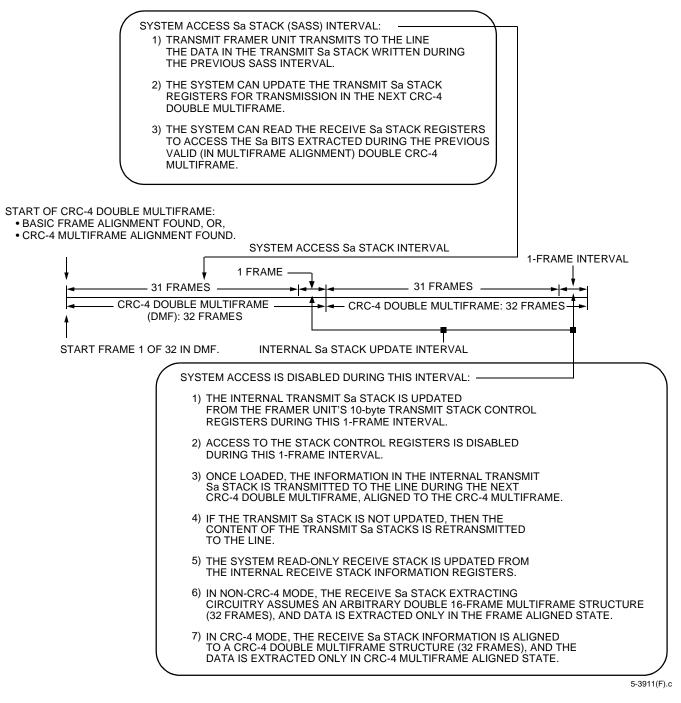

| Figure 16. Transmit and Receive Sa Stack Accessing Protocol                                   |          |

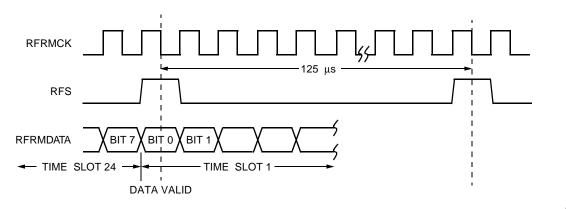

| Figure 17. Timing Specification for RFRMCK, RFRMDATA, and RFS in DS1 Mode                     |          |

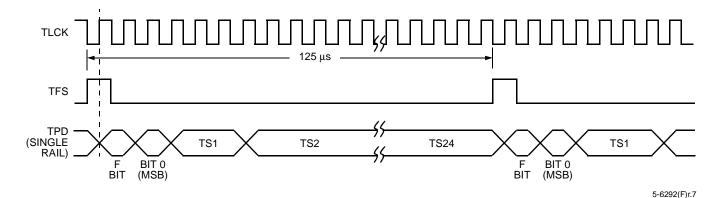

| Figure 18. Timing Specification for TFS, TLCK, and TPD in DS1 Mode                            |          |

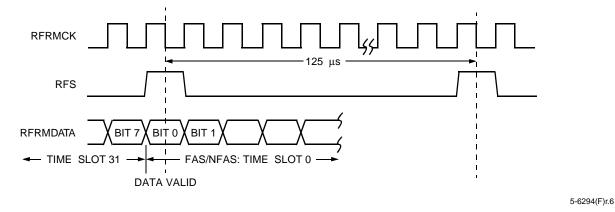

| Figure 19. Timing Specification for RFRMCK, RFRMDATA, and RFS in CEPT Mode                    |          |

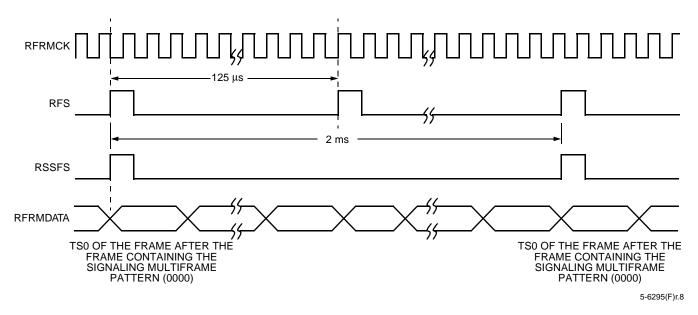

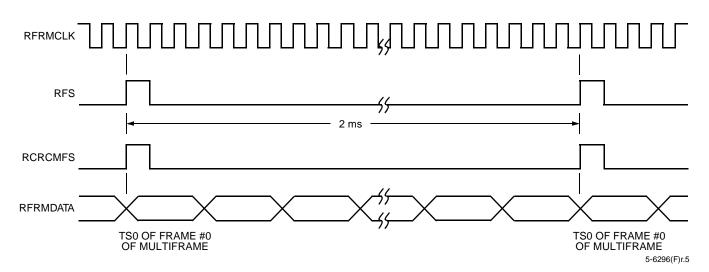

| Figure 20. Timing Specification for RFRMCK, RFRMDATA, RFS, and RSSFS in CEPT Mode             |          |

| Figure 21. Timing Specification for RCRCMFS in CEPT Mode                                      |          |

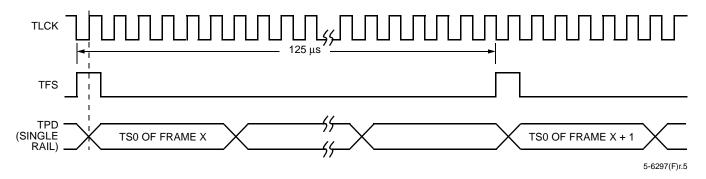

| Figure 22. Timing Specification for TFS, TLCK, and TPD in CEPT Mode                           |          |

| Figure 23. Timing Specification for TFS, TLCK, TPD, and TSSFS in CEPT Mode                    |          |

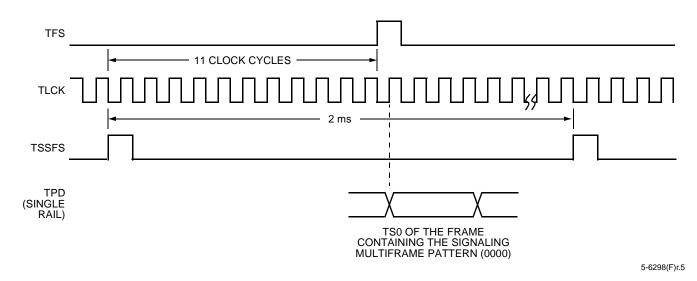

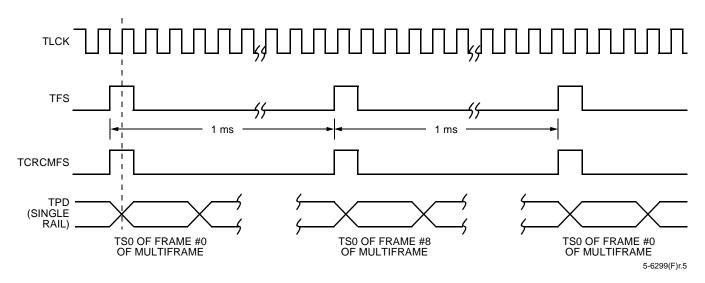

| Figure 24. Timing Specification for TFS, TLCK, TPD, and TCRCMFS in CEPT Mode                  |          |

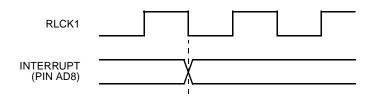

| Figure 25. Relation Between RLCK1 and Interrupt (Pin AD8)                                     |          |

|                                                                                               |          |

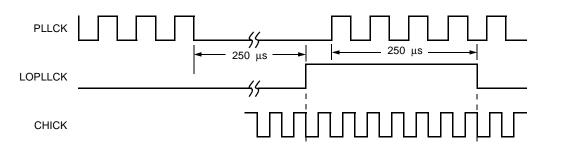

| Figure 26. Timing for Generation of LOPLLCK (Pin F25)                                         | 69       |

|                                                                                               | 69<br>72 |

#### **Figures**

#### Page

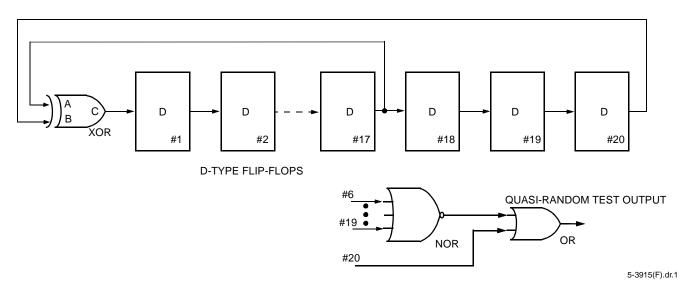

| Figure 29. 20-Stage Shift Register Used to Generate the Quasi-Random Signal                         | 78  |

|-----------------------------------------------------------------------------------------------------|-----|

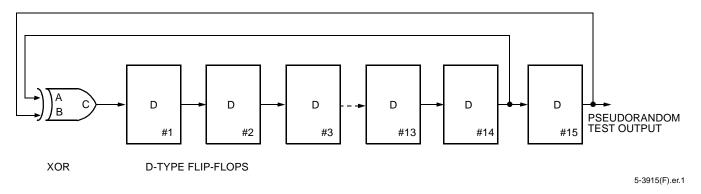

| Figure 30. 15-Stage Shift Register Used to Generate the Pseudorandom Signal                         | 79  |

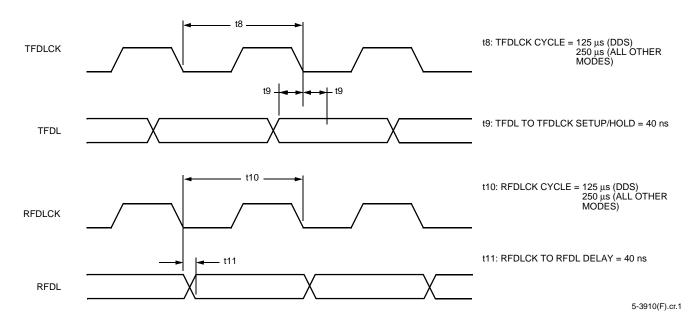

| Figure 31. TFRA08C13 Facility Data Link Access Timing of the Transmit and Receive Framer Sections   | 84  |

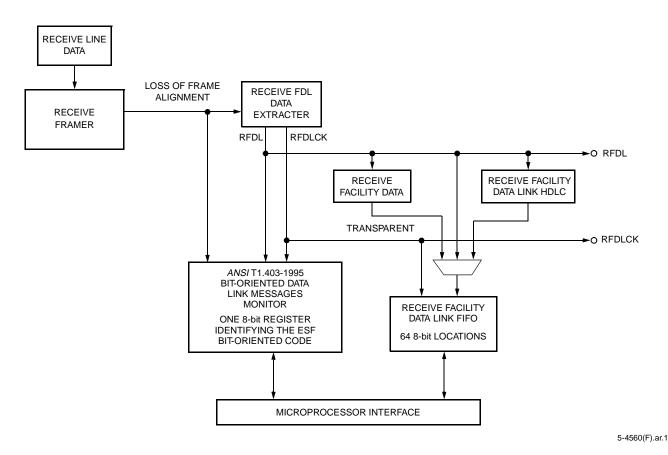

| Figure 32. Block Diagram for the Receive Facility Data Link Interface                               | 85  |

| Figure 33. Block Diagram for the Transmit Facility Data Link Interface                              | 90  |

| Figure 34. Local Loopback Mode                                                                      |     |

| Figure 35. Remote Loopback Mode                                                                     | 96  |

| Figure 36. TFRA08C13 Phase Detector Circuitry                                                       |     |

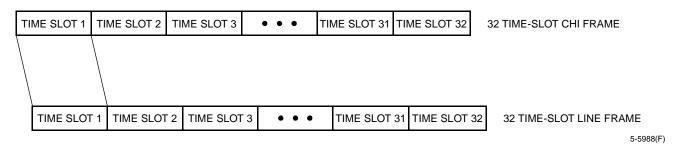

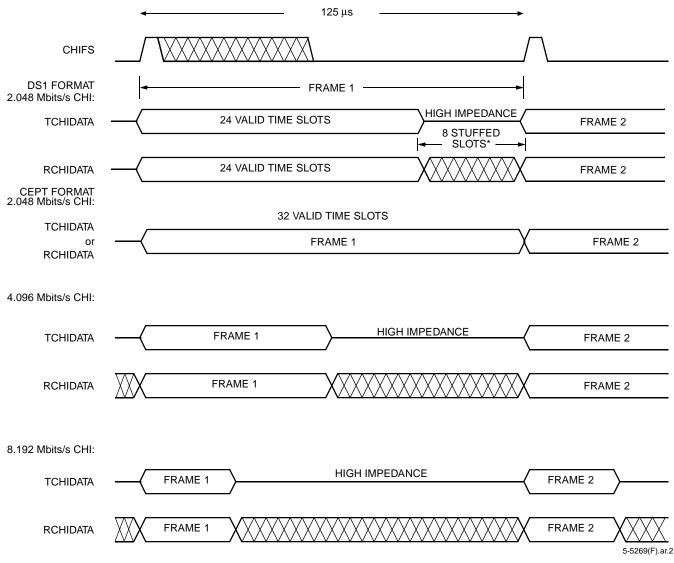

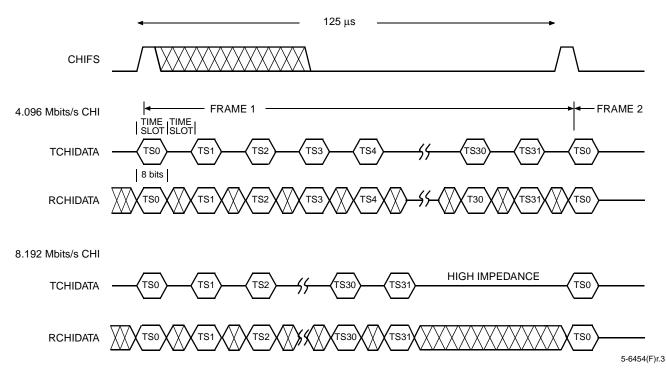

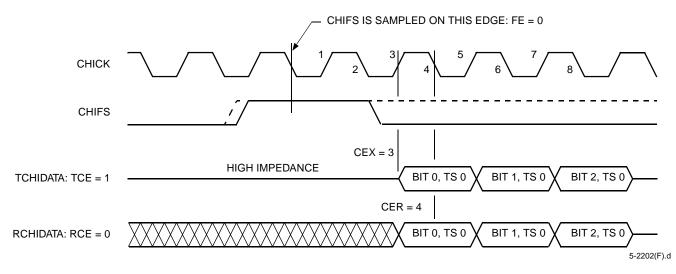

| Figure 37. Nominal Concentration Highway Interface Timing (for FRM_PR43 bit 0-bit 2 = 100 (Binary)) |     |

| Figure 38. CHIDTS Mode Concentration Highway Interface Timing                                       | 102 |

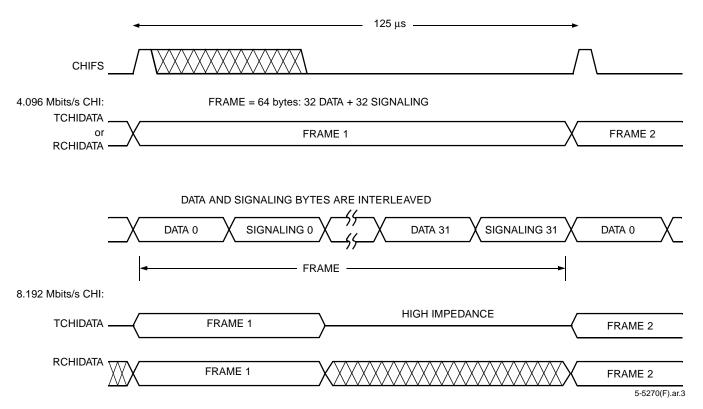

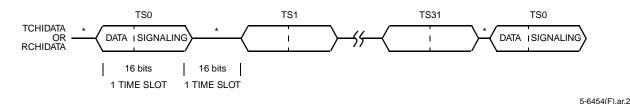

| Figure 39. Associated Signaling Mode Concentration Highway Interface Timing                         | 103 |

| Figure 40. CHI Timing with ASM and CHIDTS Enabled                                                   |     |

| Figure 41. TCHIDATA and RCHIDATA to CHICK Relationship with CMS = 0                                 |     |

| (CEX = 3 and CER = 4, Respectively)                                                                 | 104 |

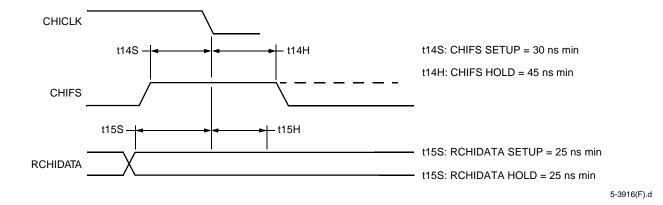

| Figure 42. Receive CHI (RCHIDATA) Timing                                                            | 105 |

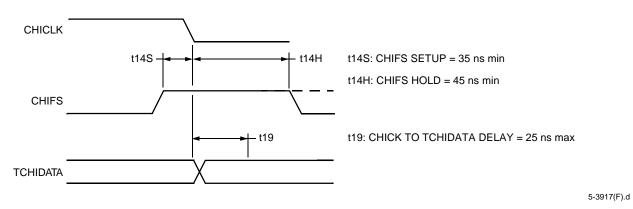

| Figure 43. Transmit CHI (TCHIDATA) Timing                                                           |     |

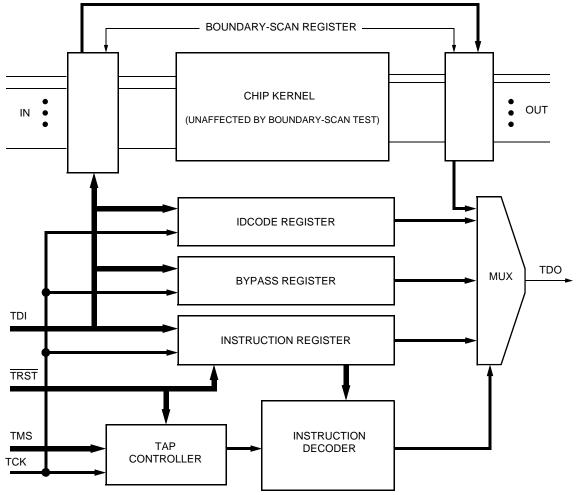

| Figure 44. Block Diagram of the TFRA08C13's Boundary-Scan Test Logic                                |     |

| Figure 45. BS TAP Controller State Diagram                                                          |     |

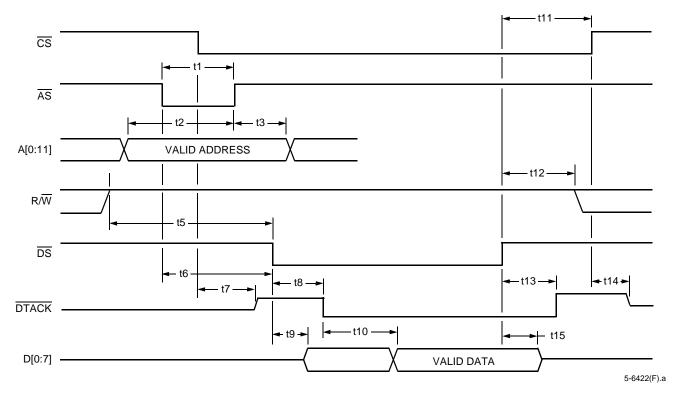

| Figure 46. Mode 1—Read Cycle Timing (MPMODE = 0)                                                    |     |

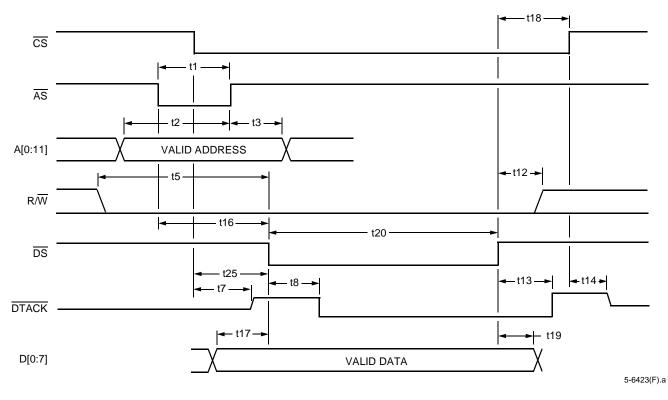

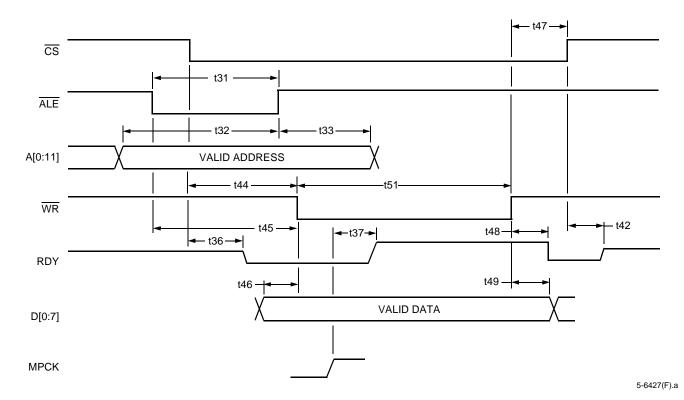

| Figure 47. Mode 1—Write Cycle Timing (MPMODE = 0)                                                   | 116 |

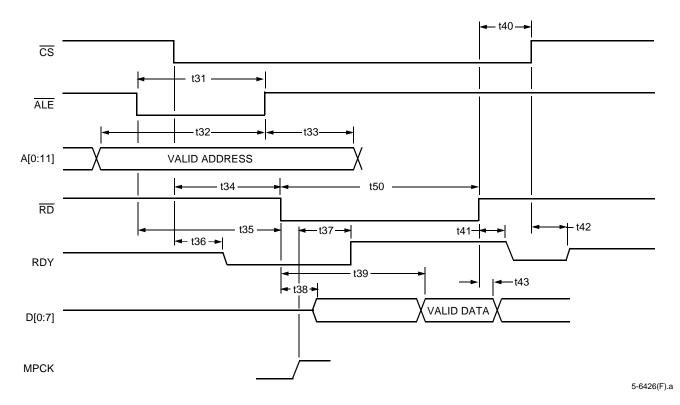

| Figure 48. Mode 3—Read Cycle Timing (MPMODE = 1)                                                    |     |

| Figure 49. Mode 3—Write Cycle Timing (MPMODE = 1)                                                   |     |

|                                                                                                     |     |

#### Tables

#### Table 14. T1 Loss of Frame Alignment Criteria ......41 Table 16. Robbed-Bit Signaling Options......43

#### Tables

| Table 25. | Associated Signaling Mode CHI 2-Byte Time-Slot Format for CEPT                    | 62  |

|-----------|-----------------------------------------------------------------------------------|-----|

| Table 26. | Red Alarm or Loss of Frame Alignment Conditions                                   | 68  |

|           | Remote Frame Alarm Conditions                                                     |     |

|           | Alarm Indication Signal Conditions                                                |     |

|           | Sa6 Bit Coding Recognized by the Receive Framer.                                  |     |

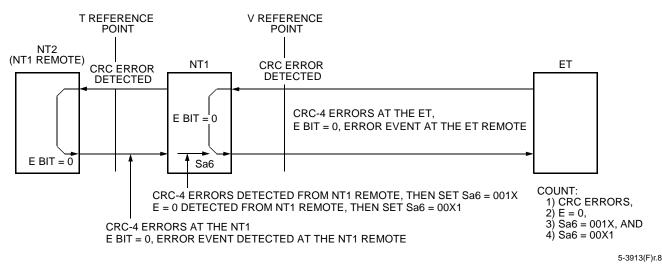

| Table 30. | Sa6 Bit Coding of NT1 Interface Events Recognized by the Receive Framer           | 71  |

|           | AUXP Synchronization and Clear Synchronization Process                            |     |

| Table 32. | Event Counters Definition                                                         | 73  |

| Table 33. | Summary of the Deactivation of SSTSSLB and SSTSLLB Modes as a                     |     |

| Function  | n of Activating the Primary Loopback Modes                                        | 76  |

| Table 34. | Register FRM_PR69 Test Patterns                                                   | 79  |

| Table 35. | Register FRM_PR70 Test Patterns                                                   | 80  |

| Table 36. | Automatic Enable Commands                                                         | 82  |

| Table 37. | On-Demand Commands                                                                | 83  |

| Table 38. | Receive ANSI Code                                                                 | 86  |

| Table 39. | Performance Report Message Structure                                              | 86  |

| Table 40. | FDL Performance Report Message Field Definition                                   | 87  |

|           | Octet Contents and Definition                                                     |     |

| Table 42. | Receive Status of Frame Byte                                                      | 88  |

| Table 43. | HDLC Frame Format                                                                 | 91  |

| Table 44. | Receiver Operation in Transparent Mode                                            | 94  |

|           | Summary of the TFRA08C13's Concentration Highway Interface Parameters             |     |

| Table 46. | Programming Values for TOFF[2:0] and ROFF[2:0] when CMS = 0                       | 104 |

|           | TAP Controller States in the Data Register Branch                                 |     |

|           | TAP Controller States in the Instruction Register Branch                          |     |

|           | TFRA08C13's Boundary-Scan Instructions                                            |     |

| Table 50. | IDCODE Register                                                                   | 110 |

|           | Microprocessor Configuration Modes                                                |     |

|           | Mode [1 and 3] Microprocessor Pin Definitions                                     |     |

|           | Microprocessor Input Clock Specifications                                         |     |

|           | TFRA08C13 Register Address Map                                                    |     |

|           | Microprocessor Interface I/O Timing Specifications                                |     |

|           | Status Register and Corresponding Interrupt Enable Register for Functional Blocks |     |

| Table 57. | Asserted Value and Deasserted State for GREG4 Bit 4 and Bit 6 Logic Combinations  | 118 |

|           | Register Summary                                                                  |     |

|           | Global Register Set (0x000-0x009)                                                 |     |

|           | Framer Block Interrupt Status Register (GREG0) (000)                              |     |

|           | Framer Block Interrupt Enable Register (GREG1) (001)                              |     |

|           | FDL Block Interrupt Status Register (GREG2) (002)                                 |     |

|           | FDL Block Interrupt Enable Register (GREG3) (003)                                 |     |

| Table 64. | Global Control Register (GREG4) (004)                                             | 125 |

| Table 65. | Device ID and Version Registers (GREG5—GREG7) (005—007)                           | 125 |

|           | Global Control Register (GREG8) (008)                                             |     |

|           | Global PLLCK Control Register (GREG9) (009)                                       |     |

|           | Framer Status and Control Blocks Address Range (Hexadecimal)                      |     |

|           | Interrupt Status Register (FRM_SR0) (Y00)                                         |     |

| Table 70. | Facility Alarm Condition Register (FRM_SR1) (Y01)                                 | 129 |

|           | Remote End Alarm Register (FRM_SR2) (Y02)                                         |     |

| Table 72. | Facility Errored Event Register-1 (FRM_SR3) (Y03)                                 | 131 |

### Tables

## Page

|                                                                                                                   | _   |

|-------------------------------------------------------------------------------------------------------------------|-----|

| Table 73. Facility Event Register-2 (FRM_SR4) (Y04)                                                               |     |

| Table 74. Exchange Termination and Exchange Termination Remote                                                    |     |

| End Interface Status Register (FRM_SR5) (Y05)                                                                     |     |

| Table 75. Network Termination and Network Termination Remote End                                                  |     |

| Interface Status Register (FRM_SR6) (Y06)                                                                         | 134 |

| Table 76. Facility Event Register (FRM_SR7) (Y07)                                                                 |     |

| Table 77. Bipolar Violation Counter Registers (FRM_SR8—FRM_SR9) (Y08—Y09)                                         |     |

| Table 78. Framing Bit Error Counter Registers (FRM_SR10—FRM_SR11) (Y0A—Y0B)                                       |     |

| Table 79. CRC Error Counter Registers (FRM_SR12—FRM_SR13) (Y0C—Y0D)                                               |     |

| Table 80. E-Bit Counter Registers (FRM_SR14—FRM_SR15) (Y0E—Y0F)                                                   |     |

| Table 81. CRC-4 Errors at NT1 from NT2 Counter Registers (FRM_SR16—FRM_SR17) (Y10—Y11)                            | 136 |

| Table 82. E Bit at NT1 from NT2 Counter (FRM_SR18—FRM_SR19) (Y12—Y13)                                             | 136 |

| Table 83. ET Errored Seconds Counter (FRM_SR20—FRM_SR21) (Y14—Y15)                                                | 137 |

| Table 84. ET Bursty Errored Seconds Counter (FRM_SR22—FRM_SR23) (Y16—Y17)                                         | 137 |

| Table 85. ET Severely Errored Seconds Counter (FRM_SR24—FRM_SR25) (Y18—Y19)                                       | 137 |

| Table 86. ET Unavailable Seconds Counter (FRM_SR26—FRM_SR27) (Y1A—Y1B)                                            | 137 |

| Table 87. ET-RE Errored Seconds Counter (FRM_SR28—FRM_SR29) (Y1C—Y1D)                                             | 137 |

| Table 88. ET-RE Bursty Errored Seconds Counter (FRM_SR30—FRM_SR31) (Y1E—Y1F)                                      |     |

| Table 89. ET-RE Severely Errored Seconds Counter (FRM_SR32—FRM_SR33) (Y20—Y21)                                    |     |

| Table 90. ET-RE Unavailable Seconds Counter (FRM_SR34—FRM_SR35) (Y22—Y23)                                         |     |

| Table 91. NT1 Errored Seconds Counter (FRM_SR36—FRM_SR37) (Y24—Y25)                                               |     |

| Table 92. NT1 Bursty Errored Seconds Counter (FRM_SR38—FRM_SR39) (Y26—Y27)                                        |     |

| Table 93. NT1 Severely Errored Seconds Counter (FRM_SR40—FRM_SR41) (Y28—Y29)                                      |     |

| Table 94. NT1 Unavailable Seconds Counter (FRM_SR42—FRM_SR43) (Y2A—Y2B)                                           |     |

| Table 95. NT1-RE Errored Seconds Counter (FRM_SR44—FRM_SR45) (Y2C—Y2D)                                            |     |

| Table 96. NT1-RE Bursty Errored Seconds Counter (FRM_SR46—FRM_SR47) (Y2E—Y2F)                                     |     |

| Table 97. NT1-RE Severely Errored Seconds Counter (FRM_SR48—FRM_SR49) (Y30—Y31)                                   |     |

| Table 98. NT1-RE Unavailable Seconds Counter (FRM_SR50—FRM_SR51) (Y32—Y33)                                        |     |

| Table 99. Receive NOT-FAS TS0 Register (FRM_SR52) (Y34)                                                           |     |

| Table 100. Receive Sa Register (FRM_SR53) (Y35)                                                                   |     |

| Table 101. SLC-96 FDL Receive Stack (FRM_SR54—FRM_SR63) (Y36—Y3F)                                                 |     |

| Table 102. CEPT Sa Receive Stack (FRM_SR54—FRM_SR63) (Y36—Y3F)                                                    |     |

| Table 103. Transmit Framer ANSI Performance Report Message Status Register Structure                              |     |

| Table 104. Received Signaling Registers: DS1 Format (FRM_RSR0—FRM_RSR23) (Y40—Y58)                                |     |

| Table 105. Receive Signaling Registers: CEPT Format (FRM_RSR0—FRM_RSR31) (Y40—Y5F)                                |     |

| Table 106. Summary of Interrupt Group Enable Registers (FRM_PR0—FRM_PR7) (Y60—Y67)                                |     |

| Table 107. Primary Interrupt Group Enable Register (FRM_PR0) (Y60)                                                |     |

| Table 108. Interrupt Enable Register (FRM_PR1) (Y61)                                                              |     |

| Table 109. Interrupt Enable Register (FRM_PR2) (Y62)                                                              |     |

| Table 110. Interrupt Enable Register (FRM_PR3) (Y63)                                                              |     |

| Table 111. Interrupt Enable Register (FRM_PR4) (Y64)         Table 112. Interrupt Enable Register (FRM_PR5) (Y65) |     |

| Table 112. Interrupt Enable Register (FRM_PR5) (Y65)         Table 113. Interrupt Enable Register (FRM_PR5) (Y66) |     |

| Table 113. Interrupt Enable Register (FRM_PR6) (Y66)         Table 114. Interrupt Enable Register (FRM_PR7) (Y67) |     |

| Table 114. Interrupt Enable Register (FRM_PR7) (Y67)         Table 115. Framer Mode Bits Decoding (FRM_PR8) (Y68) |     |

| Table 115. Framer Mode Bits Decoding (FRM_PR8) (Y68)<br>Table 116. Line Code Option Bits Decoding (FRM_PR8) (Y68) |     |

| Table 116. Line Code Option Bits Decoding (FRM_PR8) (Y68)<br>Table 117. CRC Option Bits Decoding (FRM_PR9) (Y69)  |     |

| Table 117. CRC Option Bits Decoding (FRM_PR9) (Y69)<br>Table 118. Alarm Filter Register (FRM_PR10) (Y6A)          |     |

| Table 118. Alarm Filter Register (FRM_PR10) (Y6A)<br>Table 119. Errored Event Threshold Definition                |     |

| Table 119. Errored Event Threshold Delinition                                                                     |     |

Lucent Technologies Inc.

#### Tables

| Table 121. Severely Errored Second Threshold Registers (FRM_PR12—FRM_PR13) (Y6C—Y6D)             | 146 |

|--------------------------------------------------------------------------------------------------|-----|

| Table 121. Severely Enoted Second Theshold Registers (FRM_FR12—FRM_FR13) (16C—16D)               |     |

| Table 122. ETT Enoted Event Enable Register (FRM_FR14) (T6E)                                     |     |

| Table 123. ETT Remote End Endle Register (FRM_PR16) (Y70)                                        |     |

| Table 125. NT1 Remote End Errored Event Enable Register (FRM_PR17—FRM_PR18) (Y71—Y72)            |     |

| Table 125. NTT Remote End Ended Event Enable Registers (FRM_FRT/_FRM_FRT/) (TTT_T/2)             |     |

| Table 120. Automatic AIS to the System and Automatic Loopback Enable Register (FRM_PR19) (173)   |     |

| Table 128. Transmit Test Pattern to the Line Enable Register (FRM_PR20) (Y74)                    |     |

| Table 129. Framer FDL Control Command Register (FRM_PR21) (Y75)                                  |     |

| Table 130. Framer Transmit Line Idle Code Register (FRM_PR21) (175)                              |     |

|                                                                                                  |     |

| Table 131. Framer System Stuffed Time-Slot Code Register (FRM_PR23) (Y77)                        | 149 |

| Table 132. Primary Time-Slot Loopback Address Register (FRM_PR24) (Y78)                          |     |

| Table 133. Loopback Decoding of Bits LBC[2:0] in FRM_PR24, Bits 7—5                              |     |

| Table 134. Secondary Time-Slot Loopback Address Register (FRM_PR25) (Y79)                        |     |

| Table 135. Loopback Decoding of Bits LBC[1:0] in FRM_PR25, Bits 6—5                              |     |

| Table 136. Framer Reset and Transparent Mode Control Register (FRM_PR26) (Y7A)                   | 152 |

| Table 137. Transmission of Remote Frame Alarm and CEPT Automatic                                 | 450 |

| Transmission of A Bit = 1 Control Register (FRM_PR27) (Y7B)                                      |     |

| Table 138. CEPT Automatic Transmission of E Bit = 0 Control Register (FRM_PR28) (Y7C)            | 154 |

| Table 139. Sa4—Sa8 Source Register (FRM_PR29) (Y7D)                                              |     |

| Table 140. Sa Bits Source Control for Bit 5—Bit 7 in FRM_PR29                                    |     |

| Table 141. Sa4—Sa8 Control Register (FRM_PR30) (Y7E)                                             | 155 |

| Table 142. Sa Transmit Stack (FRM_PR31—FRM_PR40) (Y7F—Y88)                                       | 156 |

| Table 143. SLC-96 Transmit Stack (FRM_PR31—FRM_PR40) (Y7F—Y88)                                   |     |

| Table 144. Transmit SLC-96 FDL Format                                                            | 156 |

| Table 145. CEPT Time Slot 16 X-Bit Remote Multiframe Alarm and AIS                               |     |

| Control Register (FRM_PR41) (Y89)                                                                |     |

| Table 146. Framer Exercise Register (FRM_PR42) (Y8A)                                             |     |

| Table 147. Framer Exercises, FRM_PR42 Bit 5—Bit 0 (Y8A)                                          |     |

| Table 148. DS1 System Interface Control and CEPT FDL Source Control Register (FRM_PR43) (Y8B)    |     |

| Table 149. Signaling Mode Register (FRM_PR44) (Y8C)                                              |     |

| Table 150. CHI Common Control Register (FRM_PR45) (Y8D)                                          |     |

| Table 151. CHI Common Control Register (FRM_PR46) (Y8E)                                          |     |

| Table 152. CHI Transmit Control Register (FRM_PR47) (Y8F)                                        |     |

| Table 153. CHI Receive Control Register (FRM_PR48) (Y90)                                         |     |

| Table 154. CHI Transmit Time-Slot Enable Registers (FRM_PR49—FRM_PR52) (Y91—Y94)                 |     |

| Table 155. CHI Receive Time-Slot Enable Registers (FRM_PR53—FRM_PR56) (Y95—Y98)                  | 163 |

| Table 156. CHI Transmit Highway Select Registers (FRM_PR57—FRM_PR60) (Y99—Y9C)                   | 163 |

| Table 157. CHI Receive Highway Select Registers (FRM_PR61—FRM_PR64) (Y9D—YA0)                    |     |

| Table 158. CHI Transmit Control Register (FRM_PR65) (YA1)                                        | 164 |

| Table 159. CHI Receive Control Register (FRM_PR66) (YA2)                                         | 164 |

| Table 160. Auxiliary Pattern Generator Control Register (FRM_PR69) (YA5)                         | 165 |

| Table 161. Pattern Detector Control Register (FRM_PR70) (YA6)                                    |     |

| Table 162. Transmit Signaling Registers: DS1 Format (FRM_TSR0—FRM_TSR23) (YE0—YF7)               |     |

| Table 163. Transmit Signaling Registers: CEPT Format (FRM_TSR0—FRM_TSR31) (YE0—YFF)              |     |

| Table 164. FDL Register Set ((A00—A0E); (A20—A2E); (B00—B0E); (B20—B2E)                          |     |

| (C00—C0E); (C20—C2E); (D00—D0E); (D20—D2E))                                                      | 168 |

| Table 165. FDL Configuration Control Register (FDL_PR0) (A00; A20; B00; B20; C00; C20; D00; D20) |     |

| Table 166. FDL Control Register (FDL_PR1) (A01; A21; B01; B21; C01; C21; D01; D21)               |     |

| $\sim$                            |     |

Page

# Table of Contents (continued)

### Tables

| Table 167. FDL Interrupt Mask Control Register (FDL_PR2) (A02; A22; B02; B22; C02; C22; D02; D22)         | 170 |

|-----------------------------------------------------------------------------------------------------------|-----|

| Table 168. FDL Transmitter Configuration Control Register (FDL_PR3)                                       |     |

| (A03; A23; B03; B23; C03; C23; D03; D23)                                                                  | 171 |

| Table 169. FDL Transmitter FIFO Register (FDL_PR4) (A04; A24; B04; B24; C04; C24; D04; D24)               | 171 |

| Table 170. FDL Transmitter Idle Character Mask Register (FDL_PR5)                                         |     |

| (A05; A25; B05; B25; C05; C25; D05; D25)                                                                  | 171 |

| Table 171. FDL Receiver Interrupt Level Control Register (FDL_PR6)                                        |     |

| (A06; A26; B06; B26; C06; C26; D06; D26)                                                                  | 172 |

| Table 172. FDL Register FDL_PR7                                                                           | 172 |

| <br>Table 173. FDL Receiver Match Character Register (FDL_PR8) (A08; A28; B08; B28; C08; C28; D08; D28)   |     |

| Table 174. FDL Transparent Control Register (FDL_PR9) (A09; A29; B09; B29; C09; C29; D09; D29)            |     |

| Table 175. FDL Transmit ANS/ ESF Bit Codes (FDL_PR10) (A0A; A2A; B0A; B2A; C0A; C2A; D0A; D2A)            |     |

| Table 176. FDL Interrupt Status Register (Clear on Read) (FDL_SR0)                                        |     |

| (A0B; A2B; B0B; B2B; C0B; C2B; D0B; D2B)                                                                  | 174 |

| Table 177. FDL Transmitter Status Register (FDL_SR1) (A0C; A2C; B0C; B2C; C0C; C2C; D0C; D2C)             |     |

| Table 178. FDL Receiver Status Register (FDL_SR2) (A0D; A2D; B0D; B2D; C0D; C2D; D0D; D2D)                |     |

| Table 179. Receive ANSI FDL Status Register (FDL_SR3) (A0E; A2E; B0E; B2E; C0E; C2E; D0E; D2E)            |     |

| Table 180. FDL Receiver FIFO Register (FDL_SR4) (A07; A27; B07; B27; C07; C27; D07; D27)                  |     |

| Table 181. Global Register Set                                                                            |     |

| Table 182. Framer Unit Status Register Map                                                                | 177 |

| Table 183. Receive Signaling Registers Map                                                                | 179 |

| Table 184. Framer Unit Parameter Register Map                                                             |     |

| Table 185. Transmit Signaling Registers Map                                                               |     |

| Table 186. Facility Data Link Register Map                                                                |     |

| Table 187. ESD Threshold Voltage                                                                          |     |

| Table 188. Logic Interface Characteristics (TA = $-40$ °C to $+85$ °C, VDD = $3.3$ V $\pm 5\%$ , Vss = 0) |     |

| -                                                                                                         |     |

# **Feature Descriptions**

## T1/E1 Framer Feature Descriptions

- Framing formats:

- Compliant with T1 standards ANSI T1.231 (1993), AT&T TR54016, AT&T TR62411 (1998).

- Unframed, transparent transmission in T1 and E1 formats.

- DS1 extended superframe (ESF).

- DS1 superframe (SF): D4; SLC-96; T1DM DDS; T1DM DDS with FDL access.

- DS1 independent transmit and receive framing modes when using the ESF and D4 formats.

- Compliant with ITU CEPT framing recommendation:

- 1. G.704 and G.706 basic frame format.

- 2. G.704 Section 2.3.3.4 and G.706 Section 4.2: CRC-4 multiframe search algorithm.

- 3. G.706 Annex B: CRC-4 multiframe search algorithm with 400 ms timer for interworking of CRC-4 and non-CRC-4 equipment.

- 4. G.706 Section 4.3.2 Note 2: monitoring of 915 CRC-4 checksum errors for loss of frame state.

- Framer line codes:

- DS1: alternate mark inversion (AMI); binary eight zero code suppression (B8ZS); per-channel zero code suppression; decoding bipolar violation monitor; monitoring of eight or fifteen bit intervals without positive or negative pulses error indication.

- DS1 independent transmit and receive path line code formats when using AMI/ZCS and B8ZS coding.

- ITU-CEPT: AMI; high-density bipolar 3 (HDB3) encoding and decoding bipolar violation monitoring, monitoring of four bit intervals without positive or negative pulses error indication.

- Single-rail option.

- Signaling:

- DS1: extended superframe 2-state, 4-state, and 16-state per-channel robbed bit.

- DS1: D4 superframe 2-state and 4-state perchannel robbed bit.

- DS1: SLC-96 superframe 2-state, 4-state, 9-state, and 16-state per-channel robbed bit.

- DS1: channel-24 message-oriented signaling.

- ITU CEPT: channel associated signaling (CAS).

- Transparent (all data channels).

- Alarm reporting, performance monitoring, and maintenance:

- ANSI T1.403-1995, AT&T TR 54016, and ITU G.826 standard error checking.

- Error and status counters:

- 1. Bipolar violations.

- 2. Errored frame alignment signals.

- 3. Errored CRC checksum block.

- 4. CEPT: received E bit = 0.

- 5. Errored, severely errored, and unavailable seconds.

- Selectable errored event monitoring for errored and severely errored seconds processing with programmable thresholds for errored and severely errored second monitoring.

- CEPT: Selectable automatic transmission of E bit to the line.

- CEPT: Sa6 coded remote end CRC-4 error E bit = 0 events.

- Programmable automatic and on-demand alarm transmission:

- 1. Automatic transmission of remote frame alarm to the line while in loss of frame alignment state.

- 2. Automatic transmission of alarm indication signal (AIS) to the system while in loss of frame alignment state.

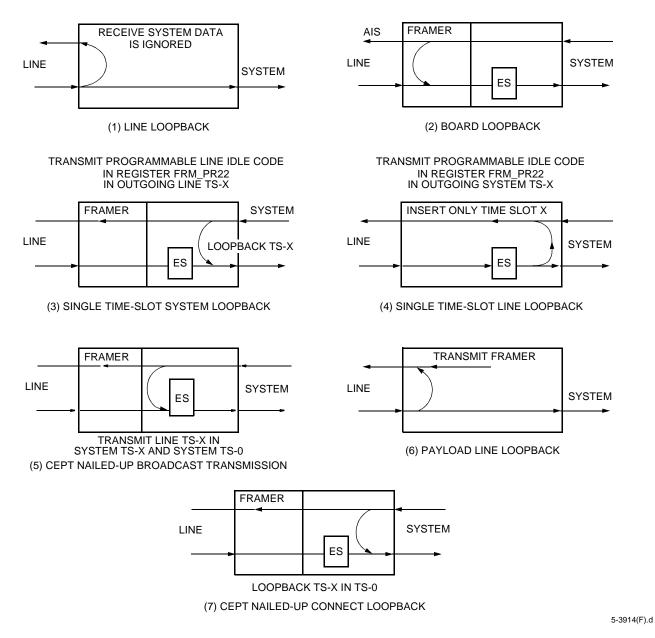

- Multiple loopback modes.

- Optional automatic line and payload loopback activate and deactivate modes.

- CEPT nailed-up connect loopback and CEPT nailed-up broadcast transmission TS-X in TS-0 transmit mode.

- Selectable test patterns for line transmission.

- Detection of framed and unframed pseudorandom and quasi-random test patterns.

- Programmable squelch and idle codes.

- System interface:

- Autonomous transmit and receive system interfaces.

- Independent transmit and receive frame synchronization input signals.

- Independent transmit and receive system interface clock.

- 2.048 Mbits/s, 2.048 MHz concentration highway interface (CHI) default mode.

- Optional 4.096 Mbits/s and 8.192 Mbits/s data rates.

- Optional 4.096 MHz and 8.192 MHz frequency system clock.

- Programmable clock edge for latching frame synchronization signals.

- Programmable clock edge for latching transmit and receive data.

- Programmable bit and byte offset.

- Programmable CHI master mode for the generation of the transmit CHI FS from internal logic with timing derived from the receive line clock signal.

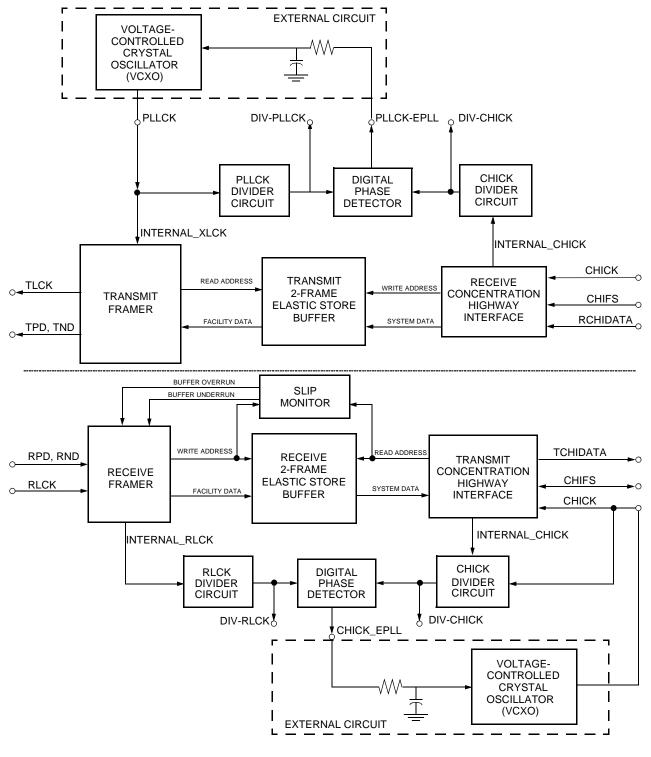

- Digital phase comparator for clock generation in the receive and transmit paths.

# **Functional Description**

**Note:** The *Concentration Highway Interface Specification*, Lucent Technologies Microelectronics Group November 1990 (DS90-124SMOS) defines the **transmit** path as output to the system interface, and the **receive** path as input from the system interface. This document is consistent with that definition.

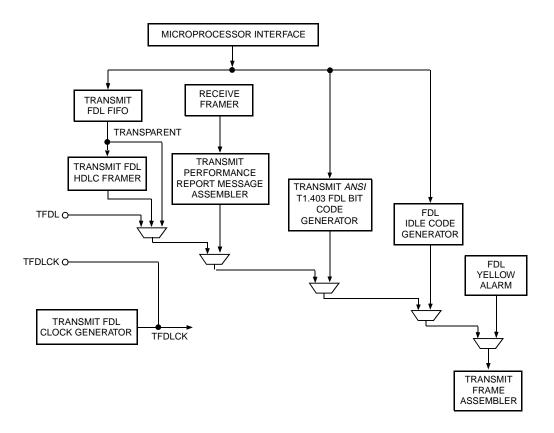

Figure 1. TFRA08C13 Block Diagram (One of Eight Channels)

Lucent Technologies Inc.

# Functional Description (continued)

The Lucent Technologies Microelectronics Group TFRA08C13 OCTAL T1/E1 Framer provides eight complete T1/E1 interfaces each consisting of a fully integrated, full-featured, primary rate framer with an HDLC formatter for facility data link access. The TFRA08C13 provides glueless interconnection from a T1 or E1 analog line interface to devices interfacing to its CHI; for example, the Lucent T7270 Time-Slot Interchanger or T7115A Synchronous Protocol Data Formatter.

The line codes supported in the framer unit include AMI, T1 B8ZS, per-channel T1 zero code suppression, and ITU-CEPT HDB3.

The framer supports DS1 superframe (D4, T1DM, *SLC*-96) and extended superframe (ESF) formats. The framer also supports, ITU-CEPT-E1 basic frame, ITU-CEPT-E1 time slot 0 multiframe, and time slot 16 multiframe formats.

The receive framer monitors the following alarms: loss of receive clock, loss of frame, alarm indication signal (AIS), remote frame alarms, and remote multiframe alarms. These alarms are detected as defined by the appropriate *ANSI*, AT&T, and ITU standards. It is recommended that the LIU/Framer interface be placed in dual rail mode, which allows the framers error/event detector to detect and report code and BPV errors.

Performance monitoring as specified by AT&T, *ANSI*, and ITU is provided through counters monitoring bipolar violation, frame bit errors, CRC errors, errored events, errored seconds, bursty errored seconds, severely errored seconds, and unavailable seconds.

In-band loopback activation and deactivation codes can be transmitted to the line via the payload or the facility data link. In-band loopback activation and deactivation codes in the payload or the facility data link are detected.

System, payload, and line loopbacks are programmable.

The default system interface is a 2.048 Mbits/s data and 2.048 MHz clock CHI serial bus. This CHI interface consists of independent transmit and receive paths. The CHI interface can be reconfigured into several modes: a 2.048 Mbits/s data interface and 4.096 MHz clock interface, a 4.096 Mbits/s data interface and 4.096 MHz clock interface, a 4.096 Mbits/s data interface and 8.192 MHz clock interface, a 8.192 Mbits/s data interface and 8.192 MHz clock interface, and 8.192 Mbits/s data interface.

The signaling formats supported are T1 per-channel robbed-bit signaling (RBS), channel-24 message-oriented signaling (MOS), and ITU-CEPT-E1 channelassociated signaling (CAS). In the T1, RBS mode voice and data channels are programmable. The entire payload can be forced into a data-only (no signaling channels) mode, i.e., transparent mode by programming one control bit. Signaling access can be through the on-chip signaling registers or the system CHI port in the associated signaling mode. Data and its associated signaling information can be accessed through the CHI in either DS1 or CEPT-E1 modes.

Extraction and insertion of the facility data link in ESF, T1DM, *SLC*-96, or CEPT-E1 modes are provided through a four-port serial interface or through a microprocessor-accessed, 64-byte FIFO either with HDLC formatting or transparently. In *SLC*-96 or CEPT-E1 frame formats, a facility data link (FDL) stack (registers in the framer section) is provided for FDL access. The bit-oriented ESF data-link messages defined in *ANSI* T1.403-1995 are monitored by the receive framer's facility data link unit. The transmit framer's facility data link unit overrides the XFDL-FIFO for the transmission of the bit-oriented ESF data-link messages defined in *ANSI* T1.403-1995.

The receive framer includes a two-frame (64-bytes) elastic store buffer for jitter attenuation that performs controlled slips and provides an indication of slip direction. This buffer can be programmed to operate as a function of the receive line clock and can be reduced to one-frame (32-bytes) in length.

## Functional Description (continued)

Accessing internal registers is done via the demultiplexed address and data bus microprocessor interface using either the *Intel* 80188 (or 80X88) interface protocol with independent read and write signals or the *Motorola* MC680X0 or M68360 interface protocol with address and data strobe signals.

The TFRA08C13 is manufactured using low-power CMOS technology and is packaged in an 352-pin plastic ball grid array (PBGA) with 50 mils ball pitch.

5-6965(F)

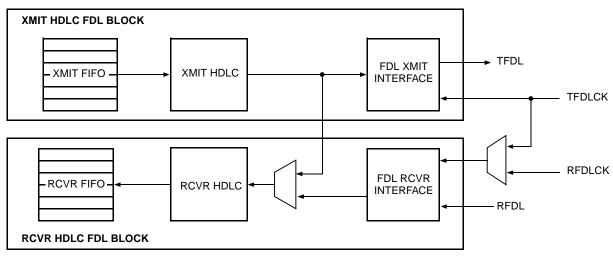

Figure 2. TFRA08C13 Block Diagram: Receive Section (One of Eight Channels)

# Functional Description (continued)

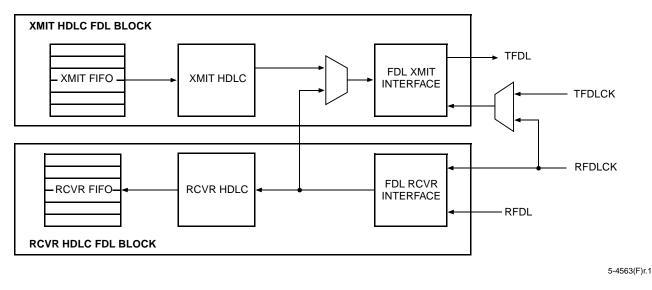

Figure 3. TFRA08C13 Block Diagram: Transmit Section (One of Eight Channels)

# **Pin Information**

The package type and pin assignment for the TFRA08C13 is illustrated in Figure 4.

Figure 4. Pin Assignment

# Table 1. Pin Assignments for 352-Pin PBGA by Pin Number Order

| Pin | Signal Name | Pin | Signal Name | Pin | Signal Name | [ | Pin  | Signal Name |

|-----|-------------|-----|-------------|-----|-------------|---|------|-------------|

| A1  | NC          | B13 | NC          | C25 | NC          |   | F3   | RFRMCLK1    |

| A2  | NC          | B14 | NC          | C26 | NC          |   | F4   | NC          |

| A3  | NC          | B15 | NC          | D1  | TCHIDATA1   |   | F23  | NC          |

| A4  | RCHIDATAB1  | B16 | NC          | D2  | TFS1        |   | F24  | NC          |

| A5  | RND8        | B17 | NC          | D3  | TCHIDATAB1  |   | F25  | LOPLLCLK    |

| A6  | NC          | B18 | 3-STATE     | D4  | NC          |   | F26  | DS1/CEPT7   |

| A7  | RCHIDATA8   | B19 | RND7        | D5  | PLLCK1      |   | G1   | TPD1        |

| A8  | TSSFS8      | B20 | RCHIDATAB7  | D6  | NC          |   | G2   | TND1        |

| A9  | TCHIDATAB8  | B21 | TCRCMFS7    | D7  | PLLCK8      |   | G3   | Vss         |

| A10 | RCRCMFS8    | B22 | TCHIDATA7   | D8  | TFDL8       |   | G4   | RFRMDATA1   |

| A11 | RFRMCK8     | B23 | RCRCMFS7    | D9  | NC          |   | G23  | LORLCK      |

| A12 | TPD8        | B24 | RFS7        | D10 | RFDLCK8     |   | G24  | RLCK7       |

| A13 | Vssd        | B25 | NC          | D11 | NC          |   | G25  | DIV-PLLCK   |

| A14 | Vddd        | B26 | NC          | D12 | RFRMDATA8   |   | G26  | PLLCK-EPLL  |

| A15 | NC          | C1  | TSSFS1      | D13 | NC          |   | H1   | NC          |

| A16 | NC          | C2  | TCRCMFS1    | D14 | NC          |   | H2   | RLCK1       |

| A17 | NC          | C3  | NC          | D15 | NC          |   | H3   | ТСК         |

| A18 | Vss         | C4  | NC          | D16 | NC          |   | H4   | NC          |

| A19 | CHIFS       | C5  | RCHIDATA1   | D17 | Vdda        |   | H23  | DIV-RLCK    |

| A20 | PLLCK7      | C6  | RND1        | D18 | CHICK       |   | H24  | CHICK-EPLL  |

| A21 | RCHIDATA7   | C7  | Vss         | D19 | NC          |   | H25  | RND6        |

| A22 | TSSFS7      | C8  | RCHIDATAB8  | D20 | TFDLCK7     |   | H26  | DIV-CHICK   |

| A23 | RFDL7       | C9  | TCRCMFS8    | D21 | NC          |   | J1   | TDI         |

| A24 | RSSFS7      | C10 | TCHIDATA8   | D22 | TCHIDATAB7  |   | J2   | TRST        |

| A25 | RFRMDATA7   | C11 | RSSFS8      | D23 | NC          |   | J3   | Vss         |

| A26 | NC          | C12 | TLCK8       | D24 | RFRMCLK7    |   | J4   | DS1/CEPT1   |

| B1  | TFDLCK1     | C13 | RLCK8       | D25 | NC          |   | J23  | NC          |

| B2  | NC          | C14 | NC          | D26 | NC          |   | J24  | DIV-CHICK   |

| B3  | TFDL1       | C15 | NC          | E1  | RSSFS1      |   | J25  | NC          |

| B4  | RPD1        | C16 | NC          | E2  | RFDL1       |   | J26  | RPD6        |

| B5  | RPD8        | C17 | Vssa        | E3  | RCRCMFS1    |   | K1   | TDO         |

| B6  | NC          | C18 | NC          | E4  | RFDLCK1     |   | K2   | TMS         |

| B7  | TFDLCK8     | C19 | RESET       | E23 | TLCK7       |   | K3   | RPD2        |

| B8  | TFS8        | C20 | RPD7        | E24 | Vdd         |   | K4   | Vdd         |

| B9  | RFDL8       | C21 | TFDL7       | E25 | TPD7        |   | K23  | PLLCK6      |

| B10 | RFS8        | C22 | TFS7        | E26 | TND7        |   | K24  | Vss         |

| B11 | TND8        | C23 | RFDLCK7     | F1  | TLCK1       |   | K25  | Vdd         |

| B12 | DS1/CEPT8   | C24 | NC          | F2  | RFS1        |   | K26  | NC          |

| L1  | PLLCK2      | R25 | TND6        | Y23 | TCHIDATAB5  |   | AC19 | TPD4        |

| L2  | RND2        | R26 | TLCK6       | Y24 | TFDL5       |   | AC20 | DS1/CEPT5   |

### Table 1. Pin Assignments for 352-Pin PBGA by Pin Number Order (continued)

| Pin | Signal Name | Pin | Signal Name |   | Pin  | Signal Name | Pin  | Signal Name |

|-----|-------------|-----|-------------|---|------|-------------|------|-------------|

| L3  | RCHIDATA2   | T1  | RFRMCLK2    |   | Y25  | TCRCMFS5    | AC21 | NC          |

| L4  | NC          | T2  | RFS2        |   | Y26  | TFDLCK5     | AC22 | NC          |

| L23 | NC          | Т3  | NC          |   | AA1  | TSSFS3      | AC23 | NC          |

| L24 | NC          | T4  | NC          |   | AA2  | TFDLCK3     | AC24 | RFRMDATA5   |

| L25 | TFDLCK6     | T23 | NC          |   | AA3  | RFDL3       | AC25 | RFRMCLK5    |

| L26 | RCHIDATA6   | T24 | RFRMCLK6    |   | AA4  | NC          | AC26 | RFS5        |

| M1  | RCHIDATAB2  | T25 | DS1/CEPT6   |   | AA23 | NC          | AD1  | NC          |

| M2  | Vdd         | T26 | TPD6        |   | AA24 | TFS5        | AD2  | RFRMDATA3   |

| M3  | TSSFS2      | U1  | TPD2        |   | AA25 | TCHIDATA5   | AD3  | NC          |

| M4  | TFDLCK2     | U2  | TND2        |   | AA26 | TSSFS5      | AD4  | TPD3        |

| M23 | RCHIDATAB6  | U3  | Vdd         |   | AB1  | TCHIDATA3   | AD5  | A1          |

| M24 | TFDL6       | U4  | RLCK2       |   | AB2  | TCHIDATAB3  | AD6  | A4          |

| M25 | TFS6        | U23 | ALE_AS      |   | AB3  | RFS3        | AD7  | A8          |

| M26 | TCRCMFS6    | U24 | RLCK6       |   | AB4  | RCRCMFS3    | AD8  | INTERRUPT   |

| N1  | TCRCMFS2    | U25 | CS          |   | AB23 | RCRCMFS5    | AD9  | RND4        |

| N2  | TFDL2       | U26 | RD_RW       |   | AB24 | RFDLCK5     | AD10 | RCHIDATA4   |

| N3  | RFDL2       | V1  | DS1/CEPT2   |   | AB25 | RSSFS5      | AD11 | TSSFS4      |

| N4  | NC          | V2  | NC          |   | AB26 | RFDL5       | AD12 | AD0         |

| N23 | RFDL6       | V3  | PLLCK3      |   | AC1  | RSSFS3      | AD13 | AD4         |

| N24 | TSSFS6      | V4  | NC          |   | AC2  | RFDLCK3     | AD14 | NC          |

| N25 | RFDLCK6     | V23 | RCHIDATAB5  |   | AC3  | NC          | AD15 | NC          |

| N26 | TCHIDATA6   | V24 | WR_DS       |   | AC4  | NC          | AD16 | RCRCMFS4    |

| P1  | TCHIDATA2   | V25 | RND5        |   | AC5  | A0          | AD17 | RFRMCLK4    |

| P2  | TFS2        | V26 | RDY_DTACK   |   | AC6  | NC          | AD18 | Vdd         |

| P3  | RCRCMFS2    | W1  | RPD3        |   | AC7  | A3          | AD19 | DS1/CEPT4   |

| P4  | TCHIDATAB2  | W2  | RND3        |   | AC8  | NC          | AD20 | Vss         |

| P23 | NC          | W3  | TFDL3       |   | AC9  | A10         | AD21 | NC          |

| P24 | TCHIDATAB6  | W4  | RCHIDATAB3  |   | AC10 | PLLCK4      | AD22 | NC          |

| P25 | RFRMDATA6   | W23 | NC          |   | AC11 | NC          | AD23 | NC          |

| P26 | RSSFS6      | W24 | RPD5        |   | AC12 | TCHIDATAB4  | AD24 | NC          |

| R1  | RSSFS2      | W25 | RCHIDATA5   |   | AC13 | NC          | AD25 | NC          |

| R2  | RFDLCK2     | W26 | PLLCK5      | ] | AC14 | AD2         | AD26 | Vss         |

| R3  | RFRMDATA2   | Y1  | RCHIDATA3   |   | AC15 | RFDL4       | AE1  | NC          |

| R4  | TLCK2       | Y2  | Vss         | ] | AC16 | NC          | AE2  | NC          |

| R23 | RFS6        | Y3  | TFS3        |   | AC17 | RFS4        | AE3  | TLCK3       |

| R24 | RCRCMFS6    | Y4  | TCRCMFS3    |   | AC18 | NC          | AE4  | TND3        |

| Pin  | Signal Name |

|------|-------------|------|-------------|------|-------------|------|-------------|

| AE5  | DS1/CEPT3   | AE17 | RFDLCK4     | AF3  | Vdd         | AF15 | AD6         |

| AE6  | A2          | AE18 | RFRMDATA4   | AF4  | RLCK3       | AF16 | NC          |

| AE7  | A6          | AE19 | NC          | AF5  | Vdd         | AF17 | RSSFS4      |

| AE8  | A9          | AE20 | TND4        | AF6  | A5          | AF18 | NC          |

| AE9  | SECOND      | AE21 | Vss         | AF7  | A7          | AF19 | TLCK4       |

| AE10 | MPCLK       | AE22 | TPD5        | AF8  | A11         | AF20 | RLCK4       |

| AE11 | RCHIDATAB4  | AE23 | NC          | AF9  | MPMODE      | AF21 | RLCK5       |

| AE12 | TFDLCK4     | AE24 | NC          | AF10 | RPD4        | AF22 | TND5        |

| AE13 | TFS4        | AE25 | NC          | AF11 | TFDL4       | AF23 | NC          |

| AE14 | AD1         | AE26 | TLCK5       | AF12 | TCRCMFS4    | AF24 | NC          |

| AE15 | AD5         | AF1  | NC          | AF13 | TCHIDATA4   | AF25 | NC          |

| AE16 | AD7         | AF2  | RFRMCLK3    | AF14 | AD3         | AF26 | NC          |

### Table 1. Pin Assignments for 352-Pin PBGA by Pin Number Order (continued)

Table 2 shows the list of the TFRA08C13 pins and a functional description for each.

## Table 2. Pin Descriptions

| Pins                                                   | Symbol             | Type* | Description                                                                                                                                                                                                                           |

|--------------------------------------------------------|--------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AF3, AF5,<br>AD18, K25,<br>E24, K4,<br>M2, U3          | Vdd                | Р     | <b>3.3 V Power Supply.</b> 3.3 V ± 5%. Each of these pins must be bypassed with a 0.1 $\mu$ F capacitor to VSS, as close to the pin as possible.                                                                                      |

| AD20, AD26,<br>AE21, G3,<br>K24,<br>A18, J3, C7,<br>Y2 | Vss                | G     | Ground.                                                                                                                                                                                                                               |

| D17                                                    | Vdda               | Р     | <b>3.3 V Quiet Analog Power Supply.</b> This pin must be bypassed with a 0.1 $\mu$ F capacitor to VSSA, as close to the pin as possible. In addition, this pin should be isolated from the 3.3 V power plane with an inductive bead.  |

| C17                                                    | VSSA               | G     | 3.3 V Quiet Analog Ground.                                                                                                                                                                                                            |

| A14                                                    | Vddd               | Р     | <b>3.3 V Quiet Digital Power Supply.</b> This pin must be bypassed with a 0.1 $\mu$ F capacitor to VSSD, as close to the pin as possible. In addition, this pin should be isolated from the 3.3 V power plane with an inductive bead. |

| A13                                                    | Vssd               | G     | 3.3 V Quiet Digital Ground.                                                                                                                                                                                                           |

| B18                                                    | 3-STATE            | lu    | <b>3-State (Active-Low).</b> Asserting this pin low forces the channel outputs into a high-impedance state.                                                                                                                           |

| C19                                                    | RESET <sup>†</sup> | lu    | <b>Reset (Active-Low).</b> Asserting this pin low resets all channels on the entire device.                                                                                                                                           |

\* I<sup>u</sup> indicates an internal pull-up, I<sup>d</sup> indicates an internal pull-down.

† After RESET is deasserted, the channel is in the default framing mode, as a function of the DS1/CEPT pin.

‡ Asserting this pin low will initially force RDY to a low state.

18

| Table 2. F | Pin Descr | iptions | (continued) |

|------------|-----------|---------|-------------|

|------------|-----------|---------|-------------|

| Pins     | Symbol      | Туре* | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|-------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AE9      | SECOND      | 0     | <b>Second Pulse.</b> A one second timer with an active-high pulse. The duration of the pulse is one RLCK cycle. Framer_1's receive line clock signal (RLCK1) is the default clock source for the internal second pulse timer. The internal second pulse is retimed in the individual framer sections with their corresponding receive line clock signal RLCK. When LORLCK_(N) is active, then Framer_(N + 1)'s receive line clock signal is used as the clock signal source for the internal second pulse timer. The second pulse is used for performance monitoring. |

| D18      | CHICK       | Ι     | CHI Clock. 2.048 MHz,<br>4.096 MHz, or 8.192 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| A19      | CHIFS       | I     | <b>CHI Frame Sync.</b> CHI 8 kHz input frame synchronization pulse. Pulse width must be a minimum of one clock period of CHICK and a maximum of a 50% duty cycle square wave.                                                                                                                                                                                                                                                                                                                                                                                         |

| H24      | CHICK-EPLL  | 0     | <b>Error Phase-Lock Loop Signal.</b> The error signal proportional to the phase difference between DIV-CHICK and DIV-RLCK as detected from the internal PLL circuitry (see Table 66. Global Control Register (GREG8) (008)                                                                                                                                                                                                                                                                                                                                            |

| G25      | DIV-PLLCK   | 0     | <b>Divided-Down PLLCK Clock.</b> 32 kHz or 8 kHz clock signal derived from the PLLCK input signal (see Table 150. CHI Common Control Register (FRM_PR45) (Y8D)).                                                                                                                                                                                                                                                                                                                                                                                                      |

| G26      | PLLCK-EPLL  | 0     | <b>Error Phase-Lock Loop Signal.</b> The error signal proportional to the phase difference between DIV-PLLCK and DIV-CHICK as detected by the internal PLL circuitry (refer to the Phase-Lock Loop section).                                                                                                                                                                                                                                                                                                                                                          |

| H23      | DIV-RLCK    | 0     | <b>Divided-Down Receive Line Clock.</b> 8 kHz clock signal derived from the recovered receive line interface unit clock or the RLCK input signal. The choice of which receive framer clock to use is defined in Table 66. Global Control Register (GREG8) (008).                                                                                                                                                                                                                                                                                                      |

| H26, J24 | DIV-CHICK   | 0     | <b>Divided-Down CHI Clock.</b> 8 kHz clock signal derived from the transmit CHI CLOCK input signal (see Table 66. Global Control Register (GREG8) (008)).                                                                                                                                                                                                                                                                                                                                                                                                             |

| J4       | DS1/CEPT[1] | lu    | <b>DS1/CEPT.</b> Strap to VDD to enable DS1 operation in the framer unit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| V1       | DS1/CEPT[2] |       | Strap to Vss to enable CEPT operation in the framer unit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| AE5      | DS1/CEPT[3] |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| AD19     | DS1/CEPT[4] |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| AC20     | DS1/CEPT[5] |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| T25      | DS1/CEPT[6] |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| F26      | DS1/CEPT[7] |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| B12      | DS1/CEPT[8] |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

\* I<sup>u</sup> indicates an internal pull-up, I<sup>d</sup> indicates an internal pull-down.

† After RESET is deasserted, the channel is in the default framing mode, as a function of the DS1/CEPT pin.

‡ Asserting this pin low will initially force RDY to a low state.

| Table 2. Pin Descriptions (continued) |

|---------------------------------------|

|---------------------------------------|

| Pins | Symbol   | Type* | Description                                                                                                                                                                                                                          |

|------|----------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D5   | PLLCK[1] | I     | Transmit Framer Phase-Locked Line Interface Clock. Clock signal                                                                                                                                                                      |

| L1   | PLLCK[2] |       | used to time the transmit framer. This signal must be phase-locked to                                                                                                                                                                |

| V3   | PLLCK[3] |       | CHICK clock signal. In DS1 frame formats, PLLCK can be a low-<br>frequency signal (1.544 MHz) or a high frequency signal (6.176 MHz).                                                                                                |

| AC10 | PLLCK[4] |       | In CEPT frame formats, PLLCK can be a low-frequency signal                                                                                                                                                                           |

| W26  | PLLCK[5] |       | (2.048 MHz) or a high-frequency signal (8.192 MHz).                                                                                                                                                                                  |

| K23  | PLLCK[6] |       |                                                                                                                                                                                                                                      |

| A20  | PLLCK[7] |       |                                                                                                                                                                                                                                      |

| D7   | PLLCK[8] |       |                                                                                                                                                                                                                                      |

| F25  | LOPLLCK  | 0     | <b>Loss of PLLCK Clock.</b> This pin is asserted high when the PLLCK clock does not toggle for a 250 µs interval. This pin is deasserted 250 µs after the first edge of PLLCK (see Table 66. Global Control Register (GREG8) (008)). |

| F1   | TLCK[1]  | 0     | Transmit Framer Line Interface Clock. Optional 1.544 MHz DS1 or                                                                                                                                                                      |

| R4   | TLCK[2]  |       | 2.048 MHz output signal from the transmit framer. TND and TPD data                                                                                                                                                                   |

| AE3  | TLCK[3]  |       | changes on the rising edge of TLCK.                                                                                                                                                                                                  |

| AF19 | TLCK[4]  |       |                                                                                                                                                                                                                                      |

| AE26 | TLCK[5]  |       |                                                                                                                                                                                                                                      |