# Clock Generator and Ready Interface for 80C286 Processors

March 1997

#### Features

- This Circuit is Processed in Accordance to MIL-STD-883 and is Fully Conformant Under the Provisions of Paragraph 1.2.1.

- Generates System Clock for 80C286 Processors

- Generates System Reset Output from Schmitt Trigger Input

- Improved Hysteresis

- Uses Crystal or External Signal for Frequency Source

- Dynamically Switchable Between Two Input Frequencies

- Provides Local READY and MULTIBUS™ READY Synchronization

- Static CMOS Technology

- Single +5V Power Supply

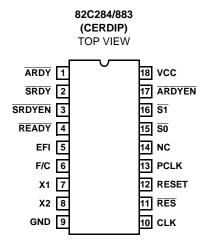

- Available in 18 Lead CERDIP Package

#### **Pinout**

# Description

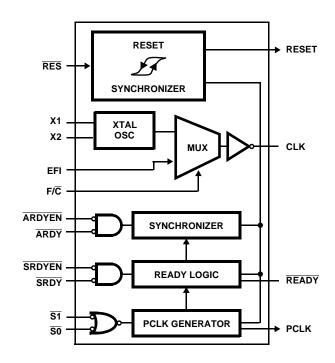

The Intersil 82C284/883 is a clock generator/driver which provides clock signals for 80C286 processors and support components. It also contains logic to supply READY to the CPU from either asynchronous or synchronous sources and synchronous RESET from an asynchronous input with hysteresis

# Ordering Information

| PART NUMBER     | TEMP. RANGE     | PACKAGE | PKG. NO. |

|-----------------|-----------------|---------|----------|

| MD82C284-12/883 | -55°C to +125°C | CERDIP  | F18.3    |

# Functional Diagram

# **Absolute Maximum Ratings**

####

#### **Thermal Information**

| Thermal Resistance | $\theta_{JA}$ (oC/W) | $\theta_{JC}$ (oC/W) |

|--------------------|----------------------|----------------------|

| CERDIP Package     | 80                   | 20                   |

| Gate Count         | 65 <sup>c</sup>      | C to +150°C          |

CAUTION: Stresses above those listed in the "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operation section of this specification is not implied.

# **Operating Conditions**

| Operating Temperature Range55°C to +125°C | EFI Rise Time (From 0.8V to 3.2V)           |

|-------------------------------------------|---------------------------------------------|

| Operating Supply Voltage +4.5V to +5.5V   | EFI Fall Time (From 3.2V to 0.8V) 8ns (Max) |

#### TABLE 1. 82C284/883 D.C. ELECTRICAL PERFORMANCE SPECIFICATIONS

Device Guaranteed and 100% Tested.

| PARAMETER                      | SYMBOL | CONDITIONS                         | GROUP A<br>SUBGROUPS | TEMPERATURE                                | MIN      | MAX | UNITS |

|--------------------------------|--------|------------------------------------|----------------------|--------------------------------------------|----------|-----|-------|

| Input LOW Voltage              | VIL    | VCC = 4.5V                         | 1, 2, 3              | $-55^{0}C \le T_{A} \le +125^{0}C$         | -        | 0.8 | V     |

| Input HIGH Voltage             | VIH    | VCC = 5.5V                         | 1, 2, 3              | $-55^{o}C \le T_A \le +125^{o}C$           | 2.2      | -   | V     |

| EFI, F/C Input High Voltage    | VIHC   | VCC = 5.5V                         | 1, 2, 3              | $-55^{O}C \le T_A \le +125^{O}C$           | 3.2      | -   | V     |

| RES HIGH Voltage               | VIHR   | VCC = 5.5V                         | 1, 2, 3              | $-55^{O}C \le T_A \le +125^{O}C$           | VCC -0.8 | -   | V     |

| RES Input Hysteresis           | VHYS   | VCC = 5.5V                         | 1, 2, 3              | $-55^{o}C \le T_A \le +125^{o}C$           | 0.5      | -   | V     |

| RESET, PCLK Output LOW Voltage | VOL    | IOL = 5mA,<br>VCC = 4.5V, Note 2   | 1, 2, 3              | $-55^{o}C \le T_{A} \le +125^{o}C$         | -        | 0.4 | V     |

| RESET, PCLK Output<br>Voltage  | VOH    | IOH = -1mA,<br>VCC = 4.5V, Note 2  | 1, 2, 3              | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$ | VCC -0.4 | -   | V     |

| READY Output LOW<br>Voltage    | VOLR   | IOH = 10mA,<br>VCC = 4.55V, Note 2 | 1, 2, 3              | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$ | -        | 0.4 | V     |

| CLK Output LOW Voltage         | VOLC   | IOL = 5mA,<br>VCC = 4.5V, Note 2   | 1, 2, 3              | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$ | -        | 0.4 | V     |

| CLK Output HIGH Voltage        | VOHC   | IOH = -5mA,<br>VCC = 4.5V, Note 2  | 1, 2, 3              | $-55^{o}C \le T_{A} \le +125^{o}C$         | VCC -0.4 | -   | V     |

| Input Leakage Current          | II     | VIN = GND or VCC,<br>VCC = 5.5V    | 1, 2, 3              | $-55^{o}C \le T_{A} \le +125^{o}C$         | -10      | 10  | μА    |

| Active Power Supply            | ICCOP  | 82C284-10/883, Note 1              | 1, 2, 3              | $-55^{O}C \le T_A \le +125^{O}C$           | -        | 48  | mA    |

| Current                        |        | 82C284-12/883, Note 1              | 1, 2, 3              | $-55^{O}C \le T_A \le +125^{O}C$           | -        | 60  | mA    |

#### NOTES:

- 1. ICCOP measured at 10MHz for the 82C284-10/883 and at 12.5MHz for the 82C284-12/883. VIN = GND or VCC, VCC = 5.5V, outputs unloaded.

- 2. Interchanging of force and sense conditions is permitted.

#### TABLE 2. 82C284/883 A.C. ELECTRICAL PERFORMANCE SPECIFICATIONS

Device Guaranteed and 100% Tested. A.C. timings are referenced to 0.8V and 2.0V points of the signals as illustrated in datasheet waveforms, unless otherwise specified.

|               |        | (NOTE 1)         | GROUP A   |                                    | 101 | ИHz | 121 | ИHz |       |

|---------------|--------|------------------|-----------|------------------------------------|-----|-----|-----|-----|-------|

| PARAMETER     | SYMBOL | CONDITIONS       | SUBGROUP  | TEMPERATURE                        | MIN | MAX | MIN | MAX | UNITS |

| EFI LOW Time  | t1     | At VCC/2, Note 8 | 9, 10, 11 | $-55^{0}C \le T_{A} \le +125^{0}C$ | 20  | -   | 16  | -   | ns    |

| EFI HIGH Time | t2     | At VCC/2, Note 8 | 9, 10, 11 | $-55^{0}C \le T_{A} \le +125^{0}C$ | 20  | -   | 20  | -   | ns    |

# TABLE 2. 82C284/883 A.C. ELECTRICAL PERFORMANCE SPECIFICATIONS (Continued)

Device Guaranteed and 100% Tested. A.C. timings are referenced to 0.8V and 2.0V points of the signals as illustrated in datasheet waveforms, unless otherwise specified. (Continued)

|                                                 |        | (NOTE 1)                             | GROUP A   | Δ                                          |            | ИHz | 12         | ИHz |       |

|-------------------------------------------------|--------|--------------------------------------|-----------|--------------------------------------------|------------|-----|------------|-----|-------|

| PARAMETER                                       | SYMBOL | CONDITIONS                           | SUBGROUP  | TEMPERATURE                                | MIN        | MAX | MIN        | MAX | UNITS |

| Status Setup Time<br>for Status Going<br>Active | t5A    |                                      | 9, 10, 11 | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$ | 20         | -   | 18         | -   | ns    |

| Status Setup Time for Going Inactive            | t5B    |                                      | 9, 10, 11 | $-55^{o}C \le T_{A} \le +125^{o}C$         | 20         | -   | 16         | -   | ns    |

| Status Hold Time                                | t6     |                                      | 9, 10, 11 | $-55^{o}C \le T_{A} \le +125^{o}C$         | 1          | -   | 1          | -   | ns    |

| F/C Setup Time                                  | t7     |                                      | 9, 10, 11 | $-55^{0}C \le T_{A} \le +125^{0}C$         | 15         | -   | 15         | -   | ns    |

| F/C Hold Time                                   | t8     |                                      | 9, 10, 11 | $-55^{o}C \le T_{A} \le +125^{o}C$         | 15         | -   | 15         | -   | ns    |

| SRDY or SRDYEN<br>Setup Time                    | t9     |                                      | 9, 10, 11 | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$ | 15         | -   | 15         | -   | ns    |

| SRDY or SRDYEN<br>Hold Time                     | t10    |                                      | 9, 10, 11 | $-55^{o}C \le T_{A} \le +125^{o}C$         | 2          | -   | 2          | -   | ns    |

| ARDY or ARDYEN<br>Setup Time                    | t11    | Note 3                               | 9, 10, 11 | $-55^{o}C \le T_{A} \le +125^{o}C$         | 5          | -   | 5          | -   | ns    |

| ARDY or ARDYEN<br>Hold Time                     | t12    | Note 3                               | 9, 10, 11 | $-55^{o}C \le T_{A} \le +125^{o}C$         | 30         | -   | 25         | -   | ns    |

| RES Setup Time                                  | t13    | Notes 3, 7                           | 9, 10, 11 | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$ | 20         | -   | 18         | -   | ns    |

| RES Hold Time                                   | t14    | Notes 3, 7                           | 9, 10, 11 | $-55^{0}C \le T_{A} \le +125^{0}C$         | 10         | -   | 8          | -   | ns    |

| CLK Period                                      | t16    |                                      | 9, 10, 11 | $-55^{o}C \le T_{A} \le +125^{o}C$         | 50         | -   | 40         | -   | ns    |

| CLK LOW Period                                  | t17    | Notes 2, 6                           | 9, 10, 11 | $-55^{o}C \le T_{A} \le +125^{o}C$         | 12         | -   | 11         | -   | ns    |

| CLK HIGH Time                                   | t18    | Notes 2, 6                           | 9, 10, 11 | $-55^{0}C \le T_{A} \le +125^{0}C$         | 16         | -   | 13         | -   | ns    |

| READY Inactive Delay                            | t21    | At 0.8V, Note 4,<br>Test Condition 2 | 9, 10, 11 | $-55^{o}C \le T_{A} \le +125^{o}C$         | 5          | -   | 5          | -   | ns    |

| READY Active De-<br>lay                         | t22    | At 0.8V, Note 4                      | 9, 10, 11 | $-55^{o}C \le T_{A} \le +125^{o}C$         | -          | 24  | -          | 18  | ns    |

| PCLK Delay                                      | t23    | CL = 75pF,<br>Test Condition 1       | 9, 10, 11 | $-55^{o}C \le T_{A} \le +125^{o}C$         | -          | 20  | -          | 16  | ns    |

| RESET Delay                                     | t24    | CL = 75pF,<br>Test Condition 3       | 9, 10, 11 | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$ | -          | 27  | -          | 26  | ns    |

| PCLK LOW Time                                   | t25    | CL = 75pF, Note 5                    | 9, 10, 11 | $-55^{o}C \le T_{A} \le +125^{o}C$         | t16-<br>10 | -   | t16-<br>10 | -   | ns    |

| PCLK HIGH Time                                  | t26    | CL = 75pF, Note 5                    | 9, 10, 11 | $-55^{o}C \le T_{A} \le +125^{o}C$         | t16-<br>10 | -   | t16-<br>10 | -   | ns    |

#### TABLE 2. 82C284/883 A.C. ELECTRICAL PERFORMANCE SPECIFICATIONS (Continued)

Device Guaranteed and 100% Tested. A.C. timings are referenced to 0.8V and 2.0V points of the signals as illustrated in datasheet waveforms, unless otherwise specified. (Continued)

|   |           |        | (NOTE 1)   | GROUP A  |             | 101 | ИHz | 121 | ИHz |       |

|---|-----------|--------|------------|----------|-------------|-----|-----|-----|-----|-------|

| L | PARAMETER | SYMBOL | CONDITIONS | SUBGROUP | TEMPERATURE | MIN | MAX | MIN | MAX | UNITS |

#### NOTES:

- 1. VCC = 4.5V and 5.5V unless otherwise specified. CLK loading: CL = 100pF.

- 2. With the internal crystal oscillator using recommended crystal and capacitive loading; or with the EFI input meeting specifications t1 and t2. The recommended crystal loading for CLK frequencies of 8MHz to 20MHz are 25pF from pin X1 to GND, and 15pF from pin X2 to GND; for CLK frequencies from 20MHz to 25MHz the recommended loading is 15pF from pin X1 to GND, and 15pF from X2 to GND. These recommended values are ±5pF and include all stray capacitance. Decouple VCC and GND as close to the 80C284/883 as possible.

- 3. This is an asychronous input. This specification is given for testing purposes only, to assure recognition at a specific CLK edge.

- 4. The pull-up resistor value for the  $\overline{READY}$  pin is  $620\Omega$  with the rated 150pF load.

- 5. t16 refers to any allowable CLK period.

- 6. When using a crystal with the recommended capacitive loading, CLK output HIGH and LOW times are guaranteed to meet 80C286 requirements.

- 7. Measured from 1.0V on the CLK to 0.8V on the RES waveform for RES active, and to 4.2V on the RES waveform for RES inactive.

- 8. Input test waveform characteristics: VIL= 0.0V, VIH = 4.5V.

TABLE 3. 82C284/883 ELECTRICAL PERFORMANCE SPECIFICATIONS

|                              |        |                                                                       |       |                                            | 101 | ИHz | 121 | ИHz |       |

|------------------------------|--------|-----------------------------------------------------------------------|-------|--------------------------------------------|-----|-----|-----|-----|-------|

| PARAMETER                    | SYMBOL | CONDITIONS                                                            | NOTES | TEMPERATURE                                | MIN | MAX | MIN | MAX | UNITS |

| Input Capacitance            | CIN    | FREQ = 1MHz, All<br>measurements are<br>referenced to de-<br>vice GND | 1     | T <sub>A</sub> = +25°C                     | -   | 10  | -   | 10  | pF    |

| EFI HIGH to CLK<br>LOW Delay | t15A   |                                                                       | 1, 2  | $-55^{o}C \le T_{A} \le +125^{o}C$         | -   | 30  | -   | 25  | ns    |

| EFI LOW to CLK<br>HIGH Delay | t15B   |                                                                       | 1, 3  | $-55^{o}C \le T_{A} \le +125^{o}C$         | -   | 35  | -   | 30  | ns    |

| CLK Rise Time                | t19    | 1.0V to 3.6V,<br>CL = 100pF                                           | 1     | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$ | -   | 8   | -   | 8   | ns    |

| CLK Fall Time                | t20    | 3.6V to 1.0V,<br>CL = 100pF                                           | 1     | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$ | =   | 8   | =   | 8   | ns    |

| X1 HIGH to CLK               | t27    |                                                                       | 1, 4  | $-55^{o}C \le T_{A} \le +125^{o}C$         | -   | 35  | ı   | 30  | ns    |

#### NOTES:

- 1. The parameters listed in Table 3 are controlled via design or process parameters and are not directly tested. These parameters are characterized upon initial design and after major process and/or design changes.

- 2. Measured from 3.2V on the EFI waveform to 1.0V on the CLK.

- 3. Measured from 0.8V on the EFI waveform to 3.6V on the CLK.

- 4. Measured from 3.6V on the X1 input to 3.6V on the CLK.

**TABLE 4. APPLICABLE SUBGROUPS**

| CONFORMANCE GROUPS | METHOD    | SUBGROUPS |  |  |

|--------------------|-----------|-----------|--|--|

| Initial Test       | 100%/5004 | -         |  |  |

| Interim Test       | 100%/5004 | 1, 7, 9   |  |  |

**TABLE 4. APPLICABLE SUBGROUPS**

| CONFORMANCE GROUPS | METHOD       | SUBGROUPS                     |

|--------------------|--------------|-------------------------------|

| PDA                | 100%         | 1                             |

| Final Test         | 100%         | 2, 3, 8A, 8B, 10, 11          |

| Group A            | -            | 1, 2, 3, 7, 8A, 8B, 9, 10, 11 |

| Groups C & D       | Samples/5005 | 1, 7, 9                       |

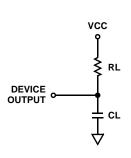

# A.C. Test Conditions

| TEST CONDITION | RL   | CL    |

|----------------|------|-------|

| 1              | 750Ω | 75pF  |

| 2              | 620Ω | 150pF |

| 3              | ∞    | 75pF  |

# A.C. Specifications

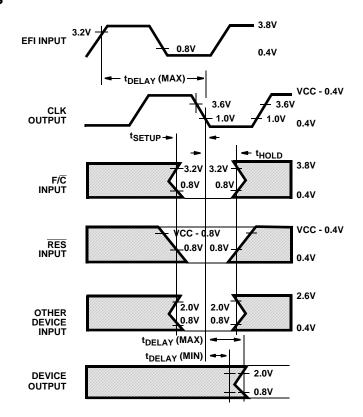

FIGURE 1. A.C. DRIVE, SETUP, HOLD AND DELAY TIME MEASUREMENT POINTS

# **Timing Waveforms**

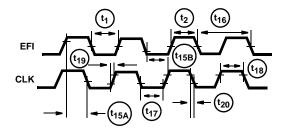

# FIGURE 2. CLK AS A FUNCTION OF EFI

NOTE: The EFI input LOW and HIGH times as shown are required to guarantee the CLK LOW and HIGH times shown.

NOTE: This is an asynchronous input. The setup and hold times shown are required to guarantee the response shown.

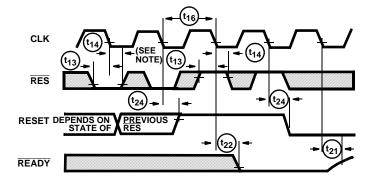

FIGURE 3. RESET AND READY TIMING AS A FUNCTION OF RES WITH \$\overline{S1}\$, \$\overline{S0}\$, \$\overline{ARDY}\$ + \$\overline{ARDYEN}\$ AND \$\overline{SRDY}\$ + \$\overline{SRDYEN}\$ HIGH

#### NOTES:

- 1. This is an asynchronous input. The setup and hold times shown are required to guarantee the response shown.

- 2. If SRDY + SRDYEN or ARDY + ARDYEN are active before and/or during the first bus cycle after RESET, READY may not be deasserted until the falling edge of φ2 of T<sub>S</sub>.

FIGURE 4. READY AND PCLK TIMING WITH RES HIGH

#

FIGURE 5. CLK AS A FUNCTION OF  $F/\overline{C}$ , PCLK, X1, AND EFI DURING DYNAMIC FREQUENCY SWITCHING NOTE: This is an asynchronous input. The setup and hold times shown are required to guarantee the response shown.

EFI

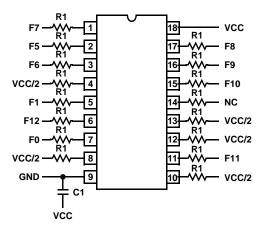

# **Burn-In Circuit**

# **18 LEAD CERDIP**

#### NOTES:

- 1. Supply Voltage: VCC = 5.5V,  $\pm 0.5$ V, GND = 0V. Driver Voltage: VIH = 4.5V  $\pm$  10%, VIL = 0V

- 2. Input Voltage Limits: VIL (Max) = 0.4V, VIH (Min) = 2.6V

- 3. Component Values: R1 =  $47k\Omega$ , C1 =  $0.1\mu F$  (Min)

- 4. Oven type and frequency requirements microtest, F0 through F12.

- 5. Approximate current per unit. ICC = 0.3mA.

- 6. Special requirements:

- (a) Electrostatic Discharge Sensitive. Proper precautions must be used when handling units.

- (b) All power supplies must be at zero volts when the boards are inserted into the ovens. After insertion, apply VCC first, then activate the driver power supplies.

- 7. Oscilloscope measurements: To be on loaded boards before insertion into the oven.

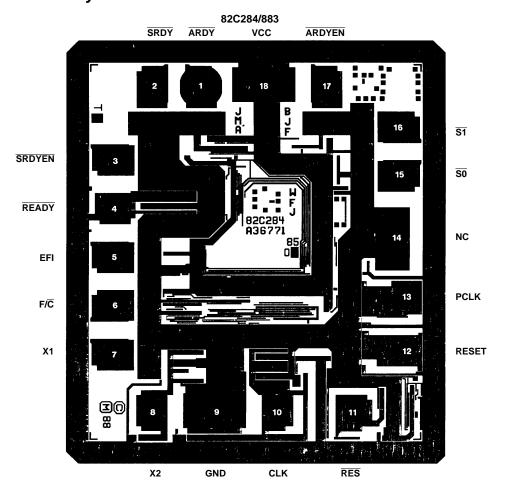

# Die Characteristics

**DIE DIMENSIONS:**

63 mils x 69 mils x 19 mils  $\pm$  1 mil

**METALLIZATION:**

Type: Silicon - Aluminum

Thickness: 8kÅ

**GLASSIVATION:**

Type: Nitrox Thickness: 10kÅ

WORST CASE CURRENT DENSITY:

$2 \times 10^5 \text{ A/cm}^2$

# Metallization Mask Layout

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com