# ML6680

# **Token Ring Copper-to-Fiber Converter**

# **GENERAL DESCRIPTION**

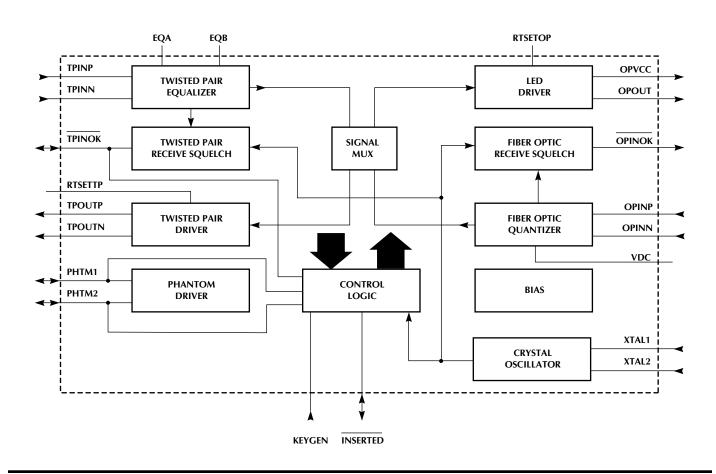

The ML6680 is a single-chip conversion between Token Ring ISO/IEC8802-5 copper-based media and Token Ring ISO/IEC8802-5 fiber-based media. The ML6680 fiber-optic interface contains a data quantizer, circuitry for fiber optic key signal generation and recognition, pin-selectable signal switching, and current driven transmitter outputs.

The ML6680 copper interface consists of a twisted pair line equalizer, receive squelch circuit, pin selectable phantom wire fault detection and signal switching, and a transmit driver. This section supports the ISO/IEC8802-5 standard requirements. The ML6680 provides an optional PECL compatible interface.

The ML6680 may be configured to one of four modes:

- 1. Standard Media Converter

- 2. Concentrator Media Converter

- 3. Lobe or Ring Out Port Media Converter

- 4. Ring In Port Media Converter

**BLOCK DIAGRAM**

## **FEATURES**

- Single-chip copper-to-fiber converter for Token Ring

- 16Mbps and 4Mbps data rates with the same external components

- Four modes of operation covering a wide variety of applications

- Full duplex operation

- Highly stable data quantizer with 55dB input dynamic range

- Current driven fiber optic LED driver for accurate launch power

- Current driven output for low RFI noise and low jitter

- Capable of driving 100Ω UTP or 150Ω STP

- Pin selectable phantom wire fault detection and signal switching

# Micro Linear

# ML6680

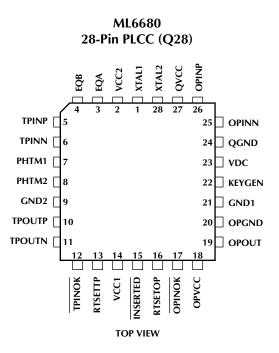

# **PIN CONFIGURATION**

# **PIN DESCRIPTION**

| PIN#   | NAME             | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 28  | XTAL1,<br>XTAL2  | Crystal inputs. A 32.768kHz watch<br>crystal connected between these pins<br>provides timing for the fiber optic<br>insertion key signal. An external clock<br>can be used to drive XTAL1 while<br>grounding XTAL2. The frequency of<br>the external clock should be between<br>32.7kHz and 34.5kHz.                                                                                                                                                                                                                                                                                          |

| 2      | V <sub>CC2</sub> | Positive 5V power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3, 4   | EQA, EQB         | Equalizer network pins. An external combination of two resistors and a capacitor connected at EQA and EQB sets up the on-chip twisted pair receive equalizer.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5, 6   | TPINP/N          | Receive twisted pair inputs. This<br>differential input pair receives<br>differential Manchester signals from<br>the coupling transformer (or PECL<br>compatible levels).                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 7, 8   | PHTM1/2          | Phantom drive/sense inputs/outputs. In<br>configuration 1, these pins are TTL<br>inputs from two external opto<br>isolators. They are low when phantom<br>power is present and high when<br>phantom power is removed. These<br>pins provide the phantom drive<br>current and are used to check for a<br>wire fault on the phantom circuits<br>when it is required in configuration 2.<br>In configuration 3, these pins are don't<br>cares. In configuration 4, these pins<br>are low for normal operation, or any<br>or both of them is high to force the<br>ML6680 into the "Bypass State." |

| 9      | GND2             | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 10, 11 | TPOUTP/N         | Transmit twisted pair outputs. This<br>differential current output pair drives<br>differential Manchester signals into the<br>network coupling transformer and<br>transmit filter. Output edge rates are<br>controlled to allow use of a simpler<br>filter than would otherwise be<br>required. These outputs can be PECL<br>compatible with an external resistor<br>network.                                                                                                                                                                                                                 |

| 12     | TPINOK           | Valid twisted pair input signal<br>indicator. It is an active low, open<br>collector LED driver. This output goes<br>low when the signal at TPINP/N meets<br>frequency and amplitude squelch<br>requirements. This input is tied to<br>ground for configurations 3 and 4 to<br>enable signal path switching.                                                                                                                                                                                                                                                                                  |

| DINI# | NIAAAE | ELINICTION |

|-------|--------|------------|

| PIN#  | NAME   | FUNCTION   |

- 13 RTSETTP Twisted pair transmit level set resistor input. A precision resistor between RTSETTP and VCC sets the amplitude of the TPOUTP/N output.

- 14 VCC1 Positive 5V power supply.

- 15 INSERTED Insertion indicator. It is an active low, open collector LED driver. In configurations 1, 3 and 4 this output goes low when the ML6680 is in the "Insert State." In configuration 2 this output goes low when the ML6680 is in the "Insert State" and no wire fault is detected. This input is tied to ground to disable the frequency squelch, and to reduce the time constant of the amplitude squelch of the optical input.

- 16 RTSETOP A precision resistor between RTSETOP and VCC sets the amplitude of the OPOUT output.

- 17 OPINOK Valid fiber optic input signal indicator. It is an active low, open collector LED driver. This output goes low when the signal at OPINP/N meets frequency and amplitude squelch limit for received signals at TPINP/N.

- 18 OPVCC Positive 5V power supply for fiber optic LED driver.

- 19 OPOUT Fiber optic LED driver output. The fiber optic LED connects between this pin and OPVCC.

- 20 OPGND Ground for the fiber optic LED driver.

- 21 GND1 Ground.

- 22 KEYGEN Key generation select CMOS input. This input is low for configurations 2 and 3 of the general description, and is high for configurations 1 and 4.

- 23 VDC Offset correction time constant capacitor input. An external capacitor between this pin and QGND determines the time constant of the internal offset correction circuit for the fiber optic quantizer.

- 24 QGND Quantizer's ground.

- 26, 25 OPINP/N Receive fiber inputs. This pair of inputs receive differential Manchester signals from the fiber optic receiver/preamp and present them to the on-chip fiber optic quantizer. These inputs should be capacitively coupled to the input source. The input resistance is approximately  $1.3k\Omega$ .

QVCC Quantizer's positive 5V power supply.

# ABSOLUTE MAXIMUM RATINGS

Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

| Power Supply Voltage Range, V <sub>CC</sub> | –0.3 to 6V              |

|---------------------------------------------|-------------------------|

| Input Voltage Range                         | –0.3 to V <sub>CC</sub> |

| Output Current                              |                         |

| TPOUTP, TPOUTN                              |                         |

| OPOUT                                       |                         |

| PHTM1, PHTM2                                | 10mA                    |

| Input Current                               |                         |

| RTSETTP, RTSETOP, TPINOK,                   |                         |

| OPINOK, INSERTED                            |                         |

| Storage Temperature                         | . –65°C to 150°C        |

| Lead Temperature (soldering, 10 sec.)       | 260°                    |

| Thermal Resistance                          | 68°C/W                  |

|                                             |                         |

# **OPERATING CONDITIONS**

| 5V ± 5%                   |

|---------------------------|

| of each other.            |

| h other.                  |

| 0°C to 70°C               |

| 0°C to 125°C              |

| 4mA                       |

| $115\Omega \pm 1\%$       |

| $\dots 255\Omega \pm 1\%$ |

|                           |

## **ELECTRICAL CHARACTERISTICS**

Over full range of operating conditions unless otherwise specified (Note 1).

| SYMBOL           | PARAMETER                      | CONDITIONS                                                                  | MIN                   | ТҮР | MAX                   | UNITS |

|------------------|--------------------------------|-----------------------------------------------------------------------------|-----------------------|-----|-----------------------|-------|

| POWER SU         | PPLY CURRENT                   |                                                                             |                       |     |                       |       |

| I <sub>CC1</sub> | V <sub>CC</sub> Supply Current | No transmitting, phantom power off                                          | 30                    | 36  | 50                    | mA    |

| I <sub>CC2</sub> | V <sub>CC</sub> Supply Current | RTSETTP = 255, RTSETOP = 115,<br>transmitting, phantom power on<br>(Note 2) | 120                   |     | 160                   | mA    |

| CMOS INP         | UTS PHTM1, PHTM2 (when         | KEYGEN = High or $\overline{\text{TPINOK}}$ is grounded) <b>AN</b>          | ND KEYGEN             |     |                       |       |

| V <sub>ILC</sub> | Input Low Voltage              |                                                                             |                       |     | 0.1 x V <sub>CC</sub> | V     |

| V <sub>IHC</sub> | Input High Voltage             |                                                                             | 0.9 x V <sub>CC</sub> |     |                       | V     |

| TTL INPUT        | XTAL1                          |                                                                             |                       |     |                       |       |

| V <sub>ILT</sub> | Input Low Voltage              |                                                                             |                       |     | 0.8                   | V     |

| V <sub>IHT</sub> | Input High Voltage             |                                                                             | 2                     |     |                       | V     |

| I <sub>ILT</sub> | Input Low Current              | V(XTAL1) = 0V                                                               | -100                  |     |                       | μA    |

| I <sub>IHT</sub> | Input High Current             | V(XTAL1) = 2.7V                                                             |                       |     | 100                   | μA    |

| R <sub>IX1</sub> | Input Resistance               |                                                                             | 400                   |     | 560                   | kΩ    |

| CONTROL          | INPUTS: INSERTED, TPINO        | к                                                                           |                       |     |                       |       |

| V <sub>ILS</sub> | Input Low Voltage              |                                                                             |                       |     | 0.1                   | V     |

| I <sub>ILS</sub> | Input Low Current              | $V_{IN} = 0V$                                                               | -50                   |     |                       | μA    |

| STATUS LEI       | D OUTPUTS: INSERTED, TP        | INOK, OPINOK                                                                |                       |     |                       |       |

| I <sub>OLS</sub> | Output Low Current             | Pin connected to V <sub>CC</sub>                                            | 14                    | 19  | 24                    | mA    |

| I <sub>OHS</sub> | Output Off Current             |                                                                             |                       | 3   | 10                    | μA    |

|                  |                                |                                                                             |                       |     |                       |       |

# ELECTRICAL CHARACTERISTICS (Continued)

| SYMBOL             | PARAMETER                                | CONDITIONS                                                   | MIN               | ТҮР  | MAX      | UNITS             |

|--------------------|------------------------------------------|--------------------------------------------------------------|-------------------|------|----------|-------------------|

| PHANTOM            | DRIVE OUTPUTS: PHTM1, PHT                | M2                                                           |                   |      | -        | -                 |

| R <sub>NF</sub>    | No Fault Phantom Load<br>Resistance      |                                                              | 2.9               |      | 5.5      | kΩ                |

| R <sub>SC</sub>    | Short Circuit Phantom Load<br>Resistance |                                                              |                   |      | 50       | Ω                 |

| R <sub>OC</sub>    | Open Circuit Phantom Load<br>Resistance  |                                                              | 50                |      |          | kΩ                |

| V <sub>OHP</sub>   | Phantom Output High Voltage              | I <sub>OHP</sub> > -1mA                                      | 4.1               |      |          | V                 |

|                    |                                          | I <sub>OHP</sub> > -2mA                                      | 3.5               |      |          | V                 |

| I <sub>SC</sub>    | Phantom Short Circuit Current            | V(PHTM1) or V(PHTM2) = 0V                                    |                   | -1.8 | -1.2     | mA                |

| I <sub>OFFP</sub>  | Phantom Off Current                      | V(PHTM1) or V(PHTM2) = 0V                                    | -100              |      | 100      | μΑ                |

| WISTED P           | AIR RECEIVER: TPINP, TPINN               |                                                              |                   |      |          |                   |

| V <sub>OSRTP</sub> | Differential Offset Voltage              |                                                              | -35               |      | 35       | mV                |

| V <sub>DSTP</sub>  | Differential Squelch Threshold           |                                                              | 200               |      | 300      | mV <sub>P-P</sub> |

| V <sub>PSTP</sub>  | Differential Post-Squelch<br>Threshold   |                                                              | 100               |      | 150      | mV <sub>P-P</sub> |

| V <sub>CMTP</sub>  | Open-Circuit Common Mode<br>Bias Voltage |                                                              |                   | 2.4  |          | V                 |

| R <sub>IDRTP</sub> | Differential Input Resistance            |                                                              | 8                 | 9.6  | 12.5     | kΩ                |

| TWISTED P          | AIR TRANSMITTER: TPOUTP, TH              | POUTN                                                        |                   |      | <b>I</b> |                   |

| I <sub>TTP</sub>   | Peak Output Current                      |                                                              | 27                |      | 29.5     | mA                |

| I <sub>OFFTP</sub> | Off State Output Current                 | RTSETTP = $255\Omega$ ,<br>Pins Connected to V <sub>CC</sub> |                   |      | 1.5      | mA                |

| I <sub>DCI</sub>   | Differential Current Im Balance          |                                                              | -300              |      | 300      | μΑ                |

| OPTICAL R          | ECEIVER: OPINP, OPINN                    |                                                              |                   |      |          |                   |

| V <sub>CMOP</sub>  | Open Circuit Common Mode<br>Bias Voltage |                                                              |                   | 1.6  |          | V                 |

| V <sub>IROP</sub>  | Input Signal Range                       |                                                              | V <sub>DSOP</sub> |      | 1600     | mV <sub>P-P</sub> |

| V <sub>OSROP</sub> | Differential Offset Voltage              |                                                              |                   | 3    |          | mV                |

| EN                 | Input Referred Voltage Noise             | 50MHz BW                                                     |                   | 25   |          | μV <sub>RMS</sub> |

| R <sub>IDROP</sub> | Differential Input Resistance            |                                                              | 1.8               | 2.6  | 3.3      | kΩ                |

| V <sub>DSOP</sub>  | Differential Squelch Threshold           |                                                              | 5                 |      | 6        | mV <sub>P-P</sub> |

| V <sub>PSOP</sub>  | Differential Post Squelch<br>Threshold   |                                                              | 4                 |      | 5        | mV <sub>P-P</sub> |

| Н                  | Hysteresis                               |                                                              |                   | 20   |          | %                 |

| OPTICAL T          | RANSMITTER: OPOUT                        |                                                              |                   |      | 1        | I                 |

| I <sub>TOP</sub>   | Peak Output Current                      | RTSETOP = 115Ω                                               | 47                | 52   | 57       | mA                |

| IOFFOP             | Off State Output Current                 |                                                              |                   |      | 1        | mA                |

# AC CHARACTERISTICS

Over full range of operating conditions unless otherwise specified. (Note 1)

| SYMBOL             | PARAMETER                                                                                             | CONDITIONS                                                                   | MIN  | ТҮР  | MAX  | UNITS |

|--------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------|------|------|-------|

| CLOCK REF          | ERENCE: XTAL1                                                                                         | · ·                                                                          |      | 1    | I    | 1     |

| f <sub>XO</sub>    | Reference Clock Frequency                                                                             |                                                                              | 32.7 |      | 34.5 | kHz   |

| D <sub>XO</sub>    | Reference Clock Duty Cycle                                                                            |                                                                              | 30   |      | 70   | %     |

| TWISTED P          | AIR RECEIVER: TPINP, TPINN                                                                            | · ·                                                                          |      | 1    |      | 1     |

| t <sub>THTP</sub>  | Input Pulse Width Threshold                                                                           |                                                                              | 550  |      | 1000 | ns    |

| t <sub>USQTP</sub> | Time to Unsquelch (Off to On)                                                                         |                                                                              | 2    |      | 5    | μs    |

| t <sub>REJTP</sub> | Time to Reject (On to Off)                                                                            |                                                                              | 550  |      | 1000 | ns    |

| OPTICAL R          | ECEIVER: OPINP, OPINN                                                                                 | · ·                                                                          |      |      | 1    | 1     |

| t <sub>THOP</sub>  | Input Pulse Width Threshold                                                                           | V(INSERTED) > 0.7V                                                           | 550  |      | 1000 | ns    |

| t <sub>USQOP</sub> | Time to Unsquelch (Off to On)                                                                         | V(INSERTED) > 0.7V                                                           | 3    |      | 9    | μs    |

|                    |                                                                                                       | V(INSERTED) = 0V                                                             | 0.8  |      | 1.2  | μs    |

| t <sub>REJOP</sub> | Time to Reject (On to Off)                                                                            | V(INSERTED) > 0.7V                                                           | 3    |      | 9    | μs    |

|                    |                                                                                                       | V(INSERTED) = 0V                                                             | 0.8  |      | 1.2  | μs    |

| PROPAGAT           | TION DELAYS STEADY STATE                                                                              | · · · · · · · · · · · · · · · · · · ·                                        |      |      | I    | 1     |

| t <sub>TPOP</sub>  | TPINP-TPINN to OPOUT                                                                                  |                                                                              |      |      | 20   | ns    |

| t <sub>OPTP</sub>  | OPINP-OPINN to<br>TPOUTP-TPOUTN                                                                       |                                                                              |      |      | 30   | ns    |

| t <sub>TPTP</sub>  | TPINP-TPINN to<br>TPOUTP-TPOUTN                                                                       |                                                                              |      |      | 30   | ns    |

| t <sub>OPOP</sub>  | OPINP-OPINN to OPOUT                                                                                  |                                                                              |      |      | 20   | ns    |

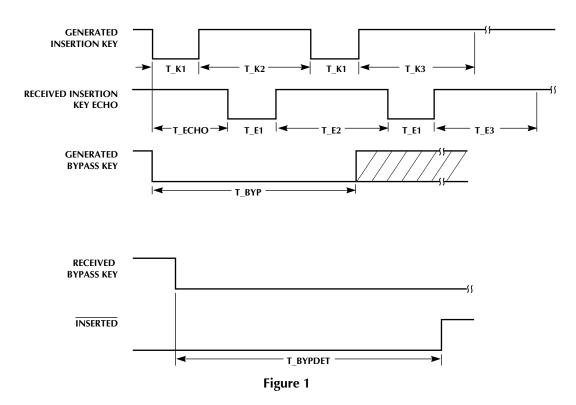

| NSERTION           | AND BYPASS KEY GENERATIO                                                                              | N (Fig. 1)                                                                   |      |      | 1    |       |

| T_K1               | Key Element #1<br>(avg. $P_O < P_{O_Off}$ )                                                           |                                                                              | 808  |      | 858  | μs    |

| T_K2               | Key Element #2<br>(avg. $P_O > P_{O_Off}$ )                                                           |                                                                              | 1616 |      | 1717 | μs    |

| T_K3               | Key Element #3<br>(avg. P <sub>O</sub> < P <sub>O_Off</sub> )                                         |                                                                              | 1616 |      |      | μs    |

| T_BYP              | Bypass Element<br>(avg. P <sub>O</sub> > P <sub>O_Off</sub> )                                         |                                                                              | 4.85 | 26.5 |      | ms    |

| T_KINIT1           | Time that phantom power<br>should be applied in config 1<br>before generating the insertion<br>key.   | V(KEYGEN) = V <sub>CC</sub> , V(TPINOK) > 0.7V                               |      | 26.5 |      | ms    |

| T_KINIT4           | Time that the optical input<br>should be valid in config 4<br>before generating the insertion<br>key. | V(KEYGEN) = V <sub>CC</sub> , V(TPINOK) = 0V<br>V(PHTM1) = 0V, V(PHTM2) = 0V |      | 26.5 |      | ms    |

| T_KOFF             | Time that the optical input<br>should be invalid before<br>generating the bypass key.                 | V(KEYGEN) = VCC, V(TPINOK) = 0V<br>V(PHTM1) = 0V, V(PHTM2) = 0V              |      | 26.5 |      | ms    |

# AC CHARACTERISTICS (continued)

| SYMBOL    | PARAMETER                                                                                  | CONDITIONS | MIN  | ТҮР | MAX  | UNITS |  |  |

|-----------|--------------------------------------------------------------------------------------------|------------|------|-----|------|-------|--|--|

| INSERTION | INSERTION KEY ECHO AND BYPASS KEY RECOGNITION (Fig. 1)                                     |            |      |     |      |       |  |  |

| T_ECHO    | Time since starting insertion<br>key generation until receiving<br>the insertion key echo. |            |      |     | 100  | ms    |  |  |

| T_E1Key   | Key Echo From T_K1                                                                         |            | 766  |     | 900  | μs    |  |  |

| T_E2Key   | Key Echo From T_K2                                                                         |            | 1533 |     | 1800 | μs    |  |  |

| T_E3Key   | Key Echo From T_K3                                                                         |            | 1533 |     |      | μs    |  |  |

| T_BYPDET  | Time of optical input not valid before recognizing a bypass key                            |            | 4    |     | 4.5  | ms    |  |  |

Note 1: Limits are guaranteed by 100% testing, sampling, or correlation with worst-case test conditions.

Note 2: Current into all V<sub>CC</sub> pins, external bias resistors, and external transmit loads. Does not include status LED's current.

# FUNCTIONAL DESCRIPTION

#### **Fiber Optic LED Driver**

The output stage of the transmitter is a current mode switch which develops the output light by sinking current from OPVCC through the LED into the OPOUT pin. Once the current requirement for the LED is determined, the RTSETOP resistor is selected. The following equation is used to select the correct RTSETOP resistor:

#### $RTSETOP = (52mA/I_{OUT}) \times 115\Omega$

No current is provided during the off cycles of the Insertion, Bypass, or Echo Keys, or when the input signal that should be routed to the Fiber Optic LED Driver does not meet the corresponding input squelch requirements.

#### **Fiber Optic Quantizer**

The OPINP, OPINN input signal is fed into a limiting amplifier with a gain of about 100 and input resistance of  $1.3k\Omega$ . Maximum sensitivity is achieved through the use of a DC restoration feedback loop and AC coupling the input. When AC coupled, the input DC bias voltage is set by an on-chip network at about 1.7V. These coupling capacitors, in conjunction with the input impedance of the amplifier, establish a high pass filter with 3dB corner frequency,  $f_L$ , at

$$f_L = 1/(2 \times \pi \times 1300 \times C)$$

Since the amplifier has a differential input, two capacitors of equal value are required. If the signal driving the input is single ended, one of the coupling capacitors can be tied to  $V_{CC}$ . The internal amplifier has a lowpass filter built-in to band limit the input signal which in turn will improve the signal to noise ratio. Although the input is AC coupled, the offset voltage,  $V_{OS}$ , within the amplifier will be present at the amplifier's output. In order to reduce this error a DC feedback loop nulls the offset voltage, forcing  $V_{OS}$  to be zero. The comparator is a high-speed differential zero crossing detector that slices and accurately digitizes the receive signal. The output of the comparator is fed in parallel into both the fiber optic squelch circuit and the signal MUX. The capacitor between pin VDC and QGND should be set to 500pF.

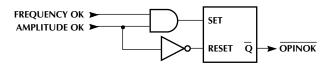

#### **Fiber Optic Squelch**

The ML6680 monitors the frequency and amplitude of the input from a fiberoptic receiver. The optical squelch circuit rejects signals whose frequencies are lower than 1MHz or whose amplitudes are lower than -32dBm.

If both requirements are met, the LED output  $\overline{OPINOK}$  goes low, and the amplitude threshold is lowered 20%.

#### **Copper Pair Driver**

The output stage of the twisted pair transmitter is a current mode switch which develops the output voltage by driving current through the terminating resistor and the output filter. The harmonic content is controlled to simplify the filter design. The transmitter employs a center tap 2:1 transformer where the center tap is tied to  $V_{CC}$ . While one pin of the transmit pair is pulled low, the other pin floats. The output pins to the twisted pair wires, TPOUTP and TPOUTN, can drive shielded or unshielded twisted pair cable through the appropriate isolation transformer. The output current is set by the value of RTSETTP. No transitions are generated at TPOUTP and TPOUTN when the input signal that should be routed to the Copper Pair Driver does not meet the corresponding input squelch requirements. PECL compatible output are obtained with an external network of 3 resistors. In this case the current of the output stage can be reduced by adjusting the value of RTSETTP.

#### Twisted Pair Line Equalizer

The receive equalizer compensates for twisted pair cable dispersion, which otherwise would give rise to inter-symbol interference (ISI). The amount of equalization varies with the average amplitude of the received signal. The received signal amplitude gives a rough value for the length of the attached cable. The filter/equalizer characteristic is the inverse of the cable's dispersion characteristic. Both UTP and STP cables approximate a low-pass filter, so the filter/ equalizer approximates an inverse square root equalizer. Two external resistors and one external capacitors are required between pins EQA and EQB. The output of the equalizer is fed into the signal MUX. On a PECL application these pins should be connected between each other.

#### **Twisted Pair Squelch Circuit**

The twisted pair line receiver internally sets the common mode bias of the input TPINP and TPINN. Voltage offset comparators are used to set the amplitude squelch threshold, and analog timers are used to set the pulse width squelch threshold. When the input signal meets amplitude and pulse width requirements, the squelch circuit reduces the offset voltage of the comparators, decreasing the amplitude squelch threshold by half. This hysteresis allows the receiver to stay on in the presence of a fading input signal. The twisted pair squelch circuit rejects signals whose frequencies are lower than 1MHz or whose amplitudes are lower than 300mV<sub>P-P</sub>. If both requirements are met, the LED output TPINOK goes low.

#### **Clock Oscillator**

The ML6680 provides an on-chip clock oscillator by connecting a 32.768kHz watch crystal between pins XTAL1 and XTAL2. The part can also be driven by an external clock applied at XTAL1 and tying XTAL2 to ground. The frequency of the external clock should be between 32.7kHz and 34.5kHz.

#### **Status LED Drivers**

The ML6680 has three status LED drivers. The LED driver pins are active low. The LED's are tied to their respective pins through a  $300\Omega$  resistor to V<sub>CC</sub>.

# Micro Linear

#### **Modes of Operation**

Four configurations are possible with the ML6680, as follows:

- 1. Standard Media Converter: Senses ISO/IEC8802-5 phantom power and generates ISO/IEC8802-5 fiberoptic insertion or bypass requests.

- 2. Concentrator Media Converter: Recognizes the ISO/ IEC8802-5 fiberoptic insertion or bypass requests and drives the ISO/IEC8802-5 phantom circuits.

- 3. Lobe or Ring Out Port Media Converter: Recognizes the ISO/IEC8802-5 fiberoptic insertion or bypass requests.

- 4. Ring In Port Media Converter: Generates ISO/ IEC8802-5 fiberoptic insertion or bypass requests. Modifies the internal signal paths depending on the presence or absence of a fiberoptic link, and on the reception of the ISO/IEC8802-5 "Insertion Key Echo."

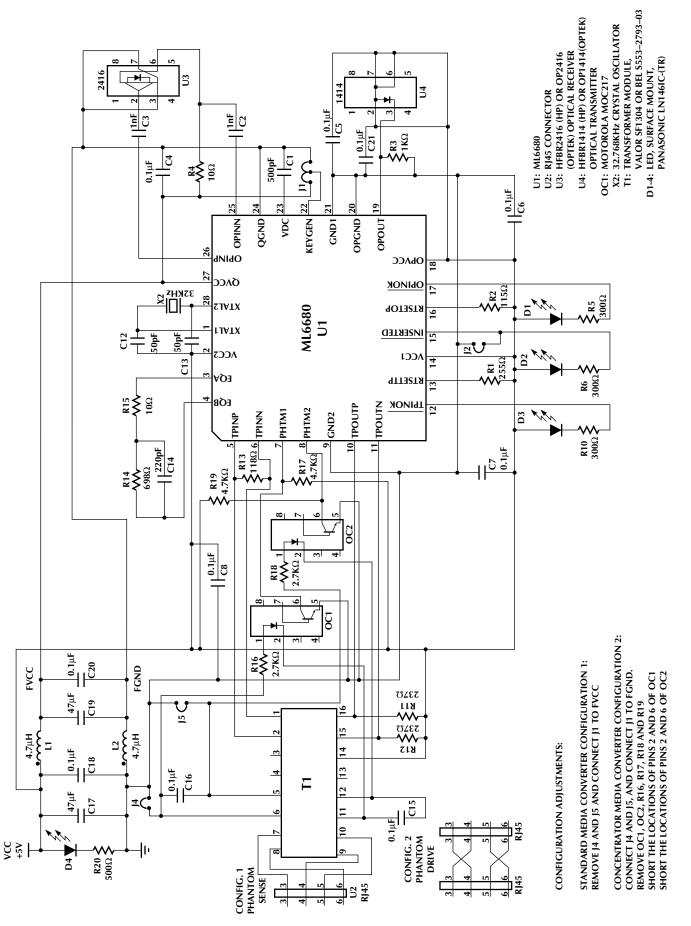

### **CONFIGURATION 1**

#### Standard Media Converter:

This configuration is selected by tying KEYGEN to VCC. There are always two fixed signal paths, one from TPINP and TPINN to OPVCC and OPOUT, and another from OPINP and OPINN to TPOUTP and TPOUTN. The generation of the "Insertion Key" or "Bypass Key" is exclusively controlled by the logic values at PHTM1 and PHTM2. The "Insertion Key" is generated when both PHTM1 and PHTM2 go low, and stay low for at least 26.5ms. If the "Insertion Key Echo" is received within the following 100ms, the part goes to the "Insert State" and the LED output INSERTED goes low. During the generation of the "Insertion Key," and while waiting for the "Insertion Key Echo" the states of PHTM1 and PHTM2 do not have any effect. When the part is in the "Insert State" and either PHTM1 or PHTM2 goes high, the LED output **INSERTED** goes high, the part leaves the "Insert State," generates the "Bypass Key," and starts waiting for PHTM1 and PHTM2 to go low again.

### **CONFIGURATION 2**

#### **Concentrator Media Converter:**

This configuration is selected by tying KEYGEN to ground. There are always two fixed signal paths, one from TPINP and TPINN to OPVCC and OPOUT, and another from OPINP and OPINN to TPOUTP and TPOUTN. The part powers on in the "Bypass State" where it neither applies phantom current nor checks for a phantom wire fault. After recognizing an "Insertion Key" at its fiber optic inputs, it applies phantom power by providing current at PHTM1 and PHTM2, goes to the "Phantom Wire Fault Check State," and starts waiting for a "Bypass Key." At this state, the LED output INSERTED stays low while no phantom wire fault is detected. When the part is in the "Phantom Wire Fault Check State" and a "Bypass Key" is recognized, the part leaves this state, removes the phantom power, and starts waiting for a "Insertion Key" again.

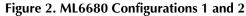

# **CONFIGURATION 3**

#### Lobe or Ring Out Port Media Converter:

This configuration is selected by tying both KEYGEN and TPINOK to ground. When the ML6680 is in the "Insert State," the signal paths are from TPINP and TPINN to OPVCC and OPOUT, and from OPINP and OPINN to TPOUTP and TPOUTN. Otherwise, the signal paths are from TPINP and TPINN to TPOUTP and TPOUTN, and from OPINP and OPINN to OPVCC and OPOUT. The part powers on in the "Bypass State" and goes to the "Insert State" after recognizing an "Insertion Key" at its fiber optic inputs. It goes back to the "Bypass State" after recognizing a "Bypass Key." While it is at the "Insert State," the LED output INSERTED stays low.

## **CONFIGURATION 4**

#### Ring In Port Media Converter:

This configuration is selected by tying KEYGEN to VCC and TPINOK to ground. When the part is in the "Insert State," the signal paths are from TPINP and TPINN to OPVCC and OPOUT, and from OPINP and OPINN to TPOUTP and TPOUTN. Otherwise, the input at TPINP and TPINN is routed to TPOUTP and TPOUTN, and also to OPVCC and OPOUT. The "Insertion Key" is generated when activity is detected at OPINP and OPINN for at least 26.5ms and, PHTM1 and PHTM2 stay low. If the "Insertion Key Echo" is received within the following 100ms, the ML6680 goes to the "Insert State" and the LED output **INSERTED** goes low. During the generation of the "Insertion Key," and while waiting for the "Insertion Key Echo" the logic states of PHTM1 and PHTM2 do not have any effect. When the part is in the "Insert State" and no activity is detected at OPINP and OPINN for at least 26.5ms, or either PHTM1 or PHTM2 goes high, the LED output **INSERTED** goes high, the part leaves the "Insert State," generates the "Bypass Key," and starts waiting for 26.5ms of optical input activity again.

#### Low Frequency Signaling Mode

Some old implementations of discrete media converters, use a non-standard protocol with frequencies between 1 and 10kHz. To facilitate the migration to the ML6680, a specific operating mode is provided by grounding the pin INSERTED. Pin KEYGEN should also be grounded to prevent the generation of unwanted "Insertion" or "Bypass Keys." In this operating mode, the optical frequency squelch circuitry is disabled and the time constant of the amplitude squelch is significantly reduced.

For each edge of the low frequency optical input, the ML6680 generates a pulse at the led output OPINOK. It also generates a pulse at the TPOUTP output for each rising edge and another at the TPOUTN output for each falling edge.

# ML6680

Micro Linear

Downloaded from Elcodis.com electronic components distributor

Figure 3. ML6680 Configurations 3 and 4

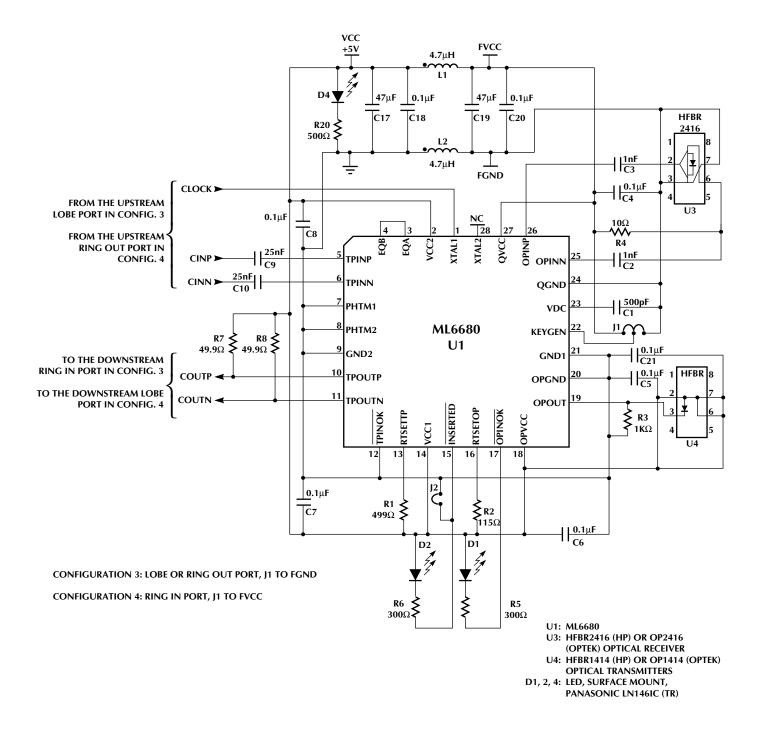

### **PHYSICAL DIMENSIONS** inches (millimeters)

# **ORDERING INFORMATION**

| PART NUMBER | TEMPERATURE RANGE | PACKAGE           |  |  |

|-------------|-------------------|-------------------|--|--|

| ML6680CQ    | 0°C to 70°C       | 28-PIN PLCC (Q28) |  |  |

© Micro Linear 1997 Bicro Linear is a registered trademark of Micro Linear Corporation

Products described in this document may be covered by one or more of the following patents, U.S.: 4,897,611; 4,964,026; 5,027,116; 5,281,862; 5,283,483; 5,418,502; 5,508,570; 5,510,727; 5,523,940; 5,546,017; 5,559,470; 5,556,761; 5,592,128; 5,594,376; Japan: 2598946; 2619299. Other patents are pending.

Micro Linear reserves the right to make changes to any product herein to improve reliability, function or design. Micro Linear does not assume any liability arising out of the application or use of any product described herein, neither does it convey any license under its patent right nor the rights of others. The circuits contained in this data sheet are offered as possible applications only. Micro Linear makes no warranties or representations as to whether the illustrated circuits infringe any intellectual property rights of others, and will accept no responsibility or liability for use of any application herein. The customer is urged to consult with appropriate legal counsel before deciding on a particular application.

2092 Concourse Drive San Jose, CA 95131 Tel: 408/433-5200 Fax: 408/432-0295