# 2ilas

PRELIMINARY CUSTOMER PROCUREMENT SPECIFICATION

# **Z86217/C17** CMOS Z8<sup>®</sup> 8-BIT MICROCONTROLLERS (POINTING DEVICE/TRACKBALL)

# FEATURES

| Part   | ROM      | RAM*    | I/O   | Speed |

|--------|----------|---------|-------|-------|

| Number | (Kbytes) | (Bytes) | Lines | (MHz) |

| Z86217 | 2        | 124     | 14    | 4     |

| Z86C17 | 2        | 124     | 14    | 4     |

\* General-Purpose

- 18-Pin DIP and SOIC Packages

- 3.0- to 5.5-Volt Operating Range

- 0°C to 70°C Operating Temperature Range

- Permanent Watch-Dog Timer (WDT)

- Oscillator Filter

- Two Programmable 8-Bit Counter/Timers

- Low-EMI Operation

- Scalable Trip-Point Buffer

- On-Board Pull-Up Resistors

- High Drive Ports Can Sink 20 mA Per Pin, with Three Pins Maximum

# **GENERAL DESCRIPTION**

The Z86217/C17 are members of Zilog's Z8<sup>®</sup> family of microcontrollers designed to reduce external system components and offer easy software/hardware development tools for pointing device and trackball applications.

The devices feature on-board pull-up resistors, and a scalable trip-point buffer to accommodate opto-transistor outputs. The high drive ports are capable of up to 20 mA (at  $V_{OL} = 0.8$ -volt) current sinking per pin, with three pins maximum, providing extra sinking current capability.

The Z86217/C17's permanently enabled Watch-Dog Timer (WDT) operates upon power-up of the MCU, and provides added operational reliability for pointing device and trackball environments.

An oscillator filter assists in separating out high-frequency noise from the oscillator input pin.

Two on-chip counter/timers with a large number of selectable modes, offload the system of administering real-time tasks such as counting/timing and I/O data communications.

Notes:

Refer to the DC electrical characteristics for detailed specification of the sinking current.

On the Z86C17, P24-P27 has a 20K pull-up, and P32 has a 47K pulldown. The Z86217 does not have these functions.

All Signals with a preceding front slash, "/", are active Low, e.g.; B//W (WORD is active Low); /B/W (BYTE is active Low, only).

Power connections follow conventional descriptions below:

| Connection | Circuit         | Device          |  |  |

|------------|-----------------|-----------------|--|--|

| Power      | V <sub>CC</sub> | V <sub>DD</sub> |  |  |

| Ground     | GND             | V <sub>SS</sub> |  |  |

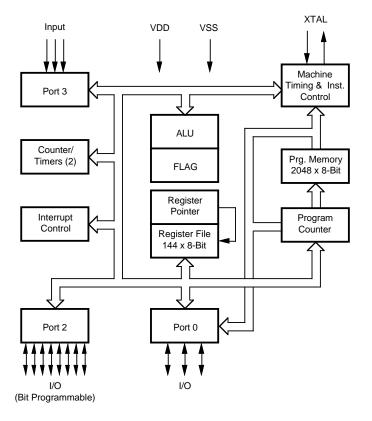

# **BLOCK DIAGRAM**

**Functional Block Diagram**

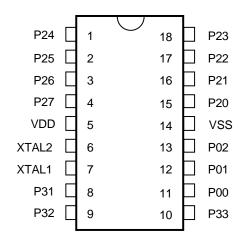

## **PIN DESCRIPTIONS**

## **18-Pin SOIC Configuration**

# **ABSOLUTE MAXIMUM RATINGS**

| Sym              | Parameter          | Min  | Мах   | Units |

|------------------|--------------------|------|-------|-------|

| V <sub>dd</sub>  | Supply Voltage (*) | -0.3 | +7    | V     |

| T <sub>stg</sub> | Storage Temp       | -65° | +150° | C     |

| T <sub>A</sub>   | Oper Ambient Temp  | †    | †     | C     |

Notes:

\* Voltages on all pins with respect to GND

† See Ordering Information

# STANDARD TEST CONDITIONS

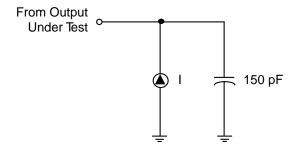

The characteristics listed below apply for standard test conditions as noted. All voltages are referenced to GND. Positive current flows into the referenced pin (Test Load).

Stress greater than those listed under Absolute Maximum

#### **Test Load Diagram**

## CAPACITANCE

$T_{A} = GND = 0V$ , f = 1.0 MHz, unmeasured pins to GND

| Parameter          | Мах   |

|--------------------|-------|

| Input capacitance  | 10 pF |

| Output capacitance | 20 pF |

| I/O capacitance    | 25 pF |

# V<sub>dd</sub> SPECIFICATION

$V_{dd} = 3.0V \text{ to } 5.5V$

# DC ELECTRICAL CHARACTERISTICS

| Symbol           | Parameter                                         | V <sub>DD</sub> | T <sub>A</sub> = 0°C<br>Min | to +70°C Typical<br>Max @ 25°C |      | Units  | Conditions                                       |  |

|------------------|---------------------------------------------------|-----------------|-----------------------------|--------------------------------|------|--------|--------------------------------------------------|--|

|                  | Max Input Voltage                                 | 3.0V<br>5.5V    |                             | 12<br>12                       |      | V<br>V | $V_{IN} = 250 \ \mu A$<br>$V_{IN} = 250 \ \mu A$ |  |

| V <sub>CH</sub>  | Clock Input High<br>Voltage                       | 3.0V            | 0.7 V <sub>DD</sub>         | V <sub>DD</sub> + 0.3          | 2.0  | V      | Driven by External<br>Clock Generator            |  |

|                  |                                                   | 5.5V            | 0.7 V <sub>DD</sub>         | $V_{DD} + 0.3$                 | 3.0  | V      | Driven by External<br>Clock Generator            |  |

| V <sub>CL</sub>  | Clock Input Low<br>Voltage                        | 3.0V            | V <sub>SS</sub> – 0.3       | $0.2 V_{DD}$                   | 0.8  | V      | Driven by External<br>Clock Generator            |  |

|                  | C C                                               | 5.5V            | V <sub>SS</sub> – 0.3       | $0.2 V_{DD}$                   | 1.5  | V      | Driven by External<br>Clock Generator            |  |

| V <sub>IH</sub>  | Input High Voltage                                | 3.0V            | $0.7 V_{DD}$                | $V_{DD} + 0.3$                 | 1.6  | V      |                                                  |  |

|                  | Schmitt-Triggered                                 | 5.5V            | 0.7 V <sub>DD</sub>         | $V_{DD} + 0.3$                 | 2.6  | V      |                                                  |  |

| $V_{\rm IH}$     | Input High Voltage                                | 3.0V            | 0.7 V <sub>DD</sub>         | $V_{DD} + 0.3$                 | 1.4  | V      |                                                  |  |

|                  | CMOS Input                                        | 5.5V            | 0.7 V <sub>DD</sub>         | $V_{DD} + 0.3$                 | 2.6  | V      |                                                  |  |

| V <sub>IL</sub>  | Input Low Voltage                                 | 3.0V            | V <sub>SS</sub> – 0.3       | 0.2 V <sub>DD</sub>            | 1.4  | V      |                                                  |  |

|                  | Schmitt-Triggered                                 | 5.5V            | V <sub>SS</sub> – 0.3       | $0.2 V_{DD}$                   | 2.6  | V      |                                                  |  |

| V <sub>IL</sub>  | Input Low Voltage                                 | 3.0V            | V <sub>SS</sub> – 0.3       | 0.2 V <sub>DD</sub>            | 1.3  | V      |                                                  |  |

|                  | CMOS Input                                        | 5.5V            | V <sub>SS</sub> - 0.3       | $0.2 V_{DD}$                   | 2.4  | V      |                                                  |  |

| $V_{OH}$         | Output High Voltge                                | 3.0V            | $V_{DD} - 0.4$              |                                | 2.8  | V<br>V | $I_{OH} = -2.0 \text{ mA}$                       |  |

|                  |                                                   | 5.5V            | V <sub>DD</sub> - 0.4       |                                | 5.5  |        | $I_{OH} = -2.0 \text{ mA}$                       |  |

| V <sub>OL1</sub> | Output Low Voltage                                | 3.0V            |                             | 0.4                            | 0.13 | V      | $I_{OL} = +4.0 \text{ mA}$                       |  |

|                  |                                                   | 5.5V            |                             | 0.4                            | 0.07 | V      | $I_{OL}^{OL} = +4.0 \text{ mA}$                  |  |

| V <sub>OL2</sub> | Output Low Voltage                                | 3.0V            |                             | 1.5                            | 0.8  | V      | I <sub>OL</sub> = 20.0 mA,<br>3 Pin Max          |  |

|                  |                                                   | 5.5V            |                             | 0.8                            | 0.3  | V      | I <sub>OL</sub> = 20.0 mA,<br>3 Pin Max          |  |

| V <sub>LV</sub>  | V <sub>CC</sub> Low Voltage<br>Protection Voltage |                 |                             | 2.7                            | 2.3  | V      | @ 2 MHz Max                                      |  |

| V <sub>TP</sub>  | Trip Point<br>Voltage                             | 3.0V<br>5.5V    |                             | $0.4 V_{DD}$                   |      | V      |                                                  |  |

|                  | Input Leakage                                     | 3.0V            | -1.0                        | 1.0                            |      | μA     | $V_{IN} = OV, V_{CC}$                            |  |

| IL               | 1                                                 | 5.5V            | -1.0                        | 1.0                            | 0.4  | μA     | $V_{IN} = OV, V_{CC}$                            |  |

| I <sub>OL</sub>  | Output Leakage                                    | 3.0V            | -1.0                        | 1.0                            | 0.4  | μA     | $V_{IN} = OV, V_{CC}$                            |  |

| 22               |                                                   | 5.5V            | -1.0                        | 1.0                            |      | μA     | $V_{IN} = OV, V_{CC}$                            |  |

#### Note:

For 2.75V operating, the device operates down to  $V_{LV}$ . The minimum operational  $V_{DD}$  is determined on the value of the voltage  $V_{LV}$  at the ambient temperature. The  $V_{LV}$  increases as the temperature decreases.

<u> Azilos</u>

| Sym              | Parameter           | V <sub>DD</sub> | T <sub>A</sub> = 0°C<br>Min | to +70°C<br>Max | Typical<br>@ 25°C | Units    | Conditions                                                        |

|------------------|---------------------|-----------------|-----------------------------|-----------------|-------------------|----------|-------------------------------------------------------------------|

| I <sub>DD</sub>  | Supply Current      | 3.0V            |                             | 1.5             | 0.41              | mA       | All Output and I/OPins<br>Floating @ 1 MHz                        |

|                  |                     | 5.5V            |                             | 3.0             | 1.44              | mA       | All Output and I/O Pins<br>Floating @ 1 MHz                       |

|                  |                     | 3.0V            |                             | 2.0             | 0.93              | mA       | All Output and I/O Pins<br>Floating @ 2 MHz                       |

|                  |                     | 5.5V            |                             | 4.0             | 2.60              | mA       | All Output and I/O Pins<br>Floating @ 2 MHz                       |

|                  |                     | 3.0V            |                             | 3.0             | 1.64              | mA       | All Output and I/O Pins<br>Floating @ 4 MHz                       |

|                  |                     | 5.5V            |                             | 6.0             | 4.28              | mA       | All Output and I/O Pins<br>Floating @ 4 MHz                       |

| I <sub>DD1</sub> | Standby Current     | 3.0V            |                             | 0.6             | 0.15              | mA       | HALT Mode V <sub>IN</sub> = 0V,<br>V <sub>CC</sub> @ 1 MHz        |

|                  |                     | 5.5V            |                             | 1.3             | 0.70              | mA       | HALT Mode V <sub>IN</sub> = 0V,<br>V <sub>CC</sub> @ 1 MHz        |

|                  |                     | 3.0V            |                             | 0.8             | 0.20              | mA       | HALT Mode V <sub>IN</sub> = 0V,<br>V <sub>CC</sub> @ 2 MHz        |

|                  |                     | 5.5V            |                             | 1.5             | 0.80              | mA       | HALT Mode V <sub>IN</sub> = 0V,<br>V <sub>CC</sub> @ 2 MHz        |

|                  |                     | 3.0V            |                             | 1.0             | 0.3               | mA       | HALT Mode $V_{IN} = 0V$ ,<br>$V_{CC} @ 4 MHz$                     |

|                  |                     | 5.5V            |                             | 2.0             | 1.0               | mA       | HALT Mode V <sub>IN</sub> = 0V,<br>V <sub>CC</sub> @ 4 MHz        |

| I <sub>DD2</sub> | Standby Current     | 3.0V            |                             | 200             | 120               | μΑ       | STOP Mode $V_{IN} = 0V$ ,<br>$V_{CC}$ WDT is Running              |

|                  |                     | 5.5V            |                             | 200             | 120               | μΑ       | STOP Mode V <sub>IN</sub> = OV,<br>V <sub>cc</sub> WDT is Running |

| I <sub>PU</sub>  | Pull-Up Current     |                 |                             |                 |                   |          |                                                                   |

|                  | Port P20-P23 (100K) | 3.0V            |                             | -35             | -13               | μA       |                                                                   |

|                  |                     | 5.5V            |                             | -100            | -57               | μA       |                                                                   |

|                  | Port P24-P27* (20K) | 3.0V            |                             | -100            | -58               | μA       |                                                                   |

|                  | Port P00-P03        | 5.5V<br>3.0V    |                             | -400<br>-35     | -270<br>-13       | μA       |                                                                   |

|                  | Port P31, P33       | 3.0V<br>5.5V    |                             | -35<br>-100     | -13<br>-56        | μΑ<br>μΑ |                                                                   |

| I <sub>PD</sub>  | Pull-Down Current   | 3.0V            |                             | 80              | 40                | μA       |                                                                   |

|                  | Port P32* (47K)     | 5.5V            |                             | 250             | 160               | μA       |                                                                   |

#### Note:

\*Available on the Z86C17 only.

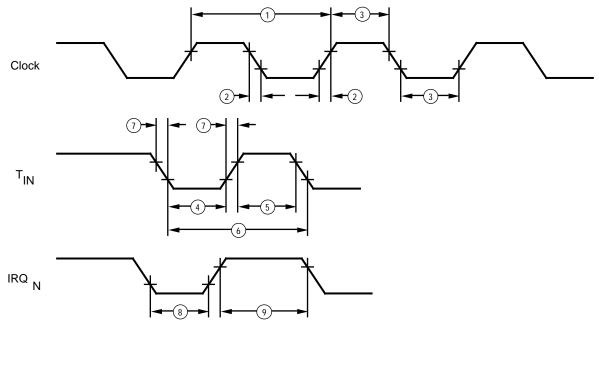

# **AC ELECTRICAL CHARACTERISTICS**

|    |                  | <b>_</b> .             | $T_A = 0^{\circ}C \text{ to } + 70^{\circ}C$ |        |         |        |         |       |       |

|----|------------------|------------------------|----------------------------------------------|--------|---------|--------|---------|-------|-------|

|    |                  |                        |                                              |        | ЛНZ     |        |         |       |       |

| NO | Symbol           | Parameter              | V <sub>DD</sub>                              | Min    | Мах     | Min    | Max     | Units | Notes |

| 1  | ТрС              | Input Clock Period     | 3.0V                                         | 1,000  | 100,000 | 250    | 100,000 | ns    | [1]   |

|    |                  |                        | 5.5V                                         | 1,000  | 100,000 | 250    | 100,000 | ns    | [1]   |

| 2  | TrC,TfC          | Clock Input Rise       | 3.0V                                         |        | 25      |        | 25      | ns    | [1]   |

|    |                  | and Fall Times         | 5.5V                                         |        | 25      |        | 25      | ns    |       |

| 3  | TwC              | Input Clock Width      | 3.0V                                         |        | 475     |        | 100     | ns    | [1]   |

|    |                  |                        | 5.5V                                         |        | 475     |        | 100     | ns    | [1]   |

| 4  | TwTinL           | Timer Input Low Width  | 3.0V                                         |        | 100     |        | 100     | ns    | [1]   |

|    |                  |                        | 5.5V                                         |        | 70      |        | 70      | ns    | [1]   |

| 5  | TwTinH           | Timer Input High Width | 3.0V                                         | 2.5TpC |         | 2.5TpC |         |       | [1]   |

|    |                  |                        | 5.5V                                         | 2.5TpC |         | 2.5TpC |         |       | [1]   |

| 6  | TpTin            | Timer Input Period     | 3.0V                                         | 4TpC   |         | 4TpC   |         |       | [1]   |

|    |                  |                        | 5.5V                                         | 4TpC   |         | 4TpC   |         |       | [1]   |

| 7  | TrTin,           | Timer Input Rise       | 3.0V                                         |        | 100     |        | 100     | ns    | [1]   |

|    | TtTin            | and Fall Timer         | 5.5V                                         |        | 100     |        | 100     | ns    | [1]   |

| 8  | TwIL             | Int. Request Input     | 3.0V                                         | 100    |         | 100    |         | ns    | [1,2] |

|    |                  | Low Time               | 5.5V                                         | 70     |         | 70     |         | ns    | [1,2] |

| 9  | TwIH             | Int. Request Input     | 3.0V                                         | 2.5TpC |         | 2.5TpC |         |       | [1]   |

|    |                  | High Time              | 5.5V                                         | 2.5TpC |         | 2.5TpC |         |       | [1,2] |

| 10 | Twdt             | Watch-Dog Timer        | 3.0V                                         | 25     |         | 25     |         | ms    | [1]   |

|    |                  | Time Out Timer         | 5.5V                                         | 10     |         | 10     |         | ms    | [1]   |

| 11 | T <sub>POR</sub> | Power-On Reset         | 3.0V                                         | 6      |         | 6      |         | ms    | [1]   |

|    |                  | Time                   | 5.5V                                         | 2      |         | 2      |         | ms    | [1]   |

Notes:

[1] Timing Reference uses  $0.9 V_{DD}$  for a logic 1 and  $0.1 V_{DD}$  for a logic 0. [2] Interrupt request through Port 3 (P33-P31)

## TIMING DIAGRAM

## **Electrical Timing Diagram**

## Low Margin:

Customer is advised that this product does not meet Zilog's internal guardbanded test policies for the specification requested and is supplied on an exception basis. Customer is cautioned that delivery may be uncertain and that, in addition to all other limitations on Zilog liability

## stated on the front and back of the acknowledgement, Zilog makes no claim as to quality and reliability under the CPS. The product remains subject to standard warranty for replacement due to defects in materials and workmanship.

#### **Pre-Characterization Product:**

The product represented by this CPS is newly introduced and Zilog has not completed the full characterization of the product. The CPS states what Zilog knows about this product at this time, but additional features or non-con-

© 1995 by Zilog, Inc. All rights reserved. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Zilog, Inc. The information in this document is subject to change without notice. Devices sold by Zilog, Inc. are covered by warranty and patent indemnification provisions appearing in Zilog, Inc. Terms and Conditions of Sale only. Zilog, Inc. makes no warranty, express, statutory, implied or by description, regarding the information set forth herein or regarding the freedom of the described devices from intellectual property infringement. Zilog, Inc. makes no warranty of merchantability or fitness for any purpose. Zilog, Inc. shall not be responsible for any errors that may appear in this document. Zilog, Inc. makes no commitment to update or keep current the information contained in this document. formance with some aspects of the CPS may be found, either by Zilog or its customers in the course of further application and characterization work. In addition, Zilog cautions that delivery may be uncertain at times, due to start-up yield issues.

Zilog's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the customer and Zilog prior to use. Life support devices or systems are those which are intended for surgical implantation into the body, or which sustains life whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

Zilog, Inc. 210 East Hacienda Ave. Campbell, CA 95008-6600 Telephone (408) 370-8000 Telex 910-338-7621 FAX 408 370-8056 Internet: http://www.zilog.com