# CXA1008P/1009P

## High-speed Sample and Hold Amplifiers

#### Description

CXA1008P/1009P are bipolar IC's developed for the purpose of sample holding video signals and other signals at high-speed.

#### **Features**

Maximum sampling frequency

CXA1008P 35 MHz CXA1009P 18 MHz

•Linearity 0.08% (Typ.)

•Clock input level ECL compatible

Low power consumption

CXA1008P 680 mW (Typ.) CXA1009P 420 mW (Typ.)

#### Structure

Bipolar silicon monolithic IC.

#### **Applications**

- A/D converter and other analog signal processing

- Other general applications.

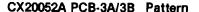

#### Function

High-speed hold circuit, wide band 6 dB amplifier, A/D reference power supply, A/D clock output circuit.

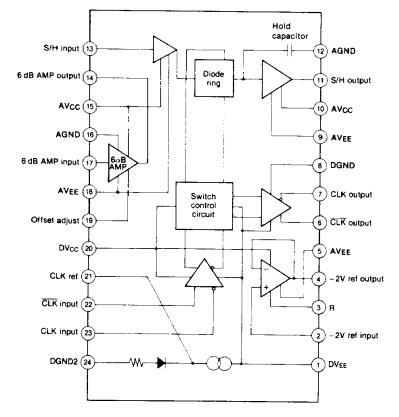

#### **Block Diagram**

Fig. 1

E89641-HP

## Absolute Maximum Ratings (T<sub>a</sub> = 25°C)

| Supply voltage               | $V_{GG}$ | + 5.5         | ٧  |

|------------------------------|----------|---------------|----|

|                              | $V_{FE}$ | -6.0          | ٧  |

| Operating temperature        | Topr     | -20  to  +75  | °C |

| •Storage temperature         | Tstg     | -55 to $+150$ | °C |

| •Allowable power dissipation | $P_{D}$  | 1.2           | W  |

## **Recommended Operating Conditions**

•Supply voltage

$$\begin{array}{ccc} \text{V}_{\text{CC}} & +4.75 \text{ to } 5.25 \text{V} \\ \text{V}_{\text{EE}} & -4.75 \text{ to } -5.45 \text{V} \end{array}$$

## Pin Description

| No. | Symbol             | Equivalent circuit   | Description                                      |

|-----|--------------------|----------------------|--------------------------------------------------|

| 1   | DVEE               |                      | Digital V <sub>EE</sub> ( – 5V)                  |

| 2   | – 2V ref<br>input  | ② O AVEE             | reference voltage input<br>for A/D converter     |

| 3   | R                  | → DV <sub>cc</sub> 4 | Pulldown terminal for external R (30Ω typically) |

| 4   | - 2V ref<br>output | 20Ω \$               | reference voltage output<br>for A/D converter    |

| 5   | AVEE               |                      | Analog V <sub>EE</sub> (-5V)                     |

| 6   | CLK output         | DGND DVcc            | CLK output for A/D converter                     |

| 7   | CLK output         | 7kΩ (6) (7)          | CLK output for A/D converter                     |

| 8   | DGND               |                      | Digital GND                                      |

| 9   | AVEE               |                      | Analog V <sub>EE</sub> (-5V)                     |

| 10  | AVcc               |                      | Analog V <sub>CC</sub> (+5V)                     |

| No. | Symbol            | Equivalent circuit                | Description                       |

|-----|-------------------|-----------------------------------|-----------------------------------|

| 11  | S/H<br>output     | 12.5Ω O AVEE                      | S/H output                        |

| 12  | AGND              |                                   | Analog GND                        |

| 13  | S/H<br>input      | AV <sub>CC</sub> AV <sub>EE</sub> | S/H input                         |

| 14  | 6dB AMP<br>output | O AVcc<br>(14)<br>O AVEE          | Olutput terminal of 6dB amplifier |

| 15  | AV <sub>CC</sub>  |                                   | Analog Vcc (+5V)                  |

| 16  | AGND              |                                   | Analog GND                        |

| No. | Symbol           | Equivalent circuit                        | Description                                                 |

|-----|------------------|-------------------------------------------|-------------------------------------------------------------|

| 17  | 6dB AMP<br>input | AV <sub>cc</sub>                          | 6dB AMP input                                               |

| 18  | AVEE             | 17<br>AGND AGND                           | Analog V <sub>EE</sub> (-5V)                                |

| 19  | offset<br>adjust | AGND                                      | 6dB AMP DC offset adjust, terminal                          |

| 20  | DVcc             |                                           | Digital Vcc (+5V)                                           |

| 21  | CLK ref          | DVcc MDGND  -1.2V  DVcc  DVcc  DVcc  DVcc | CLK reference output                                        |

| 22  | CLK input        | ②23<br>23                                 | CLK input  Note: connect to ②  PIN or input ECL CLK  signal |

| 23  | CLK input        | DVEE                                      | CLK input (Note: input ECL) CLK signal                      |

| 24  | DGND             |                                           | Digital GND                                                 |

### SONY®

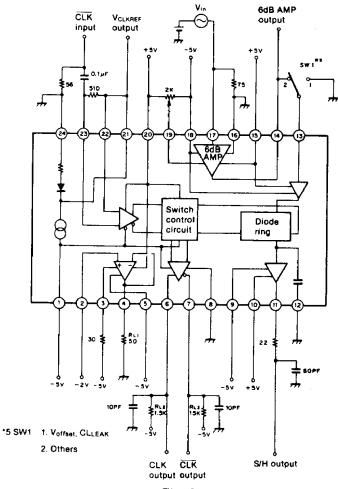

CXA1008P Electrical Characteristics (Ta = 25 °C,  $V_{CC}$  = +5V,  $V_{EE}$  = -5V) S/H section (see Fig. 3)

| Item                           | Condition                                                  | Symbol           | Min.  | Тур.  | Max.         | Unit |

|--------------------------------|------------------------------------------------------------|------------------|-------|-------|--------------|------|

|                                |                                                            | ViH              | -0.9  | -0.8  |              | ٧    |

| Digital input voltage          |                                                            | VIL              |       | - 1.6 | - 1.5        | ٧    |

| CLK Reference voltage (pin 21) |                                                            | VCLKREF          | - 1.3 | - 1.2 | - 1.1        | ٧    |

| Analog input voltage range     | △V < 1.2V *1                                               | Vins             | -3    | •     | 3            | ٧    |

| Output voltage range           |                                                            | Vouts            | -3    |       | 3            | ٧    |

|                                |                                                            | lcc              | 48    | 60    | 78           | mA   |

| Power Supply                   | without -2V ref.                                           | I <sub>EE1</sub> | 48    | 60    | 78           | mA   |

|                                | with $-2V$ ref. $R_{LI} = 50\Omega *2$                     | I <sub>EE2</sub> | 80    | 100   | 125          | mA   |

| Input bias current             | $-2V < V_{in} < 2V$                                        | IBiass           |       | 15    | 30           | μΑ   |

| Output impedance               |                                                            | Zos              |       | 20    | 40           | Ω    |

| Voltage gain ratio             |                                                            | Gvs              | 0.99  | 1.0   | 1.01         |      |

| Full power bandwidth           | $V_{in} = 2V_{p-p} (-3dB)$                                 | BW               |       | 12    | !<br>!       | MHz  |

| Power supply rejection ratio   |                                                            | SVRs             |       | - 40  | :<br>        | dB   |

| Hold mode feed through         | fin = 4MHz<br>Vin = 1 Vp-p, CLK open                       | нмтн             |       | -50   | - 40         | dB   |

| Clock leak                     | $V_{in} = 0V$                                              | CLLEAK           |       | 10    | 50           | mV   |

| Linearity                      | fin = 19.53kHz (10/512MHz)<br>f <sub>CLK</sub> = 10MHz * 3 | Lin              |       | 0.08  | 0.15         | %    |

| Hold mode droop                | input voltage range, 0 to -2V                              | HMDR             |       | 2     | 20           | mV/μ |

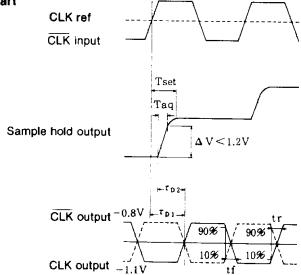

| Acquisition time               | △V = 1.2V                                                  | Taq              |       | 8     | 12           | ns   |

| Settling time                  | Settle to ±0.2% of F.S. see the Timing Chart               | T <sub>set</sub> |       | 25    |              | ns   |

| DC offset voltage              | f <sub>CLK</sub> = 5MHz                                    | Voffset          | ļ     | ± 15  | ± 100        | mV   |

| Maximum sampling frequency     |                                                            | folkh            | 35    | ļ     | <del> </del> | MHz  |

| Minimum sampling frequency     |                                                            | folkl            |       |       | 5            | MHz  |

| Differential gain (D.G.)       | Vin = NTSC                                                 | DG               |       | 0.5   | 1.0          | %    |

| Differential phase (D.P.)      | 40 IRE mode ramp.<br>f <sub>CLK</sub> = 20MHz              | DP               |       | 0.5   | 1.0          | deg  |

$(R_{L1} = 50\Omega, see Fig. 3)$

CXA1009P

Electrical Characteristics (Ta = 25°C,  $V_{CC} = +5V$ ,  $V_{EE} = -5V$ ) S/H section (see Fig. 3)

| ltem                           | Condition                                     | Symbol           | Min.        | Тур.   | Max.  | Unit                                             |

|--------------------------------|-----------------------------------------------|------------------|-------------|--------|-------|--------------------------------------------------|

| Digital input voltage          |                                               | ViH              | - 0.9       | -0.8   |       | ٧                                                |

|                                |                                               | VIL              |             | - 1.6  | -1.5  | V                                                |

| CLK Reference voltage (pin 21) |                                               | VCLKREF          | -1.3        | -1.2   | -1.1  | V                                                |

| Analog input voltage range     | △V < 1.2V *1                                  | VINS             | -3          | †<br>i | 3     | V                                                |

| Output voltage range           |                                               | Vouts            | - 3         | †·     | 3     | V                                                |

|                                |                                               | Icc              | 25          | 35     | 45    | mA                                               |

| Power supply                   | without -2V ref.                              | lee1             | 25          | 35     | 45    | mA                                               |

|                                | with $-2V$ ref. $R_{LI} = 50\Omega *2$        | I <sub>EE2</sub> | 60          | 75     | 98    | mA                                               |

| Input bias current             | -2V < Vin < 2V                                | Biass            |             | 9      | 18    | μΑ                                               |

| Output impedance               |                                               | Zos              |             | 20     | 40    | Ω                                                |

| Voltage gain ratio             |                                               | Gvs              | 0.99        | 1.0    | 1.01  | <del>                                     </del> |

| Full power bandwidth           | $V_{in} = 2V_{p-p} (-3dB)$                    | BW               |             | 6      |       | MHz                                              |

| Power supply rejection ratio   |                                               | SVRs             | <del></del> |        | ·     | ₫B                                               |

| Hold mode feed through         | fin = 4MHz<br>Vin = 1 Vp-p, CLK open          | НМТН             |             | -50    | -40   | dB                                               |

| Clock leak                     | Vin = 0V                                      | CLLEAK           |             | 10     | 50    | mV                                               |

| Linearity                      | fin = 19.53kHz (10/512MHz)<br>fclk = 10MHz *3 | Lin              |             | 0.08   | 0.15  | %                                                |

| Hold mode droop                | input voltage range, 0 to -2V                 | HMDR             |             | 2      | 10    | mV/μs                                            |

| Acquisition time               | △V = 1.2V                                     | Taq              |             | 12     | 20    | ns                                               |

| Settling time                  | Settle to ±0.2% of F.S. see the Timing Chart  | T <sub>set</sub> |             | 36     |       | ns                                               |

| DC offset voltage              | fclk = 5MHz                                   | Voffset          |             | ± 15   | ± 100 | m۷                                               |

| Maximum sampling frequency     |                                               | fcLkH            | 18          |        |       | MHz                                              |

| Minimum sampling frequency     |                                               | fclkl            |             |        | 2     | MHz                                              |

| Differential gain (D.G.)       | Vin = NTSC                                    | DG               |             | 0.5    | 1.0   | %                                                |

| Differential phase (D.P.)      | 40 IRE more ramp<br>fclk = 15MHz              | DP               |             | 0.5    | 1.0   | deg                                              |

\*1 AV is voltage change during one sampling period.

\*3 Input voltage waveform

51 2<sub>µ</sub>S

Fig. 2

- 2.0V

<sup>\*2</sup> Power consumption is  $I_{CC} \times 5V + I_{EE1} \times 5V + 40 \text{mA} \times 1.8V$ .

#### 6dB amp section (see Fig. 3)

| _                            |                               | 0                   | (    | CXA1008F | ·     |       | CXA1009F | 5     | Unit  |

|------------------------------|-------------------------------|---------------------|------|----------|-------|-------|----------|-------|-------|

| Item                         | Condition                     | Symbol              | Min. | Тур.     | Max.  | Min.  | Тур.     | Мах.  | Offic |

| Intput voltage range         | *3                            | VINA                | -1.3 |          | + 0.8 | - 1.3 |          | + 0.8 | ٧     |

| Band width (-3dB)            | $V_{in} = IV_{pp}$            | W                   | 45   | 55       |       | 15    | 25       |       | MHz   |

| Input bias current           | -1V <<br>V <sub>in</sub> < 1V | I <sub>Bias A</sub> |      | 9        | 20    |       | 5        | 10    | μΑ    |

| Output impedance             |                               | ZOA                 |      | 4        | 10    |       | 4        | 10    | Ω     |

| Voltage gain                 | *4                            | GVA                 | 5.1  | 6.0      | 6.9   | 5.1   | 6.0      | 6.9   | dB    |

| Power supply rejection ratio |                               | SVRA                |      | - 40     |       |       | - 40     |       | dB    |

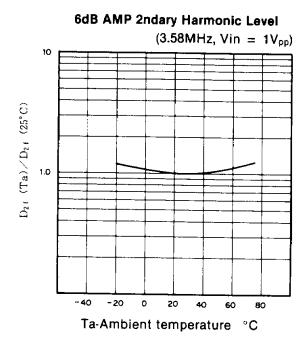

<sup>\*3 2</sup>ndary harmonic: -40dB fin = 3.58MHz

#### CLK OUT section (see Fig. 3)

|                |           | 0 1111           | 0                | (    | CXA1008F | •     |       | CXA10091 | P    | Unit |

|----------------|-----------|------------------|------------------|------|----------|-------|-------|----------|------|------|

| Item           | 1         | Condition        | Symbol           | Min. | Тур.     | Max.  | Min   | Тур.     | Max. | — —  |

|                | Amplitude |                  | V <sub>CLK</sub> | 0.2  | 0.3      | 0.4   | 0.2   | 0.3      | 0.4  | ٧    |

| Output voltage | Low level |                  | VCLKL            | -1.2 | -1.1     | - 0.9 | - 1.2 | -1.1     | -0.9 | ٧    |

| Rise time      |           | RL2 = 1.5        | tr               |      | 7        | 10    |       | 7        | 10   | ns   |

| Fall time      |           | KΩ<br>see Fig. 3 | tf               |      | 5        | 8     |       | 5        | 8    | ns   |

| CLK Delay 1    |           | 1                | TD1              | 20   | 28       | 34    | 36    | 38       | 45   | ns   |

| CLK Delay 2    |           | 1                | τD2              | 14   | 22       | 28    | 24    | 26       | 33   | ns   |

## - 2V<sub>ref</sub> amp section (see Fig. 3)

|                     |                     |                     |      | CXA1008 | P    |      | CXA1009 |      | Unit  |

|---------------------|---------------------|---------------------|------|---------|------|------|---------|------|-------|

| Item                | Condition           | Symbol              | Min. | Тур.    | Max. | Min. | Тур.    | Max. | Oint  |

| Voltage gain ratio  | $V_{ref} = -2V$     | GVR                 | 0.9  | 1.0     | 1.1  | 0.9  | 1.0     | 1.1  |       |

| Voltage galli ialio | $R_{Li} = 50\Omega$ |                     |      |         |      |      |         |      |       |

| land bloo overant   | $-3V < V_{in}$      | I <sub>Bias R</sub> |      | 5       | 10   |      | 5       | 10   | μΑ    |

| Input bias current  | < 0V                | IBIAS R             |      |         |      |      |         |      | ,<br> |

| Output impedance    |                     | ZOR                 |      | 2       | 10   |      | 2       | 10   | Ω     |

<sup>\*4</sup>  $f_{in} = 3.58MHz V_{in} = 1V_{p-p}$

## **Electrical Characteristics Test Circuit**

Fig. 3

Fig. 4

#### **Description of Functions**

CXA1008P/1009P are the monolithic ICs incorporating a high-speed sample hold circuit, a wide band 6 dB amp, reference power supply for A/D converter, and a clock output section, and operate up to a sampling frequency of 35/18 MHz.

CXA1008P/1009P can compose in 20/15 MS/s A/D converter system in combination with a CX20052A. CXA1008P/1009P form, with the input of a single phase or 2-phase ECL clock input, a new sampling signal. For this reason, the sampling period remain unchanged even when the frequency or duty of the input sampling CLK signal changes.

#### •Wide band 6 dB AMP.

in-phase amp with a band width over 45/15 MHz amplifies ordinary TV signal (1Vp-p) to a 2Vp-p signal which gives the highest accuracy when processed in CX20052A.

#### •CLK output section

When used in combination with an A/D converter such as CX20052A, the CLK timing between the S/H circuit and the A/D converter needs to be adjusted, and up to 20/15 MHz, CXA1008P/1009P generate CLK timing signals for driving the A/D converter, and output 2-phase CLK at 300 mVp-p from pins 6 and 7. With this output, no separate CLK is required to combine with an A/D converter.

CXA1008P/1009P incorporate a buffer amp to provide a reference voltage for the A/D converter.

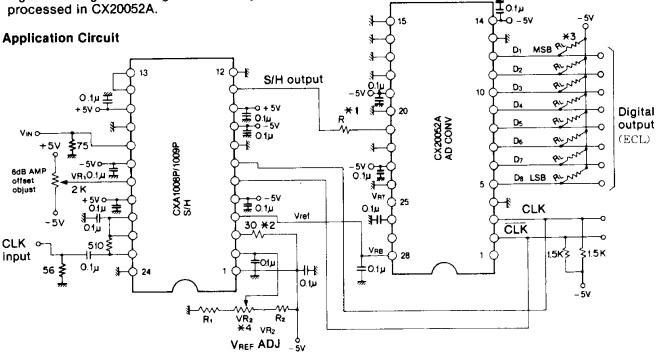

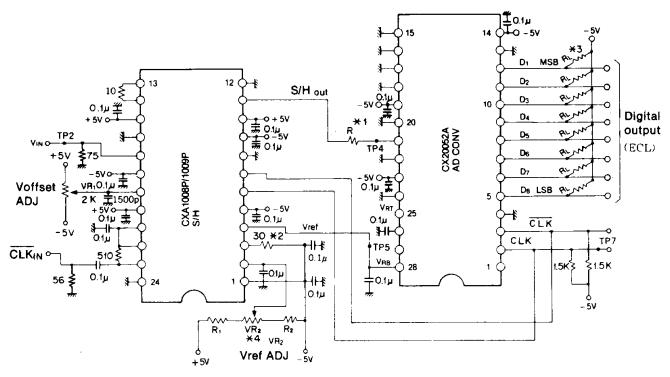

Fig. 5 Connection of CXA 1008P/1008P with CX20052A (1)

- \*1 R is a ringing preventing resistor. Select between 10 to  $50\Omega$

- \*2 Pulldown R for Vret

- \*3  $R_L = 4.3k\Omega$

- \*4  $R_1 = 1k\Omega$ ,  $VR_2 = 2k\Omega$ ,  $R_2 = 2k\Omega$

#### **Notes on Application**

- 1. Unless sufficiently stable power supply and GND voltage in the high-frequency range are used, the device characteristics deteriorates. For this reason, bring the power supply bypass capacitor as near to this IC as possible, and make the pattern to the power supply and to the earth terminal as wide as feasible.

- To reduce CLK leak, use waveforms similar to sine waves as far as possible, up to the CLK input. For satisfactory operation, a CLK input ampritude of around 300mV is enough.

- 3. When the S/H input deviates over 1.2V during one sampling period, the output may contain errors.

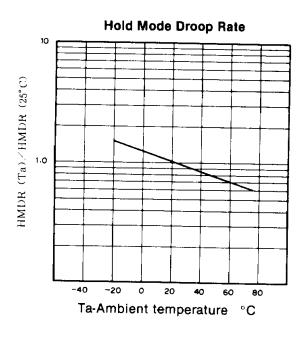

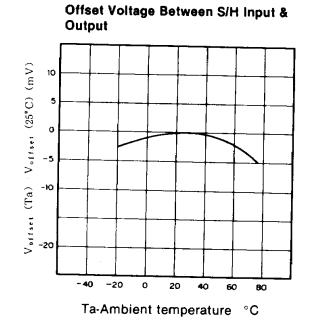

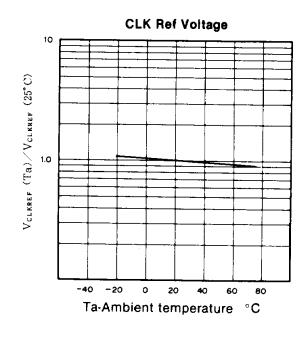

## Changes in Characteristics with Temperature

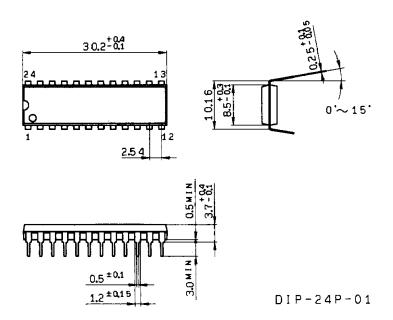

## Package Outline Unit: mm

#### 24pin DIP(Ptastic) 400mil 2.0g

# 8bit, 20/15MHz A/D Converter Evaluation Board with CXA1008P/CXA1009P S/H.

#### Description

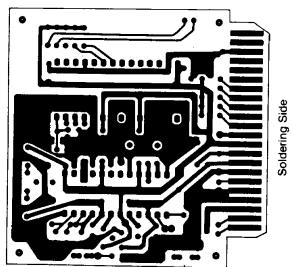

CX20052A PCB-3A/3B is an 8 bit A/D converter board for video signal processing. A high speed S/H IC CXA1008P/1009P and a high speed 8 bit A/D converter CX20052A are assembled on single small printed circuit board.

CX20052A PCB-3A with CXA1008P mounted, operates up to 20 MHz of conversion rate, and CX20052A PCB-3B with CXA1009P mounted, operates up to 15 MHz of conversion rate.

#### **Features**

Resolution

8 bit ± 1/2 LSB

Conversion rate

20 MHz CX20052A PCB-3A 15 MHz CX20052A PCB-3B

• Analog input level

1Vp-p ECL level

Digital output levelPower supply

±5V

7

## 2. Characteristics

## 1. Supply Voltage

## $(Ta = 25^{\circ}C, V_{EE} = -5V, V_{CC} = 5V)$

|                 | Item |                    | Symbol     | Min | Тур       | Max       | Unit     |

|-----------------|------|--------------------|------------|-----|-----------|-----------|----------|

| V <sub>cc</sub> | + 5V | CX20052A<br>PCB-3A | lcc<br>lee |     | 70<br>220 | 80<br>240 | mA<br>mA |

| V <sub>EE</sub> | -5V  | CX20052A           | Icc        |     | 50        | 60        | mA       |

|                 |      | PCB-3B             | lee        |     | 200       | 220       | mA       |

#### 2. Analog Input (V<sub>IN</sub>)

| Item                       | Symbol | Min   | Тур   | Max | Unit |

|----------------------------|--------|-------|-------|-----|------|

| AC Input Voltage Amplitude | VIN    |       |       | 1   | V    |

| Offset Adjustable Range    |        | ± 1.5 | ± 2.0 |     | V    |

| Input Impedance            | Zin    |       |       |     |      |

| CX20052APCB-3A             |        |       | 75    |     | Ω    |

| CX20052APCB-3B             |        |       | 75    |     | Ω    |

## 3. Digital Input (CLK IN)

| Item                | Symbol           | Min | Тур | Max | Unit |

|---------------------|------------------|-----|-----|-----|------|

| Input Voltage (p-p) | V <sub>CLK</sub> | 0.3 | 0.8 | 4   | ٧    |

| Input Impedance     | Zincl            |     | 50  |     | Ω    |

#### 4. Digital Output (D1 ~ D8) (1.5k $\Omega$ to V<sub>EE</sub>)

| Item           | Symbol          | Min   | Тур    | Max           | Unit |

|----------------|-----------------|-------|--------|---------------|------|

| Output Voltage | V <sub>OH</sub> | -0.90 | -0.75  |               | ٧    |

|                | Vol             |       | - 1.50 | <b>- 1.35</b> | V    |

## 5. Clock Output (CLKout, CLKout) (See timing chart)

| Item           |           | Symbol CX20052A PCB-3A |       |      | CX20052A PCB-3B |       |      |       |      |

|----------------|-----------|------------------------|-------|------|-----------------|-------|------|-------|------|

|                | •••       | Symbol                 | Min   | Тур  | Max             | Min   | Тур  | Max   | Unit |

| Output voltage | Amplitude | V <sub>CLK</sub>       | 0.2   | 0.3  | 0.4             | 0.2   | 0.3  | 0.4   | ٧    |

| •              | Low Level | VCLKL                  | - 1.2 | -1.1 | -0.9            | - 1.2 | -1.1 | - 0.9 | V,   |

| Rise time      |           | tr                     |       | 6    | 10              |       | 6    | 10    | ns   |

| Fall time      |           | tf                     |       | 12   | 15              |       | 12   | 15    | ns   |

| CLK Delay      |           | τ <sub>F</sub>         | 20    | 28   | 34              | 36    | 38   | 45    | ns   |

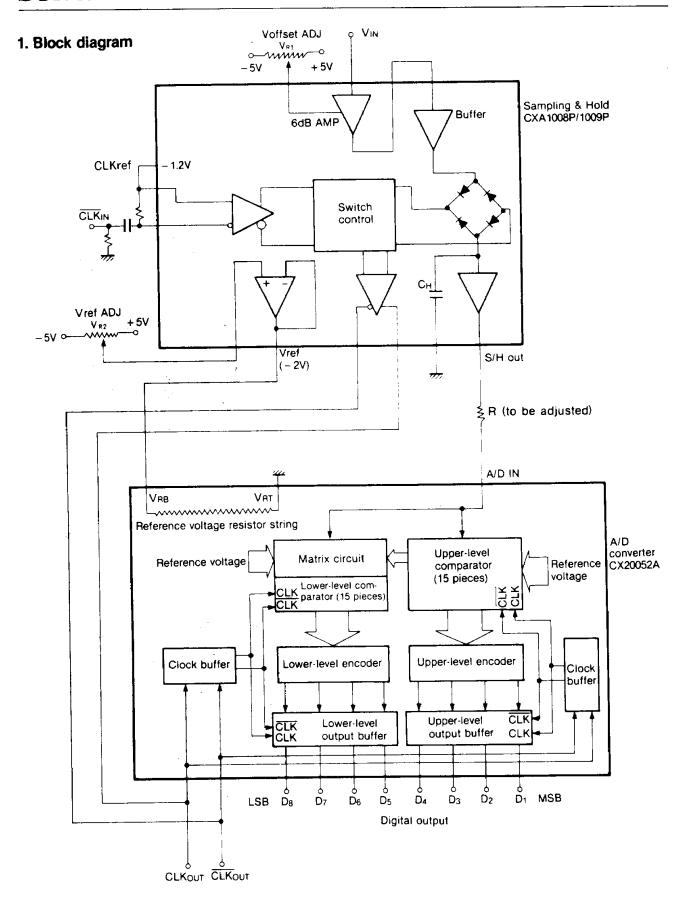

## 3. Timing Chart

$T_{\text{H}}$  shows a timing when the A/D latches upper 4 bits.  $T_{\text{L}}$  shows a timing when the A/D latches lower 4 bits.

| - 1            | 0               | CX20052A PCB-3A |     |     | CX20052A PCB-3B |     |     |      |

|----------------|-----------------|-----------------|-----|-----|-----------------|-----|-----|------|

| Item           | Symbol          | Min             | Тур | Max | Min             | Тур | Мах | Unit |

|                | τ <sub>CH</sub> |                 | 25  |     |                 | 33  |     | ns   |

| Clock in       | ₹GL             |                 | 25  |     |                 | 33  | •   | ns   |

|                | T <sub>A</sub>  |                 | 6   |     |                 | 12  |     | ns   |

| Sampling delay | $	au_{B}$       |                 | 25  |     |                 | 36  | •   | ns   |

| Clock out      | 7F              | 20              | 28  | 34  | 36              | 38  | 45  | ns   |

| Data dalay     | <i>T</i> E      |                 |     | 8   |                 |     | 8   | ns   |

| Data delay     | $	au_{ m D}$    |                 |     | 4   |                 |     | 4   | ns   |

#### 4. Adjustment

(1) Offset Voltage (Voffset ADJ)

$VR_1$  should be adjusted so that the S/H output meets the input voltage range of the A/D (0 to -2V).

(2) A/D reference voltage (Vref ADJ).

The reference voltage of the A/D (TP5) is to be -2V. VR₂ should be adjusted.

## 5. Output Data Format

The input of the A/D converter IC (S/H out) is quantized in 8 bit within the reference voltage range of  $V_{RT}$  and  $V_{RB}$  are set at 0V and -2V respectively on the printed circuit board.

| Step  |       | A/D input signal voltage |                    | Digital output of | ode: |

|-------|-------|--------------------------|--------------------|-------------------|------|

|       |       |                          |                    | MSB               | LSB  |

|       | over  | 0. 0 0 0 0 V             |                    | 111111            | 1 1  |

| 0 0 0 |       | 0. 0 0 0 V               | (V <sub>RT</sub> ) | 111111            | 1 1  |

|       |       | •                        |                    | •                 |      |

| •     |       | •                        |                    |                   |      |

| •     |       |                          |                    |                   |      |

| 1 2 7 |       | -0. 9 9 6 1 V            |                    | 100000            | 0 0  |

| 1 2 9 |       | -1. 0 0 3 9 V            |                    | 0 1 1 1 1 1       | 1 1  |

| •     |       |                          |                    |                   |      |

| •     |       |                          |                    |                   |      |

| •     |       | •                        |                    |                   |      |

| 2 5 5 |       | -2. 0 0 0 0 V            | (V <sub>RB</sub> ) | 000000            | 0 0  |

|       | under | -2. 0 0 0 0 V            | ŀ                  | 000000            | 0 0  |

## Note on application

- (1) Although the pull down resistors (RL:  $4.3k\Omega$ ) are mounted on the PCB, additional pull down is recommended in an external circuit. The output current at the A/D output terminal should not exceed 10 mA.

- (2) Digital output data should be latched by an external circuit to achieve a rated performance. Output data can be latched at a rising edge of CLKout.

- CLK<sub>OUT</sub> AND CLK<sub>OUT</sub> should be reshaped by an ECL line receiver such as MC10116 in an external circuit.

(3) The reference voltage is derived from the V<sub>EE</sub> by a simple resistor dividing network. The power supply (±5V) should be stabilized to reduce voltage drift of the reference voltage.

- (4) To reduce CLK leak, use waveforms similar to sine waves as far as possible up to the CLK input. For satisfactory operation, a CLK input amplitude of around 300m Vpp is enough.

- (5) When the S/H input deviates over 1.2V during one sampling period, the output may contain errors.

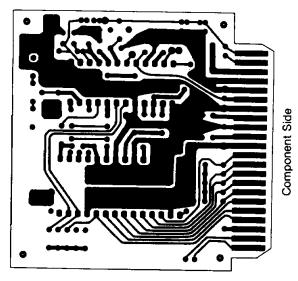

#### CX20052A PCB-3A/3B Circuit

- \*1. R is a ringing preventing resistor. Select between 10 to  $50\Omega$  according to pattern length.

- \*2. Pulldown R for Vref.

- \*3. RL =  $4.3k\Omega$

- \*4. R<sub>1</sub> =  $2k\Omega$ ,  $VR_2 = 2k\Omega$ ,  $R_2 = 1k\Omega$

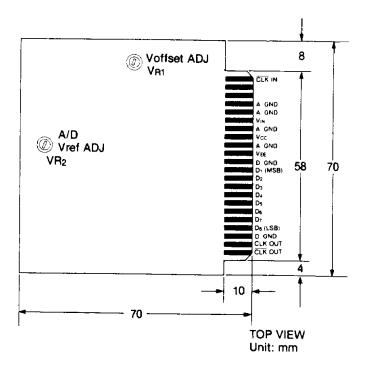

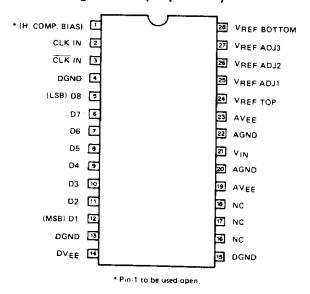

## Additional Information on CX20052A Pin Configuration (Top View)

## Pin Description

| No. | Symbol      | Description                                                                        |

|-----|-------------|------------------------------------------------------------------------------------|

| 1   | H-COMP BIAS | Pin connected to internal comparator. It should not be connected to outer circuit. |

| 2   | CLK IN      | CLOCK input pin.                                                                   |

| 3   | CLK IN      | CLOCK input pin.                                                                   |

| 4   | DGND        | Ground pin of digital circuit.                                                     |

| 15  | DGND        | Ground pin of digital circuit.                                                     |

| 17  | NC          | Non-connection.                                                                    |

| 18  | NC          |                                                                                    |

| 24  | VREF (T)    | Reference voltage pin. (OV)                                                        |

| 25  | VREF ADJI   | Reference voltage adjusting                                                        |

| 26  | VREF ADJ2   | pin.                                                                               |

| 27  | VREF ADJ3   | (Usually it should be con-<br>nected to GND through<br>0.047 µF capacitor.)        |

| 28  | VREF (B)    | Reference voltage pin. (-2.0V)                                                     |

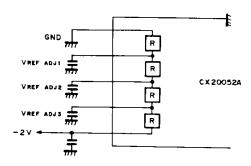

(\*) Reference resistors have adjusting pins as shown below. Usually these pins are connected to GND through 0.047  $\mu$ F capacitors. When an adjustment is required, they should be connected to GND or VREF (B) through resistors.

#### **Output Coding**

| Step | Input signal voltage | Output digital code |

|------|----------------------|---------------------|

| 000  | 0.0000V              | MSB LSB<br>11111111 |

|      | •                    |                     |

|      | •                    |                     |

|      |                      |                     |

| 127  | -0.9961V             | 10000000            |

| 128  | -1.0039V             | 01111111            |

| 129  | -1.0118V             | 01111110            |

|      |                      |                     |

|      |                      |                     |

|      |                      |                     |

| 255  | -2.0000V             | 0000000             |