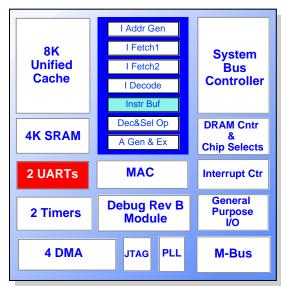

# MCF5307 UART MODULE

5307 UART Module

#### **UART INTERFACE**

#### **OVERVIEW**

- TWO INDEPENDENT, FULL DUPLEX ASYNCHRONOUS/SYNCHRONOUS RECEIVER/ TRANSMITTER CHANNELS

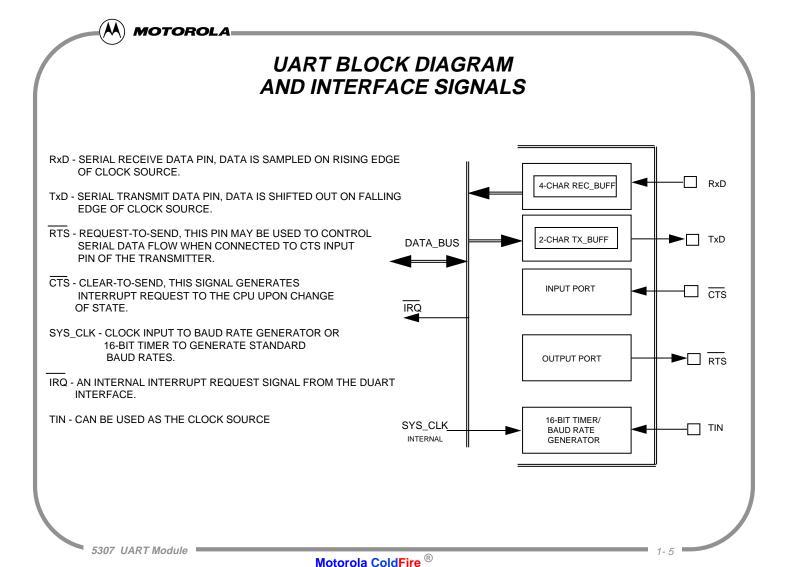

- INDEPENDENTLY PROGRAMMABLE BAUD RATE GENERATOR FOR EACH RECEIVER AND TRANSMITTER DERIVABLE FROM SYSTEM CLOCK OR EXTERNAL CLOCK ON **TIN** PIN

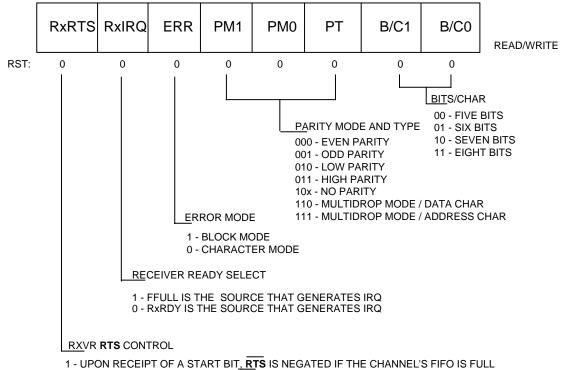

- PROGRAMMABLE DATA FORMAT, FIVE TO EIGHT DATA BITS PLUS PARITY OR ADDRESS MARK BIT

#### **PARITY OPTIONS:**

- 1- ODD PARITY

- 2- EVEN PARITY

- 3- FORCE PARITY

- 4- NO PARITY

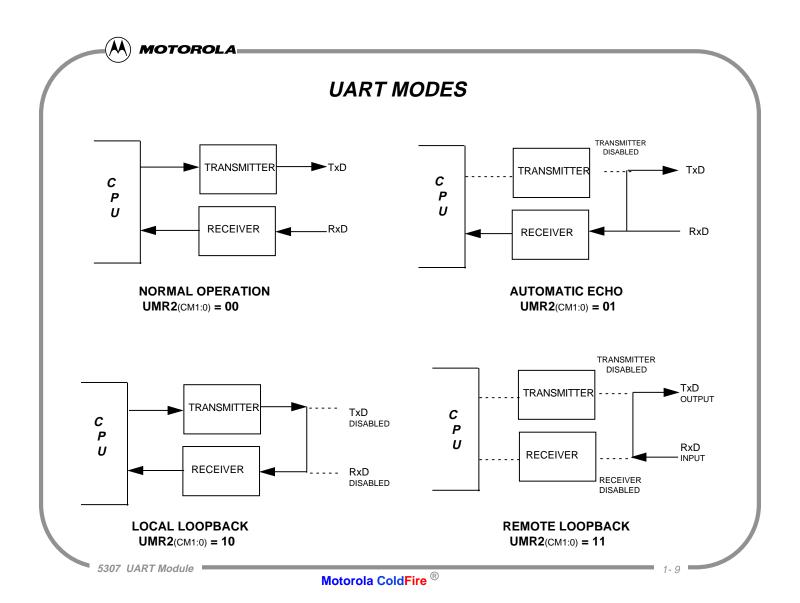

- PROGRAMMABLE CHANNEL MODES NORMAL (FULL DUPLEX) AUTOMATIC ECHO (HALF DUPLEX) LOCAL LOOPBACK REMOTE LOOPBACK

- •UART CAN BE PROGRAMMED TO DIRECTLY INTERRUPT DMA FOR FAST TRANSFERS

MCF5307

5307 UART Module

## **UART RECEIVER**

#### **FEATURES:**

- AUTOMATIC WAKEUP FOR MULTIDROP APPLICATIONS

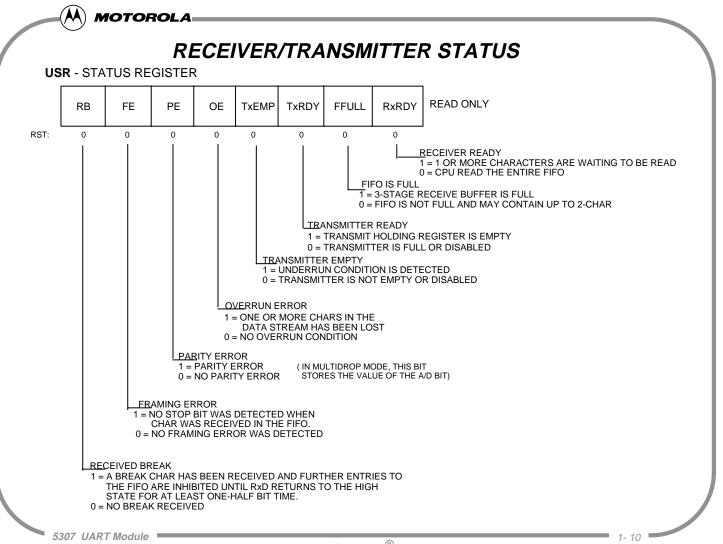

- FRAMING, PARITY AND OVERRUN ERROR DETECTIONS

- FALSE START BIT DETECTION

- LINE-BREAK DETECTION

- DETECTION OF A BREAK ORIGINATING IN THE MIDDLE OF A CHARACTER

- START/END BREAK INTERRUPT /STATUS

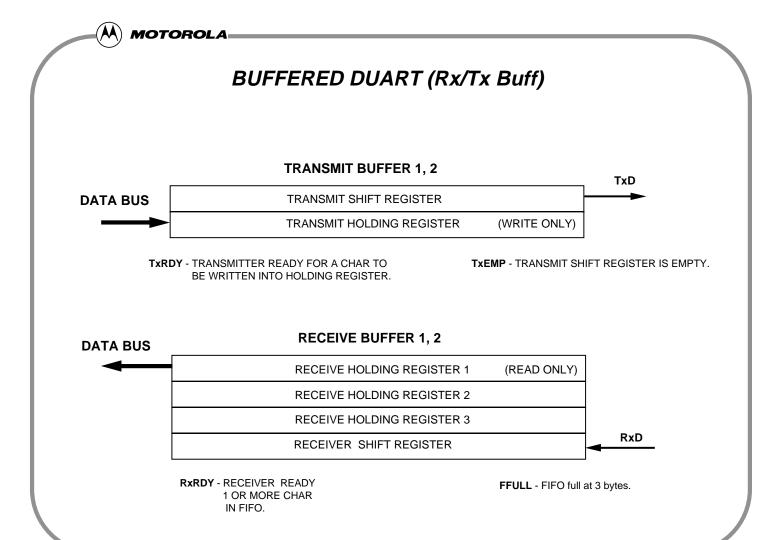

- FOUR STAGE FIFO RECEIVE BUFFER

- RECEIVER OPERATION MAY BE POLLED OR INTERRUPT DRIVEN

5307 UART Module

**Motorola ColdFire** ®

## **UART TRANSMITTER**

#### **FEATURES:**

- DOUBLE-BUFFERED OPERATION

- PARITY GENERATION: ODD, EVEN, NO PARITY OR FORCE PARITY

- STOP BIT GENERATION FROM .563 TO 2-BITS

- BREAK GENERATION

- AUTOMATIC NEGATION OF REQUEST-TO-SEND UPON COMPLETION OF MESSAGE TRANSMISSION

- PROGRAMMABLE CHARACTER LENGTH FROM 5 TO 8-BITS

5307 UART Module

**Motorola ColdFire** ®

**Motorola ColdFire** ®

5307 UART Module

## RECEIVER REGISTERS

#### **UMR1** - UART MODE REGISTER 1

0 - RECEIVER HAS NO EFFECT ON RTS

5307 UART Module

#### M) MOTOROLA

### **UART REGISTERS**

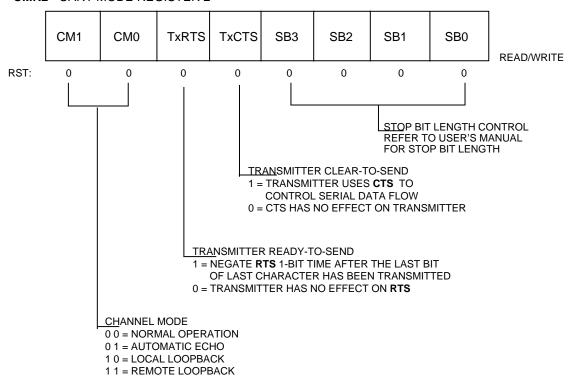

#### **UMR2** - UART MODE REGISTER 2

5307 UART Module

Motorola ColdFire ®

## **BAUD RATE SELECTION**

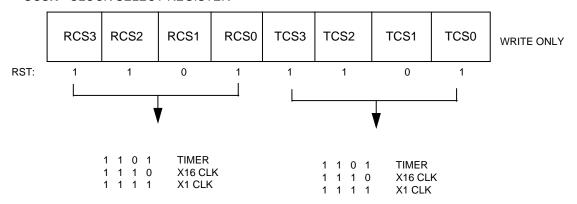

#### **UCSR** - CLOCK SELECT REGISTER

RECEIVER BAUD RATE SELECTION

TRANSMITTER BAUD RATE SELECTION

5307 UART Module

## **UART COMMANDS**

#### **UCR** - COMMAND REGISTER

|      | - | MISC2 | MISC1 | MISC0 | TC1 | TC0 | RC1 | RC0 | WRITE ONLY |

|------|---|-------|-------|-------|-----|-----|-----|-----|------------|

| RST: | 0 | 0     | 0     | 0     | 0   | 0   | 0   | 0   |            |

| MISC2 | 2 MISC1 | MISC0 | COMMAND              |

|-------|---------|-------|----------------------|

| 0     | 0       | 0     | NO COMMAND           |

| 0     | 0       | 1     | RESET MODE REG PNTR  |

| 0     | 1       | 0     | RESET RECEIVER       |

| 0     | 1       | 1     | RESET TRANSMITTER    |

| 1     | 0       | 0     | RESET ERROR STATUS   |

| 1     | 0       | 1     | RESET BRK CHANGE IRQ |

| 1     | 1       | 0     | START BREAK          |

| 1     | 1       | 1     | STOP BREAK           |

MISC COMMANDS

| TC1 T | ГС0 | COMMAND             |

|-------|-----|---------------------|

| 0     | 0   | NO COMMAND          |

| 0     | 1   | ENABLE TRANSMITTER  |

| 1     | 0   | DISABLE TRANSMITTER |

| 1     | 1   | DO NOT USE          |

#### TRANSMITTER COMMANDS

| RC1              | RC0              | COMMAND                                                         |

|------------------|------------------|-----------------------------------------------------------------|

| 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | NO COMMAND<br>ENABLE RECEIVER<br>DISABLE RECEIVER<br>DO NOT USE |

RECEIVER COMMANDS

5307 UART Module

Motorola ColdFire ®

#### M) MOTOROLA

### **UART REGISTERS**

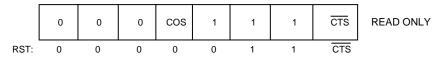

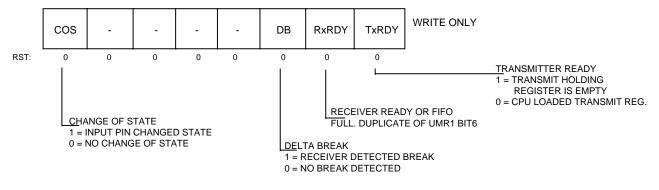

#### **UIPCR - INPUT PORT CHANGE REGISTER**

COS - WHEN SET INDICATES A LOW-TO-HIGH OR HIGH-TO-LOW TRANSITION LONGER THAN 25-50usec HAS OCCURRED ON INPUT PIN. AN IRQ IS GENERATED TO THE CPU, IF ENABLED

CTS - INDICATES THE CURRENT PIN STATE INPUT

#### **UIP - INPUT PORT REGISTER**

CTS - INDICATES THE CURRENT PIN STATE INPUT

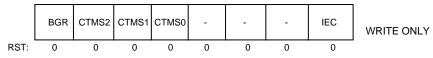

#### **UACR - AUXILIARY CONTROL REGISTER**

BGR=1, SET 2 OF BAUD RATES IS SELECTED BGR=0, SET 1 OF BAUD RATES IS SELECTED

CTMS[2:0] SHOULD BE SET TO 110

IEC = 1, ENABLE IRQ TO CPU BY A CHANGE OF STATE ON CTS INPUT.

IEC = 0, NO IRQ IS GENERATED TO CPU BECAUSE OF A CHANGE ON CTS

5307 UART Module

#### $oldsymbol{oldsymbol{M}})$ motorola

## **UART REGISTERS**

##

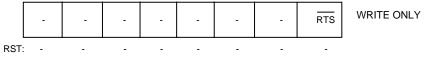

Write a 1 to force RTS low

**BIT RESET**

Write a 1 to force RTS high

5307 UART Module Motorola ColdFire ®

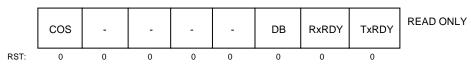

## INTERRUPT ENABLE & STATUS

#### **UISR** - INTERRUPT STATUS REGISTER

#### **UIMR** - INTERRUPT MASK REGISTER

5307 UART Module

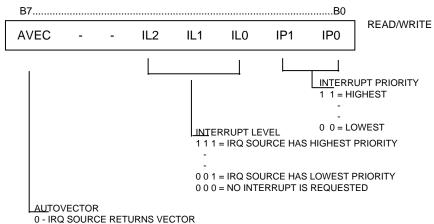

## **UART INTERRUPT CONTROL**

#### ICR 3 & 4- UART INTERRUPT CONTROL REGISTER 3 & 4

1 - SIM GENERATES AVEC FOR IRQ SOURCE

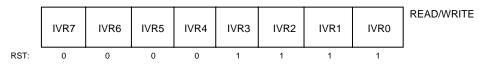

#### **UIVR** - INTERRUPT VECTOR REGISTER

5307 UART Module

Motorola ColdFire ®