# Microstep Operation-Supported 4-Phase Stepping Motor Driver ( $I_O = 1.5A$ )

#### Overview

The STK672-040 is a unipolar constant-current choppertype externally-excited 4-phase stepping motor driver hybrid IC which uses MOSFET power devices. It has a microstep operation-supported 4-phase distributed controller built-in to realize a high torque, low vibration, low noise stepping motor driver using a simple control circuit.

#### **Applications**

• Printer, copier, and X-Y plotter stepping motor drivers

#### **Features**

- Microstep sine-wave driver operation using only an external clock input  $(0.33\Omega)$  current detection resistor built-in)

- Microstep drive using only an external reference voltage setting resistor

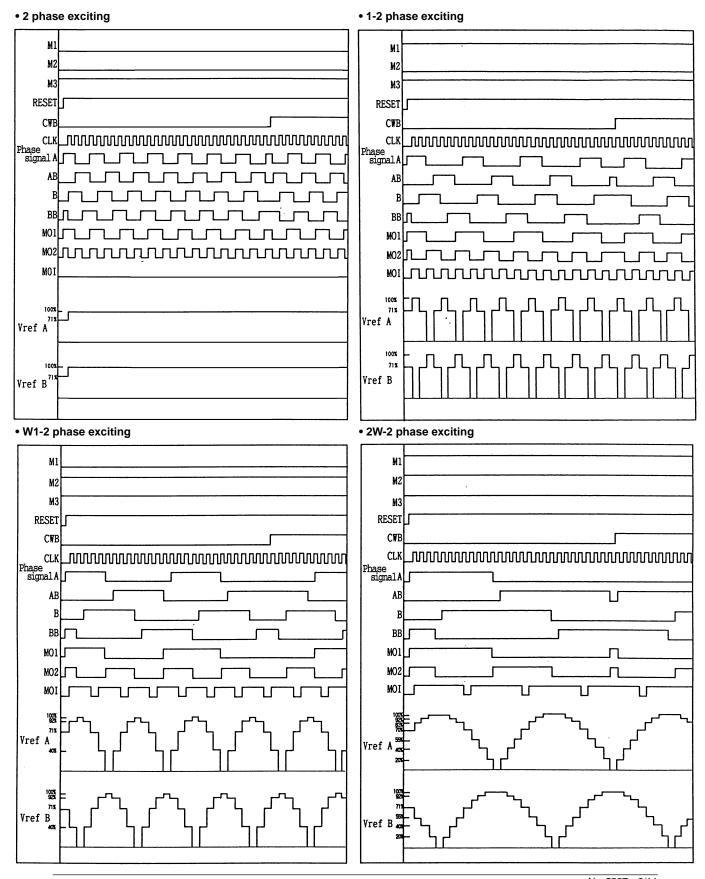

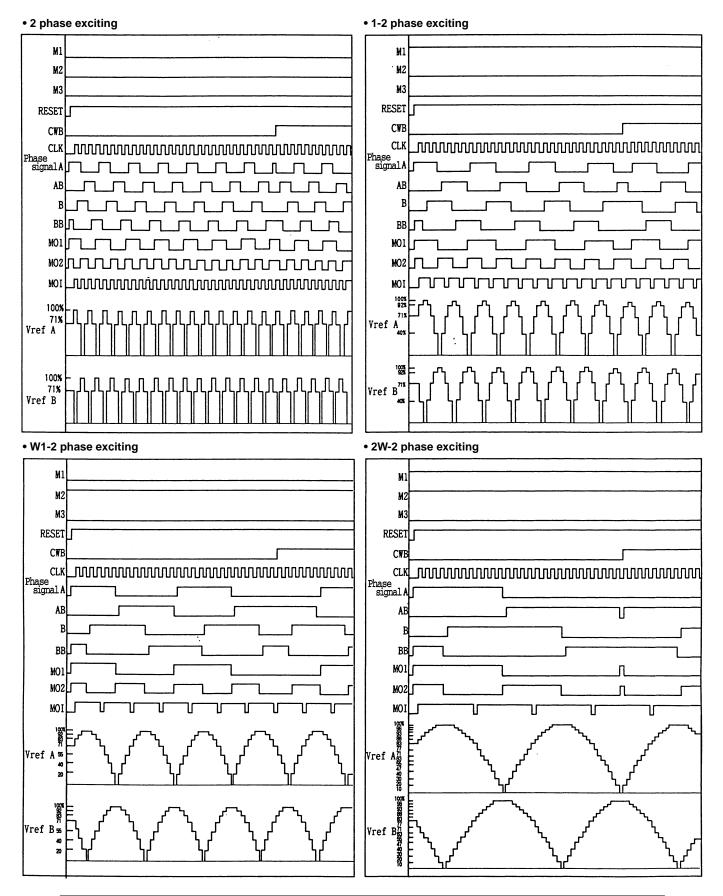

- 2, 1-2, W1-2, 2W1-2, 4W1-2 phase excitation selectable using external pins

- Selectable vector locus (perfect circle mode, inside 1 mode, outside 2 modes) to match motor characteristics in microstep drive state

- Phase hold function during excitation switching

- Schmitt trigger inputs with built-in pull-up resistor  $(20k\Omega)$

- Monitor output pin enabling real-time confirmation of IC excitation

- The CLK and RETURN inputs provide an internal noise elimination circuit as well as CMOS Schmitt circuit to prevent malfunction due to impulse noise.

- 4-phase distribution switch timing selected externally to either CLK rising-edge only detection mode or both rising-edge and falling-edge detection mode

- ENABLE pin for excitation current cutoff, thereby reducing system current drain when driver is stopped

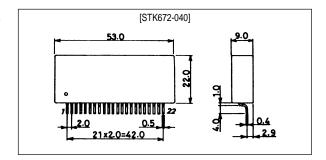

# Package Dimensions

unit: mm

4161

# **Series Organization**

The following devices form a series with differing output capacity.

| Type No.   | Output current (A) |

|------------|--------------------|

| STK672-040 | 1.5                |

| STK672-050 | 3.0                |

# **Specifications**

# **Maximum Ratings** at Ta = 25°C

| Parameter                                | Symbol                | Conditions                                                                 | Ratings      | Unit |

|------------------------------------------|-----------------------|----------------------------------------------------------------------------|--------------|------|

| Maximum supply voltage 1                 | V <sub>CC</sub> 1 max | No signal                                                                  | 52           | V    |

| Maximum supply voltage 2                 | V <sub>CC</sub> 2 max | No signal                                                                  | -0.3 to +7.0 | V    |

| Input voltage                            | V <sub>IN</sub> max   | Logic input block                                                          | -0.3 to +7.0 | V    |

| Phase output current                     | I <sub>OH</sub> max   | One 0.5s pulse, $V_{CC}1$ applied, Load/phase: $R = 5\Omega$ , $L = 10$ mH | 2.2          | А    |

| Repetitive avalanche handling capability | Ear max               |                                                                            | 38           | mJ   |

| Maximum output dissipation               | Pd max                | θc–a = 0                                                                   | 12           | W    |

| Operating substrate temperature          | Tc max                |                                                                            | 105          | °C   |

| Junction temperature                     | Tj max                |                                                                            | 150          | °C   |

| Storage temperature                      | Tstg                  |                                                                            | -40 to +125  | °C   |

# Allowable Operating Ranges at Ta = 25°C

| Parameter                      | Symbol              | Conditions                                  | Ratings   | Unit |

|--------------------------------|---------------------|---------------------------------------------|-----------|------|

| Supply voltage 1               | V <sub>CC</sub> 1   | With signal                                 | 10 to 45  | V    |

| Supply voltage 2               | V <sub>CC</sub> 2   | With signal 5.0 ± 5%                        |           | V    |

| Input voltage                  | V <sub>IH</sub>     | 0 to V <sub>CC</sub> 2                      |           | V    |

| Phase driver withstand voltage | V <sub>DSS</sub>    | Tr1, 2, 3, 4 (A, A, B, B outputs) 100 (min) |           | V    |

| Phase current                  | I <sub>OH</sub> max | 50% duty                                    | 1.5 (max) | А    |

# **Electrical Characteristics** at $Tc = 25^{\circ}C$ , $V_{CC}1 = 24V$ , $V_{CC}2 = 5V$

| Parameter                      | Symbol                                | Conditions                                              | min   | typ   | max   | Unit |

|--------------------------------|---------------------------------------|---------------------------------------------------------|-------|-------|-------|------|

| Control supply current         | I <sub>CC</sub>                       | Pin 7 input, ENABLE = low                               | -     | 4.5   | 15    | mA   |

| Output saturation voltage      | Vsat                                  | $R_L = 15\Omega (I = 1.5A)$                             | -     | 1.4   | 1.9   | V    |

| Average output current         | lo ave                                | Vref = 1V,<br>Load/phase: $R = 3.5\Omega$ , $L = 3.8mH$ | 0.465 | 0.517 | 0.569 | А    |

| FET diode forward voltage      | Vdf                                   | If = 1.0A                                               | -     | 1.2   | 1.8   | V    |

| [Control inputs]               | <u> </u>                              |                                                         |       |       | •     |      |

| Input voltage                  | V <sub>IH</sub>                       | Excluding Vref pin                                      | 4.0   | _     | _     | V    |

| Input voltage                  | V <sub>IL</sub>                       | Excluding Vref pin                                      | -     | -     | 1.0   | V    |

| Input ourrent                  | I <sub>IH</sub>                       | Excluding Vref pin                                      | 0     | 1     | 10    | μΑ   |

| Input current                  | I <sub>IL</sub>                       | Excluding Vref pin                                      | 125   | 250   | 510   | μΑ   |

| [Vref input]                   | <u> </u>                              |                                                         | -1    | 1     |       |      |

| Input voltage                  | V <sub>I</sub>                        | Pin 8                                                   | 0     | _     | 2.5   | V    |

| Input current                  | l <sub>l</sub>                        | Pin 8                                                   | -     | 1     | -     | μΑ   |

| [Control outputs]              |                                       |                                                         | -     |       | •     |      |

| Output valtage                 | V <sub>OH</sub>                       | I = -3mA (MoI, Mo1, Mo2 pins)                           | 2.4   | _     | _     | V    |

| Output voltage                 | V <sub>OL</sub>                       | I = +3mA (MoI, Mo1, Mo2 pins)                           | _     | -     | 0.4   | V    |

| PWM frequency                  | fc                                    |                                                         | 37    | 47    | 57    | kHz  |

| [Current division ratio (A/B)] | · · · · · · · · · · · · · · · · · · · |                                                         |       | !     | !     | 1.   |

| 2W1-2, W1-2, 1-2               | Vref                                  | θ = 1/8                                                 |       |       | 100   | %    |

| 2W1-2, W1-2                    | Vref                                  | $\theta = 2/8$                                          | 92    |       | %     |      |

| 2W1-2                          | Vref                                  | $\theta = 3/8$                                          |       | 83 %  |       |      |

| 2W1-2, W1-2, 1-2               | Vref                                  | $\theta = 4/8$                                          |       |       | 71    | %    |

| 2W1-2       | Vref | $\theta = 5/8$ | 55  | % |

|-------------|------|----------------|-----|---|

| 2W1-2, W1-2 | Vref | θ = 6/8        | 40  | % |

| 2W1-2       | Vref | θ = 7/8        | 20  | % |

| 2           | Vref |                | 100 | % |

Note: All tests are made using a constant-voltage supply.

The current division ratio shows the design value.

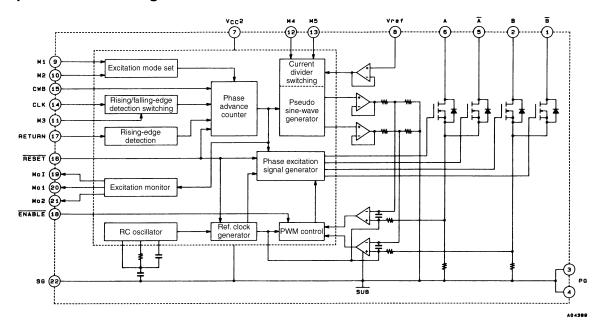

# **Equivalent Block Diagram**

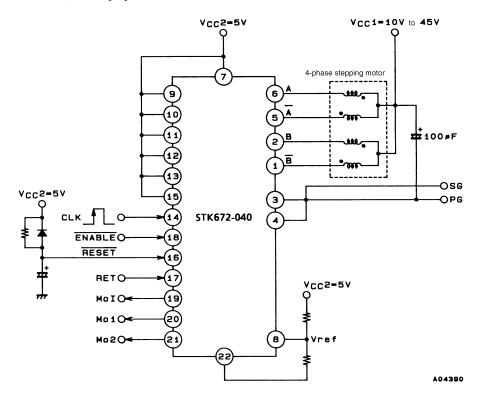

# **Sample Application Circuit**

2W1-2 phase excitation (microstep operation)

#### **Motor Current Calculation**

The motor current  $I_{OH}$  is determined by the reference voltage on pin 8 (Vref). The relationship between  $I_{OH}$  and Vref is given by the following equation.

$$I_{OH} = \frac{1}{3} \times Vref/Rs$$

where Rs is the built-in current detection resistance  $(0.33\Omega \pm 3\%).$

The motor current ranges from the current due to the frequency duty set by the oscillator (0.05 to 0.1A) to the allowable operating range maximum of  $I_{OH} = 1.5A$ .

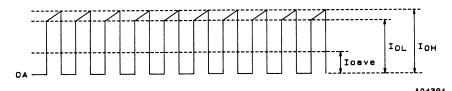

Motor current waveform

# **Function Tables**

| M1 | M2 | М3 | Excitation  | Phase switching CLK edge timing |  |  |

|----|----|----|-------------|---------------------------------|--|--|

| 0  | 0  | 0  | Phase 1-2   |                                 |  |  |

| 0  | 1  | 0  | Phase 2W1-2 | Rising and falling edge         |  |  |

| 1  | 0  | 0  | Phase W1-2  | - Itising and failing edge      |  |  |

| 1  | 1  | 0  | Phase 4W1-2 |                                 |  |  |

| 0  | 0  | 1  | Phase 2     |                                 |  |  |

| 0  | 1  | 1  | Phase W1-2  | Rising edge only                |  |  |

| 1  | 0  | 1  | Phase 1-2   | Nising edge only                |  |  |

| 1  | 1  | 1  | Phase 2W1-2 |                                 |  |  |

| RESET |    |    | Low    |

|-------|----|----|--------|

| Mo1   | Мо | 02 | Output |

| 0     | 0  | )  | Ā      |

| 0     |    |    | 2      |

Input ENABLE Active level

Low

| CWB | Direction |

|-----|-----------|

| 0   | Forward   |

| 1   | Reverse   |

| Mo1 | Mo2 | Output |

|-----|-----|--------|

| 0   | 0   | Ā      |

| 0   | 1   | В      |

| 1   | 0   | A      |

| 1   | 1   | B      |

# **Design material**

# 1. Explanation of input pins

| Pin No.   | Name       | Function                                                     | Pin format                                         |

|-----------|------------|--------------------------------------------------------------|----------------------------------------------------|

| 14        | CLK        | Phase switching phase                                        | CMOS Schmitt configuration with pull-down resistor |

| 15        | CWB        | Setting of rotation direction (CW/CCW)                       | CMOS Schmitt configuration with pull-down resistor |

| 17        | RETURN     | Phase origin forced return                                   | CMOS Schmitt configuration with pull-down resistor |

| 18        | ENABLE     | Output cut-off CMOS Schmitt configuration with pull-down res |                                                    |

| 9, 10, 11 | M1, M2, M3 | Setting of exciting mode                                     | CMOS Schmitt configuration with pull-down resistor |

| 12, 13    | M4, M5     | Setting of vector locus                                      | CMOS Schmitt configuration with pull-down resistor |

| 16        | RESET      | System reset                                                 | CMOS Schmitt configuration with pull-down resistor |

| 8         | Vref       | Setting of current value                                     | CMOS Schmitt configuration with pull-down resistor |

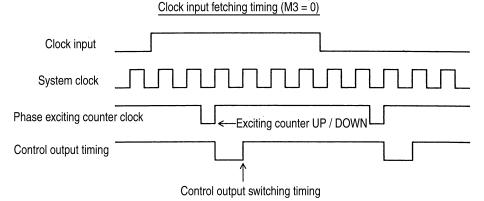

#### 2. Functions and timing of input signals

#### 2-1. CLK (Phase switching clock)

1. Input frequency range ■DC to 50 kHz

2. Minimum pulse width 10 μs3. Duty 40 to 60%

4. Pin format ■CMOS Schmitt containing pull-up resistor (20 kΩ typical value)

5. Noise eliminating circuit with multiple stages is contained.

- 6. Functions

- a. When the signal M3 is set to 1 or it is opened.

The exciting phase moves at each step at the leading edge of the clock.

b. When the signal M3 is set to 0

The exciting phase moves at each step at the leading and trailing edges of the clock.

# 2-2. CWB (Setting of rotation direction)

- 1. Pin format ■CMOS Schmitt configuration containing pull-up resistor (20kΩ, typical value)

- 2. Function

- a. When the signal CWB is set to 1 It rotates clockwise.

- b. When the signal CWB is set to 0

It rotates counterclockwise.

#### 2-3. RETURN (It forcibly returns the phase to the origin of current exciting phase.)

- 1. Pin format ■CMOS Schmitt configuration containing pull-up resistor (20kΩ, typical value)

- 2. Noise eliminating circuit is contained.

- 3. Function Forces to moves to the origin of current exciting phase by setting the RETURN signal to high state.

# 2-4. ENABLE(ON/OFF control of exciting drive output A, A, B, and B and selection of operation/hold state in HI-IC)

- 1. Pin format ■CMOS Schmitt configuration containing pull-up resistor (20 kΩ, typical value)

- 2. Function

- a. When the ENABLE signal is set to a high state or it is opened.

It is usually placed in the operation status.

b. When the ENABLE signal is set to a low state

The H-IC is placed into the hold state, forcing the exciting drive output to be turned off. At this time, the system clock of the HC stops, the H-IC is not affected if the input pin other than the reset input changes.

#### 2-5. M1, M2, and M3 (Selection of exciting modes and clock input edge timing)

- 1. Pin format ■CMOS Schmitt configuration containing the pull-up resistor (20 kΩ typical value)

- 2. Functions

| M2    | 0                  | 0                   | 1                    | 1                    | Phase switching clock edge timing  |  |

|-------|--------------------|---------------------|----------------------|----------------------|------------------------------------|--|

| M3 M1 | 0                  | 1                   | 0                    | 1                    | Triase switching clock edge timing |  |

| 1     | 2 phase exciting   | 1-2 phase exciting  | W1-2 phase exciting  | 2W1-2 phase exciting | Only the leading edge              |  |

| 0     | 1-2 phase exciting | W1-2 phase exciting | 2W1-2 phase exciting | 4W1-2 phase exciting | Leading edge and trailing edge     |  |

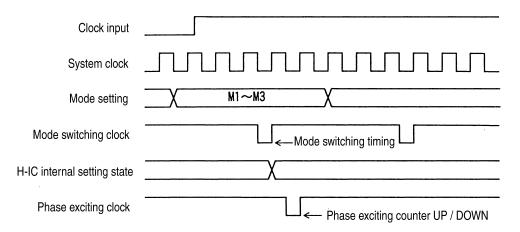

- 3. Valid timing of mode setting

- ■The mode must not be changed within 5 µs from the leading edge and trailing edge of the clock.

#### Fetching toming of mode setting

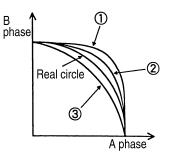

#### 2-6. M4 and M5 (Setting of rotation vector locus at micro-step)

| M4   | 1           | 0 | 1 | 0 |

|------|-------------|---|---|---|

| M5   | 1           | 0 | 0 | 1 |

| Mode | Real circle | ① | 2 | 3 |

For the current division ratio, see Section 4.3.

# 2-7. RESET (Reset of entire system)

(20 kΩ typical value)

2. Function All circuit states are set to the initial values by setting the RESET signal to the

low state (pulse width of 10 µs or more). At this time, for all modes including

the exciting mode, the A and  $\overline{B}$  phases are set to the origin.

#### 2-8. Vref(Setting of the current value used as the reference of constant current detection)

1. Pin format ■Analog input configuration

2. Function

By applying the voltage of 2.5 V or less of the control system power source

Voc2 the constant control can be performed over the exciting current of

Vcc2, the constant current control can be performed over the exciting current of the motor at the 100% of the rated current value.

■The constant current can be controlled in proportional to the Vref voltage with this value specified as a high limit.

#### 3. Explanation of output pins

| Pin No. | Name     | Function                      | Pin format                  |  |  |

|---------|----------|-------------------------------|-----------------------------|--|--|

| 19      | Mol      | Phase exciting origin monitor | CMOS standard configuration |  |  |

| 20, 21  | Mo1, Mo2 | Phase exciting state monitor  | CMOS standard configuration |  |  |

#### 4. Functions and timing of output signals

# 4-1. A, $\overline{A}$ , B, and $\overline{B}$ (Output for phase exciting use of motor)

1. Function In four phase two exciting mode, the interval of  $3.75 \,\mu s$  (typical value) is set when the output signals of the phases A and  $\overline{A}$ , B and  $\overline{B}$  change.

#### 4-2. MO1, MO2, and MOI (Monitor of exciting state)

1. Pin format ■CMOS standard configuration

2. Function Outputs the state of the current phase exciting output.

| Phase coordinate | A phase | B phase | Ā phase | B̄ phase |  |

|------------------|---------|---------|---------|----------|--|

| Mo1              | 1       | 0       | 0       | 1        |  |

| Mo2              | 0       | 1       | 0       | 1        |  |

For the MOI, 0 is output at the origin of each phase. At other points, 1 is output.

# STK672-040

# 4-3. Current division ratio based on M3, M4, and M5 . . . . . . Reference values

| Mode                   |          | Real circle | 1      | 2      | 3      |        |      |                 |         |

|------------------------|----------|-------------|--------|--------|--------|--------|------|-----------------|---------|

| Setting M              | M3 = 0   | M3 = 1      | M4 = 1 | M4 = 0 | M4 = 1 | M4 = 0 | Unit | Number of steps |         |

|                        | IVIS = U |             | M5 =1  | M5 = 0 | M5 =1  | M5 = 0 |      |                 |         |

| Current division ratio | 4W1–2    |             | 14     | 15     | 15     | 13     | %    |                 | 1 / 16  |

|                        |          | 2W1-2       | 20     | 25     | 23     | 19     |      | 1/8             | 2/16    |

|                        |          |             | 31     | 34     | 33     | 28     |      |                 | 3 / 16  |

|                        |          | 2W1-2       | 40     | 44     | 42     | 39     |      | 2/8             | 4 / 16  |

|                        |          |             | 48     | 51     | 49     | 45     |      |                 | 5 / 16  |

|                        |          | 2W1-2       | 55     | 62     | 57     | 54     |      | 3/8             | 6 / 16  |

|                        |          |             | 65     | 69     | 65     | 62     |      |                 | 7 / 16  |

|                        |          | 2W1-2       | 71     | 77     | 71     | 69     |      | 4/8             | 8 / 16  |

|                        |          |             | 77     | 82     | 77     | 74     |      |                 | 9/16    |

|                        |          | 2W1-2       | 83     | 88     | 85     | 82     |      | 5/8             | 10 / 16 |

|                        |          |             | 88     | 92     | 89     | 85     |      |                 | 11 / 16 |

|                        |          | 2W1-2       | 92     | 95     | 95     | 92     |      | 6/8             | 12 / 16 |

|                        |          |             | 97     | 98     | 98     | 94     |      |                 | 13 / 16 |

|                        |          | 2W1-2       | 100    | 100    | 100    | 100    |      | 7/8             | 14 / 16 |

[Load conditions]  $\mbox{Vccl} = \mbox{24V, Vcc2} = \mbox{5V, R / L} = \mbox{3.5}\Omega \mbox{/ 3.8mH}$

# 5. Phase exciting and timing chart

# 5-1. Leading edge operation of clock

# 5-2. Leading edge and trailing edge operation of clock

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees, jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of January, 1997. Specifications and information herein are subject to change without notice.