CMOS IC

LC895127, 895127K

# 40× CD-ROM Decoder with SCSI Interface

# **Functions**

- CD-ROM ECC function

- SCSI I/F function

- Subcode I/F function

- CAV audio function

## **Features**

- SCSI interface (includes on-chip SCAM selection register)

- Supports 20× speed and a 10 MBytes/s transfer rate when using 16-bit 70-ns EDO DRAM

- Supports 40× speed and a 10 MB/s transfer rate when using 16-bit 50-ns EDO DRAM

- Up to 4 M bits of buffer RAM can be used.

- The user can freely set up the CD main channel and the C2 flag areas in buffer RAM.

- Batch transfer function (Allows the CD main channel, the C2 flags, and other data to be sent in a single operation.)

- Multi-block transfer function (Allows multiple blocks to be sent automatically in a single operation.)

- Subcode buffering and CD-TEXT support

# Specifications

## Absolute Maximum Ratings at $V_{SS} = 0 V$

- CAV audio function

- Supports 20 MBytes/s transfers

- Package: SQFP-144

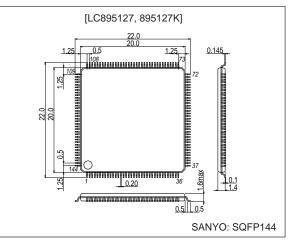

# **Package Dimensions**

unit: mm

## 3214-SQFP144

| Parameter                             | Symbol                          | Conditions | Ratings                       | Unit |

|---------------------------------------|---------------------------------|------------|-------------------------------|------|

| Maximum supply voltage                | V <sub>DD</sub> max             | Ta = 25°C  | -0.3 to +7.0                  | V    |

| Input/output voltage                  | V <sub>I</sub> , V <sub>O</sub> | Ta = 25°C  | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Allowable power dissipation           | Pd max                          | Ta ≤ 70°C  | 550                           | mW   |

| Operating temperature                 | Topr                            |            | -30 to +70                    | °C   |

| Storage temperature                   | Tstg                            |            | -55 to +125                   | °C   |

| Soldering temperature (pin part only) |                                 | 10 s       | 260                           | °C   |

### Allowable Operating Ranges at Ta = $-30^{\circ}$ C to $+70^{\circ}$ C, V<sub>SS</sub> = 0 V

| Parameter           | Symbol          | Conditions |     | Ratings | Unit            |      |

|---------------------|-----------------|------------|-----|---------|-----------------|------|

| Palameter           | Symbol          | Conditions | min | typ     | max             | Unit |

| Supply voltage      | V <sub>DD</sub> |            | 4.5 | 5.0     | 5.5             | V    |

| Input voltage range | V <sub>IN</sub> |            | 0   |         | V <sub>DD</sub> | V    |

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

## SANYO Electric Co., Ltd. Semiconductor Company TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

| Demonster                 | Quarter          | Qualities                 | Angliashla gina |                       | Ratings |                     | Unit |

|---------------------------|------------------|---------------------------|-----------------|-----------------------|---------|---------------------|------|

| Parameter                 | Symbol           | Conditions                | Applicable pins | min                   | typ     | max                 |      |

| Input high-level voltage  | V <sub>IH1</sub> | TTL levels                | (1)             | 2.2                   |         |                     | V    |

| Input low-level voltage   | V <sub>IL1</sub> |                           | (1)             |                       |         | 0.8                 | V    |

| Input high-level voltage  | V <sub>IH2</sub> | TTL levels                | (9)             | 2.2                   | -       | —                   | V    |

| Input low-level voltage   | V <sub>IL2</sub> | with pull-up resistor     | (9)             | —                     |         | 0.8                 | V    |

| Input high-level voltage  | V <sub>IH3</sub> | TTL levels                | (2)             | 2.2                   | _       | —                   | V    |

| Input low-level voltage   | V <sub>IL3</sub> | Schmitt                   | (2)             | —                     | —       | 0.8                 | V    |

| Input high-level voltage  | V <sub>IH4</sub> | CMOS levels               | (3)             | 0.8 V <sub>DD</sub>   | _       | —                   | V    |

| Input low-level voltage   | V <sub>IL4</sub> | Schmitt                   | (3)             | —                     | _       | 0.2 V <sub>DD</sub> | V    |

| Input high-level voltage  | V <sub>IH5</sub> |                           | (4), (8), (10)  | 2.0                   |         | —                   | V    |

| Input low-level voltage   | V <sub>IL5</sub> |                           | (4), (8), (10)  |                       |         | 0.8                 | V    |

| Input high-level voltage  | V <sub>IH2</sub> | TTL levels                | (11)            | 2.2                   |         | —                   | V    |

| Input low-level voltage   | V <sub>IL2</sub> | with pull-up resistor     | (11)            | —                     | _       | 0.8                 | V    |

| Output high-level voltage | V <sub>OH1</sub> | I <sub>OH1</sub> = -12 mA | (6)             | V <sub>DD</sub> - 2.1 | _       | —                   | V    |

| Output low-level voltage  | V <sub>OL1</sub> | I <sub>OL1</sub> = 12 mA  | (0)             | —                     | _       | 0.4                 | V    |

| Output high-level voltage | V <sub>OH2</sub> | I <sub>OH2</sub> = -8 mA  | (7)             | 2.4                   |         |                     | V    |

| Output low-level voltage  | V <sub>OL2</sub> | I <sub>OL2</sub> = 8 mA   | (7)             |                       |         | 0.4                 | V    |

| Output high-level voltage | V <sub>OH2</sub> | $I_{OH2} = -2 \text{ mA}$ | (9), (5), (11)  | 2.4                   |         |                     | V    |

| Output low-level voltage  | V <sub>OL2</sub> | I <sub>OL2</sub> = 2 mA   | (3), (3), (11)  |                       |         | 0.4                 | V    |

| Output low-level voltage  | V <sub>OL4</sub> | I <sub>OL4</sub> = 48 mA  | (10)            |                       |         | 0.4                 | V    |

| Input leakage current     | IIL              | $V_{I} = V_{SS}, V_{DD}$  | All input pins  | -25                   |         | +25                 | μΑ   |

| Pull-up resistance        | R <sub>UP</sub>  |                           | (5), (9), (11)  | 60                    | 120     | 240                 | kΩ   |

## DC Characteristics at Ta = -30 to +70 $^{\circ}C,$ V\_{SS} = 0 V, V\_{DD} = 4.5 to 5.5 V

Applicable pin sets are as follows.

#### INPUT

(1) TEST0 to TEST4, CSCTRL, SUA0 to SUA6, C2P0, SDATA, BCK, LRCK, SCOR, WFCK, SBS0, MCK2SEL

- (2) RESET

- (3)  $\overline{CS}, \overline{RD}, \overline{WR}$

- (4) SCSISEL, XTALSEL

#### OUTPUT

- (5) INTO, INTI, SWAIT

- (6) MCK

- (7) EXCK, DSDATA, DLRCK, DBCK, RAS0, CAS0, CAS1, OE, UWE, LWE, RA0 to RA8

#### INOUT

- (8) ACK, ATN

- (9) D0 to D7, IO0 to IO15, IOP0 to IOP7

- (10)  $\overline{DB0}$  to  $\overline{DB7}$ ,  $\overline{DBP}$ ,  $\overline{BSY}$ , I/O,  $\overline{MSG}$ ,  $\overline{SEL}$ ,  $\overline{RST}$ ,  $\overline{REQ}$ , C/D

- (11) IOP0 to IOP7

Note: Pins XTAL0, XTALCK0, XTAL1, XTALCK1, and X1EN are not included in DC characteristics.

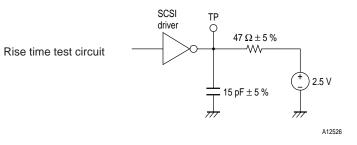

### **SCSI Pin Input Characteristics**

| Parameter               | Symbol            | Conditions                       | Ratings |      |      | Unit |

|-------------------------|-------------------|----------------------------------|---------|------|------|------|

| Farameter               | Symbol            | Conditions                       | min     | typ  | max  | Unit |

| Input threshold voltage | V <sub>t+t1</sub> |                                  |         | 1.60 | 2.00 | V    |

| Input theshold voltage  | V <sub>t-t1</sub> | V <sub>DD</sub> = 4.50 to 5.50 V | 0.80    | 1.10 |      | V    |

| Hysteresis width        | $\Delta V_{tt1}$  | V <sub>DD</sub> = 5.0 V          | 0.41    | 0.5  |      | V    |

### **Active-Low Output Characteristics**

| Parameter                 | Symbol          | Conditions | Ratings |     |     | Unit |

|---------------------------|-----------------|------------|---------|-----|-----|------|

| Palameter                 | Symbol          | Conditions | min     | typ | max | Unit |

| Output high-level voltage | V <sub>OH</sub> |            | 2.5     |     |     | V    |

| Output low-level voltage  | V <sub>OL</sub> |            |         |     | 0.4 | V    |

Note: Only applies to the active-low output pins  $\overline{\text{DB0}}$  to  $\overline{\text{DB7}}$ ,  $\overline{\text{REQ}}$ ,  $\overline{\text{DBPB}}$

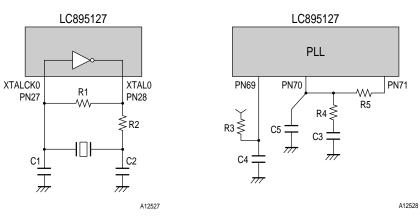

### **Recommended Oscillator and PLL Circuits**

$R1 = 120 \text{ k}\Omega$ ,  $R2 = 47 \Omega$ , C1 = 30 pF

Crystal oscillator frequency XTALCK0 = 16.9344 MHz

$R3 = 7.5 \text{ k}\Omega, R4 = 200 \Omega, R5 = 10 \text{ k}\Omega, C3 = 0.1 \mu\text{F}$

$C4=0.1~\mu F,\,C5=0.002~\mu F$  to 0.01  $\mu F$

Note: The values listed above for R3, R4, R5, and C3 also apply when the XTALKC0 frequency is 33.8688 MHz.

Applications must be designed so that the analog  $V_{DD}$  and  $V_{SS}$  power supply system is completely independent of the logic system power supply and is not affected by the logic system power supply fluctuation in any way.

Note: Since the exact values of these components will vary depending on the characteristics of the printed circuit board used and other factors, consult the manufacturer of the crystal element when designing the oscillator circuit.

## LC895127, 895127K

## **Pin Functions**

|   | Туре   |   |             |    |             |  |  |  |  |

|---|--------|---|-------------|----|-------------|--|--|--|--|

| I | INPUT  | В | BIDIRECTION | NC | NOT CONNECT |  |  |  |  |

| 0 | OUTPUT | Р | POWER       |    |             |  |  |  |  |

| Pin No. | Pin name                  | Туре | Pin functions                                                                       |

|---------|---------------------------|------|-------------------------------------------------------------------------------------|

| 1       | V <sub>SS0</sub>          | P    |                                                                                     |

| 2       | IO2                       | В    |                                                                                     |

| 3       | IO1                       | B    | Buffer RAM data I/O                                                                 |

| 4       | 100                       | В    | These pins have built-in pull-up resistors.                                         |

| 5       | MCK2SEL                   |      | PLL frequency selection. Currently, this pin must be connected to V <sub>DD</sub> . |

| 6       | C2PO                      |      |                                                                                     |

| 7       | SDATA                     | 1    |                                                                                     |

| 8       | BCK                       | 1    | CD DSP interface                                                                    |

| 9       | LRCK                      |      |                                                                                     |

| 10      | EXCK                      | 0    | Subcode I/O                                                                         |

| 10      | WFCK                      | 1    |                                                                                     |

| 12      | SBSO                      |      |                                                                                     |

| 12      | SCOR                      |      | Subcode I/O                                                                         |

| 13      | DSDATA                    | 0    |                                                                                     |

| 14      | DSDATA                    | 0    |                                                                                     |

| 15      | DERCK                     | 0    | D/A converter outputs                                                               |

| 17      | MCK                       | 0    | XTALCLK0.1/1.1/2 and stan autout                                                    |

|         |                           | P    | XTALCLK0 1/1, 1/2, and stop output                                                  |

| 18      | V <sub>DD</sub>           | P    |                                                                                     |

| 19      | V <sub>SS0</sub><br>RESET |      | I O seast The IO's seast as a low bool issue                                        |

| 20      | _                         |      | IC reset. The IC is reset on a low-level input                                      |

| 21      | CSCTRL                    |      | MC (Microcontroller) CSL <sub>0</sub> , Hi                                          |

| 22      | TEST3                     |      |                                                                                     |

| 23      | TEST0                     | I    | Test pins. These pins must be connected to V <sub>SS0</sub> in normal operation.    |

| 24      | TEST1                     |      |                                                                                     |

| 25      | TEST2                     |      |                                                                                     |

| 26      | V <sub>SS0</sub>          | P    |                                                                                     |

| 27      | XTALCK0                   |      | Crystal oscillator circuit input                                                    |

| 28      | XTAL0                     | 0    | Crystal oscillator circuit output                                                   |

| 29      | TEST4                     |      | Test pin. This pin must be connected to V <sub>SS0</sub> in normal operation.       |

| 30      | V <sub>SS0</sub>          | P    |                                                                                     |

| 31      | V <sub>SS0</sub>          | P    |                                                                                     |

| 32      | V <sub>SS0</sub>          | P    |                                                                                     |

| 33      | V <sub>SS0</sub>          | P    |                                                                                     |

| 34      | IOP7                      |      | General-purpose I/O ports. These pins include built-in pull-up resistors.           |

| 35      | IOP6                      |      |                                                                                     |

| 36      | V <sub>SS0</sub>          | P    |                                                                                     |

| 37      | V <sub>DD</sub>           | P    |                                                                                     |

| 38      | IOP5                      |      |                                                                                     |

| 39      | IOP4                      | <br> |                                                                                     |

| 40      | IOP3                      | I    | General-purpose I/O ports. These pins include built-in pull-up resistors.           |

| 41      | IOP2                      |      |                                                                                     |

| 42      | IOP1                      |      | -                                                                                   |

| 43      | IOP0                      | 1    |                                                                                     |

| 44      | V <sub>SS0</sub>          | Р    |                                                                                     |

| 45      | RD                        | 1    | Microcontroller data read signal input                                              |

| 46      | WR                        | 1    | Microcontroller data write signal input                                             |

| 47      | CS                        | 1    | Register chip select input from the microcontroller                                 |

| 48      | SUA0                      | 1    |                                                                                     |

| 49      | SUA1                      | 1    |                                                                                     |

| 50      | SUA2                      | 1    | Microcontroller register selection signals                                          |

| 51      | SUA3                      | 1    |                                                                                     |

| 52      | SUA4                      | 1    |                                                                                     |

| 52      |                           |      |                                                                                     |

Continued on next page.

## LC895127, 895127K

Continued from preceding page.

| Pin No. | Pin                   | I/O | Function                                                                                             |

|---------|-----------------------|-----|------------------------------------------------------------------------------------------------------|

| 54      | V <sub>DD</sub>       | Р   |                                                                                                      |

| 55      | V <sub>SS0</sub>      | Р   |                                                                                                      |

| 56      | SUA6                  | 1   | Microcontroller register selection signals                                                           |

| 57      | D0                    | В   |                                                                                                      |

| 58      | D1                    | В   |                                                                                                      |

| 59      | D2                    | В   |                                                                                                      |

| 60      | D3                    | В   | Microcontroller data signals                                                                         |

| 61      | D4                    | В   | -                                                                                                    |

| 62      | D5                    | В   |                                                                                                      |

| 63      | V <sub>SS0</sub>      | P   |                                                                                                      |

| 64      | <br>D6                | B   |                                                                                                      |

| 65      | D7                    | B   | Microcontroller data signals                                                                         |

| 66      |                       | 0   | Interrupt request signal output to the microcontroller (ECC side. Set by setting a register value.)  |

|         |                       | 0   |                                                                                                      |

| 67      |                       |     | Interrupt request signal output to the microcontroller (SCSI side. Set by setting a register value.) |

| 68      | SWAIT                 | 0   | Wait signal output to the microcontroller                                                            |

| 69      | X1EN                  |     | Used by the PLL. This pin must be connected to V <sub>DD</sub> through a resistor.                   |

| 70      | XTALCK1               |     | Used by the PLL.                                                                                     |

| 71      | XTAL1                 | 0   | Used by the PLL.                                                                                     |

| 72      | V <sub>SS0</sub>      | P   | Analog V <sub>SS</sub>                                                                               |

| 73      | V <sub>DD</sub>       | Р   | Analog V <sub>DD</sub>                                                                               |

| 74      |                       | NC  |                                                                                                      |

| 75      | I/O                   | В   | SCSI interface                                                                                       |

| 76      | REQ                   | В   |                                                                                                      |

| 77      | V <sub>SS1</sub>      | Р   |                                                                                                      |

| 78      | C/D                   | В   |                                                                                                      |

| 79      | SEL                   | В   | SCSI interface                                                                                       |

| 80      |                       | NC  |                                                                                                      |

| 81      | V <sub>DD</sub>       | Р   |                                                                                                      |

| 82      | V <sub>SS1</sub>      | Р   |                                                                                                      |

| 83      | MSG                   | В   |                                                                                                      |

| 84      | RST                   | В   | SCSI interface                                                                                       |

| 85      | V <sub>SS1</sub>      | P   |                                                                                                      |

| 86      | ACK                   | В   |                                                                                                      |

| 87      | BSY                   | B   | SCSI interface                                                                                       |

|         |                       | В   |                                                                                                      |

| 88      | V <sub>SS1</sub>      |     |                                                                                                      |

| 89      | ATN                   | В   | SCSI interface                                                                                       |

| 90      | V <sub>DD</sub>       | P   |                                                                                                      |

| 91      | V <sub>SS1</sub>      | P   |                                                                                                      |

| 92      |                       | NC  |                                                                                                      |

| 93      | DBP                   | В   | SCSI interface                                                                                       |

| 94      | V <sub>DD</sub>       | Р   |                                                                                                      |

| 95      | DB7                   | В   | SCSI interface                                                                                       |

| 96      | DB6                   | В   |                                                                                                      |

| 97      | V <sub>SS1</sub>      | Р   |                                                                                                      |

| 98      | DB5                   | В   | SCSI interfere                                                                                       |

| 99      | DB4                   | В   | SCSI interface                                                                                       |

| 100     | V <sub>DD</sub>       | Р   |                                                                                                      |

| 101     | DB3                   | В   |                                                                                                      |

| 102     | DB2                   | В   | SCSI interface                                                                                       |

|         | V <sub>SS1</sub>      | Р   |                                                                                                      |

| 103     |                       | В   |                                                                                                      |

|         | DB1                   |     |                                                                                                      |

| 104     | DB1                   |     | SCSI interface                                                                                       |

|         | DB1<br>DB0<br>SCSISEL | B   | SCSI interface<br>SCSI pin layout selection. (This pin must be connected to V <sub>SS0</sub> .)      |

Continued on next page.

### LC895127, 895127K

Continued from preceding page.

| Pin No. | Pin              | I/O | Function                                                          |

|---------|------------------|-----|-------------------------------------------------------------------|

| 108     | V <sub>SS1</sub> | Р   |                                                                   |

| 109     | V <sub>DD</sub>  | Р   |                                                                   |

| 110     | V <sub>SS0</sub> | Р   |                                                                   |

| 111     | RAS0             | 0   | Buffer RAM RAS signal output 0                                    |

| 112     | V <sub>DD</sub>  | Р   |                                                                   |

| 113     | CAS0             | 0   | Buffer RAM CAS signal output 0 (Normally held fixed at 0 (low).)  |

| 114     | CAS1             | 0   | Buffer RAM RAS signal output 1                                    |

| 115     | ŌĒ               | 0   | Buffer RAM output enable                                          |

| 116     | UWE (RA9)        | 0   | Buffer RAM upper write enable (RA9 when 8M or more DRAM is used.) |

| 117     | LWE              | 0   | Buffer RAM lower write enable                                     |

| 118     | V <sub>SS0</sub> | Р   |                                                                   |

| 119     | RA0              | 0   |                                                                   |

| 120     | RA1              | 0   |                                                                   |

| 121     | RA2              | 0   |                                                                   |

| 122     | RA3              | 0   | Buffer RAM address signal outputs                                 |

| 123     | RA4              | 0   |                                                                   |

| 124     | RA5              | 0   |                                                                   |

| 125     | RA6              | 0   |                                                                   |

| 126     | V <sub>DD</sub>  | Р   |                                                                   |

| 127     | V <sub>SS0</sub> | Р   |                                                                   |

| 128     | RA7              | 0   |                                                                   |

| 129     | RA8              | 0   | Buffer RAM address signal outputs                                 |

| 130     | IO15             | В   |                                                                   |

| 131     | IO14             | В   |                                                                   |

| 132     | IO13             | В   |                                                                   |

| 133     | IO12             | В   | Buffer RAM data I/O                                               |

| 134     | IO11             | В   | These pins have built-in pull-up resistors.                       |

| 135     | IO10             | В   |                                                                   |

| 136     | IO9              | В   | ]                                                                 |

| 137     | IO8              | В   |                                                                   |

| 138     | V <sub>SS0</sub> | Р   |                                                                   |

| 139     | 107              | В   |                                                                   |

| 140     | IO6              | В   |                                                                   |

| 141     | IO5              | В   | Buffer RAM data I/O                                               |

| 142     | IO4              | В   | These pins have built-in pull-up resistors.                       |

| 143     | IO3              | В   | ]                                                                 |

| 144     | V <sub>DD</sub>  | Р   |                                                                   |

Unused ("NC") pins must be left open. Pins whose name is under a bar operate with inverted (negative) logic.  $V_{SS0}$  is the logic system ground and  $V_{SS1}$  is the SCSI interface driver ground.

If DRAM is used, applications must adopt measures to prevent undershoot and other DRAM problems. Such measures include inserting resistors in the RAS

and CAS lines and inserting capacitors between  $V_{SS}$  pins. See the article on Designing with the Latest Microcontrollers and Memory in special issue number 25 of Transistor Technology for details on these measures. Since this device includes buffers that sink a current of 48 mA, applications must take adequate noise prevention measures.

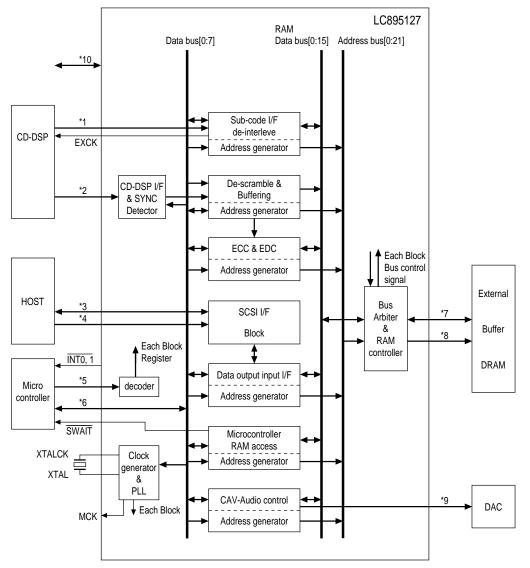

## **Block Diagram**

A12529

- \*1 WFCK, SBSO, SCOR

- \*2 BCK, SDATA, LRCK, C2PO

- \*3 DB0 to DB7, DBP, BSY, MSG, SEL, RST, REQ, I/O, C/D

- \*4 ACK, ATN

- \*5 RD, WR, SUA0 to SUA6, ZCS, CSCTRL

- \*6 D0 to D7

- \*7 IO0 to IO15

- \*8 RA0 to RA10, RAS1, CAS0, CAS1, OE, UWE, LWE

- \*9 DBCK, DLRCK, DSDATA

- \*10 IOP7 to IOP0

- Specifications of any and all SANYO products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Electric Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO products (including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of SANYO Electric Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of December, 1999. Specifications and information herein are subject to change without notice.