# MNDSPEED

## CX28342/3/4/6/8

### Dual/Triple/Quad/Hex/Octal-Enhanced DS3/E3 Framer

The CX28342/3/4/6/8 provides Dual, Triple, Quad, Hex, and Octal DS3/E3 framers designed to support DS3-M13, DS3-C-bit parity, E3-G.751, and E3-G.832 transmission formats.

The CX28342/3/4/6/8 provides framing recovery for M13, M23, C-bit parity, G.751, and G.832 formatted signals. A FIFO buffer in the receive path can be enabled to reduce jitter on the incoming data. The CX28342/3/4/6/8 devices allow for ease of configuration, while providing maximum flexibility to support the transmission and recovery of industry standard formats. It provides a flexible overhead bit generation method in DS3/E3 modes to source overhead bits on an individual framer.

NOTE:

The index letter *i*, appearing in a register's name, represents the channel number, one per channel.

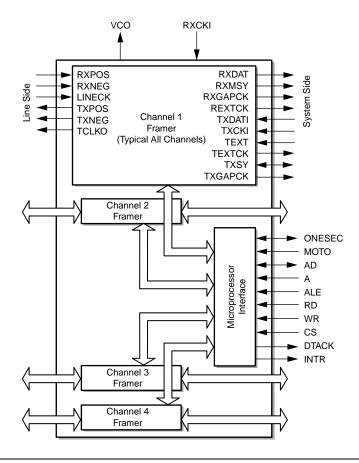

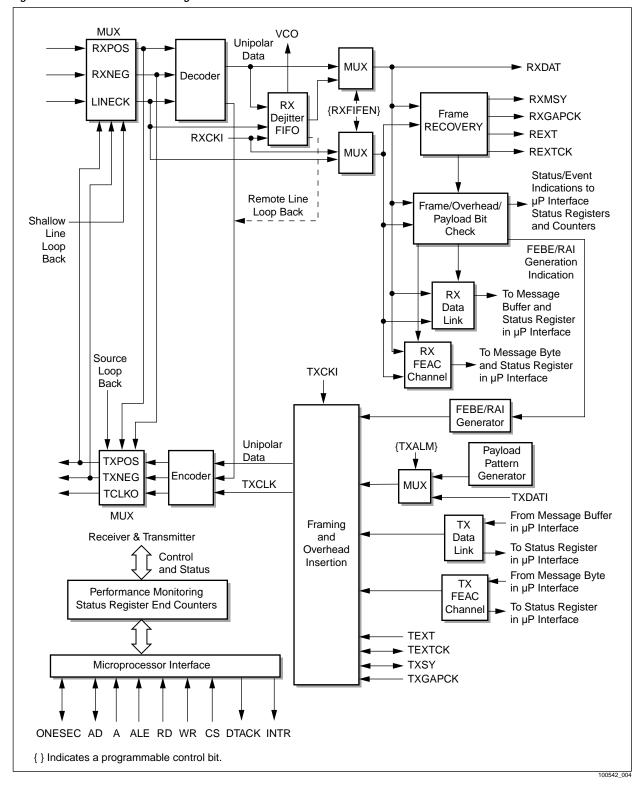

### Functional Block Diagram

### **Distinguishing Features**

- Two, three, four, six, eight independent T3/ E3 framers in one package

- Line coding supported:

- T3-B3ZS, NRZ, AMI

- E3-HDB3, NRZ, AMI

- Framing supported:

- T3-M13, M23, C-bit parity

- E3-G.751, G.832

- Inserts and extracts overhead bits

- Full FEAC and TDL channels support

- Full Performance Monitoring support per T1.231

- Integrated Dejitter FIFO

- Glueless interfaces to the following processors:

- Intel: 8051, 8151, 8031, 8751, 8x251

- Motorola: 68000, 68020, 68030, 68302

- An asynchronous processor interface

- LIU Interfaces:

- Glueless interface to Conexant's DS3/E3 LIU (CX2832/3)

- Option for a definition of LIU's clocks polarity-sampling edge

- Power Supplies and Power Consumption

- I/O 3.3 V, input 5 V-tolerant, core 2.5 V

- Requires 3.3 V and 2.5 V power supplies. Optional 5 V supply required for 5 V input tolerance

- Low power operation (<200 mW per port)

#### Applications

- Digital Cross-Connect Systems

- Digital PCM Switches

- Access Concentrators

- ♦ CSUs

- ATM Switches

- Concentrators

- PBXs

- Routers

- Test Equipment

#### Testing

JTAG boundary scan support

### **Ordering Information**

| Model Numbe | Number of Frames | Package                  | Ambient Temperature Range |

|-------------|------------------|--------------------------|---------------------------|

| CX28342     | 2                | 144 pin ETQFP            | –40 °C to 85 °C           |

| CX28343     | 3                | 144 pin ETQFP            | –40 °C to 85 °C           |

| CX28344     | 4                | 144 pin ETQFP            | –40 °C to 85 °C           |

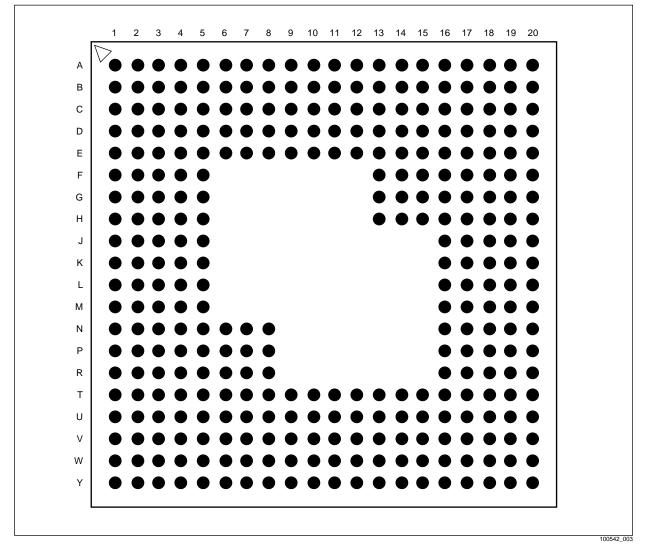

| CX28346     | 6                | 27 x 27 mm 318-ball PBGA | –40 °C to 85 °C           |

| CX28348     | 8                | 27 x 27 mm 318-ball PBGA | –40 °C to 85 °C           |

### **Revision History**

| Revision         | Level       | Date           | Description                                                                                                              |

|------------------|-------------|----------------|--------------------------------------------------------------------------------------------------------------------------|

| A (Doc # 100542) | Advance     | May 2000       | Created                                                                                                                  |

| A *              | _           | September 2001 | Added details on memory mapping for CX28346<br>and CX28348 devices. * Document number<br>changed from 100542 to 500064A. |

| В                | Preliminary | November 2001  | Added jitter attenuator information.                                                                                     |

| С                | Release     | August 2002    | Corrected Jitter attenuation information. Rolled up Errata, document #101317A.                                           |

| А                | Release     | December 2002  | Renumbered document to 28348-DSH-001-A                                                                                   |

| В                | Release     | February 2003  | Revised section 2.2.5.5                                                                                                  |

© 2002, 2003 Mindspeed Technologies<sup>™</sup>, A Conexant Business All Rights Reserved.

Information in this document is provided in connection with Mindspeed Technologies ("Mindspeed") products. These materials are provided by Mindspeed as a service to its customers and may be used for informational purposes only. Mindspeed assumes no responsibility for errors or omissions in these materials. Mindspeed may make changes to specifications and product descriptions at any time, without notice. Mindspeed makes no commitment to update the information and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to its specifications and product descriptions.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Mindspeed's Terms and Conditions of Sale for such products, Mindspeed assumes no liability whatsoever.

THESE MATERIALS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, RELATING TO SALE AND/OR USE OF MINDSPEED PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, CONSEQUENTIAL OR INCIDENTAL DAMAGES, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. MINDSPEED FURTHER DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. MINDSPEED SHALL NOT BE LIABLE FOR ANY SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS, WHICH MAY RESULT FROM THE USE OF THESE MATERIALS.

Mindspeed products are not intended for use in medical, lifesaving or life sustaining applications. Mindspeed customers using or selling Mindspeed products for use in such applications do so at their own risk and agree to fully indemnify Mindspeed for any damages resulting from such improper use or sale.

The following are trademarks of Conexant Systems, Inc.: Mindspeed Technologies<sup>™</sup>, the Mindspeed<sup>™</sup> logo, and "Build It First"<sup>™</sup>. Product names or services listed in this publication are for identification purposes only, and may be trademarks of third parties. Third-party brands and names are the property of their respective owners.

For additional disclaimer information, please consult Mindspeed Technologies Legal Information posted at www.mindspeed.com which is incorporated by reference.

## Contents

| Cont  | ents |                            |                                                                                                                                                                                            | iii                                                                                                                                                                                    |

|-------|------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figu  | res  |                            |                                                                                                                                                                                            | vii                                                                                                                                                                                    |

| Table | 29   |                            |                                                                                                                                                                                            | ix                                                                                                                                                                                     |

|       |      |                            |                                                                                                                                                                                            |                                                                                                                                                                                        |

| 1.0   | Proc | luct Des                   | ription                                                                                                                                                                                    | 1-1                                                                                                                                                                                    |

|       | 1.1  | 1.1.1<br>1.1.2             | DS3 Mode<br>E3 Mode                                                                                                                                                                        | 1-1<br>1-2<br>1-2                                                                                                                                                                      |

|       | 1.2  |                            | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                      | 3/4) 1-3                                                                                                                                                                               |

|       | 1.3  | Pin Desc                   | iptions (CX28346/                                                                                                                                                                          | 8) 1-17                                                                                                                                                                                |

| 2.0   | Fund | ctional D                  | escription                                                                                                                                                                                 |                                                                                                                                                                                        |

|       | 2.1  | Transmit<br>2.1.1<br>2.1.2 | Transmitter         Overhe           2.1.1.1         DS3 M           2.1.1.2         E3–G.7           2.1.1.3         E3–G.8           Alarm Signal Gene           2.1.2.1         Loss of | 2-3         ad Bit Generation.       2-11         ode       2-12         51 Mode       2-15         32 Mode       2-16         ration       2-18         Signal Generation.       2-18 |

|       |      | 2.1.3                      | 2.1.2.3 E3-G.7<br>2.1.2.4 E3-G.8<br>Terminal Data Link                                                                                                                                     | bde       2-19         51 Mode       2-21         32 Mode       2-22         Transmission       2-23         ADD 5       200                                                           |

|       |      |                            | 2.1.3.2         FIFO Co           2.1.3.3         Initial S           2.1.3.4         Sendin                                                                                               | APD Formatting Circuitry2-23ontrol Circuitry2-24etup of Transmit Data Link2-25g Message Using the FIFO—Normal Operation2-26pecial Events2-27                                           |

|       |      | 2.1.4                      | 2.1.4.1 Single                                                                                                                                                                             | smission         2-29           Code-Word Mode         2-30           ive Code-Word Mode         2-30                                                                                  |

|       |      | 2.1.5                      | 2.1.5.1         DS3 M           2.1.5.2         E3-G.7           2.1.5.3         E3-G.8                                                                                                    | Error Insertion       2-31         ode       2-31         51 Mode       2-32         32 Mode       2-33         ding Errors       2-33                                                 |

| 2.2 | Receive  | Operation                                                                                   |

|-----|----------|---------------------------------------------------------------------------------------------|

|     | 2.2.1    | Line-Side Interface                                                                         |

|     | 2.2.2    | System-Side Interface                                                                       |

|     | 2.2.3    | Clock Dejitter FIFO                                                                         |

|     | 2.2.4    | Overhead Bit Recovery                                                                       |

|     |          | 2.2.4.1 Processing of Overhead Bits 2-41                                                    |

|     |          | 2.2.4.2 Internal Processing of Overhead Bits 2-42                                           |

|     | 2.2.5    | Performance Monitoring                                                                      |

|     |          | 2.2.5.1 Bipolar Violation (BPV), Excessive Zeros (EXZ), and Line Code Violation (LCV). 2-45 |

|     |          | 2.2.5.2 Loss of Signal (LOS)                                                                |

|     |          | 2.2.5.3 Framing Bit Error (FBE) 2-45                                                        |

|     |          | 2.2.5.4 Out of Frame (OOF)                                                                  |

|     |          | 2.2.5.5 Severely Errored Frame (SEF) 2-46                                                   |

|     |          | 2.2.5.6 Alarm Indication Signal (AIS) 2-47                                                  |

|     |          | 2.2.5.7 Idle Signal (IDLE)                                                                  |

|     |          | 2.2.5.8 Parity Error (PER) and P-Bit Disagreement (PBD) 2-47                                |

|     |          | 2.2.5.9 Path Parity Error (PPER)                                                            |

|     |          | 2.2.5.10 Remote Alarm/Defect Indication (RAI/RDI), X-bit disagreement (XBD) 2-48            |

|     |          | 2.2.5.11 Far-End Block Error/Remote Error Indication (FEBE/REI) 2-48                        |

|     | 2.2.6    | One-Second Counter Latching                                                                 |

|     | 2.2.7    | Terminal Data Link Reception                                                                |

|     |          | 2.2.7.1 Initial Setup                                                                       |

|     |          | 2.2.7.2 Writing Messages into the FIFO 2-52                                                 |

|     |          | 2.2.7.3 Reading Messages from the FIFO 2-53                                                 |

|     | 2.2.8    | Far-End Alarm and Control Channel Reception                                                 |

|     |          | 2.2.8.1 Writing into the FEAC Stack 2-57                                                    |

|     |          | 2.2.8.2 Reading from the FEAC Stack 2-57                                                    |

| 2.3 | Micropr  | cessor Interface                                                                            |

|     | 2.3.1    | Address/Data Bus                                                                            |

|     | 2.3.2    | Control Signals                                                                             |

|     | 2.3.3    | Interrupt Requests                                                                          |

|     | 2.3.4    | Hardware Reset                                                                              |

|     | 2.3.5    | Software Reset                                                                              |

|     | 2.3.6    | Initialization Guidelines                                                                   |

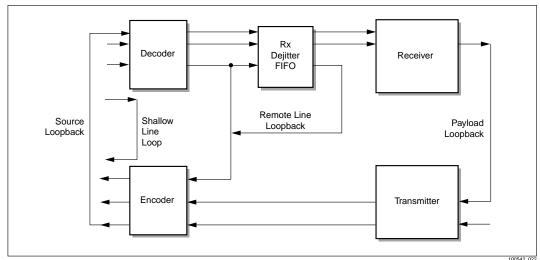

| 2.4 | Loopbac  | xs                                                                                          |

|     | 2.4.1    | Shallow Line Loopback                                                                       |

|     | 2.4.2    | Remote Line Loopback                                                                        |

|     | 2.4.3    | Payload Loopback                                                                            |

|     | 2.4.4    | Source Loopback                                                                             |

| 2.5 | Joint Te | t Access Group (JTAG) Interface                                                             |

|     | 2.5.1    | Instructions 2-65                                                                           |

v

| 3.0 | Reg | isters                                        | 3-1          |

|-----|-----|-----------------------------------------------|--------------|

|     | 3.1 | Register Address Map                          | 3-1          |

|     | 3.2 | Register Address Map                          |              |

|     | 3.3 | Control Registers.                            |              |

|     | 0.0 | General Control Registers                     |              |

|     |     | General1 Control Register (GCR00)             | 3-7          |

|     |     | General2 Control Register (GCR01)             | 3-8          |

|     |     | Channel Control Registers                     | . 3-9        |

|     |     | Mode Control Register (CR00i)                 | 3-9          |

|     |     | Counter Interrupt Control Register (CR01i)    | 3-10         |

|     |     | Dual-Edge Interrupt Control Registers         | 3-11         |

|     |     |                                               | 3-11         |

|     |     | Alarm End Interrupt Control Register (CR03i)  | 3-12         |

|     | 3.4 |                                               | 3-13         |

|     |     |                                               | 3-13         |

|     |     |                                               | 3-14         |

|     |     |                                               | 3-15         |

|     |     |                                               | 3-16<br>3-17 |

|     |     | Transmit Overhead Insertion Control Registers |              |

|     |     |                                               | 3-19         |

|     |     |                                               | 3-20         |

|     |     |                                               | 3-22         |

|     |     |                                               | 3-23         |

|     |     |                                               | 3-24         |

|     |     |                                               | 3-24         |

|     |     |                                               | 3-25         |

|     |     |                                               | 3-25         |

|     |     |                                               | 3-26         |

|     |     |                                               | 3-26         |

|     |     | Error Insertion Control Registers             | 3-26<br>3-27 |

|     |     |                                               | 3-27         |

|     | 3.5 | Status Registers                              |              |

|     | 5.0 |                                               |              |

|     |     | General Status Registers                      | 3-29         |

|     |     | <b>e</b>                                      | 3-30         |

|     |     | •                                             | 3-31         |

|     |     | <b>v</b>                                      | 3-31         |

|     |     |                                               | 3-32         |

|     |     |                                               | 3-33         |

|     |     | Dual-Edge Interrupt Status Registers          | 3-34         |

|     |     |                                               | 3-34         |

|     |     | Alarm End Interrupt Status Register (SR04i)   | 3-35         |

|     |     | E3-832 MA Fields Registers                    |              |

|     |     |                                               | 3-36         |

|     |     |                                               | 3-36         |

|     |     |                                               | 3-37         |

|     |     | <b>e e e e e e e e e e</b>                    | 3-38<br>3-39 |

|     |     |                                               | 3-39<br>3-41 |

|     |     |                                               | 3-41         |

|     |     |                                               | 1.1.1        |

|     | 3.6  | Counters                                                                           | 12 |

|-----|------|------------------------------------------------------------------------------------|----|

|     |      | DS3 Parity Disagreement Counter (Ctr01i) 3-4                                       |    |

|     |      | DS3 X Disagreement Counter (Ctr02i) 3-4<br>DS3/E3 Frame Error Counter (Ctr03i) 3-4 |    |

|     |      | DS3 Path Parity Error Counter (CtrO4i) 3-4                                         |    |

|     |      | DS3/E3 FEBE Event Counter (Ctr05i) 3-4                                             |    |

|     |      | DS3/E3 Excessive Zeros Counter (Ctr06i) 3-4                                        |    |

|     |      | DS3/E3 LCV Counter (Ctr07i) 3-4                                                    |    |

|     | 3.7  | General Counters                                                                   |    |

| 4.0 | Elec | rical and Mechanical Specifications 4-                                             | 1  |

|     | 4.1  | Environmental Conditions                                                           | -1 |

|     |      | 4.1.1 Power Requirements and Temperature Range 4-                                  | -1 |

|     |      | 4.1.1.1 Recommended Operating Conditions                                           | -1 |

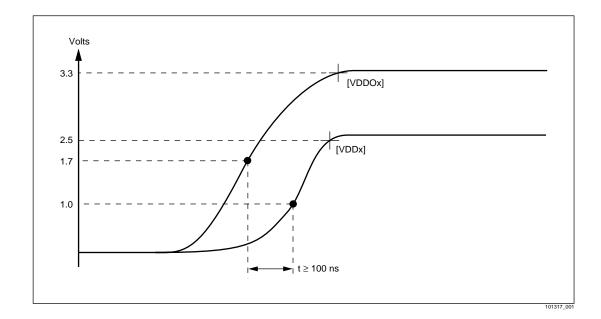

|     |      | 4.1.1.2 Power Ramp Sequence of VDDx and VDDOx                                      | ·2 |

|     |      | 4.1.2 Electrical Characteristics 4-                                                | -2 |

|     |      | 4.1.2.1 DC Characteristics                                                         | -2 |

|     | 4.2  | AC Characteristics                                                                 | -4 |

|     |      | 4.2.1 Input Clock Timing                                                           | -4 |

|     |      | 4.2.2 Signal Timing and Clock Output Timings 4-                                    | -5 |

|     | 4.3  | Microprocessor Interface Timing 4-                                                 | -8 |

|     |      | 4.3.1 Additional Restrictions                                                      | 2  |

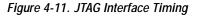

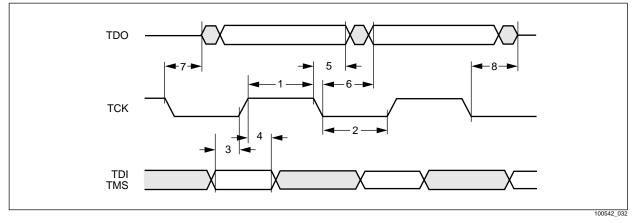

|     | 4.4  | JTAG Interface Timing                                                              | 3  |

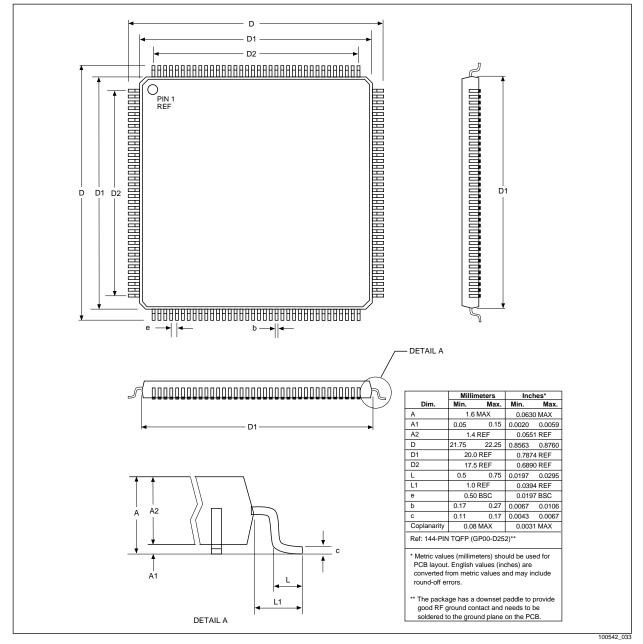

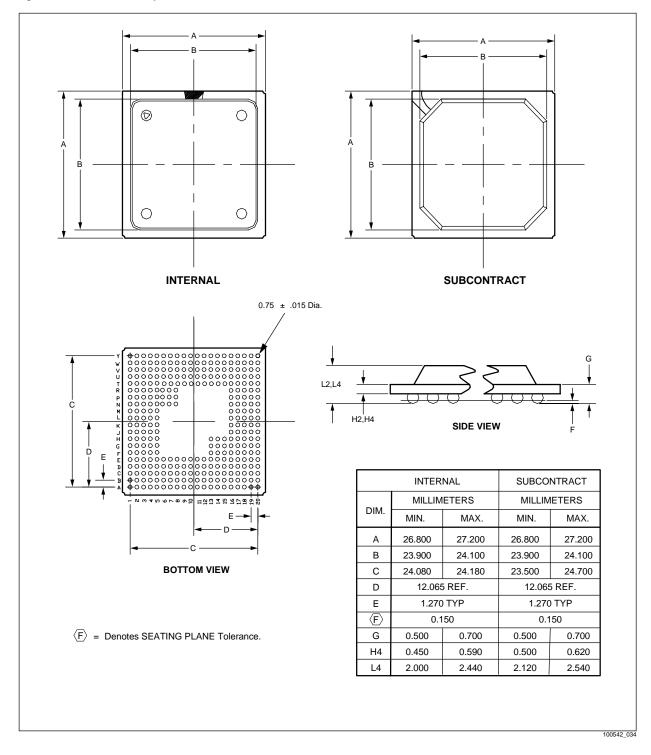

|     | 4.5  | Mechanical Specifications 4-1                                                      | 4  |

|     |      | 4.5.1 Package Types                                                                | 4  |

|     | 4.6  | Applicable Standards 4-1                                                           | 6  |

| Α.  | Deji | er Circuit Analysis                                                                | 1  |

| B.  | Fran | e Structure Summary                                                                | 1  |

| C.  | B3Z  | /HDB3 Encoding                                                                     | 1  |

| D.  | Acro | ıyms                                                                               | 1  |

## Figures

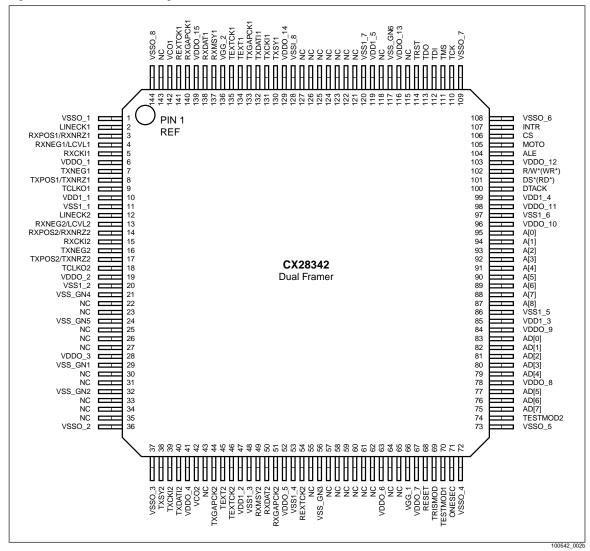

| Figure 1-1.  | CX28342 Pin Assignments                                                                               |

|--------------|-------------------------------------------------------------------------------------------------------|

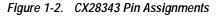

| Figure 1-2.  | CX28343 Pin Assignments 1-4                                                                           |

| Figure 1-3.  | CX28344 Pin Assignments 1-5                                                                           |

| Figure 1-4.  | CX28346/8 Pin Assignments (Top View) 1-17                                                             |

| Figure 2-1.  | Functional Block Diagram of a Channel 2-2                                                             |

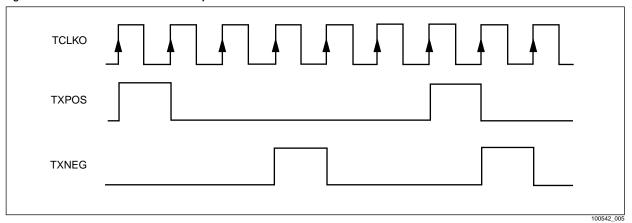

| Figure 2-2.  | Transmitter Line Side Outputs                                                                         |

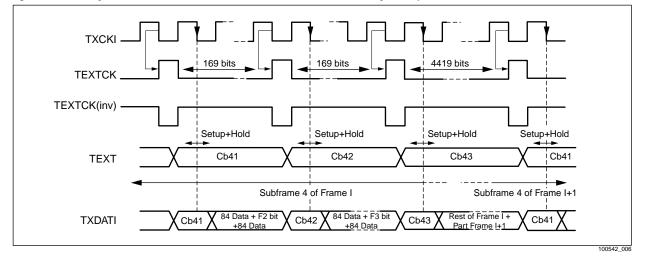

| Figure 2-3.  | Tx System Side External Overhead Insertion (DS3 FEBE-only example) 2-4                                |

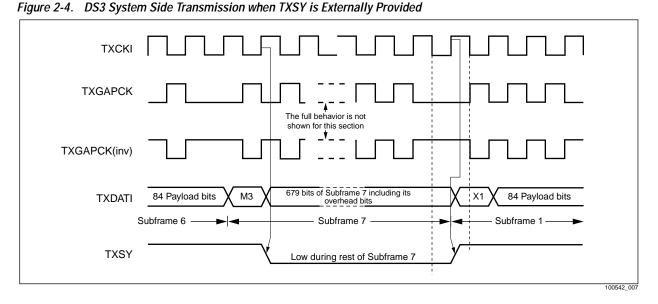

| Figure 2-4.  | DS3 System Side Transmission when TXSY is Externally Provided                                         |

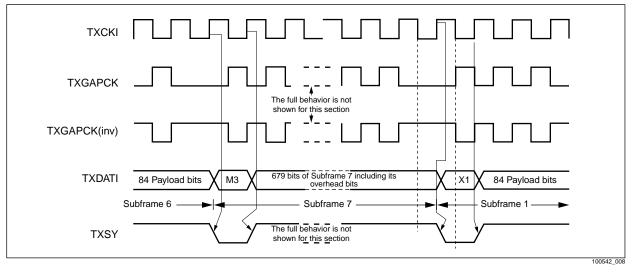

| Figure 2-5.  | DS3 System Side Transmission Unit when TXSY is Used as an Overhead Indication Bit 2-6                 |

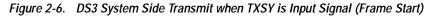

| Figure 2-6.  | DS3 System Side Transmit when TXSY is Input Signal (Frame Start)                                      |

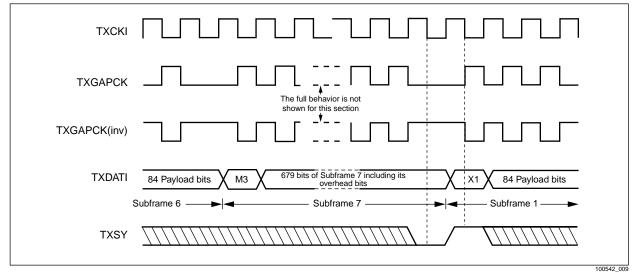

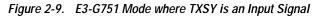

| Figure 2-7.  | E3-G.751 Transmit Mode when TXSY is Frame Start Sync Output Signal 2-8                                |

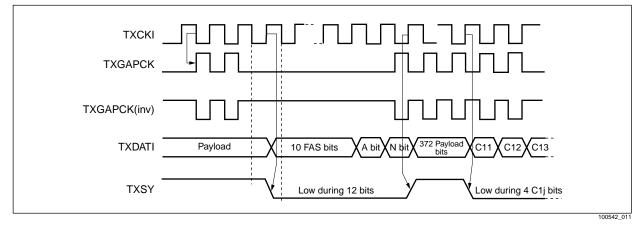

| Figure 2-8.  | E3-G.751 Transmit Mode where TXSY is an Overhead Indicator Output Signal 2-8                          |

| Figure 2-9.  | E3-G751 Mode where TXSY is an Input Signal 2-9                                                        |

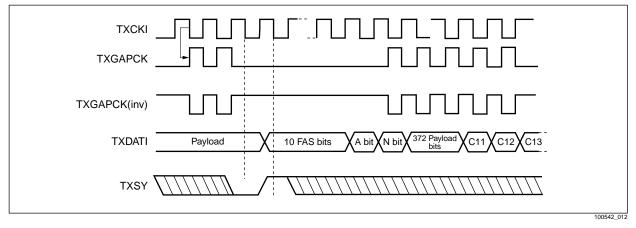

| Figure 2-10. | E3-G.832 Mode where TXSY is an Output Signal Indicating Frame Start Sync 2-9                          |

| Figure 2-11. | TXSY Transmitter System Side Signal (E3-G.832)                                                        |

| Figure 2-12. | TXSY Transmitter System Side Signal (E3-G.832)                                                        |

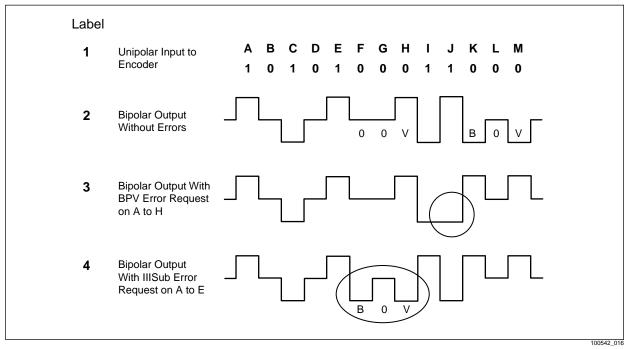

| Figure 2-13. | Line Coding Error Insertion                                                                           |

| Figure 2-14. | Receiver Line Side Inputs                                                                             |

| Figure 2-15. | Receiver System Side Outputs [RXGAPCK]                                                                |

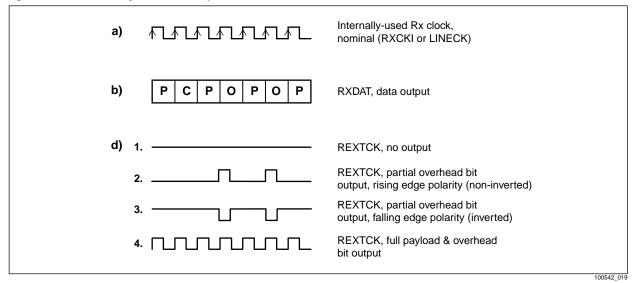

| Figure 2-16. | Receiver System Side Outputs [REXTCK]                                                                 |

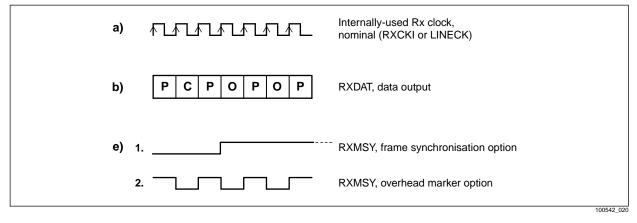

| Figure 2-17. | Receiver System Side Outputs 2-39                                                                     |

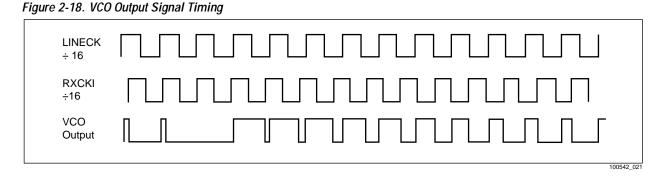

| Figure 2-18. | VCO Output Signal Timing 2-40                                                                         |

| Figure 2-19. | Loopback Types                                                                                        |

| Figure 4-1.  | Power Ramp Sequence of VDDx and VDDOx                                                                 |

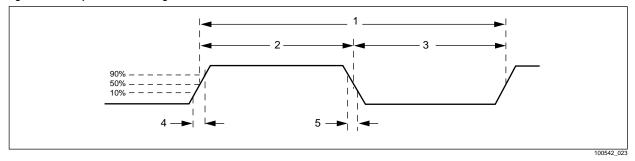

| Figure 4-2.  | Input Clock Timing                                                                                    |

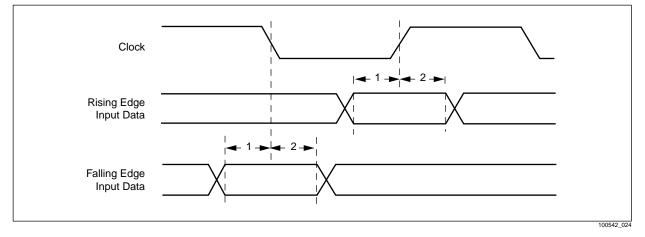

| Figure 4-3.  | Line Side Receiver Input Data Setup/Hold Timing (1 = tsu [setup time]; 2 = thld [hold time]) .<br>4-5 |

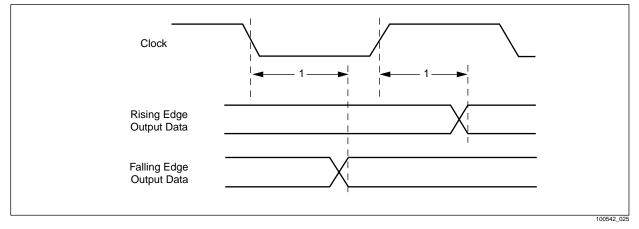

| Figure 4-4.  | Line Side Transmitter Output Data Timing (1 = tpd [propogation delay]) 4-5                            |

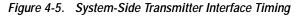

| Figure 4-5.  | System-Side Transmitter Interface Timing 4-6                                                          |

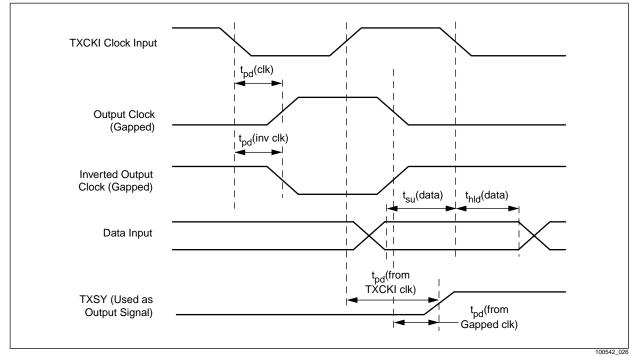

| Figure 4-6.  | System-Side Receiver Interface Timing 4-6                                                             |

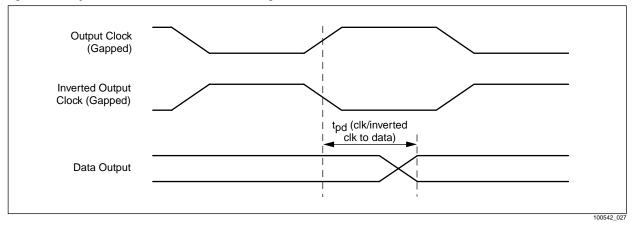

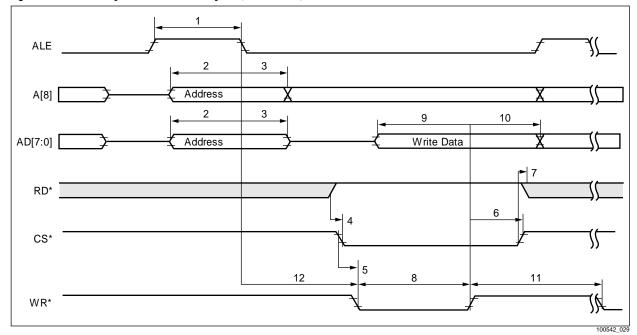

| Figure 4-7.  | Intel Asynchronous Read Cycle (MOTO* = 1) 4-8                                                         |

| Figure 4-8.  | Intel Asynchronous Write Cycle (MOTO* = 1) 4-9                                                        |

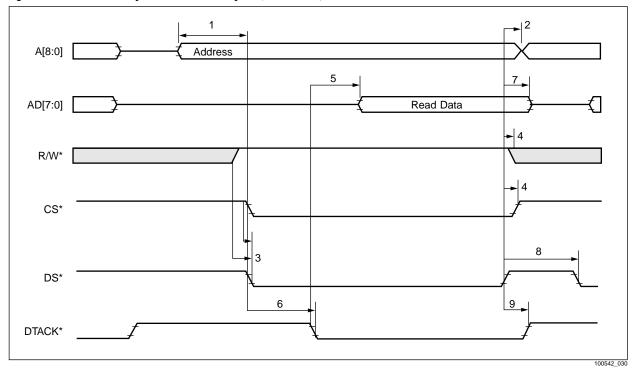

| Figure 4-9.  | Motorola Asynchronous Read Cycle (MOTO* = 0)                                                          |

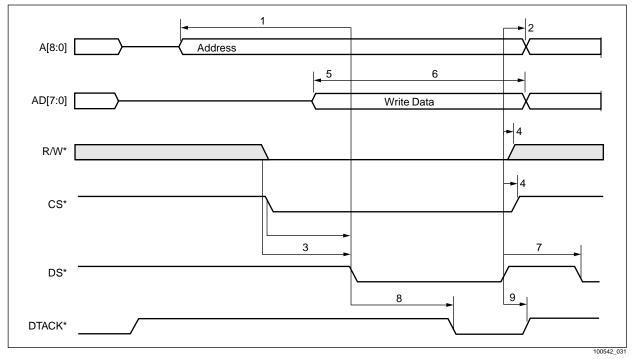

| Figure 4-10. | Motorola Asynchronous Write Cycle (MOTO* = 0)                                                         |

| Figure 4-11. | JTAG Interface Timing                                                                                 |

| Figure 4-12. | Mechanical Specification for 144-pin ETQFP 4-14                                                       |

| Figure 4-13. | Mechanical Specification for 27x27 mm 318-Ball PBGA | 4-15 |

|--------------|-----------------------------------------------------|------|

| Figure A-1.  | CS2834x Dejitter Circuitry                          | A-1  |

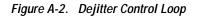

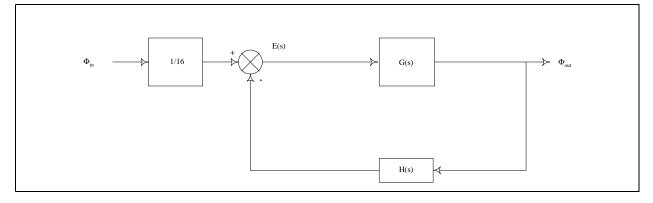

| Figure A-2.  | Dejitter Control Loop                               | A-2  |

| Figure A-3.  | Components of System Gain                           | A-3  |

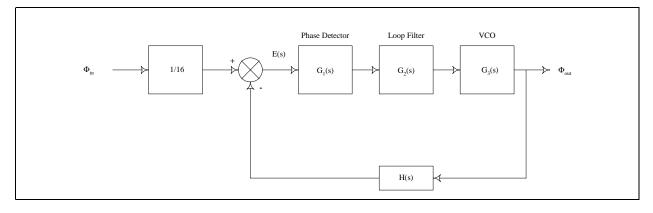

| Figure A-4.  | Bode Diagram of the System                          | A-8  |

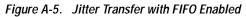

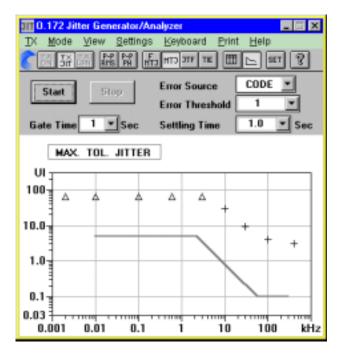

| Figure A-5.  | Jitter Transfer with FIFO Enabled                   | A-9  |

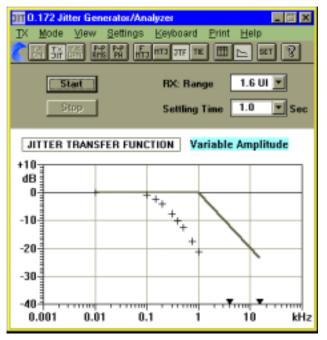

| Figure A-6.  | Jitter Tolerance with FIFO Enabled                  | A-9  |

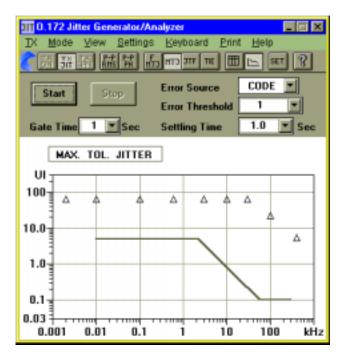

| Figure A-7.  | Jitter Transfer with FIFO Disabled                  | A-10 |

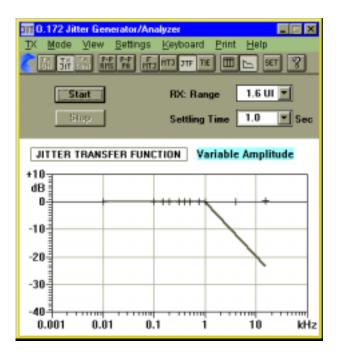

| Figure A-8.  | Jitter Tolerance with FIFO Disabled                 | A-10 |

## Tables

| Table 1-1.  | Pin Type Definitions                                                |

|-------------|---------------------------------------------------------------------|

| Table 1-2.  | CX28342/3/4 Pins                                                    |

| Table 1-3.  | Transmitter Section Line Side                                       |

| Table 1-4.  | Transmitter Section System Side                                     |

| Table 1-5.  | Receiver Section Line Side 1-11                                     |

| Table 1-6.  | Receiver Section System Side 1-13                                   |

| Table 1-7.  | Microprocessor Interface                                            |

| Table 1-8.  | JTAG Interface                                                      |

| Table 1-9.  | Framer Distribution                                                 |

| Table 1-10. | Pin Distribution                                                    |

| Table 1-11. | CX28346 and CX28348 General Pins                                    |

| Table 1-12. | Transmitter Section Line Side                                       |

| Table 1-13. | Transmitter Section System Side 1-23                                |

| Table 1-14. | Receiver Section Line Side 1-27                                     |

| Table 1-15. | Reciever Section System Side 1-30                                   |

| Table 1-16. | Microprocessor Interface                                            |

| Table 1-17. | JTAG Interface                                                      |

| Table 2-1.  | Overhead Sourcing Methods 2-11                                      |

| Table 2-2.  | Overhead Options                                                    |

| Table 2-3.  | DS3 Mode Alarm Signal Setting 2-19                                  |

| Table 2-4.  | Setting the Error Insertion1 Control Register in DS3 Mode 2-31      |

| Table 2-5.  | Setting the Error Insertion1 Control Register in E3-G.751 Mode      |

| Table 2-6.  | Setting the Error Insertion1 Control Register in E3-G.832 Mode 2-33 |

| Table 2-7.  | Line-side Interface Modes 2-35                                      |

| Table 2-8.  | Status Byte Description                                             |

| Table 2-9.  | JTAG Instruction Codes 2-65                                         |

| Table 3-1.  | General Registers                                                   |

| Table 3-2.  | Channel (i) Registers 3-5                                           |

| Table 3-3.  | DS3-C Bit Parity/E3-G.751 Mode Field Interpretation 3-19            |

| Table 3-4.  | E3-G.832 Mode Field Interpretation                                  |

| Table 4-1.  | Absolute Maximum Ratings 4-1                                        |

| Table 4-2.  | Recommended Operating Conditions                                    |

| Table 4-3.  | DC Characteristics                                                  |

| Table 4-4.  | Input Clock Timing                                                  |

| Table 4-5.  | Output Signal Timing 4-7                                            |

| Table 4-6.  | Input Signal Timing                                                 |

| Table 4-9.  | Motorola Asynchronous Read Cycle (MOTO* = 0)            | 1-11 |

|-------------|---------------------------------------------------------|------|

| Table 4-10. | Motorola Asynchronous Write Cycle (MOTO* = 0)           | 1-12 |

| Table 4-11. | Test and Diagonstic Interface Timing Requirements       | 1-13 |

| Table 4-12. | Test and Diagnostic Interface Switching Characteristics | 1-13 |

| Table B-1.  | Overhead Bits in DS3 Mode                               | B-1  |

| Table B-2.  | Overhead Bits in E3G751 Mode                            | B-2  |

| Table B-3.  | Overhead Bytes in E3G832                                | B-2  |

|             |                                                         |      |

|             |                                                         |      |

|             |                                                         |      |

|             |                                                         |      |

Intel Asynchronous Read Cycle (MOTO\* = 1) ..... 4-9

Intel Asynchronous Write Cycle (MOTO\* = 1) ..... 4-10

Table 4-7.

Table 4-8.

## **1.0 Product Description**

### 1.1 Overview

The CX28342/3/4/6/8 device includes two, three, four, six, and eight identical framers that perform the following functions:

- Signal encoding and decoding

- Frame synchronization and recovery

- Alarm detection and generation

- Far End Alarm Control (FEAC) processing

- Data link processing

- Error and event counting

- Signal and frame generation

Each framer in the CX28342/CX28343/CX28344/CX28346/CX28348 device can be configured individually and is capable of operating at 44.736 Mbps in DS3 mode and 34.368 Mbps in E3 mode. Each framer is composed of a transmitter block and a receiver block. In addition, the CX28342/3/4/6/8 framer includes a microprocessor interface.

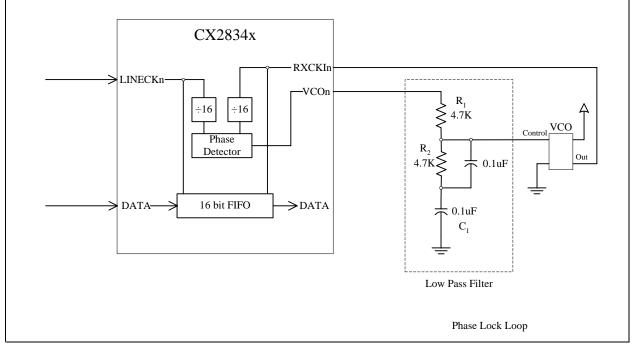

Data into the receiver can be in B3ZS/HDB3, AMI, or NRZ format. The B3ZS/HDB3 or AMI data is decoded and the bipolar input is converted to unipolar. The data can then be applied to a First In First Out (FIFO) buffer to reduce jitter on the incoming data. The FIFO buffer provides a Voltage Controlled Oscillator (VCO) control signal to an external clock recovery circuit. A dejittered clock (RXCKI) from the VCO can then be used to read data from the FIFO buffer going to the remaining receiver circuitry.

Each of the receiver blocks provides framing recovery for the M13/M23 DS3, C-bit Parity DS3, E3-G.751, and E3-G.832 formatted signals. The data bits are extracted from the received frame and transferred serially to the system. The transmitter can process serial data from an external pin. In addition, the transmitter can generate AIS/ RAI/RDI and IDLE code. The transmitter also transmits the Link Access Direct (LAPD) data link data in HDLC format. The HDLC data is transmitted through a 128-byte FIFO buffer. The microprocessor can use the FIFO status for data transfer. The transmitter can transmit the FEAC channel data in several modes.

The microprocessor interface supports the Intel and Motorola microprocessors. The microprocessor is responsible for configuration, control, and monitoring of the framer. The framers have various event detectors, status indicators, and counters, which are readable by the microprocessor. The microprocessor interface includes (depending on the device) one (CX28342/3/4) or two (CX28346/8) interrupt pins that combine several sources of individually masked interrupts (i.e. the start and end of events, OOF, IDLE, AIS, and RAI/RDI). Status indicators that are available to the microprocessor through status registers are start of a Severely Errored Framing Event (SEF), Yellow Alarm (RAI, RDI), Alarm Indication Signal (AIS), Idle, Out of Frame (OOF), and Loss of Signal (LOS).

### 1.1.1 DS3 Mode

In DS3 mode, each of the receiver blocks provides framing recovery for DS3 M13/ M23 and DS3 C-bit parity formatted signals. The receive signals can be in B3ZS, AMI, or NRZ format. The following events are detected and counted:

- P-bits

- CP-bits (DS3 C-bit parity only)

- FEBE (DS3 C-bit parity only)

- X-bit disagreement

- P-bit disagreement

- Framing Error

- Line Code Violation (LCV)

- Excessive Zeros (EXZ) in rail mode only

The C-bits in DS3 M13/M23 can be provided with the data or through an external pin. Overhead bits can be selectively provided through an external pin or internally generated. The transmitter can generate idle code and other alarm indication codes (AIS and RAI/RDI). In addition, the alarms generated in C-bit parity mode include FEBE and CP for performance monitoring.

Overhead bit can be selected for insertion with the data stream in this mode.

### 1.1.2 E3 Mode

In E3 mode, each receive block provides framing recovery for E3 G.751 and E3 G.832 formatted signals. The receive signals can be in HDB3, AMI, or NRZ format. The following events are detected and counted:

- BIP (G.832 only)

- REI (G.832)

- Framing Error

- Line Code Violation (LCV)

- Excessive Zeros (EXZ) in rail mode only

The Justification Control bits (Cj) in E3 G.751 can be provided with the data or through an external pin. Overhead bits can be selectively provided through an external pin or internally generated. The transmitter can also generate AIS and RAI/RDI signals. In addition, REI and BIP alarm bits in E3 G.832 format are generated for performance monitoring.

Overhead bit can be selected for insertion with the data stream in this mode. The detailed operation in each mode is described in Chapter 2.

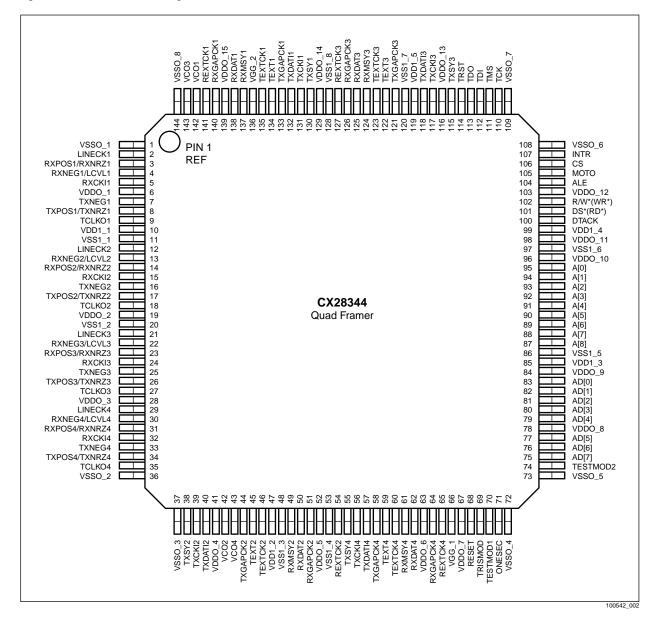

### 1.2 Pin Descriptions (CX28342/3/4)

Pin descriptions for the CX28342, CX28343, and CX28344 devices are covered in the following paragraphs.

Figure 1-1 illustrates pin assignments for CX28342 dual framer. Figure 1-2 illustrates pin assignments for CX28343 triple framer. Figure 1-4 illustrates pin assignments for CX28344 quad framer.

*NOTE:* All input pins are 5 V-tolerant. See Table 1-1 for pin type definitions. See Tables 1-2 through 1-8 for pin descriptions.

Figure 1-1. CX28342 Pin Assignments

Figure 1-3. CX28344 Pin Assignments

| Symbol                                                               | Name and Function                                                |  |  |

|----------------------------------------------------------------------|------------------------------------------------------------------|--|--|

| 1                                                                    | Input pin, CMOS levels, no internal termination                  |  |  |

| IPU                                                                  | Input pin, CMOS levels, 75K internal pullup                      |  |  |

| IPD                                                                  | Input pin, CMOS levels, 75K internal pulldown                    |  |  |

| 0/Z                                                                  | Three-state-capable CMOS output pin                              |  |  |

| 10                                                                   | CMOS bidirectional pin                                           |  |  |

| IOPD                                                                 | CMOS programmable pin, 75K internal pulldown                     |  |  |

| IOZPU Three-state capable CMOS programmable pin, 75K internal pullup |                                                                  |  |  |

| IOZPD                                                                | Three-state capable CMOS programmable pin, 75K internal pulldown |  |  |

| ODO Open Drain Output, no internal pullup                            |                                                                  |  |  |

| PC                                                                   | Digital power pin for core circuits                              |  |  |

| PI                                                                   | Digital power pin for I/O pads                                   |  |  |

| GC                                                                   | Digital ground pin for core circuits                             |  |  |

| GI                                                                   | Digital ground pin for I/O pads                                  |  |  |

Table 1-1. Pin Type Definitions

Table 1-2. CX28342/3/4 Pins

| Pin Label   | CX28342<br>Pin #                                                             | CX28343<br>Pin #                                                             | CX28344 Pin #                                                          | Signal Name                            | I/O   | Definition                                                                                                                                                                                                                                                                                                            |

|-------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET*      | 68                                                                           | 68                                                                           | 68                                                                     | General reset                          | I     | Resets all counters and registers to their default values (active low) <sup>(1)</sup> .                                                                                                                                                                                                                               |

| VGG[1:2]    | 66, 136                                                                      | 66, 136                                                                      | 66, 136                                                                | Voltage<br>supply                      | I     | These pins must be connected to 5 V if 5 V input tolerance is required; if not, it must be connected to 3.3 V.                                                                                                                                                                                                        |

| VDD1[1:5]   | 10, 47, 85,<br>99, 119                                                       | 10, 47, 85,<br>99, 119                                                       | 10, 47, 85, 99,<br>119                                                 | Core Supply<br>Voltage                 | PC    | The core is provided with 2.5 V using<br>these pins.<br>Note: Refer to Section 4, Power Ramp<br>Sequence of VDDx and VDDOx.                                                                                                                                                                                           |

| VDDO[1:15]  | 6, 19, 28,<br>41, 52, 63,<br>67, 78, 84,<br>96, 98,<br>103, 116,<br>129, 139 | 6, 19, 28,<br>41, 52, 63,<br>67, 78, 84,<br>96, 98,<br>103, 116,<br>129, 139 | 6, 19, 28, 41, 52,<br>63, 67, 78, 84,<br>96, 98, 103, 116,<br>129, 139 | Output<br>Drivers<br>Supply<br>Voltage | ΡI    | These pins must be connected to a 3.3 V<br>power supply.<br>Note: Refer to Section 4, Power Ramp<br>Sequence of VDDx and VDDOx.                                                                                                                                                                                       |

| VSSO[1:8]   | 1, 36, 37,<br>72, 73,<br>108, 109,<br>144                                    | 1, 36, 37,<br>72, 73,<br>108, 109,<br>144                                    | 1, 36, 37, 72, 73,<br>108, 109, 144                                    | Ground                                 | GI    | These are 3.3 V ground pins.                                                                                                                                                                                                                                                                                          |

| TRISMOD     | 69                                                                           | 69                                                                           | 69                                                                     | Three-state<br>Mode                    | IPD   | Setting this pin high forces all the output/<br>inputs on the device to drive High Z,<br>regardless of the state of the internal state<br>machines, and the frame processing<br>taking place at the same time. Setting this<br>pin low enable the output/inputs to<br>normal driving state.                           |

| VSS1[1:8]   | 11, 20, 48,<br>53, 86, 97,<br>120, 128                                       | 11, 20, 48,<br>53, 86, 97,<br>120, 128                                       | 11, 20, 48, 53,<br>86, 97, 120, 128                                    | Ground                                 | GC    | These are 2.5 V ground pins.                                                                                                                                                                                                                                                                                          |

| VSS_GN[1:6] | 21, 24, 29,<br>32, 56,<br>117                                                | 29, 32, 56                                                                   |                                                                        | Ground                                 |       | Must be connected to ground.                                                                                                                                                                                                                                                                                          |

| TESTMOD1    | 70                                                                           | 70                                                                           | 70                                                                     | Test Mode 1                            | IPD   | For Conexant use only. Must be connected to ground.                                                                                                                                                                                                                                                                   |

| TESTMOD2    | 74                                                                           | 74                                                                           | 74                                                                     | Test Mode 2                            | IPD   | For Conexant use only. Must be connected to ground.                                                                                                                                                                                                                                                                   |

| ONESEC      | 71                                                                           | 71                                                                           | 71                                                                     | One-Second<br>Timer                    | IOZPD | Controls or marks one-second interval<br>used for counter latching. When input,<br>the timer is aligned to ONESEC rising<br>edge. When output, rising edge indicates<br>start of each one-second interval. When<br>output, derived from TXCKI1 clock of the<br>first framer. The ONESEC pulse length is<br>16 clocks. |

<sup>10</sup> During reset, TXCKI and LINECK (and RXCKI, if Rx dejitter FIFO buffer is to be used) clocks should be supplied for normal operation.

| Pin Label         | CX28342 Pin # | CX28343 Pin # | CX28344 Pin # | Signal Name                                     | I/O | Definition                                                                                                                 |

|-------------------|---------------|---------------|---------------|-------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------|

| TCLK01            | 9             | 9             | 9             | Framer 1<br>Transmit Clock<br>Out               | O/Z | Used to clock out the TXPOS/<br>TXNRZ and TXNEG outputs.<br>Data is clocked out on the                                     |

| TCLKO2            | 18            | 18            | 18            | Framer 2<br>Transmit Clock<br>Out               | O/Z | rising or on the falling edge of<br>TCLKO according to settings<br>of bit LTxCkRis at the<br>Feature2(I) Control register. |

| TCLK03            | -             | 27            | 27            | Framer 3<br>Transmit Clock<br>Out               | O/Z |                                                                                                                            |

| TCLKO4            | -             |               | 35            | Framer 4<br>Transmit Clock<br>Out               | O/Z |                                                                                                                            |

| TXPOS1/<br>TXNRZ1 | 8             | 8             | 8             | Framers 1<br>Transmit<br>Positive/NRZ<br>Output | 0/Z | In rail mode or AMI mode,<br>B3ZS/HDB3/AMI encoder<br>generates the positive output.<br>In unipolar mode, generates        |

| TXPOS2/<br>TXNRZ2 | 17            | 17            | 17            | Framers 2<br>Transmit<br>Positive/NRZ<br>Output | O/Z | the NRZ output.                                                                                                            |

| TXPOS3/<br>TXNRZ3 |               | 26            | 26            | Framers 3<br>Transmit<br>Positive/NRZ<br>Output | O/Z |                                                                                                                            |

| TXPOS4/<br>TXNRZ4 | _             | _             | 34            | Framers 4<br>Transmit<br>Positive/NRZ<br>Output | O/Z |                                                                                                                            |

| TXNEG1            | 7             | 7             | 7             | Framers 1<br>Transmit<br>Negative Output        | 0/Z | In rail mode or AMI mode,<br>B3ZS/HDB3/AMI encoder<br>generates the negative output.                                       |

| TXNEG2            | 16            | 16            | 16            | Framers 2<br>Transmit<br>Negative Output        | 0/Z | In unipolar mode, not used.                                                                                                |

| TXNEG3            | _             | 25            | 25            | Framers 3<br>Transmit<br>Negative Output        | O/Z |                                                                                                                            |

| TXNEG4            | _             | _             | 33            | Framers 4<br>Transmit<br>Negative Output        | 0/Z |                                                                                                                            |

### Table 1-3. Transmitter Section Line Side

| Pin Label | CX28342 Pin # | CX28343 Pin # | CX28344 Pin # | Signal Name                                | I/O   | Definition                                                                                                        |

|-----------|---------------|---------------|---------------|--------------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------|

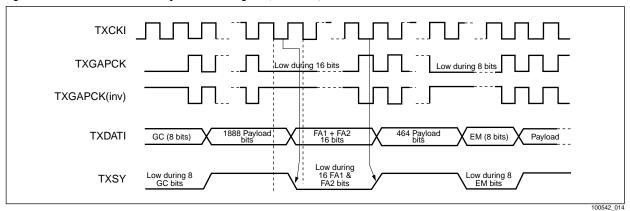

| TXDATI1   | 132           | 132           | 132           | Framers 1<br>Transmit Serial<br>Data Input | IPD   | TXDATI is serial data input to<br>framer transmitter. The serial<br>data is sampled on the falling                |

| TXDATI2   | 40            | 40            | 40            | Framers 2<br>Transmit Serial<br>Data Input | IPD   | edge of TXCKI input clock.                                                                                        |

| TXDATI3   | _             | 118           | 118           | Framers 3<br>Transmit Serial<br>Data Input | IPD   |                                                                                                                   |

| TXDATI4   | _             | _             | 57            | Framers 4<br>Transmit Serial<br>Data Input | IPD   |                                                                                                                   |

| TXSY1     | 130           | 130           | 130           | Framers 1<br>Transmit Sync                 | IOZPD | Framer transmit frame synchronization indicator. The                                                              |

| TXSY2     | 38            | 38            | 38            | Framers 2<br>Transmit Sync                 | IOZPD | sync signal can be<br>programmed to be generated<br>internally (the pin used as                                   |

| TXSY3     | —             | 115           | 115           | Framers 3<br>Transmit Sync                 | IOZPD | output) or supplied from<br>external circuit (the pin used                                                        |

| TXSY4     | —             |               | 55            | Framers 4<br>Transmit Sync                 | IOZPD | as input). After reset, it has a high-Z value.                                                                    |

| TXCKI1    | 131           | 131           | 131           | Framers 1<br>Transmit Clock<br>In          | I     | Used to clock in serial data<br>TXDATI in serial mode. The<br>sync and data inputs are                            |

| TXCKI2    | 39            | 39            | 39            | Framers 2<br>Transmit Clock<br>In          | I     | sampled on the falling edge.<br>DS3 Mode Clock = 44.736<br>MHz E3-G.751/G.832 Mode<br>Clock = 34.368 MHz          |

| ТХСКІЗ    | _             | 117           | 117           | Framers 3<br>Transmit Clock<br>In          | I     |                                                                                                                   |

| TXCKI4    | _             | _             | 56            | Framers 4<br>Transmit Clock<br>In          | I     |                                                                                                                   |

| TXGAPCK1  | 133           | 133           | 133           | Framers 1<br>Transmit<br>Gapped Clock      | O/Z   | A gapped clock is derived<br>from the falling edge of TXCKI<br>clock. It is gapped during                         |

| TXGAPCK2  | 44            | 44            | 44            | Framers 2<br>Transmit<br>Gapped Clock      | O/Z   | Overhead bits that are not<br>selected to be inserted with<br>payload on TXDATI. Its<br>polarity is programmable. |

| TXGAPCK3  | _             | 121           | 121           | Framers 3<br>Transmit<br>Gapped Clock      | O/Z   | , , , , , , , , , , , , , , , , , , ,                                                                             |

| TXGAPCK4  |               |               | 58            | Framers 4<br>Transmit<br>Gapped Clock      | O/Z   |                                                                                                                   |

Table 1-4. Transmitter Section System Side (1 of 2)

| Pin Label | CX28342 Pin # | CX28343 Pin # | CX28344 Pin # | Signal Name                                                | I/O | Definition                                                                                                                                            |

|-----------|---------------|---------------|---------------|------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| TEXT1     | 134           | 134           | 134           | Framers 1<br>Transmit<br>External<br>Overhead Bit In       | IPD | Transmit external Overhead<br>bits input. The Overhead bit<br>groups to be inserted through<br>this pin are programmable.                             |

| TEXT2     | 45            | 45            | 45            | Framers 2<br>Transmit<br>External<br>Overhead Bit In       | IPD | The options for each mode of operation are specified in Section 2.1.1                                                                                 |

| TEXT3     | _             | 122           | 122           | Framers 3<br>Transmit<br>External<br>Overhead Bit In       | IPD |                                                                                                                                                       |

| TEXT4     | _             | _             | 59            | Framers 4<br>Transmit<br>External<br>Overhead Bit In       | IPD |                                                                                                                                                       |

| TEXTCK1   | 135           | 135           | 135           | Framers 1<br>Transmit<br>External<br>Overhead Bit<br>Clock | O/Z | Used to indicate to the system<br>when to insert a new<br>Overhead bit on TEXT pin.<br>This output has a clock pulse<br>for each position of Overhead |

| TEXTCK2   | 46            | 46            | 46            | Framers 2<br>Transmit<br>External<br>Overhead Bit<br>Clock | O/Z | bits (for the specific DS3/E3<br>mode) that were chosen to be<br>inserted through TEXT pin. Its<br>behavior is specified in<br>Section 2.1.1.         |

| TEXTCK3   | _             | 123           | 123           | Framers 3<br>Transmit<br>External<br>Overhead Bit<br>Clock | O/Z |                                                                                                                                                       |

| TEXTCK4   | _             | _             | 60            | Framers 4<br>Transmit<br>External<br>Overhead Bit<br>Clock | O/Z |                                                                                                                                                       |

Table 1-4. Transmitter Section System Side (2 of 2)

| Pin Label         | CX28342 Pin # | CX28343 Pin # | CX28344 Pin # | Signal Name                                                      | I/O | Definition                                                                                                                                                           |

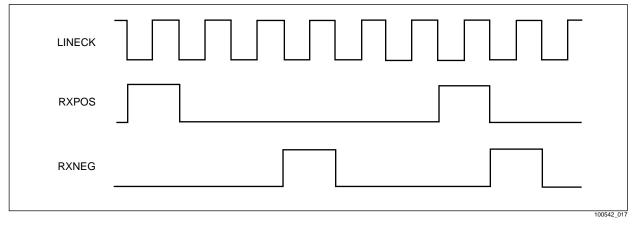

|-------------------|---------------|---------------|---------------|------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LINECK1           | 2             | 2             | 2             | Framers 1<br>Receive Line<br>Clock In                            | I   | Line clock input should be<br>connected to a 44.736 MHz<br>source in DS3 mode or to a                                                                                |

| LINECK2           | 12            | 12            | 12            | Framers 2<br>Receive Line<br>Clock In                            | I   | 34.368 MHz source in E3<br>mode, derived from incoming<br>receive data.                                                                                              |

| LINECK3           | _             | 21            | 21            | Framers 3<br>Receive Line<br>Clock In                            | I   |                                                                                                                                                                      |

| LINECK4           | -             | _             | 29            | Framers 4<br>Receive Line<br>Clock In                            | I   |                                                                                                                                                                      |

| RXPOS1/<br>RXNRZ1 | 3             | 3             | 3             | Framers 1<br>Receive<br>Positive/NRZ<br>Input                    | IPD | In rail mode and in AMI mode,<br>it is the positive data input. In<br>unipolar mode it is the NRZ<br>data input. Sampled on the                                      |

| RXPOS2/<br>RXNRZ2 | 14            | 14            | 14            | Framers 2<br>Receive<br>Positive/NRZ<br>Input                    | IPD | rising/falling (programmable)<br>edge of the receiver input<br>clock (LINECK).                                                                                       |

| RXPOS3/<br>RXNRZ3 | _             | 23            | 23            | Framers 3<br>Receive<br>Positive/NRZ<br>Input                    | IPD |                                                                                                                                                                      |

| RXPOS4/<br>RXNRZ4 | _             | _             | 31            | Framers 4<br>Receive<br>Positive/NRZ<br>Input                    | IPD |                                                                                                                                                                      |

| RXNEG1/<br>LCVI1  | 4             | 4             | 4             | Framers 1<br>Receive<br>Negative/Line<br>Code Violation<br>Input | IPD | In rail mode and in AMI mode,<br>it is the negative data input. In<br>unipolar mode, it is the line<br>code violation input for LCV<br>counting (if unused tie low). |

| RXNEG2/<br>LCVI2  | 13            | 13            | 13            | Framers 2<br>Receive<br>Negative/Line<br>Code Violation<br>Input | IPD | Sampled on the rising/falling<br>(programmable) edge of the<br>receiver input clock (LINECK).                                                                        |

| RXNEG3/<br>LCVI3  | _             | 22            | 22            | Framers 3<br>Receive<br>Negative/Line<br>Code Violation<br>Input | IPD |                                                                                                                                                                      |

| RXNEG4/<br>LCVI4  | _             | _             | 30            | Framers 4<br>Receive<br>Negative/Line<br>Code Violation<br>Input | IPD |                                                                                                                                                                      |

Table 1-5. Receiver Section Line Side (1 of 2)

| Pin Label | CX28342 Pin # | CX28343 Pin # | CX28344 Pin # | Signal Name                                    | I/O | Definition                                                                                                         |

|-----------|---------------|---------------|---------------|------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------|

| RXCKI1    | 5             | 5             | 5             | Framers 1<br>Receive<br>Dejittered Clock<br>In | I   | Used to read the received data<br>out of the internal clock dejitter<br>FIFO buffer (if unused, tie to<br>ground). |

| RXCKI2    | 15            | 15            | 15            | Framers 2<br>Receive<br>Dejittered Clock<br>In | Ι   |                                                                                                                    |

| RXCKI3    | _             | 24            | 24            | Framers 3<br>Receive<br>Dejittered Clock<br>In | Ι   |                                                                                                                    |

| RXCKI4    | -             | _             | 32            | Framers 4<br>Receive<br>Dejittered Clock<br>In | Ι   |                                                                                                                    |

| VCO1      | 142           | 142           | 142           | Framers 1<br>Phase Detector<br>Output          | O/Z | Used as the phase detector for<br>the clock recovery circuit that<br>generates dejittered clock,                   |

| VCO2      | 42            | 42            | 42            | Framers 1<br>Phase Detector<br>Output          | O/Z | RXCKI. Valid only when framer dejitter FIFO buffer is enabled.                                                     |

| VCO3      | _             | 143           | 143           | Framers 1<br>Phase Detector<br>Output          | O/Z |                                                                                                                    |

| VCO4      | —             |               | 43            | Framers 1<br>Phase Detector<br>Output          | O/Z |                                                                                                                    |

Table 1-5. Receiver Section Line Side (2 of 2)

| Pin Label | CX28342 Pin # | CX28343 Pin # | CX28344 Pin # | Signal Name                                     | I/O | Definition                                                                                                           |

|-----------|---------------|---------------|---------------|-------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------|

| RXMSY1    | 137           | 137           | 137           | Framers 1<br>Receive Sync                       | 0/Z | The frame synchronization output of framer recovered                                                                 |

| RXMSY2    | 49            | 49            | 49            | Framers 2<br>Receive Sync                       | O/Z | from the incoming serial data stream.                                                                                |

| RXMSY3    | _             | 124           | 124           | Framers 3<br>Receive Sync                       | O/Z |                                                                                                                      |

| RXMSY4    | —             |               | 61            | Framers 4<br>Receive Sync                       | O/Z |                                                                                                                      |

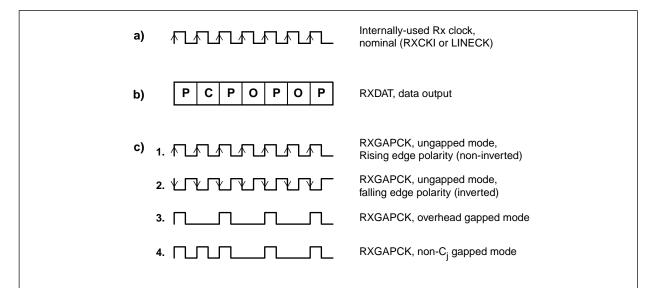

| RXGAPCK1  | 140           | 140           | 140           | Framers 1<br>Receive Gapped<br>Clock            | 0/Z | It is a gapped clock signal<br>output that is used to indicate<br>RXDAT serial data output.                          |

| RXGAPCK2  | 51            | 51            | 51            | Framers 2<br>Receive Gapped<br>Clock            | 0/Z | RXGAPCK clock polarity and<br>behavior are programmable<br>and have several options (see<br>Section 2.2).            |

| RXGAPCK3  | -             | 126           | 126           | Framers 3<br>Receive Gapped<br>Clock            | O/Z |                                                                                                                      |

| RXGAPCK4  | -             |               | 64            | Framers 4<br>Receive Gapped<br>Clock            | O/Z |                                                                                                                      |

| REXTCK1   | 141           | 141           | 141           | Framer 1<br>Receive<br>Overhead Clock<br>Output | O/Z | Used to indicate chosen<br>Overhead bits that output on<br>RXDAT. This output has a<br>clock pulse for each position |

| REXTCK2   | 54            | 54            | 54            | Framer 2<br>Receive<br>Overhead Clock<br>Output | O/Z | of the chosen group of<br>Overhead bits for the specific<br>DS3/E3 mode. Its polarity is<br>programmable.            |

| REXTCK3   | _             | 127           | 127           | Framer 3<br>Receive<br>Overhead Clock<br>Output | 0/Z |                                                                                                                      |

| REXTCK4   | —             | —             | 65            | Framer 4<br>Receive<br>Overhead Clock<br>Output | O/Z |                                                                                                                      |

Table 1-6. Receiver Section System Side (1 of 2)

| Pin Label | CX28342 Pin # | CX28343 Pin # | CX28344 Pin # | Signal Name                                | I/O | Definition                                                                                                                   |

|-----------|---------------|---------------|---------------|--------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------|

| RXDAT1    | 138           | 138           | 138           | Framers 1<br>Receive Serial<br>Data Output | O/Z | This pin is the serial data bit<br>stream of framer. Data is<br>clocked out on the rising edge<br>of receive internal clock. |

| RXDAT2    | 50            | 50            | 50            | Framers 2<br>Receive Serial<br>Data Output | O/Z |                                                                                                                              |

| RXDAT3    | _             | 125           | 125           | Framers 3<br>Receive Serial<br>Data Output | O/Z |                                                                                                                              |

| RXDAT4    | _             | _             | 62            | Framers 4<br>Receive Serial<br>Data Output | O/Z |                                                                                                                              |

### Table 1-6. Receiver Section System Side (2 of 2)

| Table 1-7. Microprocessor Inte | erface |

|--------------------------------|--------|

|--------------------------------|--------|

| Pin Label | CX28342 Pin # | CX28343 Pin # | CX28344 Pin # | Signal Name                                | I/O  | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------|---------------|---------------|---------------|--------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOTO*     | 105           | 105           | 105           | Motorola Bus<br>Mode                       | I    | Selects Intel- or Motorola-style<br>microprocessor interface.<br>DS*, R/W*, A[8:0], and<br>AD[7:0] functions are affected.<br>0 = Motorola; AD[7:0] is data,<br>A[8:0] is address, DS* is data<br>strobe, and R/W* indicates<br>read (high) or write (low) data<br>direction.<br>1 = Intel; AD[7:0] is<br>multiplexed address/data,<br>A[7:0] is ignored, A[8] is<br>address, DS* is read strobe<br>(RD*), and R/W* is write<br>strobe (WR*). |

| A[8:0]    | 87–95         | 87–95         | 87–95         | Address Bus                                | IPD  | Address used to identify a<br>register for subsequent read/<br>write data transfer cycle. In<br>Motorola bus mode, all nine<br>address bits (A[8:0]) are valid.<br>In Intel bus mode, only the<br>upper bit (A[8]) is used.                                                                                                                                                                                                                   |

| AD[7:0]   | 75–77, 79-83  | 75–77, 79-83  | 75–77, 79-83  | Data Bus or<br>Address/Data                | IOPD | Multiplexed address/data<br>(Intel) or data only (Motorola).<br>Refer to MOTO* definition.                                                                                                                                                                                                                                                                                                                                                    |

| ALE       | 104           | 104           | 104           | Address Strobe                             | I    | For Intel bus mode only, ALE<br>falling edge asynchronously<br>latches address from A[8:0]<br>(Motorola) or A[8]+AD[7:0]<br>(Intel) to identify one register<br>for subsequent read/write data<br>transfer cycle.                                                                                                                                                                                                                             |

| CS*       | 106           | 106           | 106           | Chip Select                                | I    | Active low enables read/write<br>decoder. Active high ends<br>current read or write cycle and<br>places data bus output in high<br>impedance.                                                                                                                                                                                                                                                                                                 |

| DS*(RD*)  | 101           | 101           | 101           | Data Strobe or<br>Read Strobe              | I    | Active low read data strobe<br>(RD*) for MOTO* = 1, or data<br>strobe (DS*) for MOTO* = 0.                                                                                                                                                                                                                                                                                                                                                    |

| R/W*(WR*) | 102           | 102           | 102           | Read/Write<br>Direction or<br>Write Strobe | I    | Active low write data strobe<br>(WR*) for MOTO* = 1, or data<br>select (R/W*) for MOTO* = 0.                                                                                                                                                                                                                                                                                                                                                  |

| INTR*     | 107           | 107           | 107           | Interrupt<br>Request                       | O/Z  | Open drain active low output<br>signifies one or more pending<br>interrupt requests. INTR goes<br>to high impedance state.                                                                                                                                                                                                                                                                                                                    |