| Others are tested in the same manner. | ا<br>ت      | same        | man             | ner.           |                    |                   |                            |                |                  |                |                           |                  |                  |               |             |       |            |             |            |            |                                              |           |                 |              |              |                 |

|---------------------------------------|-------------|-------------|-----------------|----------------|--------------------|-------------------|----------------------------|----------------|------------------|----------------|---------------------------|------------------|------------------|---------------|-------------|-------|------------|-------------|------------|------------|----------------------------------------------|-----------|-----------------|--------------|--------------|-----------------|

|                                       | MC431       | 16/4016     |                 |                |                    | MC43<br>MC43      | MC4317/4017<br>MC4319/4019 | 117            |                  |                |                           |                  |                  |               |             |       |            |             |            |            |                                              |           |                 |              |              |                 |

| 8                                     | MC431       | MC4318/4018 | ہ<br>ا~ _       |                | *                  | 13 Clock          | k 1 00                     | <u></u>        |                  |                |                           |                  |                  |               |             |       |            |             |            |            |                                              |           |                 |              |              |                 |

| 0                                     | 0 6 Clock   | 5           | ő               |                | ۱Ÿ                 |                   | κ 2<br>01                  |                |                  |                |                           |                  |                  |               |             |       |            | Ĩ           | ST CURRE   | NT/VOLT    | TEST CURRENT/VOLTAGE VALUES                  | s         |                 |              |              |                 |

| 0 0                                   |             | 02          | ٩               |                | , _Y               | 3 5<br>=          | α2                         | <u>_</u>       |                  |                | e                         | T_               |                  |               | A m         |       |            |             |            |            | Valts                                        |           |                 |              |              |                 |

| , 0                                   | 5<br>7<br>7 |             | -               |                | 6                  | 14 02             | 03                         |                |                  |                | Ten                       | Temperature      | i loli a         |               | _           | но    | ç          | ۷IL         | H>         | ннι        | VILT                                         | VIHT      | ν<br>CC         | -            | VCCH         |                 |

| o                                     | 3           | ,           | 11,0            |                | Ŷ                  | 8                 | Bus                        | 2              |                  |                | -                         | -55°C            |                  | $\rightarrow$ |             | -1.6  | -          | 0.4         | 2.4        | 5. L       | 0.8                                          | 2.0       | 50              | 45           | 5 2          |                 |

| 0                                     |             | r           | ן<br>נו         |                | Υ.'                |                   |                            |                | ž                | MC4316-4019    | 66                        | +125°C           | C 12.8           | 13.8          | 0<br>0<br>0 | 9<br> | <b>₽</b> , | 0.4         | 2.4        | 6 5<br>5   | 0.8                                          | 2.0       | 20.5            | 4.5          | 5.5          |                 |

| 0                                     | EW 02       | Bus         |                 |                | ĥ                  |                   |                            |                |                  |                | _                         | 000              |                  | + +           |             | -1.6  |            | 0.4         | 2.5        | 5.5        | 0.8                                          | 2'0       | 5.0             | 4 75         | 5.25         |                 |

|                                       |             |             |                 |                |                    |                   |                            |                | Ж                | MC4016-4019    | 019                       | +25°C            | C 12.8<br>C 12.8 | 13.8          | 9.6<br>9.6  | -1.6  | ę .        | 0.4         | 2.5        | 5.5        | 0.8<br>0.8                                   | 2.0       | 5.0             | 4 75<br>4 75 | 5 25<br>5 25 |                 |

|                                       |             |             | WC              | 1316 -4        | MC4316 4319 Test L | Limits            | +                          | MC40           | MC4016-4019 Test | 9 Test Li      | Limits                    | -                |                  |               |             |       | TEST       | CURRENT     | /VOLTAGI   | APPLIED    | CURRENT/VOLTAGE APPLIED TO PINS LISTED BELOW | STED BEI  | MO              |              |              |                 |

| Char acteristic                       | Symbol      | Under       | Min Max Min Max | × Min +2       | -                  | +125°C<br>Min Max | Aux Min q                  | n Max          | Min +25          | Max            | +75-C<br>Min Max          | Š                | 1011             | 1 10L2        | 1013        | но    | <u>ب</u>   | ۲IL         | H^         | ннιν       | VILT                                         | VIHT      | ν <sub>CC</sub> | VCCL         | VCCH         | Gnd             |

| Input                                 |             | +           |                 |                | _                  | -                 |                            |                |                  |                |                           |                  | -                |               |             | L     | t          | ,           | :          |            |                                              |           | -               |              | 4            | r               |

| Forward Current                       | <u>[</u>    | ~ ~         | -16             | 9 0            | -1.6               |                   | 3.5                        | -16            |                  | 9.1-           | 1.6                       | 6 mAdc           | ب                |               |             |       | ,          | n n         | <u>5</u> 4 | 11         | 1 :                                          | 1         | 1.1             |              | <u>e</u> –   | 3,8<br>8,12     |

|                                       |             | n 4         | ġŦ              |                | -1.6               | ( <b>`</b> 1      |                            | 77             |                  | -1.6           | 7                         | v 9              |                  |               |             |       | ,          | া ধা        | · m        | I          | ı                                            | ÷         | 1               | :            | _            |                 |

|                                       |             | ഹ           |                 | ہ<br>بو        | -1.6               | 1                 | 1.6                        | 7 °            |                  | -1.6           |                           | o r              | _                |               |             |       | ·          |             | 01         | 1 1        |                                              |           | 1 1             | : 1          |              | ~ ~             |

|                                       |             | o 0         | γiφ             | <br>           | - 6.4              | ; ¥               |                            | ှမှ            |                  | -6.4           | γφ                        | V 4              |                  | 1             | I           | 1     |            |             | 2,5,11,14  | 11         |                                              |           |                 | 1            |              | m               |

|                                       |             | 2           | ; ;             |                | -1.6               |                   | 1.6                        | -16            |                  | -1.6           | , <del>,</del>            | 9                |                  |               |             |       |            |             | 10         | I          |                                              |           |                 | !            |              |                 |

|                                       |             | 14          |                 | 9              | - 1.6              | '                 | 16                         | -1.6           |                  | -16            | T                         |                  |                  |               |             | •     |            |             | 0          | ,          |                                              | 1         | 1               | , ;          | -            | 1               |

|                                       | 1112        | ~ ~         | - i<br>- i      | 4 0            | 4.1.               |                   | 1.4<br>2 C                 | 4 - C          |                  | -1.4<br>8.0    |                           | 4 mAdc           | Ŷ                |               |             |       |            |             | <u>0</u> 4 | 11         |                                              |           | 1               | <u>9</u> -   |              | ె ఐం            |

|                                       |             | n 4         | ÷÷              | . <del>.</del> | 4.1.               | - 14<br>          | 4                          | 4.1-           |                  | -14            | 17                        | 4                |                  | -             |             |       |            |             | m          | ı          |                                              |           |                 |              |              | ω,              |

|                                       |             | <b>ئ</b> م  | - 1.4           | 4 0            | -1.4<br>-2.8       |                   | -14                        | -14            |                  | -14            | -1.4                      | 4 00             |                  |               |             |       |            | υ<br>υ<br>υ | 0          | 11         |                                              |           |                 |              |              | 8, 8)<br>8, 8)  |

|                                       |             | 9           | 1<br>1<br>1     |                | 5.6                | 7                 | 5.6                        | -5.6           |                  | -56            | ыў •                      | 9,               |                  |               |             |       |            | 2:          | 2,5,11,14  | ł          |                                              |           | 1 1             |              |              | -m -            |

|                                       |             | 14          | <del>; ;</del>  | 4 4            | <br>               |                   | 1 4                        | 1 1            |                  | 4              | <del>.</del> <del>.</del> | *                | ;                |               |             |       |            | 4           | 20         |            |                                              |           |                 | -            | ĺ            | -               |

| Leakage Current                       | Ŧ           | 2           | 40              |                | <b>6</b> 8         |                   | 40                         | <del>8</del> 8 |                  | 40             | 4 2                       | D µAdc           | U                |               |             |       |            |             | ۲<br>د     | . 1 - 1    | ; ,                                          |           |                 | ,            | <u>9</u> –   | 8,10<br>4,8     |

|                                       |             | n 4         | 4 4             | -              | 6                  | . 4               | 6 Q                        | 6 6            |                  | 8 <b>9</b>     | 0 <del>4</del>            |                  |                  |               |             |       |            |             | ) <b>T</b> | I          |                                              |           | ;               |              |              | Ξ,              |

|                                       |             | с ч         | 40              |                | <b>6</b> 8         |                   | <b>6</b> 6                 | 48             |                  | 6 8<br>8       | 4 %                       | 0.0              |                  |               |             | 1     |            |             | م م        | <b>)</b> I |                                              |           | ; 1             |              |              | ≓.∞<br>∞        |

|                                       |             | , <u>2</u>  | <u>1</u> 9      | 1              | 160                |                   | 160                        | 160            | •                | 160            | 91                        | , 0              |                  | _             |             |       |            | :           | 0          | I          |                                              |           | 1               | •            |              | 2,5,8           |

|                                       |             | 1 1         | 40              |                | <b>4</b> 4         |                   | 0 4 0                      | -<br>6 6       |                  | <del>4</del> 4 | 4<br>0<br>1<br>0          |                  |                  |               |             |       |            |             | 1          | 1 1        |                                              | I         | - 1             | : 1          | -            | ໝ່              |

|                                       | 3           | ~           | 1.0             | 1.0            | +                  | 0.1               | -                          | 0              | 1.0              | 1              | 0.1                       | mAdc             | 2                |               | -           |       | t          |             |            | 2          |                                              |           | ,               | ,<br>        | 16           | α)<br>α         |

|                                       | <u> </u>    | (1)         |                 |                | ,                  |                   |                            |                | _                |                |                           |                  |                  | '             |             |       |            | . 1         |            | с <b>ч</b> |                                              |           | · ·             | 1 '          |              | 4<br>8,8<br>8,8 |

|                                       |             | t -0        |                 | _              |                    |                   | ;                          |                |                  |                |                           |                  |                  |               | _           |       |            |             |            | G          |                                              |           |                 | ·            |              | ຜ່              |

|                                       |             | φĘ          |                 |                | :                  |                   |                            | :              |                  |                |                           |                  |                  |               |             | 1     |            |             |            | ¢ ₽        | 1                                            |           | - 1             | 1 :          |              | а<br>2.5.8.1    |

|                                       |             | 2 = 3       | *               |                |                    |                   | -                          | -              |                  |                | -                         | -                | 1                |               |             |       |            |             |            | = 2        |                                              |           |                 | 1 :          |              | 8,10            |

| Clamp Voltage                         | رب<br>۲     | 2           | ·   1           | • •            | . 1                |                   |                            |                | . !              | 10             |                           | - <del>1</del>   | !<br>            |               |             |       | 2          |             | 1          | 1          | 1                                            | 1         | +-'             | 9            | ,            | 80              |

|                                       | 2           |             | ╀               | ╉              | 2                  | +                 | ╉                          | +              | 1                | t              | ╀                         | $\left  \right $ | +                | ļ             | ſ           | Ì     | t          |             |            |            |                                              |           | +-              |              |              |                 |

| Output Voltage                        | Nor         |             | 0.4             | 4 4            | 04                 |                   | 0.4                        | 0.4            |                  | 4.0            | 0.4                       |                  |                  | . ~           | 1.5         |       |            | ,           |            | н I        | 2.3.5.11.14                                  |           |                 | 31           | 16           | ∞ ⊣             |

|                                       |             | 12          |                 |                | 0.5                | 5                 | 0.5                        | 0.5            |                  |                | _                         | - 5              | ,                | 1             | 12          |       | :          |             | ı          | ,          | m                                            | - t       | 4               | 16           | 1            |                 |

|                                       | HON         | -           | 2.4 -           | 2.4            |                    | 2.4               | - 2                        | s              | 2.5              |                | 2.5                       | Vdc              | 0                |               | -           | 1     |            |             |            | 1          | e                                            | 2,5,11,14 |                 | 9            | •            | 8               |

| Short-Circuit Current                 | so          | - 3         | -20 -65         | 5 -20          | -65                | - 20              | -65 -2<br>3.8 -1           | -20 -65        | -20              | - 65<br>- 3.8  | -20 -65                   | 5 mAdc<br>8 mAdc | ب<br>م           |               | • •         | × 1   |            | ñ           | 2,5,11,14  | 11         | I                                            |           | 16              | 1 1          | 1 1          | 8,13<br>8,13    |

| Dama Damana                           | ļ           | +           |                 |                |                    |                   | +-                         |                | +-               | -              |                           |                  |                  | ļ             |             |       | t          |             |            |            |                                              |           | +               |              |              |                 |

| (Total Device)                        | _           | ų           |                 |                | 33                 |                   |                            |                |                  |                |                           | mAdc             | ا<br>            |               | 1           | 1     |            | ,           | ,          | ı          | ,                                            |           | 36              | 1            | 1            |                 |

| LOWE SUPPLY URBIN VIEW                | 5           | 2           |                 |                | 3                  |                   |                            |                |                  | ;              | _                         |                  |                  |               |             |       | -          |             |            |            |                                              |           |                 |              |              |                 |

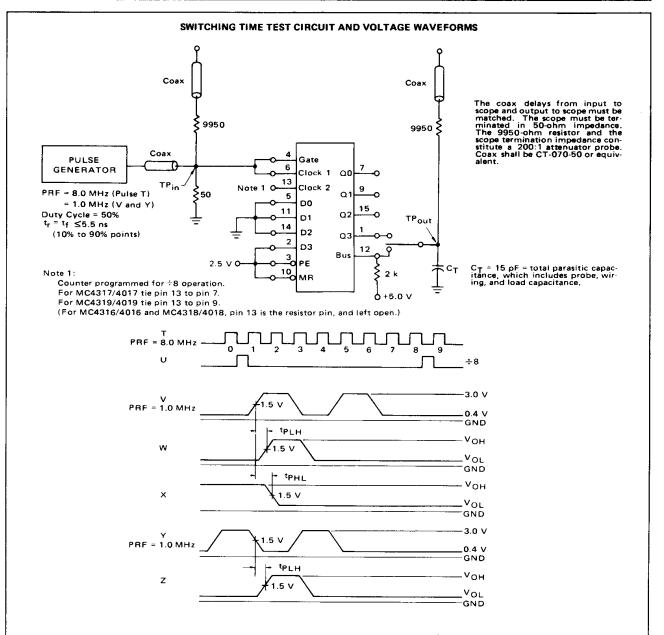

# SWITCHING TIME TEST PROCEDURES (T<sub>A</sub> = $25^{\circ}$ C) (Letters shown in test columns refer to waveforms.)

|                                                                                  |                  |       |       | INPUT        |             | OUTF   | TUT   |     |          |          |

|----------------------------------------------------------------------------------|------------------|-------|-------|--------------|-------------|--------|-------|-----|----------|----------|

|                                                                                  |                  | Clock | Gate  | D0, D1, D2   | D3,PE, MR   | Bus    | Q3    | 1   | LIMITS   | 3        |

| TEST                                                                             | SYMBOL           | Pin 6 | Pin 4 | Pins 5,11,14 | Pins 2,3,10 | Pin 12 | Pin 1 | Min | Max      | Unit     |

| Toggle Frequency<br>(Check before measuring<br>propagation delay.)               | ftog             | т     | т     | Gnd          | 2.5 V       | _      | U     | 8.0 | _        | мна      |

| Propagation Delay<br>Clock to Bus                                                | t₽LH             | v     | v     | Gnd          | 2.5 V       | w      | -     | -   | 65       | ns       |

| Propagation Delay<br>Gate to Q3                                                  | <sup>t</sup> ₽⊾н | Y     | Y     | Gnd          | 2.5 V       | -      | z     | -   | 35       | ns       |

| Propagation Delay<br>Clock 1 to Q3<br>MC4316, 17/4016, 17<br>MC4318, 19/4018, 19 | <sup>t</sup> РНL | v     | v     | Gnd          | 2.5 V       |        | ×     |     | 45<br>78 | ns<br>ns |

#### **OPERATING CHARACTERISTICS**

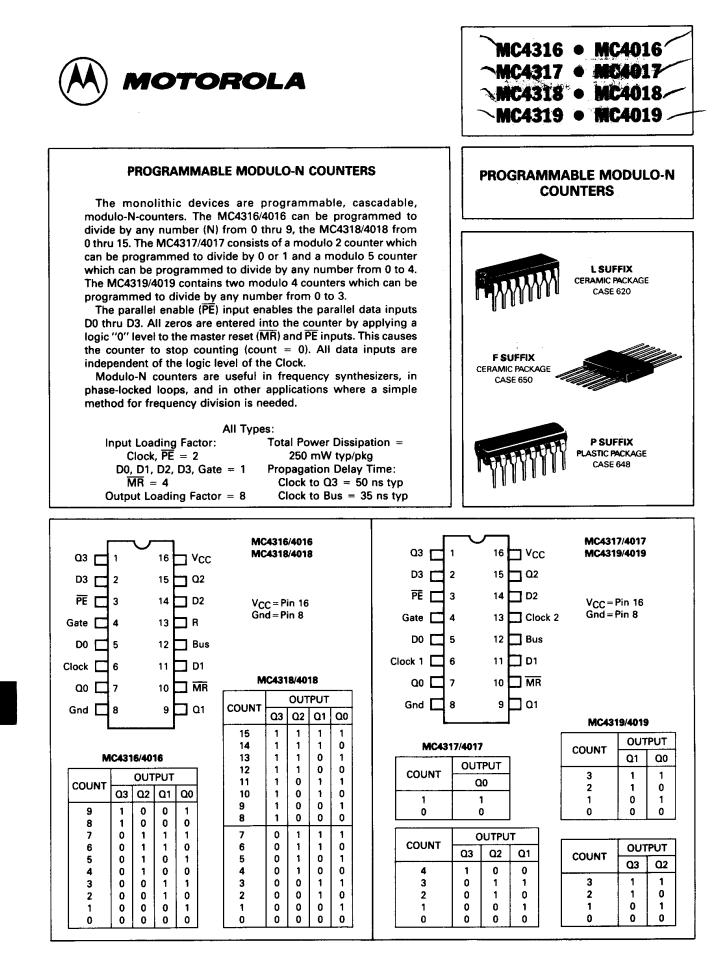

MC4316/4016, MC4318/4018

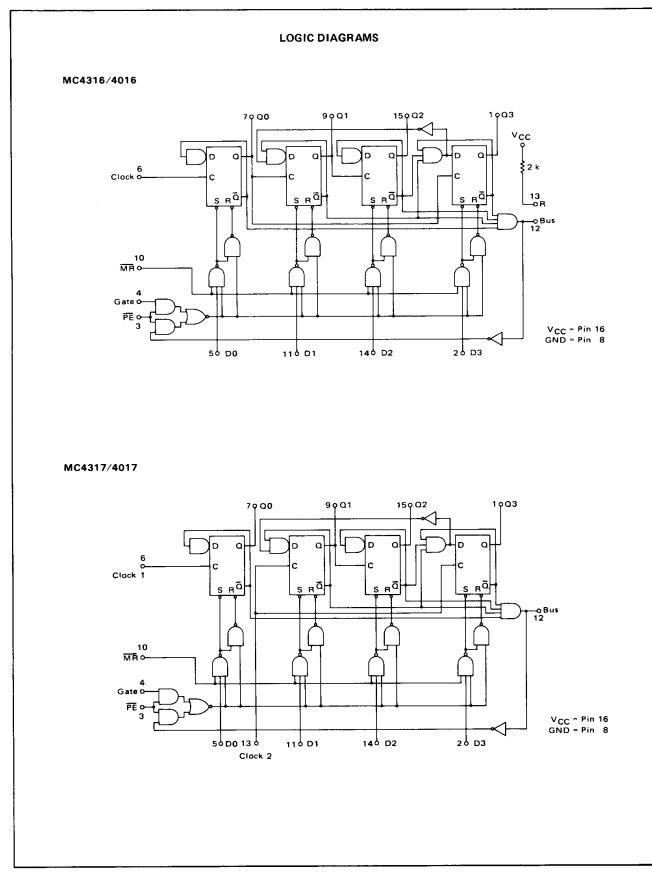

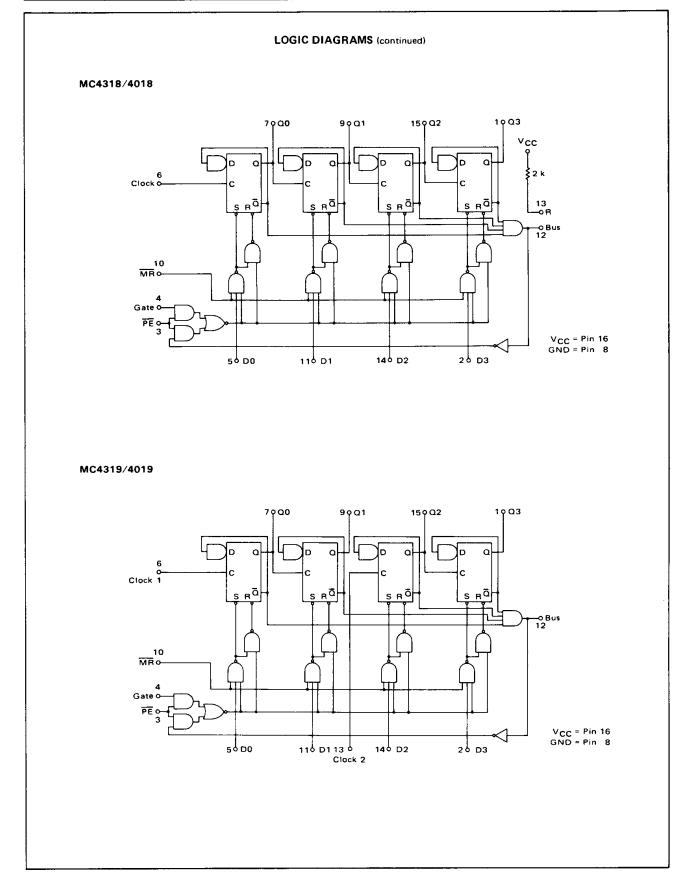

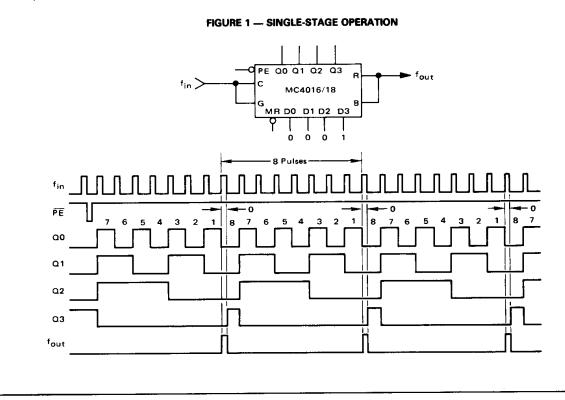

Operation of both counters is essentially the same. The MC4316/4016 has a maximum modulus of ten while the MC4318/4018 is capable of dividing by up to sixteen. Minor differences in the programming procedure will be covered in the discussion of cascaded stages.

Suitable connections for operating a single stage are shown in Figure 1, as well as appropriate waveforms. The desired modulus is applied to the data inputs D0, D1, D2, and D3 in binary (MC4018) or binary coded decimal (MC4016) positive logic format. If a number greater than nine (BCD 1001) is applied to the MC4016, it treats the most significant bit position as a zero; if for example, binary fourteen (1110) were applied to an MC4016, the counter would divide by six. BCD eight is programmed in Figure 1. As PE is taken low the states on the parallel inputs are transferred to their respective outputs. Subsequent positive transitions of the input clock will decrement the counter until the all zero state is detected by the bus gate. The resulting positive transition of the bus line is internally inverted and fed back to the preset gating circuitry but does not yet preset the counter since the gateclock input is still high. As the clock returns to the low state the counter is set to the programmed state, taking the bus line low. The net result is one positive pulse on the bus line for every N clock pulses. The output pulse width is approximately equal to one clock pulse high time.

Operation will continue in this fashion until the data on the programmable inputs is changed. Since the preset circuitry is inhibited except when the counter is in the zero state, preset data may be changed while clocking is occurring. If it is necessary to enter a new number before the counter has reached zero this can be done by momentarily taking PE low. Countdown will continue from the new number on the next positive clock transition.

The counters can be made to divide by 10 (MC4016) or 16 (MC4018) by inhibiting the preset logic. This may be done by either holding the gate input high or by holding the bus line low.

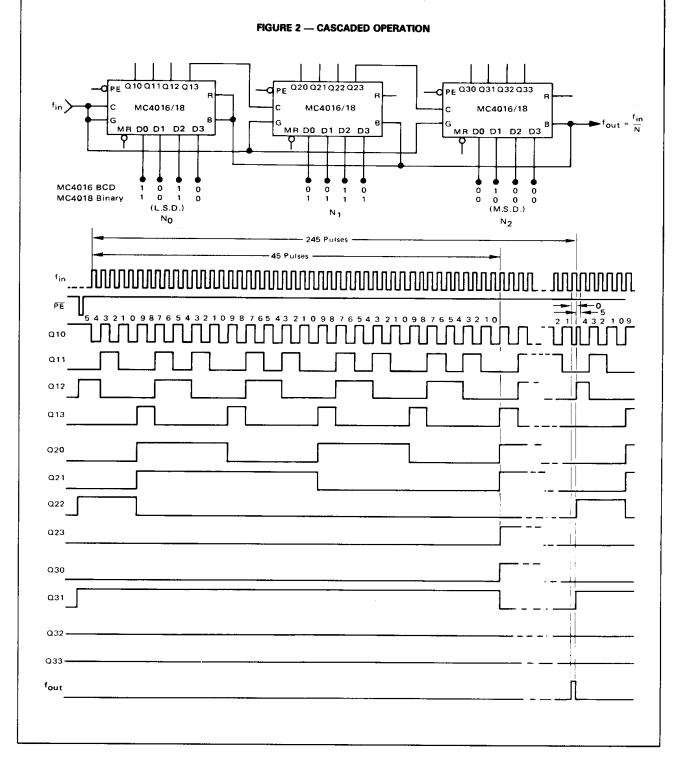

The normal connections for cascading stages are indicated in Figure 2, with the appropriate waveforms. Note that the gate input of each stage is connected to the clock; all bus outputs are tied to one of the internal pullup resistors, R. The total modulus for cascaded MC4016s is determined from  $N_T = N_0 + 10N_1 + 100N_2 + ...; N_T$ for MC4018s is given by  $N_T = N_0 + 16N_1 + 256N_2$ + ... Stated another way, the BCD equivalent of each decimal digit is applied to respective MC4016 stages while the data inputs of the MC4018 stages are treated as part of one long binary number. The difference in programming is illustrated in Figure 2 where  $N_T = 245$ is coded for both counter types.

Cascaded operation can be further clarified by referring to the timing diagram of Figure 2. For the MC4016, counting begins with the first positive clock transition after the data has been set in. After the five clock pulses, the leastsignificant stage has been counted down to zero. The bus line does not go high at this time since the three bus terminals are wire-ORed and the other two stages are not in the zero state. Since no reset occurs, the next positive

### OPERATING CHARACTERISTICS: MC4316/4016, MC4318/4018

clock edge advances the least significant stage to the nine (1001) state, causing the second stage to be decremented. The process continues in this manner with the least significant stage now dividing by ten. The second stage eventually counts down to zero and also reverts to dividing by ten. Each pulse out of the second stage decrements the third until it reaches zero. At this time the bus line goes high; it remains high until the clock goes low, causing all three stages to be reset to the programmed count again.

#### OPERATING CHARACTERISTICS: MC4316/4016, MC4318/4018

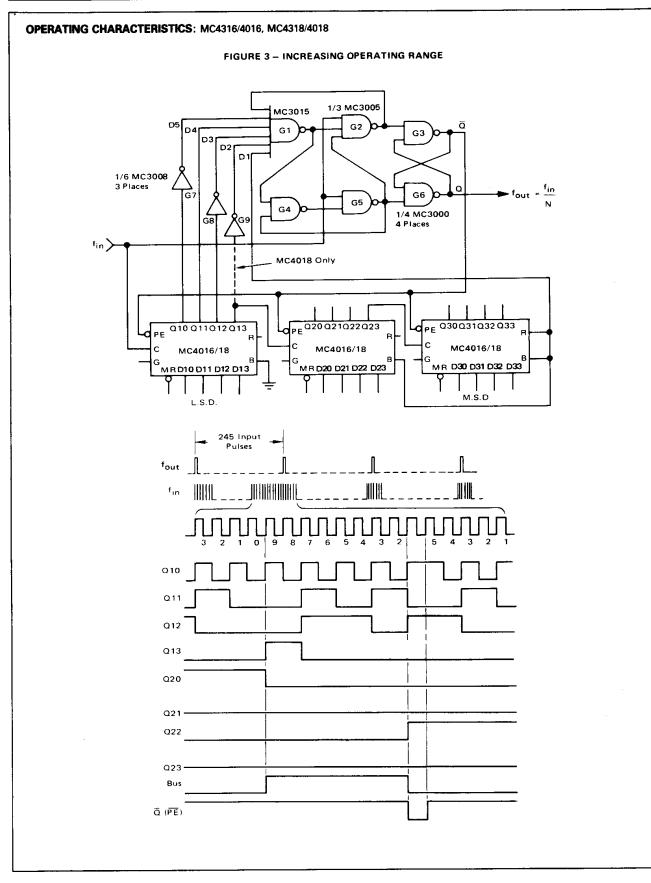

Maximum operating frequency of the basic MC4016/ 4018 counter is limited by the time required for reprogramming at the end of each count down cycle. Operation can be extended to approximately 25 MHz by adding an "early decode" feature as shown in Figure 3. The appropriate connections for three stages are shown; however up to eight stages can be satisfactorily cascaded. Note the following differences between this and the nonextended method: the counter gate inputs are not connected to the input clock; all Parallel Enables are connected to the  $\overline{\mathbf{Q}}$  output of a type D flip-flop formed by gates G1 through G6; the bus terminal of the least significant stage is grounded; all other bus terminals and one internal resistor, R, are connected together and serve as a data input to the flip-flop. Four additional data inputs are provided for decoding the "two" state of the least significant stage. Circuit operation is illustrated in the waveforms of Figure 3 where the timing for the end of

a count-down cycle is shown in expanded form. The counter parallel inputs are assumed to have N = 245applied. Timing is not shown for the third stage since it has already been counted down to the all zero state. As the next-to-least significant stage reaches zero, the common bus line goes high. Count down of the least significant stage continues until the "two" state is reached. This condition causes the remaining D inputs to the flipflop to be high. The next-to-last clock pulse of the cycle then triggers the flip-flop Q output high.  $\overline{Q}$  simultaneously takes the parallel enable of all stages low, resetting the programmed data to the outputs. The next input pulse clocks Q (fout) back to the zero state since the data inputs to the flip-flop are no longer all high. The positive output pulse is one input clock period in duration. Note that division by N equal to 1 or 2 is not available using this method.

#### OPERATING CHARACTERISTICS MC4317/4017, MC4319/4019

The MC4317/4017 consists of a modulo 2 and a modulo 5 programmable counter. The MC4319/4019 contains two modulo 4 programmable counters. Both parts are implemented in the same manner as the MC4316/4016 and MC4318/4018, however in these devices the output of the appropriate flip-flop is disconnected from the input of the next flip-flop. This input is then brought out as the second clock input for the package (see logic diagrams on page 2 of this data sheet). The resistor existing on the MC4316/ 4016 and MC4318/4018 is eliminated on the MC4317/4017 and MC4319/4019 in order not to exceed 16 pins. Elimination of the resistor causes no problems because only one resistor is required per divider chain and these parts will normally be used with the MC4316/4016 and/or MC4318/4018. In applications where the parts are used alone, an external resistor is connected to the bus output. To operate the MC4317/4017 as a modulo 2 program-

mable counter, the modulo 5 programmable counter

must be disabled by programming it to zero (D1, D2, and D3 grounded). Likewise, to use the device as a modulo 5 programmable counter the modulo 2 counter must be disabled (D0 grounded). Operation of the MC4319/4019 is similar in that the modulo 4 counter not being used must be disabled by programming it to zero (D0 thru D1 grounded or D2 and D3 grounded).

When cascading packages for large divide ratios, the most significant Q output of the modulo counter being used provides the input for the next package and all bus outputs are tied together. This method of connection is the same as for the MC4316/4016 and MC4318/4018.

The MC4317/4017 and MC4319/4019 can be made to perform the same function as the MC4316/4016 and MC4318/4018, respectively, by externally connecting the last Q output of one counter to the clock input of the other counter and programming inputs in the normal manner.

#### **APPLICATIONS INFORMATION**

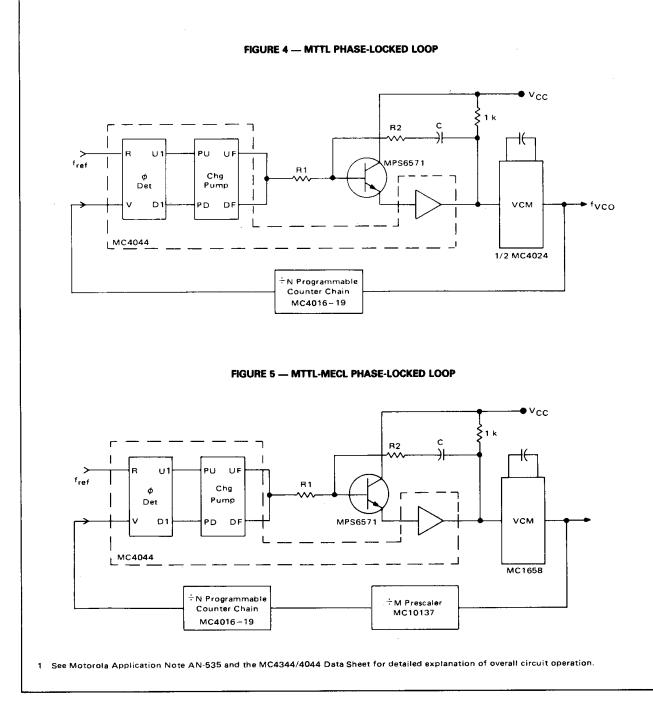

A typical system application for programmable counters is illustrated in the frequency synthesizer shown in Figure 4. There the counter provides a means of digitally selecting some integral multiple of a stable reference frequency. The circuit phase locks the output,  $f_{VCO}$ , of a voltage controlled oscillator to a reference frequency,  $f_{ref}$ .<sup>1</sup> Circuit operation is such that  $f_{VCO} = Nf_{ref}$ , where N is the divider ratio of the feedback counter.

In many synthesizer applications the VCO is operated at VHF frequencies too high for direct division by TTL counters. In these cases the VCO output is usually prescaled by using a suitable fixed divide-by-M ECL circuit as shown in Figure 5. For this configuration,  $f_{VCO} =$ NMf<sub>ref</sub>, where N is variable (programmable) and M is fixed. Design of the optimum loop filter requires that the input reference frequency be as high as possible where

the upper limit is established by the required channel spacing. Since  $f_{VCO} = Nf_{ref}$  in the non-prescaled case, if N is changed by one, the VCO output changes by  $f_{ref}$ , or the synthesizer channel spacing is just equal to  $f_{ref}$ . When the prescaler is used as in Figure 5,  $f_{VCO} = NMf_{ref}$ , and a change of one in N results in the VCO changing by Mf\_{ref}, i.e., if  $f_{ref}$  is set equal to the minimum permissible channel spacing as is desirable, then only every M channels in a given band can be selected. One solution is to set  $f_{ref} =$  channel spacing/M but this leads to more stringent loop filter requirements.

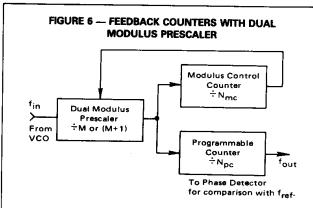

An alternate approach that avoids this problem is provided by the counter configuration shown in Figure 6.<sup>2</sup> It too uses a prescaler ahead of a programmable counter, however the modulus of the prescaler is now controlled by a third counter, causing it to alternate between M and M + 1. Operation is best explained by assuming that all three counters have been set for the beginning of a cycle: the prescaler for division by (M + 1), the modulus control counter for division by  $N_{mc}$ , and the programmable counter for division by  $N_{pc}$ . The prescaler will divide by (M + 1) until the modulus control counter has counted down to zero; at this time, the all zero state is detected and causes the prescaler to divide by M until the programmable counter has also counted down to zero. When this occurs, a cycle is complete and each counter is reset to its original modulus in readiness for the next cycle. For this configuration,

$$fout = \frac{f_{in}}{MN_{pc} + N_{mc}}$$

In terms of the synthesizer application,  $f_{VCO} = (MN_{pc} + N_{mc}) f_{ref}$  and channels can be selected every  $f_{ref}$  by letting  $N_{pc}$  and  $N_{mc}$  take on suitable integer values, including zero.

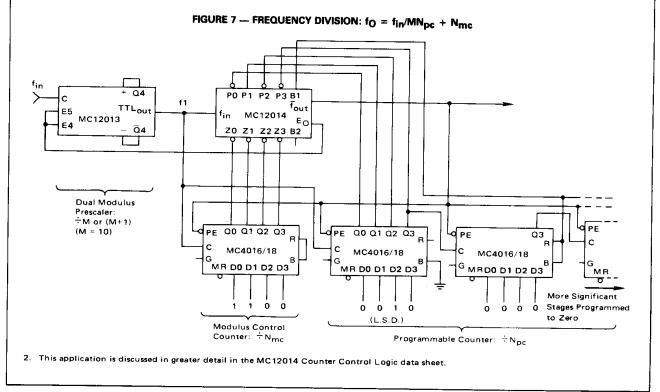

A simplified example of this technique is shown in Figure 7. The MC12013 Dual Modulus Prescaler divides by either 10 or 11 when connected as shown in Figure 7. If the E3 and E4 Enable inputs are high at the start of a prescaler cycle, division by 10 results; if the Enable inputs are low at the beginning of the cycle, division by 11 results. The zero detection circuitry of the MC12014 Counter Control Logic is connected to monitor the outputs of the modulus control counter; this provides a suitable enable signal at E0 as the modulus control counter reaches its terminal (zero) count. The remainder of the MC12014 is connected to extend the operating frequency of the programmable counter chain.

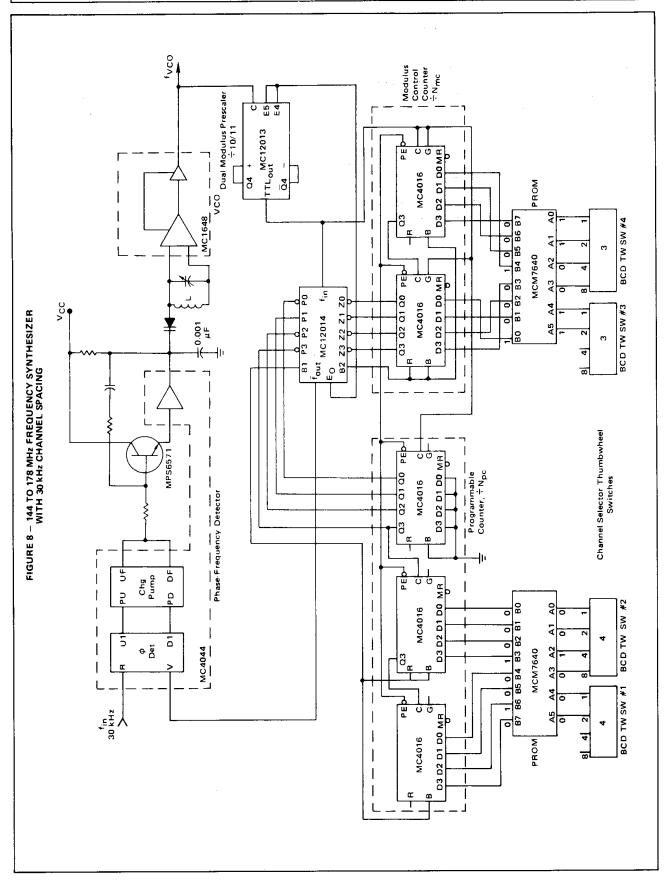

A specific example of this technique is shown in Figure 8. There the feedback divider circuitry required for generating frequencies between 144 MHz and 178 MHz with 30 kHz channel spacing is shown.<sup>2</sup>

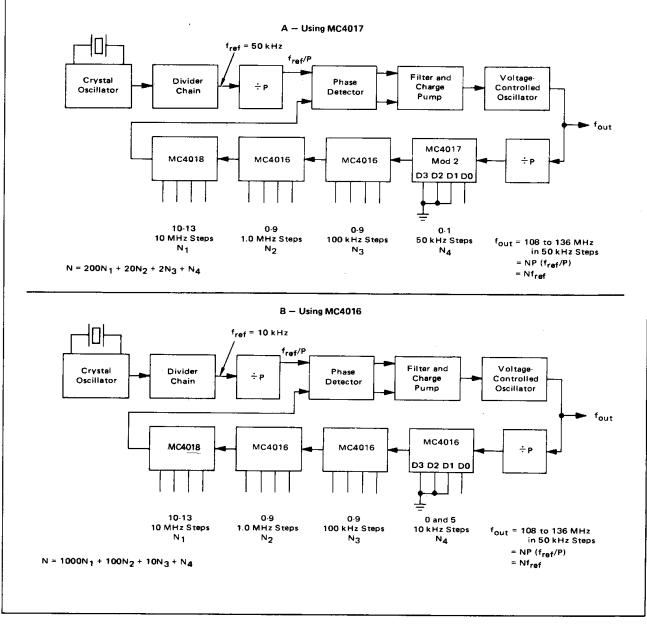

Figure 9 shows a frequency synthesizer system for the aircraft band of 108 to 136 MHz with a channel spacing of 50 kHz. The use of the MC4017 as a modulo 2 programmable counter is shown in Figure 9A, while Figure 9B shows the same system implemented using the MC4016. For a system of this type it is desirable to use direct-reading thumbwheel switches for channel selection. To implement this system with these constraints, it is necessary to calculate the required reference frequency ( $f_{ref}$ ). Using the equations in Figure 9A, the required reference is 50 kHz and N4 must be programmed to 0 and 1. Figure 9B requires a reference frequency of 10 kHz and N4 must be programmed to only 0 and 5.

meeting the system requirements. The higher the reference frequency, the higher the number of sampling pulses received by the phase detector per unit time. This results in (1) easier filtering of the control voltage, (2) faster lock-up time, and (3) less noise in the output spectrum. The higher reference frequency is also desirable because the reference frequency appears as sidebands on the output frequency and the farther the sidebands are away from the output the better the system. Another advantage of the higher reference frequency is the smaller divide ratio required in the programmable counter chain. This is advantageous when calculating realizable resistors for the filter. For these reasons, the system using the MC4017 is superior to the one using the MC4016.

For any phase-locked loop system it is desirable to maintain as high a reference frequency as possible while

FIGURE 9 --- 108 TO 136 MHz FREQUENCY SYNTHESIZER WITH 50 kHz CHANNEL SPACING

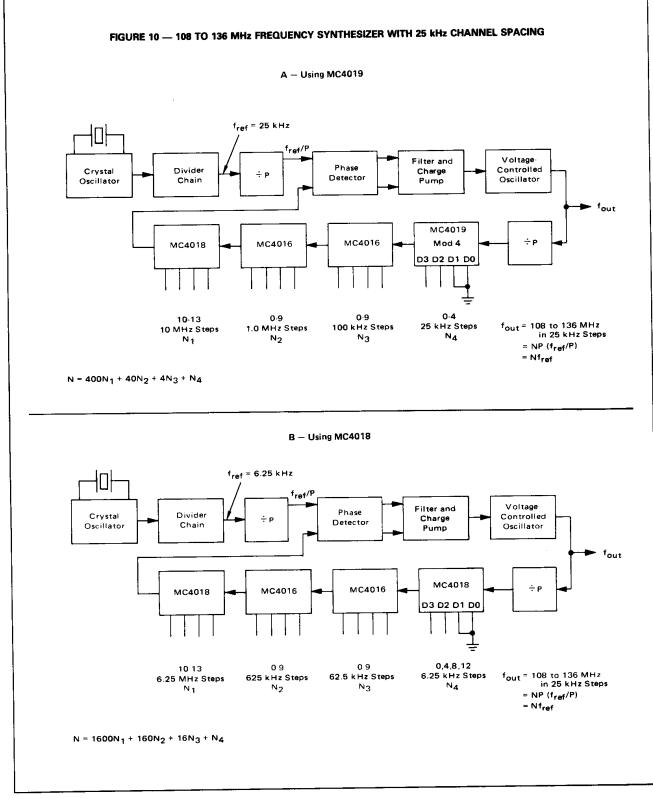

Figure 10 shows the implementation of the aircraft band synthesizer with 25 kHz channel spacing (the 25 kHz spacing has been proposed to the FCC). The system is implemented in Figure 10A using the MC4019, and has

a reference frequency of 25 kHz. Figure 10B shows the system using an MC4018 as the first counter, and has a reference frequency of 6.25 kHz to obtain the direct programming.

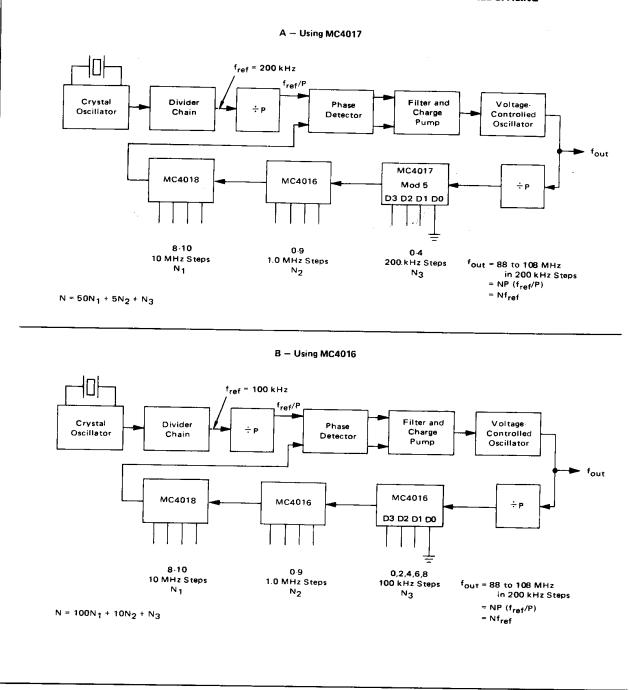

Figures 11A and 11B show the FM band implemented with MC4017 (used as a modulo 5 counter) and MC4016, respectively. The first system has a 200 kHz reference frequency, and the second system has a 100 kHz reference frequency. These systems using the MC4017/19 offer the same advantages over the MC4016/18 as with the aircraft band systems.

nel spacing is 2 × 10<sup>n</sup> Hz when used as a modulo 5 programmable counter, and 5 × 10<sup>n</sup> Hz when used as a modulo 2 programmable counter. The MC4319/4019 is for applications with a channel spacing of  $2.5 \times 10^{n}$  Hz. The MC4316/4016 covers phase-locked loop applications where the channel spacing is 1 × 10<sup>n</sup> Hz. The MC4318/ 4018 is used when the most significant digit is between 9 and 15.

These examples illustrate the desirability of the MC4317/ 4017 for phase-locked loop applications where the chan-

## L 18. MOTOROLA SC LOGIC

Ł.

14E D 6367252 0082850 7

T-90-20

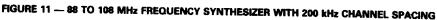

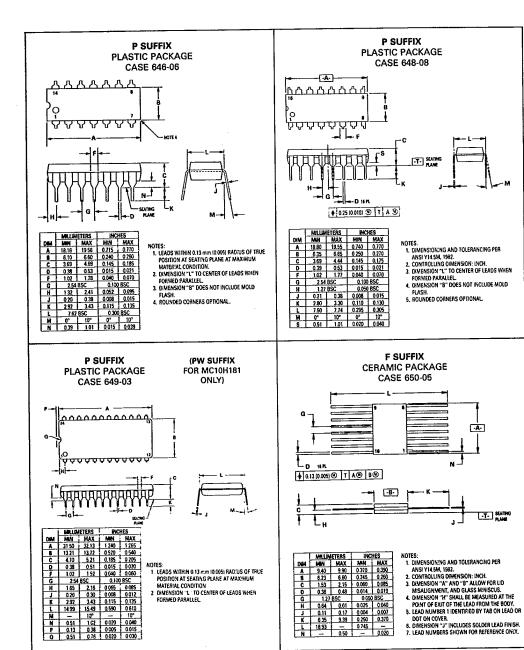

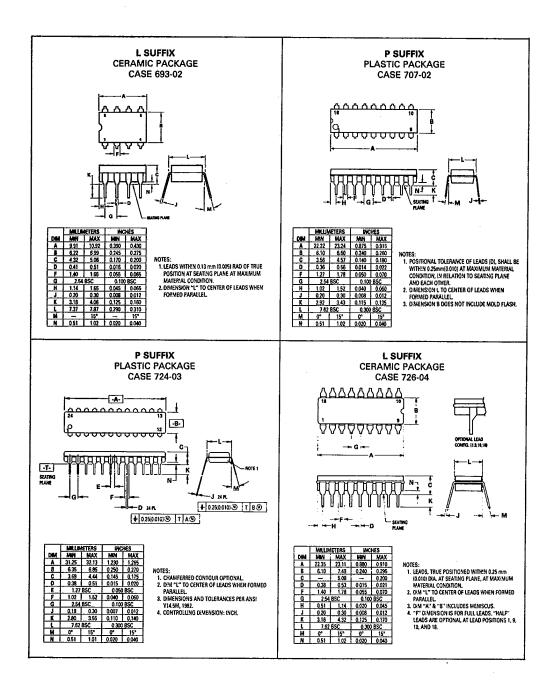

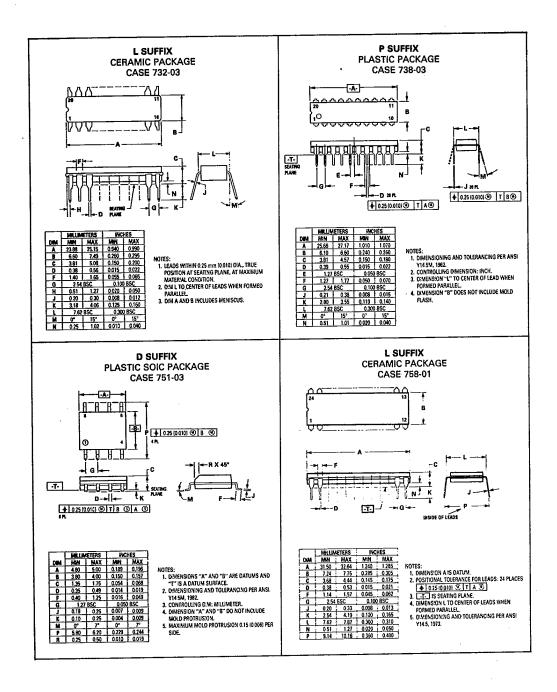

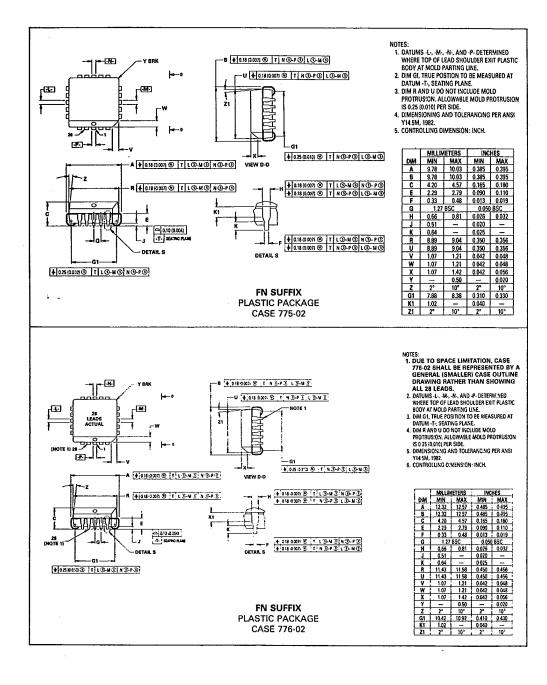

A letter suffix to the MECL logic function part number is used to specify the package style (see drawings below). See appropriate selector guide for specific packaging available for a given device type.

MOTOROLA SC LOGIC

PACKAGE OUTLINE DIMENSIONS (continued)

E.

14E D 6367252 0082851 9

T-90-20

1

MOTORCLA SC LOGIC

## 14E D 6367252 0082852 0

PACKAGE OUTLINE DIMENSIONS (continued)

T-90-20

,

14E D 📲 6367252 0082853 2 📲

T-90-20

## PACKAGE OUTLINE DIMENSIONS (continued)

## MOTOROLA SC LOGIC

# 14E D 6367252 0082854 4

T-90-20

1-30

MOTOROLA SC LOGIC

14E D 6367252 0082855 6

T-90-20

## **MECL Logic Surface Mount**

#### WHY SURFACE MOUNT?

Surface Mount Technology is now being utilized to offer answers to many problems that have been created in the use of insertion technology.

Limitations have been reached with insertion packages and PC board technology. Surface Mount Technology offers the opportunity to continue to advance the Stateof-the-Art designs that cannot be accomplished with Insertion Technology.

Surface Mount Packages allow more optimum device performance with the smaller Surface Mount configuration. Internal lead lengths, parasitic capacitance and inductance that placed limitations on chip performance have been reduced.

The lower profile of Surface Mount Packages allows more boards to be utilized in a given amount of space. They are stacked closer together and utilize less total volume than insertion populated PC boards.

Printed circuit costs are lowered with the reduction of the number of board layers required. The elimination or reduction of the number of plated through holes in the board, contribute significantly to lower PC board prices.

Surface Mount assembly does not require the preparation of components that are common on insertion technology lines. Surface Mount components are sent directly to the assembly line, eliminating an intermediate step.

Automatic placement equipment is available that can place Surface Mount components at the rate of a few thousand per hour to hundreds of thousands of components per hour.

Surface Mount Technology is cost effective, allowing the manufacturer the opportunity to produce smaller units and offer increased functions with the same size product.

#### MECL AVAILABILITY IN SURFACE MOUNT

Motorola is now offering MECL 10K and MECL 10KH in the PLCC (Plastic Leaded Chip Carrier) packages.

MECL in PLCC may be ordered in conventional plastic rails or on Tape and Reel. Refer to the Tape and Reel section for ordering details.

#### TAPE AND REEL

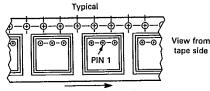

Motorola has now added the convenience of Tape and Reel packaging for our growing family of standard Integrated Circuit products. The packaging fully conforms to the latest EIA RS-481A specification. The antistatic embossed tape provides a secure cavity sealed with a peel-back cover tape.

# GENERAL INFORMATION Beel Size 13 inch

- Reel Size 13 inch (330 mm) Suffix: R2 Tape Width 16 mm

- Tape Width 16 mn

Units/Reel 1000

#### MECHANICAL POLARIZATION

Linear direction of travel

#### ORDERING INFORMATION

- Minimum Lot Size/Device Type = 3000 Pieces.

- No Partial Reel Counts Available.

- To order devices which are to be delivered in Tape and Reel, add the appropriate suffix to the device number being ordered.

#### EXAMPLE:

ORDERING CODE MC10100FN MC10100FNR2 MC10H100FN MC10H100FNR2 MC12015D MC12015DR2 SHIPMENT METHOD Magazines (Rails) 13 inch Tape and Reel Magazines (Rails) 13 inch Tape and Reel Magazines (Rails) 13 inch Tape and Reel

#### DUAL-IN-LINE PACKAGE TO PLCC PIN CONVERSION DATA

The following tables give the equivalent I/O pinouts of Dual-In-Line (DIL) packages and Plastic Leaded Chip Carrier (PLCC) packages.

#### **Conversion Tables**

| 16 PIN DIL<br>20 PIN PLCC | 11 | 2 | 3 | 4 | 5 | 6 | 7 | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

|---------------------------|----|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|

| 20 PIN PLCC               | 2  | 3 | 4 | 5 | 7 | 8 | 9 | 10 | 12 | 13 | 14 | 15 | 17 | 18 | 19 | 20 |

20 PIN DIL

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

20

PIN PLCC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

20

PIN PLCC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

24 PIN DIL 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 28 PIN PLCC 2 3 4 5 6 7 9 10 11 12 13 14 16 17 18 19 20 21 23 24 25 26 27 28