## 9.9-11.2Gb/s Optical Modulator Driver

### **TGA4953-EPU**

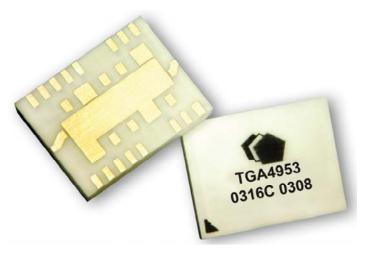

OC-192 Metro and Long Haul Applications Surface Mount Package

### **Description**

The TriQuint TGA4953-EPU is part of a series of surface mount modulator drivers suitable for a variety of driver applications and is compatible with Metro MSA standards.

The 4953 consists of two high performance wideband amplifiers combined with off chip circuitry assembled in a surface mount package. A single 4953 placed between the MUX and Optical Modulator provides OEMs with a board level modulator driver surface mount solution.

The 4953 provides Metro and Long Haul designers with system critical features such as: low power dissipation (1.1 W at Vo=6 V), very low rail ripple, high voltage drive capability at 5V bias (6 V amplitude adjustable to 3 V), low output jitter (10 ps typical), and low input drive sensitivity (250 mV at Vo=6 V).

The 4953 requires external DC blocks, a low frequency choke, and control circuitry.

The TGA4953-EPU is available on an evaluation board.

## **Key Features and Performance**

- Metro MSA Compatible

- Wide Drive Range (3V to 10V)

- Single-ended Input / Output

- Low Power Dissipation (1W at Vo=6V)

- Very Low Rail Ripple

- 25 ps Edge Rates (20/80)

- Small Form Factor

- 11.4 x 8.9 x 2 mm

- 0.450 x 0.350 x 0.080 inches

- Evaluation Board Available.

## **Primary Applications**

Mach-Zehnder Modulator Driver for Metro and Long Haul.

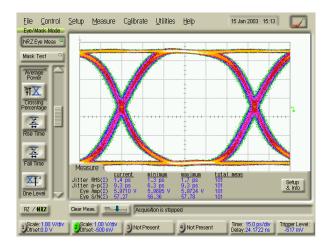

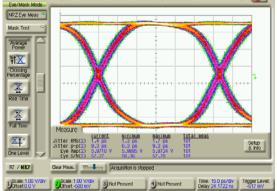

#### **Measured Performance**

TGA4953 Evaluation Board (Metro MSA Conditions) 10.7 Gb/s, Vplus=5 V, Id=210 mA, (Pdc=1.1 Watt) Vout=6 Vpp, CPC=50%, Vin = 500 mVpp Scale: 2 V/div, 15 ps/div

#### **MAXIMUM RATINGS**

| SYMBOL         | PARAMETER <u>6</u> /                     | VALUE         | NOTES         |

|----------------|------------------------------------------|---------------|---------------|

|                | POSITIVE SUPPLY VOLTAGE                  |               |               |

| Vd1, Vd2T      | Drain Voltage                            | 8 V           |               |

|                |                                          |               |               |

|                | POSITIVE SUPPLY CURRENT                  |               |               |

| Id1            | Drain Current                            | 100 mA        | <u>1</u> /    |

| Id2T           | Drain Current                            | 300mA         |               |

| $P_d$          | POWER DISSIPATION                        | 4 W           | <u>2</u> /    |

|                | NEGATIVE GATE                            |               |               |

| Vg1, Vg2       | Voltage                                  | 0 V to -3 V   |               |

| Ig1, Ig2       | Gate Current                             | 5 mA          |               |

|                | CONTROL GATE                             |               |               |

| Vctrl1, Vctrl2 | Voltage                                  | Vd/2 to −3 V  | <u>3</u> /    |

| Ictrl1, Ictrl2 | Gate Current                             | 5 mA          |               |

|                | RF INPUT                                 |               |               |

| $P_{IN}$       | Sinusoidal Continuous Wave Power         | 23 dBm        |               |

| $V_{ m IN}$    | 10.7Gb/s PRBS Input Voltage Peak to Peak | 4 Vpp         |               |

| $T_{CH}$       | OPERATING CHANNEL TEMPERATURE            | 150 °C        | <u>4</u> / 5/ |

| $T_{STG}$      | STORAGE TEMPERATURE                      | -40 to 125 °C |               |

#### Notes:

- 1/ Assure the combination of Vd and Id does not exceed maximum power dissipation rating.

- 2/ When operated at this bias condition with a base plate temperature of 80°C, the median life is reduced.

- 3/ Assure Vctl1 never exceeds Vd1 and assure Vctrl2 never exceeds Vd2 during bias up and down sequences.

- 4/ These ratings apply to each individual FET.

- 5/ Junction operating temperature will directly affect the device median time to failure (MTTF). For maximum life, it is recommended that junction temperatures be maintained at the lowest possible levels.

- 6/ These ratings represent the maximum operable values for the device.

#### THERMAL INFORMATION

| Parameter                                                                  | Test Condition                 | P <sub>diss</sub> (W) | T <sub>Base</sub><br>(°C) | T <sub>CH</sub><br>(°C) | R <sub>eJC</sub><br>(°C/W) | MTTF<br>(HRS) |

|----------------------------------------------------------------------------|--------------------------------|-----------------------|---------------------------|-------------------------|----------------------------|---------------|

| R <sub>eJC</sub> Thermal Resistance<br>(channel to backside of<br>carrier) | Vd2T=4.7V,<br>Id2T=150mA +/-5% | .71                   | 80                        | 98                      | 26                         | >1E6          |

#### Notes:

- 1. Based on a detailed thermal model of the output stage where channel temperature is highest. Assumes worst case power dissipation condition (where no RF is applied at the input (no power is dissipated in the load).

- 2. Thermal transfer is conducted thru the bottom of the TGA4953EPU package into the motherboard. Design the motherboard to assure adequate thermal transfer to the base plate.

#### RF SPECIFICATIONS (T<sub>A</sub> = 25°C Nominal)

| NOTE                   | TEST                            | MEASUREMENT<br>CONDITIONS     | VALUE |     | UNITS |     |

|------------------------|---------------------------------|-------------------------------|-------|-----|-------|-----|

|                        |                                 |                               | MIN   | TYP | MAX   |     |

|                        | SMALL SIGNAL BW                 |                               |       | 8   |       | GHz |

|                        | SATURATED POWER BW              |                               |       | 12  |       | GHz |

| <u>1</u> /, <u>2</u> / | SMALL-SIGNAL                    | 2 and 4 GHz                   | 30    |     |       |     |

|                        | GAIN MAGNITUDE                  | 6 GHz                         | 28    |     |       |     |

|                        |                                 | 10 GHz                        | 26    |     |       | dB  |

|                        |                                 | 14 GHz                        | 19    |     |       |     |

|                        |                                 | 18 GHz                        | 12    |     |       |     |

|                        |                                 |                               |       |     |       |     |

|                        | GAIN FLATNESS                   | 500KHz thru 5GHz              |       |     | +/-1  | dB  |

|                        | SMALL SIGNAL AGC RANGE          | Midband                       |       | 30  |       | dB  |

|                        | NOISE FIGURE                    | 3 GHz                         |       | 2.5 |       | dB  |

| <u>3</u> /, <u>4</u> / | EYE AMPLITUDE                   | VD2T=8.0V                     | 10    |     |       |     |

|                        |                                 | VD2T=6.5V                     | 8.0   |     |       |     |

|                        |                                 | VD2T=5.5V                     | 7.0   |     |       | Vpp |

|                        |                                 | VD2T=4.5V                     | 6.0   |     |       |     |

|                        |                                 | VD2T=4.0V                     | 5.5   |     |       |     |

| <u>5</u> /             | ADDITIVE JITTER (rms)           |                               |       | .5  |       | ps  |

| <u>6</u> /, <u>7</u> / | SATURATED OUTPUT<br>POWER       | 2, 4, 6, 8, and<br>10 GHz     | 25    |     |       | dBm |

| <u>1</u> /, <u>2</u> / | INPUT RETURN LOSS<br>MAGNITUDE  | 2, 4, 6, 10, 14, and<br>18GHz | 10    | 15  |       | dB  |

| <u>1</u> /, <u>2</u> / | OUTPUT RETURN LOSS<br>MAGNITUDE | 2, 4, 6, 10, 14, and<br>18GHz | 10    | 15  |       | dB  |

|                        | RISE TIME (20/80)               |                               |       | 25  | 30    | ps  |

## RF SPECIFICATION (Continued)

#### Notes:

- 1/ Verified at package level RF test.

- 2/ Package RF Test Bias: Vd=5 V, adjust Vg1 to achieve Id=65 mA then adjust Vg2 to achieve Id=200mA, Vctrl=+0.2 V

- 3/ Verified by design, SMT assembled onto a demonstration board detailed on sheet 6.

- 4/ Vin=250mV, Data Rate = 10.7Gb/s, VD1=VD2T or greater, VCTRL2 and VG2 are adjusted for maximum output.

- 5/ Computed using RSS Method where Jrms additive = SQRT(Jrms out<sup>2</sup> Jrms in<sup>2</sup>)

- 6/ Verified at die level on-wafer probe.

- 7/ Power Bias Die Probe: Vtee=8 V, adjust Vg to achieve Id=175 mA+/-5%, Vctrl=1.5 V Note: At the die level, drain bias is applied thru the RF output port using a bias tee, voltage is at the DC input to the bias tee.

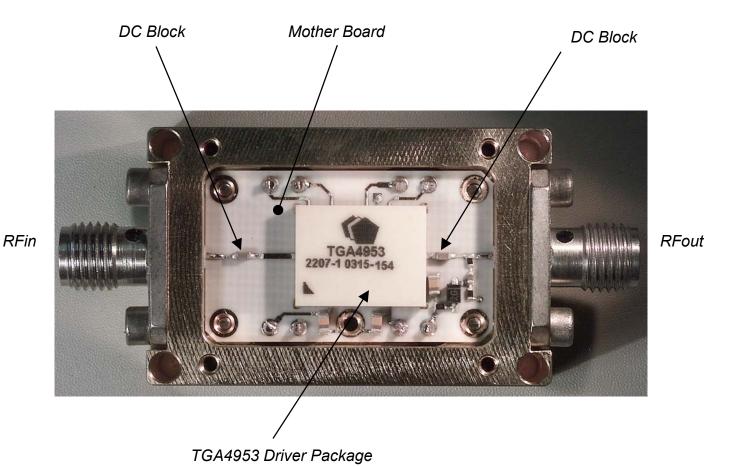

## **Demonstration Board**

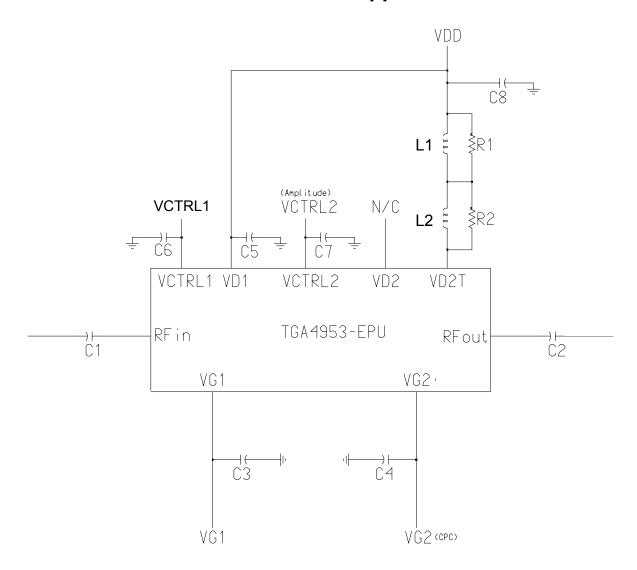

## **Demonstration Board Application Circuit**

#### Note:

- 1. C3 and C4 extend low frequency performance thru 30 KHz. For applications requiring low frequency performance thru 100 KHz, C3 and C4 may be omitted.

- 2. C5 is a power supply decoupling capacitor and may be omitted.

- 3. C6 and C7 are power supply decoupling capacitors and may be omitted when driven directly with an op-amp. Impedance looking into VCTRL1 and VCTRL2 is 10Kohms real.

# Demonstration Board Application Circuit (Continued)

## **Recommended Components:**

| DESIGNATOR | DESCRIPTION                  | MANUFACTURER | PART NUMBER            |

|------------|------------------------------|--------------|------------------------|

| C1, C2     | DC Block, Broadband          | Presidio     | BB0502X7R104M16VNT9820 |

| C3, C4, C5 | 10uF Capacitor MLC Ceramic   | AVX          | 0802YC106KAT           |

| C6, C7     | 0.01 uFCapacitor MLC Ceramic | AVX          | 0603YC103KAT           |

| C8         | 10 uF Capacitor Tantalum     | AVX          | TAJA106K016R           |

| L1         | 220 uH Inductor              | Belfuse      | S581-4000-14           |

| L2         | 330 nH Inductor              | Panasonic    | ELJ-FAR33MF2           |

| R1, R2     | 274 $Ω$ Resistor             | Panasonic    | ERJ-2RKF2740X          |

# **TGA4953 Typical Performance Data Measured on a Demonstration Board**

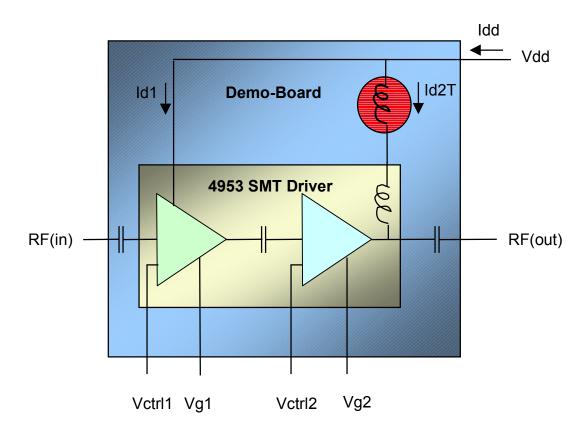

**Demonstration Board Block Diagram**

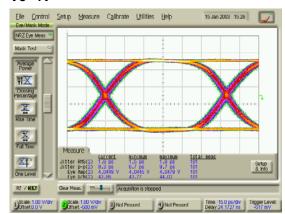

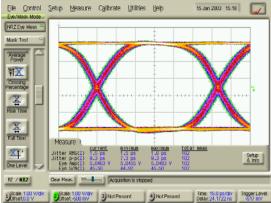

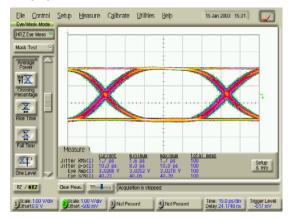

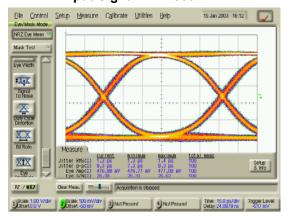

# Typical Measured Performance on Demonstration Board 10.7Gb/s 2^31-1, Vdd=5V CPC=50%

# Vo=6V Vo Elle Control Setup Measure Calibrate Utilities Help 15 Jan 2003 15-13 Elle CoverMask

#### Vo=4V

#### Vo=5V

#### Vo=3V

#### Input Signal Vin=500mV

# Typical Bias Conditions Vdd=5V

| Vo(V) | Vg1(V) | Vg2(V) | ld  | Vctrl2 |

|-------|--------|--------|-----|--------|

| 6     | -0.66  | -0.57  | 221 | +0.22  |

| 5     | -0.66  | -0.59  | 198 | +0.04  |

| 4     | -0.66  | -0.67  | 172 | -0.14  |

| 3     | -0.66  | -0.74  | 147 | -0.34  |

|       |        |        |     |        |

#### Notes:

- 1. Vdd=5V, Id1=65mA, and Vctrl1=-0.2V

- 2. Vin=500mVpp

- 3.50%CPC

# Bias Procedure Vdd=5V, Vo=6Vamp, CPC=50%

#### **Bias ON**

- 1. Disable the output of the PPG

- 2. Set Vd=0V Vctrl1=0V Vctrl2=0 Vg1=0V and Vg2=0V

- 3. Set Vg1=-1.5V Vg2=-1.5V Vctrl1=-0.2V

- 4. Increase Vd to 5V observing Id.

- Assure Id=0mA

- 5. Set Vctrl2=+0.2V

- Id should still be 0mA

- 6. Make Vg1 more positive until Idd=65mA.

- This is Id1 (current into the first stage)

- Typical value for Vg1 is -0.65V

- 7. Make Vg2 more positive until Idd=220mA.

- This sets Id2T to 155mA.

- Typical value for Vg2 is -0.55V

- 8. Enable the output of the PPG.

- Set Vin=500mV

- 9. <u>Output Swing Adjust</u>: Adjust <u>Vctrl2</u> slightly positive to increase output swing or adjust Vctrl slightly negative to decrease the output swing.

- Typical value for <u>Vctrl2 is +0.22V</u> for Vo=6V.

- 10. Crossover Adjust: Adjust  $\underline{Vg2}$  slightly positive to push the crossover down or adjust  $\underline{Vg2}$  slightly negative to push the crossover up.

- Typical value for <u>Vg2 is -0.57V</u> to center crossover with Vo=6V.

#### **Bias OFF**

- 1. Disable the output of the PPG

- 2. Set Vctrl2=0V

- 3. Set Vd=0V

- 4. Set Vctrl1=0V

- 5. Set Vg2=0V

- 6. Set Vq1=0V

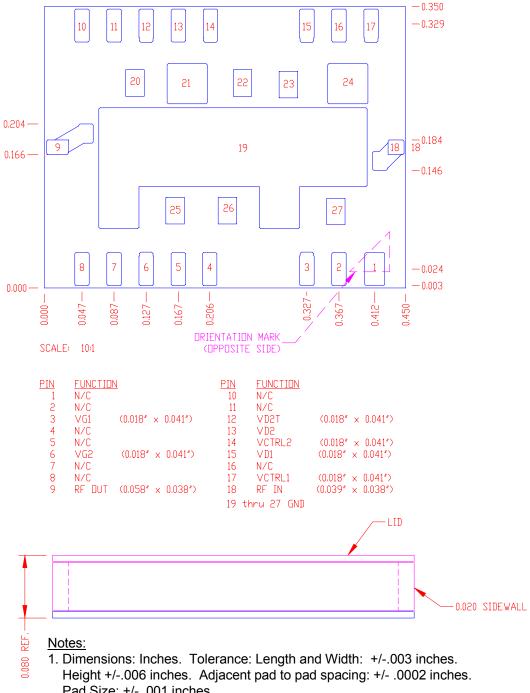

## **TGA4953 Mechanical Drawing**

Pad Size: +/- .001 inches.

2. Surface Mount Interface: Material: RO4003 (thickness=.008 inches), 1/2oz copper (thickness=.0007 inches) Plating Finish: 100-350 microinches nickel underplate, with 5-10 microinches flash gold overplate.