# intel

# Intel<sup>®</sup> 845 Family Chipset-Mobile: 82845MP/82845MZ Chipset Memory Controller Hub Mobile (MCH-M)

**Datasheet**

**April 2002**

Order Number: 250687-002

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Actual system-level properties, such as skin temperature, are a function of various factors, including component placement, component power characteristics, system power and thermal management techniques, software application usage and general system design. Intel is not responsible for its customers' system designs, nor is Intel responsible for ensuring that its customers' products comply with all applicable laws and regulations. Intel provides this and other thermal design information for informational purposes only. System design is the sole responsibility of Intel's customers should not rely on any Intel-provided information as either an endorsement or recommendation of any particular system design characteristics.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The 845MP/845 MZ Memory Controller Hub (MCH-M) may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

$l^2$ C is a 2-wire communications bus/protocol developed by Philips. SMBus is a subset of the  $l^2$ C bus/protocol and was developed by Intel. Implementations of the  $l^2$ C bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Alert on LAN\* is a result of the Intel-IBM Advanced Manageability Alliance and a trademark of IBM

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation

www.intel.com

or call 1-800-548-4725

Intel®, Pentium®, and SpeedStep<sup>™</sup> are registered trademarks or trademarks of Intel Corporation and its subsidiaries in the United States and other countries.

\*Other brands and names may be claimed as the property of others.

Copyright © Intel Corporation 2002

# int<sub>e</sub>l. *Contents*

| 1. | Overv                | <i>r</i> iew                                                             | 14 |  |  |  |

|----|----------------------|--------------------------------------------------------------------------|----|--|--|--|

|    | 1.1.                 | System Architecture                                                      | 15 |  |  |  |

|    | 1.2.                 | Mobile Intel Pentium <sup>®</sup> 4 Processor-M Host Interface           | 15 |  |  |  |

|    |                      | 1.2.1. System Bus Error Checking                                         |    |  |  |  |

|    | 1.3.                 | System Memory Interface                                                  |    |  |  |  |

|    | 1.4.                 | AGP Interface                                                            |    |  |  |  |

|    | 1.5.                 | Hub Interface                                                            | 18 |  |  |  |

|    | 1.6.                 | MCH-M Clocking                                                           |    |  |  |  |

|    | 1.7.                 | System Interrupts                                                        |    |  |  |  |

| 2. | Signa                | I Description                                                            | 20 |  |  |  |

|    | 2.1.                 | Host Interface Signals                                                   | 21 |  |  |  |

|    | 2.2.                 | DDR Interface                                                            |    |  |  |  |

|    | 2.3.                 | Hub Interface Signals                                                    |    |  |  |  |

|    | 2.4.                 | AGP Interface Signals                                                    |    |  |  |  |

|    | 2.4.                 | 2.4.1. AGP Addressing Signals                                            |    |  |  |  |

|    |                      | 2.4.2. AGP Flow Control Signals                                          |    |  |  |  |

|    |                      | 2.4.3. AGP Status Signals                                                |    |  |  |  |

|    |                      | 2.4.4. AGP Strobes                                                       |    |  |  |  |

|    |                      | 2.4.5. AGP/PCI Signals-Semantics                                         | 27 |  |  |  |

|    | 2.5.                 | Clocks, Reset, and Miscellaneous                                         |    |  |  |  |

|    | 2.6.                 | Voltage References, PLL Power                                            | 31 |  |  |  |

|    | 2.7.                 | Pin State Table                                                          | 31 |  |  |  |

| 3. | Register Description |                                                                          |    |  |  |  |

|    | 3.1.                 | Conceptual Overview of the Platform Configuration Structure              | 36 |  |  |  |

|    | 3.2.                 | Standard PCI Bus Configuration Mechanism                                 | 36 |  |  |  |

|    | 3.3.                 | Routing Configuration Accesses                                           | 37 |  |  |  |

|    |                      | 3.3.1. PCI Bus #0 Configuration Mechanism                                | 37 |  |  |  |

|    |                      | 3.3.2. Primary PCI and Downstream Configuration Mechanism                |    |  |  |  |

|    |                      | 3.3.3. AGP Configuration Mechanism                                       |    |  |  |  |

|    | 3.4.                 | MCH-M Register Introduction                                              |    |  |  |  |

|    | 3.5.                 | I/O Mapped Registers                                                     |    |  |  |  |

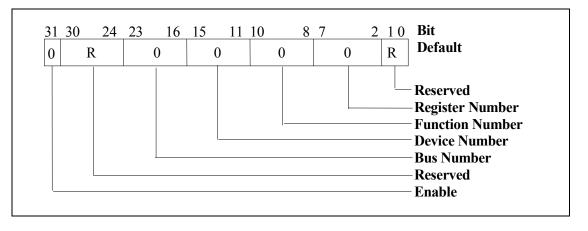

|    |                      | 3.5.1. CONFIG_ADDRESS – Configuration Address Register                   |    |  |  |  |

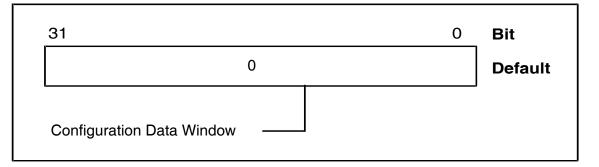

|    |                      | 3.5.2. CONFIG_DATA - Configuration Data Register                         |    |  |  |  |

|    | 3.6.                 | Memory Mapped Register Space                                             |    |  |  |  |

|    |                      | 3.6.1. DRAMWIDTH—DRAM Width Register                                     | 43 |  |  |  |

|    |                      | 3.6.2. DQCMDSTR – Strength Control Register for DQ and CMD Signal        | 11 |  |  |  |

|    |                      | Groups<br>3.6.3. CKESTR – Strength Control Register for CKE Signal Group |    |  |  |  |

|    |                      | 3.6.4. CSBSTR – Strength Control Register for CS# Signal Group           |    |  |  |  |

|    |                      | 3.6.5. CKSTR – Strength Control Register for CK Signal Group (CK / CK#)  |    |  |  |  |

|    |                      | 3.6.6. RCVENSTR – Strength Control Register for RCVENOUT# Signals        |    |  |  |  |

|    | 3.7.                 | Host-Hub Interface Bridge Device Registers – Device #0                   |    |  |  |  |

|    |                      | 3.7.1. VID – Vendor Identification Register – Device#0                   |    |  |  |  |

|    |                      | 3.7.2. DID – Device Identification Register – Device#0                   |    |  |  |  |

|    |                      | 3.7.3. PCICMD – PCI Command Register – Device #0                         | 52 |  |  |  |

|    |                      | 3.7.4. PCISTS – PCI Status Register – Device #0                          | 53 |  |  |  |

|    |                      |                                                                          |    |  |  |  |

2

3

|      | 3.7.5.             | RID – Revision Identification Register – Device #0                                                         |          |

|------|--------------------|------------------------------------------------------------------------------------------------------------|----------|

|      | 3.7.6.             | SUBC – Sub-Class Code Register – Device #0                                                                 |          |

|      | 3.7.7.             | BCC – Base Class Code Register – Device #0                                                                 |          |

|      | 3.7.8.             | MLT – Master Latency Timer Register – Device #0                                                            |          |

|      | 3.7.9.             | HDR – Header Type Register – Device #0                                                                     |          |

|      | 3.7.10.            | APBASE – Aperture Base Configuration Register – Device #0                                                  | 56       |

|      | 3.7.11.            | SVID – Subsystem Vendor ID – Device #0                                                                     |          |

|      | 3.7.12.            | SID – Subsystem ID – Device #0                                                                             | 57       |

|      | 3.7.13.            | CAPPTR – Capabilities Pointer – Device #0                                                                  |          |

|      | 3.7.14.            | AGPM- AGP Miscellaneous Configuration                                                                      |          |

|      | 3.7.15.            | DRB[0:7] – DRAM Row Boundary Registers – Device #0                                                         |          |

|      | 3.7.16.            | DRA[0:7] – DRAM Row Attribute Registers – Device #0                                                        |          |

|      | 3.7.17.            | DRT – DRAM Timing Register – Device #0                                                                     |          |

|      | 3.7.18.            | DRC – DRAM Controller Mode Register – Device #0                                                            |          |

|      | 3.7.19.            | DERRSYN – DRAM Error Syndrome Register                                                                     |          |

|      | 3.7.20.            | EAP – Error Address Pointer Register – Device #0                                                           |          |

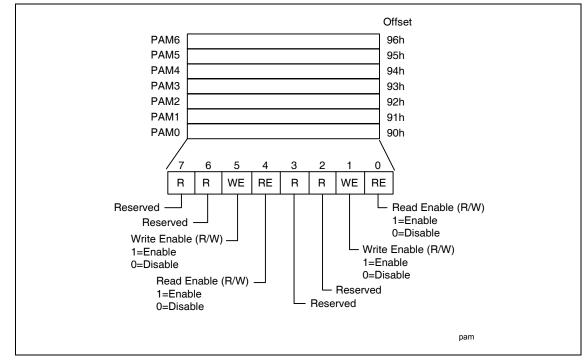

|      | 3.7.21.            | PAM[0:6] – Programmable Attribute Map Registers – Device #0                                                |          |

|      | 3.7.22.            | FDHC – Fixed DRAM Hole Control Register – Device #0                                                        |          |

|      | 3.7.23.            | SMRAM – System Management RAM Control Register – Device #0                                                 | 69       |

|      | 3.7.24.            | ESMRAMC – Extended System Mgmt RAM Control Register                                                        | 70       |

|      | 0 7 05             | – Device #0                                                                                                |          |

|      | 3.7.25.            | ACAPID – AGP Capability Identifier Register – Device #0                                                    |          |

|      | 3.7.26.            | AGPSTAT – AGP Status Register – Device #0                                                                  |          |

|      | 3.7.27.            | AGPCMD – AGP Command Register – Device #0                                                                  |          |

|      | 3.7.28.            | AGPCTRL – AGP Control Register                                                                             |          |

|      | 3.7.29.            | APSIZE – Aperture Size – Device #0                                                                         |          |

|      | 3.7.30.            | ATTBASE – Aperture Translation Table Base Register – Device #0                                             |          |

|      | 3.7.31.            | AMTT – AGP Interface Multi-Transaction Timer Register – Device #0                                          |          |

|      | 3.7.32.            | LPTT – AGP Low Priority Transaction Timer Register – Device #0                                             |          |

|      | 3.7.33.            | TOM – Top of Low Memory Register – Device #0                                                               |          |

|      | 3.7.34.            | MCH-MCFG – MCH-M Configuration Register – Device #0                                                        |          |

|      | 3.7.35.            | ERRSTS – Error Status Register – Device #0                                                                 |          |

|      | 3.7.36.            | ERRCMD – Error Command Register – Device #0                                                                |          |

|      | 3.7.37.            | SMICMD – SMI Command Register – Device #0                                                                  |          |

|      | 3.7.38.            | SCICMD – SCI Command Register – Device #0                                                                  |          |

|      | 3.7.39.            | SKPD – Scratchpad Data – Device #0                                                                         |          |

|      | 3.7.40.            | CAPID – Product Specific Capability Identifier                                                             |          |

| 3.8. |                    | ge Registers – Device #1                                                                                   |          |

|      | 3.8.1.             | VID1 – Vendor Identification Register – Device #1                                                          |          |

|      | 3.8.2.             | DID1 – Device Identification Register – Device #1                                                          |          |

|      | 3.8.3.             | PCICMD1 – PCI-PCI Command Register – Device #1                                                             |          |

|      | 3.8.4.             | PCISTS1 – PCI-PCI Status Register – Device #1                                                              |          |

|      | 3.8.5.             | RID1 – Revision Identification Register – Device #1                                                        |          |

|      | 3.8.6.             | SUBC1- Sub-Class Code Register – Device #1                                                                 |          |

|      | 3.8.7.             | BCC1 – Base Class Code Register – Device #1                                                                |          |

|      | 3.8.8.             | MLT1 – Master Latency Timer Register – Device #1                                                           |          |

|      | 3.8.9.             | HDR1 – Header Type Register – Device #1                                                                    |          |

|      | 3.8.10.            | PBUSN1 – Primary Bus Number Register – Device #1                                                           |          |

|      | 3.8.11.            | SBUSN1 – Secondary Bus Number Register – Device #1                                                         |          |

|      | 3.8.12.            | SUBUSN1 – Subordinate Bus Number Register – Device #1                                                      |          |

|      | 3.8.13.            | SMLT1 – Secondary Master Latency Timer Register – Device #1                                                |          |

|      | 3.8.14.            | IOBASE1 – I/O Base Address Register – Device #1                                                            | 94       |

|      | 0 0 1 -            |                                                                                                            | <u> </u> |

|      | 3.8.15.<br>3.8.16. | IOLIMIT1 – I/O Limit Address Register – Device #1<br>SSTS1 – Secondary PCI-PCI Status Register – Device #1 |          |

|       | 3.8.17.       MBASE1 – Memory Base Address Register – Device #1         3.8.18.       MLIMIT1 – Memory Limit Address Register – Device #1         3.8.19.       DMDASE4                                                                        |         |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|       | <ul> <li>3.8.19. PMBASE1 – Prefetchable Memory Base Address Register – Device</li> <li>3.8.20. PMLIMIT1 – Prefetchable Memory Limit Address Register – Device</li> <li>3.8.21. BCTRL1 – PCI-PCI Bridge Control Register – Device #1</li> </ul> | : #1 99 |

|       | 3.8.22. ERRCMD1 – Error Command Register – Device #1                                                                                                                                                                                           |         |

|       | 3.8.23. DWTMC – DRAM Write Thermal Management Control                                                                                                                                                                                          |         |

|       | 3.8.24. DRTMC – DRAM Read Thermal Management Control                                                                                                                                                                                           |         |

| Syste | em Address Map                                                                                                                                                                                                                                 | 105     |

| 4.1.  | Memory Address Ranges                                                                                                                                                                                                                          |         |

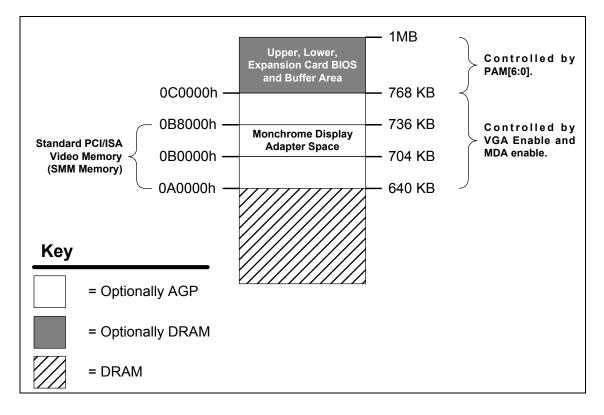

|       | 4.1.1. VGA and MDA Memory Space                                                                                                                                                                                                                |         |

|       | 4.1.2. PAM Memory Spaces                                                                                                                                                                                                                       |         |

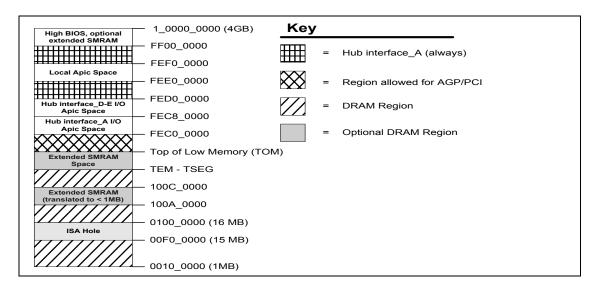

|       | 4.1.3. ISA Hole Memory Space                                                                                                                                                                                                                   |         |

|       | 4.1.4. TSEG SMM Memory Space                                                                                                                                                                                                                   |         |

|       | 4.1.5. System Bus Interrupt APIC Memory Space                                                                                                                                                                                                  |         |

|       | 4.1.6. High SMM Memory Space                                                                                                                                                                                                                   | 109     |

|       | 4.1.7. AGP Aperture Space (Device #0 BAR)                                                                                                                                                                                                      |         |

|       | 4.1.8. AGP Memory and Prefetchable Memory                                                                                                                                                                                                      | 109     |

|       | 4.1.9. Hub Interface A Subtractive Decode                                                                                                                                                                                                      |         |

| 4.2.  | AGP Memory Address Ranges                                                                                                                                                                                                                      |         |

|       | 4.2.1. AGP DRAM Graphics Aperture                                                                                                                                                                                                              |         |

| 4.3.  | System Management Mode (SMM) Memory Range                                                                                                                                                                                                      |         |

|       | 4.3.1. SMM Space Definition                                                                                                                                                                                                                    |         |

|       | 4.3.2. SMM Space Restrictions                                                                                                                                                                                                                  |         |

| 4.4.  | I/O Address Space                                                                                                                                                                                                                              | 112     |

| 4.5.  | MCH-M Decode Rules and Cross-Bridge Address Mapping                                                                                                                                                                                            | 112     |

|       | 4.5.1. Decode Rules for the Hub Interface A                                                                                                                                                                                                    | 112     |

|       | 4.5.2. AGP Interface Decode Rules                                                                                                                                                                                                              | 113     |

| Funct | tional Description                                                                                                                                                                                                                             | 114     |

| 5.1.  | Host Interface Overview                                                                                                                                                                                                                        | 114     |

|       | 5.1.1. Dynamic Bus Inversion                                                                                                                                                                                                                   | 114     |

|       | 5.1.2. System Bus Interrupt Delivery                                                                                                                                                                                                           | 114     |

|       | 5.1.3. Upstream Interrupt Messages                                                                                                                                                                                                             | 115     |

| 5.2.  | System Memory Interface                                                                                                                                                                                                                        | 115     |

|       | 5.2.1. DDR Interface Overview                                                                                                                                                                                                                  | 115     |

|       | 5.2.2. Memory Organization and Configuration                                                                                                                                                                                                   | 116     |

|       | 5.2.2.1. Configuration Mechanism for SO-DIMMs                                                                                                                                                                                                  | 116     |

|       | 5.2.2.1.1. Memory Detection and Initialization                                                                                                                                                                                                 | 116     |

|       | 5.2.2.1.2. SMBus Configuration and Access of the Serial<br>Presence Detect Ports                                                                                                                                                               | 116     |

|       | 5.2.2.1.3. Memory Register Programming                                                                                                                                                                                                         |         |

|       | 5.2.3. DRAM Performance Description                                                                                                                                                                                                            |         |

|       | 5.2.3.1. Data Integrity (ECC)                                                                                                                                                                                                                  |         |

| 5.3.  | AGP Interface Overview                                                                                                                                                                                                                         |         |

| 0.0.  | 5.3.1. AGP Target Operations                                                                                                                                                                                                                   |         |

|       | 5.3.1. AGP Transaction Ordering                                                                                                                                                                                                                |         |

|       | 5.3.2. AGP Transaction Ordening<br>5.3.3. AGP Signal Levels                                                                                                                                                                                    |         |

|       | 5.3.4. 4x AGP Protocol                                                                                                                                                                                                                         |         |

|       | 5.3.5. Fast Writes                                                                                                                                                                                                                             |         |

|       | 5.3.6. AGP FRAME# Transactions on AGP                                                                                                                                                                                                          |         |

|       |                                                                                                                                                                                                                                                |         |

4.

5.

|    | 5.3                 | 6.1. MCH-M Target and Initiator Operations for AGP FRA<br>Transactions |     |

|----|---------------------|------------------------------------------------------------------------|-----|

|    | 5.4. Power and      | Thermal Management                                                     |     |

|    |                     | Various States                                                         |     |

|    | 5.4.2.              | General Description of Supported CPU States                            | 123 |

|    |                     | General Description of ACPI System States                              |     |

|    | 5.4.4.              | Power Transitions                                                      | 124 |

|    | 5.4.5.              | Intel SpeedStep <sup>®</sup> Technology                                | 125 |

|    |                     | ocking                                                                 |     |

|    | 5.6. MCH-M Sys      | stem Reset and Power Sequencing                                        | 125 |

| 6. | Electrical Characte | ristics                                                                | 126 |

|    | 6.1. Absolute M     | aximum Ratings                                                         | 126 |

|    | 6.2. Thermal Cl     | naracteristics                                                         | 126 |

|    |                     | racteristics                                                           |     |

| 7. | Signal Groups       |                                                                        | 128 |

| 8. | DC Characteristics  |                                                                        | 130 |

| 9. | Ballout and Packag  | e Information                                                          | 133 |

|    | -                   | gram                                                                   |     |

|    |                     | le                                                                     |     |

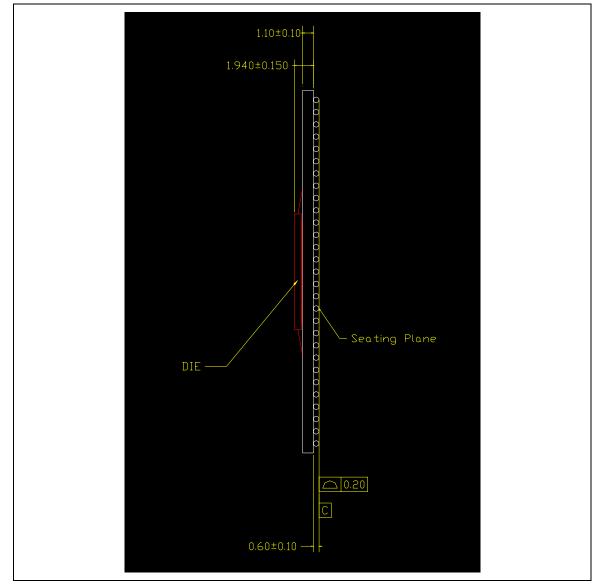

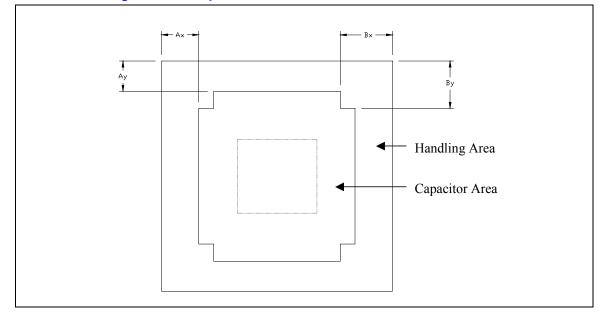

|    |                     | echanical Information                                                  |     |

|    | 5                   |                                                                        |     |

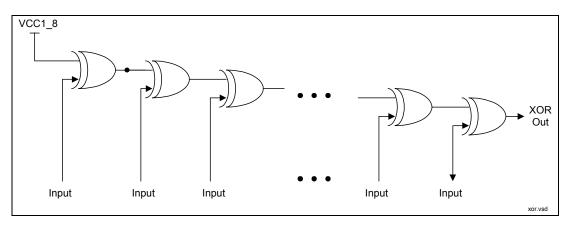

|    | ,                   | XOR Test Mode Initialization                                           |     |

|    |                     | XOR Chains                                                             |     |

|    |                     |                                                                        |     |

# int<sub>el</sub>.

## **Figures**

| Figure 1. Intel <sup>®</sup> 845MP/845MZ Chipset System Block Diagram |     |

|-----------------------------------------------------------------------|-----|

| Figure 2. Configuration Address Register                              |     |

| Figure 3. Configuration Data Register                                 |     |

| Figure 4. PAM Register Attributes                                     |     |

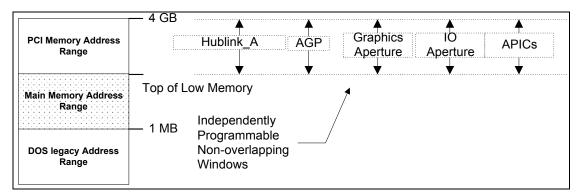

| Figure 5. Addressable Memory Space                                    | 105 |

| Figure 6. Detailed DOS Compatible Area Address Map                    | 106 |

| Figure 7. Detailed Extended Memory Range Address Map                  | 108 |

| Figure 8. MCH-M BGA Package Dimensions (Top View)                     | 139 |

| Figure 9. MCH-M BGA Package Dimensions (Side View)                    | 140 |

| Figure 10. MCH-M BGA Package Dimensions (Bottom View)                 | 141 |

| Figure 11. XOR–Tree Chain                                             | 143 |

## **Tables**

| Table 1. DDR Memory Capacity                                                 | 16  |

|------------------------------------------------------------------------------|-----|

| Table 2. DDR Device Configurations                                           |     |

| Table 3. MCH-M Clock Ratio Table                                             | 19  |

| Table 4. Host Interface Signal Descriptions                                  | 21  |

| Table 5. DDR Interface Signal Descriptions                                   | 23  |

| Table 6. Hub Interface Signal Descriptions                                   | 24  |

| Table 7. AGP Addressing Signal Descriptions                                  | 24  |

| Table 8. AGP Flow Control Signal Descriptions                                | 25  |

| Table 9. AGP Status Signal Descriptions                                      | 25  |

| Table 10. AGP Strobe Descriptions                                            | 26  |

| Table 11. AGP/PCI Signal Semantics Descriptions                              | 27  |

| Table 12. Clocks, Reset, and Miscellaneous Descriptions                      | 30  |

| Table 13. Voltage Reference Descriptions                                     | 31  |

| Table 14. Host Signals                                                       |     |

| Table 15. DDR Signals                                                        |     |

| Table 16. AGP Signals                                                        | 34  |

| Table 17. Clock/Miscellaneous Signals                                        | 35  |

| Table 18. Hub Interface Signals                                              |     |

| Table 19. Device Number Assignment                                           | 36  |

| Table 20. Nomenclature for Access Attributes                                 | 48  |

| Table 21. MCH-M Configuration Space for Device #0                            | 49  |

| Table 22. Control Signals for Various Memory Segments                        | 65  |

| Table 23. PAM Register Details                                               | 67  |

| Table 24. Nomenclature for Access Attributes                                 | 85  |

| Table 25. MCH-M Configuration Space - Device #1                              | 85  |

| Table 26. SMM Space                                                          |     |

| Table 27. Relation of DBI Bits to Data Bits                                  |     |

| Table 28. Data Bytes on SO-DIMM Used for Programming DRAM Registers          |     |

| Table 29. AGP Commands Supported by the MCH-M When Acting as an AGP Target   | 118 |

| Table 30. Fast Write Initialization                                          |     |

| Table 31. PCI Commands Supported by the MCH-M When Acting as a FRAME# Target |     |

| Table 32. Power Management State Combinations                                | 123 |

| Table 33. Intel 845MP/845MZ Power Transitions                                |     |

| Table 34. Absolute Maximum Ratings                                           | 126 |

| Table 35. Intel 845MP/845MZ Chipset MCH-M Package Thermal Resistance         | 126 |

| Table 36. Power Characteristics                                              | 127 |

| Table 37. Signal Groups                                                      |     |

| Table 38. DC Characteristics                                                 |     |

| Table 39. Top View (Left Side)                                               |     |

| Table 40. Top View (Right Side)                                              |     |

| Table 41. FCBGA Handling Zone Description                                    |     |

| Table 42. XOR Chains                                                         | 144 |

intel

## **Revision History**

| Rev. | Description         | Date       |

|------|---------------------|------------|

| 001  | Initial release     | March 2002 |

| 002  | Included 845MZ data | April 2002 |

250687-002

## **Reference Documents**

| Document                                                                                                                         | Document<br>Number/Location |

|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| Mobile Intel <sup>®</sup> Pentium <sup>®</sup> 4 Processor-M and Intel <sup>®</sup> 845MP/845MZ Chipset Platform<br>Design Guide | www.developer.intel.com     |

| Intel <sup>®</sup> 82801CAM I/O Controller Hub 3 (ICH3-M) Datasheet                                                              | www.developer.intel.com     |

| Intel <sup>®</sup> DDR200 JEDEC Specification Addendum, Revision 1.0                                                             | www.developer.intel.com     |

| Intel <sup>®</sup> DDR266 JEDEC Specification Addendum, Revision 0.9                                                             | www.developer.intel.com     |

| JEDEC Double Data Rate (DDR) SDRAM Specification, Revision 2.0                                                                   | www.jedec.org               |

| JEDEC PC2100 DDR SDRAM Un-buffered SO-DIMM Reference Design Specification (includes PC1600 DDR SDRAM)                            | www.jedec.org               |

| Accelerated Graphics Port Interface Specification Rev 2.0                                                                        | http://www.agpforum.org/    |

| PCI Local Bus Specification Rev. 2.1                                                                                             | www.pcisig.com              |

| PCI-PCI Bridge Specification Rev. 1.0                                                                                            | www.pcisig.com              |

| PCI Bus Power Management Interface Specification Rev. 1.0                                                                        | www.pcisig.com              |

| Advanced Configuration and Power Interface Specification (ACPI) Rev. 1.0b                                                        | www.teleport.com/~acpi/     |

*Note:* See Mobile Intel<sup>®</sup> Pentium<sup>®</sup> 4 Processor-M and Intel<sup>®</sup> 845MP/845MZ Chipset Platform Design Guide for an expanded set of related documents.

## Terminology

**MCH-M** - The Mobile Memory Controller Hub-M component that contains the processor interface, DRAM controller, and AGP interface. It communicates with the I/O controller hub (ICH3-M) and other IO controller hubs over proprietary interconnect called the hub interface.

**ICH3-M** - The Mobile I/O Controller Hub 3-M component that contains the primary PCI interface, LPC interface, USB, ATA-100, AC'97, and other IO functions. It communicates with the Intel<sup>®</sup> 845MP/845MZ Chipset MCH-M over a proprietary interconnect called hub interface.

Host - This term is used synonymously with processor.

Core - The internal base logic in the MCH-M.

**System Bus** - Processor-to-MCH-M interface. The Enhanced Mode of the Scalable Bus is the P6 Bus plus enhancements, consisting of source synchronous transfers for address and data, and system bus interrupt delivery. The Mobile Intel Pentium 4 Processor-M implements a subset of Enhanced Mode.

**Hub interface** - The proprietary hub interconnect that ties the MCH-M to the ICH3-M. In this document hub interface cycles originating from or destined for the primary PCI interface on the ICH3-M is generally referred to as hub interface cycles.

Accelerated Graphics Port (AGP) - Refers to the AGP interface that is in the MCH-M. It supports AGP 2.0 compliant components only with 1.5V signaling level. PIPE# and SBA addressing cycles and their associated data phases are generally referred to as AGP transactions. FRAME# cycles over the AGP bus are generally referred to as AGP/PCI transactions.

**PCI\_A** - The physical PCI bus, driven directly by the ICH3-M component. It supports 5-V, 32-bit, 33-MHz PCI 2.2 compliant components. Communication between PCI\_A and MCH-M occurs over hub interface. Note: Even though it is referred to as PCI\_A it is not PCI Bus #0 from a configuration standpoint.

Full Reset - A Full MCH-M Reset is defined in this document when RSTIN# is asserted.

System Bus - Synonymous with Host or Front Side Bus

**GART** - Graphics Aperture Re-map Table. This table contains the page re-map information used during AGP aperture address translations.

GTLB - Graphics Translation Look-aside Buffer. A cache used to store frequently used GART entries.

UP - Uniprocessor

**DBI** – Dynamic Bus inversion

**MSI** – Message Signaled Interrupts. MSI's allow a device to request interrupt service via a standard Memory Write transaction instead of through a hardware signal.

IPI – Inter Processor Interrupt

**Word** - 16 bits = 2 bytes

**Dword (DW)** – Doubleword: 32bits = 4 bytes

250687-002

**Qword (QW)** – Quadword: 8bytes = 4 words

**DQword (DQW)** – Double Quadword: 16 bytes or 8 words. This is sometimes referred to as a Superword (SW of Sword), and is also referred to as a "Cache Line".

# intel

## Intel<sup>®</sup> 845 Chipset MCH-M Features

- Processor/Host Bus Support

- Supports the Mobile Intel Pentium 4 Processor-M CPU

- Supports the Intel Pentium<sup>®</sup> 4 processor subset of the Enhanced Mode Scaleable Bus Protocol

- -2x Address, 4x Data

- Mobile Intel Pentium 4 Processor-M System Bus interrupt delivery

- Supports system bus at 400 MT/s (100 MHz)

- Supports host bus Dynamic Bus Inversion (DBI)

- -Supports 32-bit host bus addressing

- 12 deep In-Order Queue

- AGTL+ bus driver technology with integrated AGTL termination resistors

- Memory System

- Directly supports one DDR channel, 64b wide (72b with ECC).

- Supports 200 and 266-MHz DDR compliant devices (845MZ supports 200 MHz DDR only)

- Supports 64-Mb, 128-Mb, 256-Mb and 512-Mb technologies for x16 devices and x8 devices.

- All supported devices have 4 banks

- Configurable optional ECC operation (single bit Error Correction and multiple bit Error Detection)

- Supports up to 16 simultaneous open pages

- Supports page sizes of 2 KB, 4 KB, 8 KB, and 16 KB. Page size is individually selected for every row.

- Thermal throttling scheme to selectively throttle reads and/or writes. Throttling can be triggered by preset read/write bandwidth limits.

- Max of 2 double-sided (4 rows populated) with unbuffered PC2100 DDR (with or without ECC) SO-DIMMs (845MZ supports only 200-MHz DDR).

- Largest memory supported is 1 GB (845MZ supports only up to 512 MB).

- System Interrupts

- Supports only System Bus interrupt delivery mechanism

- Supports interrupts signaled as upstream Memory Writes from AGP/PCI (PCI semantics only) and hub interface

- -MSI direct to the System Bus

- Supports peer MSI between hub interface and AGP

- Provides redirection for IPI and upstream interrupts to the System Bus

- Accelerated Graphics Port (AGP) Interface

- Supports a single AGP device (either a connector or on the motherboard)

- -AGP Support

- Supports AGP 2.0 including 1x, 2x, and 4x AGP data transfers and 2x/4x Fast Write protocol

- Supports only 1.5-V AGP electricals

- -32 deep AGP request queue

- PCI semantic (FRAME# initiated) accesses to DRAM are snooped

- -High priority access support

- -Hierarchical PCI configuration mechanism

- Delayed transaction support for AGP-to-DRAM FRAME# semantic reads that can not be serviced immediately

- 32-bit upstream address support for inbound AGP and PCI cycles

- 32-bit downstream address support for outbound PCI and Fast Write cycles

- -AGP Busy/Stop Protocol

- -AGP Clamping and Sense Amp Control

- Hub Interface to ICH3-M

- -266-MB/s, point-to-point hub interface to ICH3-M

- -66-MHz base clock

- Supports the following traffic types to the ICH3-M

- -Hub interface-to-AGP memory writes

- -Hub interface-to-DRAM

- -CPU-to-hub interface

- -Messaging

- —MSI Interrupt messages

- Power Management state change

- -SMI, SCI and SERR error indication

- Power Management

- --- SMRAM space remapping to A0000h (128 KB)

- Supports extended SMRAM space above 256 MB, additional 128K/256K/512K TSEG from Top of Memory, cacheable (cacheability controlled by CPU)

- APM Rev 1.2 compliant power management

- ACPI 2.0 Support

- Intel SpeedStep™ technology support

- -Cache coherency with CPU in sleep mode

- Dynamic Memory Power-down

- Package

- -Package options

# 1. Overview

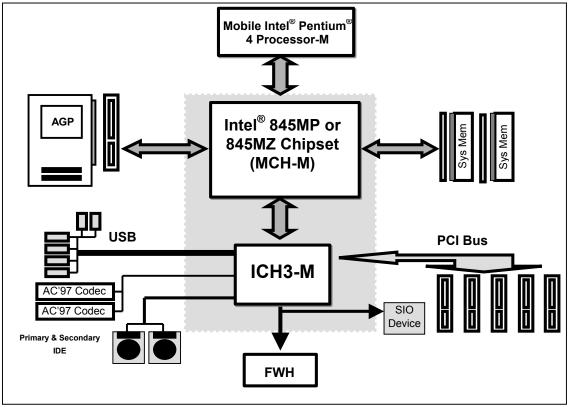

#### Figure 1. Intel<sup>®</sup> 845MP/845MZ Chipset System Block Diagram

The Intel 845MP/845MZ Chipset Memory Controller Hub-M (MCH-M) is designed for use with the Mobile Intel Pentium 4 Processor-M. The Intel 845MP/845MZ Chipset MCH-M manages the flow of information between its four interfaces: the System Bus, the memory interface, the AGP port, and the hub interface. The MCH-M arbitrates between the four interfaces when each initiates an operation. While doing so, the MCH-M must support data coherency via snooping and must perform address translation for access to AGP Aperture memory.

The Intel 845MP/845MZ Chipset Memory Controller Hub-M (MCH-M) may contain design defects or errors known as errata, which may cause the product to deviate from published specifications.

## 1.1. System Architecture

int

The Intel 845MP/845MZ Chipset Memory Controller Hub-M (MCH-M) component provides the processor interface, DRAM interface, AGP interface, and hub interface. The CPU interface supports the Mobile Intel Pentium 4 Processor-M subset of the Extended Mode of the Scalable Bus Protocol. The Intel 845MP/845MZ Chipset is optimized for the Mobile Intel Pentium 4 Processor-M. It supports a single channel of DDR memory. The MCH-M contains advanced power management logic. The Intel 845MP/845MZ Chipset platform supports the third generation mobile I/O Controller Hub (ICH3-M) to provide the features required by a mobile platform.

The Intel 845 Chipset-Mobile Family (MCH-M) is in a 593-pin FC-BGA package and contains the following functionality:

- Supports single Mobile Intel Pentium 4 Processor-M configurations at 400 MT/s

- AGTL+ host bus with integrated termination supporting 32-bit host addressing

- 845MP supports up to 1 GB of PC2100 Memory

- 845MZ supports up to 512 MB of PC1600 Memory

- 1.5-V AGP interface with 4x SBA/PIPE# Data Transfer and Fast Write capability

- 1.8-V, 8-bit, 66-MHz 4x hub interface to ICH3-M

- Deeper Sleep

- Intel SpeedStep<sup>®</sup> technology

- Distributed arbitration for highly concurrent operation

## **1.2.** Mobile Intel Pentium<sup>®</sup> 4 Processor-M Host Interface

The Intel 845MP/845MZ Chipset MCH-M is optimized for the Mobile Intel Pentium 4 Processor-M. The primary enhancements over the Compatible Mode P6 bus protocol are:

- Source synchronous double pumped address

- Source synchronous quad pumped data

- System bus interrupt and side-band signal delivery

In this mode, the MCH-M supports a 64B cache line size. Only one processor is supported at a System bus frequency of 400 MT/s. The MCH-M integrates AGTL+ termination resistors on all of the AGTL+ signals. The MCH-M supports 32-bit host addresses, allowing the CPU to access the entire 4 GB of the MCH-M memory address space.

The MCH-M has a 12-deep In-Order Queue to support up to 12 outstanding pipelined address requests on the host bus. The MCH-M supports two outstanding defer cycles at a time; however, only one to any particular IO interface. Host initiated I/O cycles are positively decoded to AGP/PCI or MCH-M configuration space and subtractively decoded to the hub interface. Host initiated memory cycles are positively decoded to AGP/PCI or MCH-M configuration space and subtractively decoded to the hub interface. Host initiated from AGP/PCI to DRAM are not snooped on the host bus. Memory accesses initiated from AGP/PCI using PCI semantics and from the hub interface to DRAM will be snooped on the System bus. Memory accesses whose

addresses lie within the AGP aperture are translated using the AGP address translation table, regardless of the originating interface.

#### 1.2.1. System Bus Error Checking

The Intel 845MP/845MZ Chipset MCH-M does not generate nor check parity for Data, Address/Request, and Response signals on the processor bus.

## 1.3. System Memory Interface

The Intel 845MP/845MZ Chipset memory controller directly supports one channel of PC1600 or PC2100 (845MZ PC1600 only) SO-DIMM DDR memory. The Intel 845MP/845MZ Chipset memory interface supports DDR devices with densities of 64-Mb, 128-Mb, 256-Mb, and 512-Mb technology. The maximum memory support is two, double-sided SO-DIMMs (four rows populated). The Intel 845MP/845MZ Chipset memory interface also supports variable page sizes of 2 KB, 4 KB, 8 KB, and 16 KB. Page size is individually selected for every row and a maximum of 16 pages may be opened simultaneously.

#### Table 1. DDR Memory Capacity

| Technology | 845MP/845MZ Maximum |

|------------|---------------------|

| 64 Mb      | 128 MB/128 MB       |

| 128 Mb     | 256 MB/256 MB       |

| 256 Mb     | 512 MB/512 MB       |

| 512 Mb     | 1 GB/ 512 MB        |

The memory interface provides optional ECC error checking for DRAM data integrity. During DRAM writes, ECC is generated on a QWORD (64 bit) basis. Because the Intel 845MP/845MZ Chipset MCH-M stores only entire cache lines in its internal buffers, partial QWORD writes initially cause a read of the underlying data, and their write-back into memory is no different from that of a complete cache line. During DRAM reads and the read of the data that underlies partial writes, the MCH-M supports detection of single-bit and multiple-bit errors, and will correct single bit errors when correction is enabled.

| SO-<br>DIMM<br>Capacity | SO-DIMM<br>Organization | Density  | DDR<br>Organization | # of<br>Components | Package<br>Type | # of<br>Physical<br>Banks | # of<br>Banks<br>in DDR | # Address<br>Bits<br>(row/col) |

|-------------------------|-------------------------|----------|---------------------|--------------------|-----------------|---------------------------|-------------------------|--------------------------------|

| 64 MB                   | 8M x 64                 | 64 Mbit  | 4M x 16             | 8                  | 66 lead<br>TSOP | 2                         | 4                       | 12/8                           |

| 64 MB                   | 8M x 64                 | 128 Mbit | 8M x 16             | 4                  | 66 lead<br>TSOP | 1                         | 4                       | 12/9                           |

| 64 MB                   | 8M x 72                 | 128 Mbit | 8M x 16             | 5                  | 66 lead<br>TSOP | 1                         | 4                       | 12/9                           |

| 128 MB                  | 16M x 64                | 128 Mbit | 8M x 16             | 8                  | 66 lead<br>TSOP | 2                         | 4                       | 12/9                           |

| 128 MB                  | 16M x 64                | 256 Mbit | 16M x 16            | 4                  | 66 lead<br>TSOP | 1                         | 4                       | 13/9                           |

| 128 MB                  | 16M x 72                | 256 Mbit | 16M x 16            | 5                  | 66 lead<br>TSOP | 1                         | 4                       | 13/9                           |

| 256 MB                  | 32M x 64                | 256 Mbit | 16M x 16            | 8                  | 66 lead<br>TSOP | 2                         | 4                       | 13/9                           |

| 256 MB                  | 32M x 64                | 512 Mbit | 32M x 16            | 4                  | 66 lead<br>TSOP | 1                         | 4                       | 13/10                          |

| 256 MB                  | 32M x 72                | 512 Mbit | 32M x 16            | 5                  | 66 lead<br>TSOP | 1                         | 4                       | 13/10                          |

| 512 MB                  | 64M x 64                | 512 Mbit | 32M x 16            | 8                  | 66 lead<br>TSOP | 2                         | 4                       | 13/10                          |

| 64 MB                   | 8M x 64                 | 64 Mbit  | 8M x 8              | 8                  | 66 lead<br>TSOP | 1                         | 4                       | 12/9                           |

| 128 MB                  | 16M x 64                | 128 Mbit | 16M x 8             | 8                  | 66 lead<br>TSOP | 1                         | 4                       | 12/10                          |

| 256 MB                  | 32M x 64                | 256 Mbit | 32M x 8             | 8                  | 66 lead<br>TSOP | 1                         | 4                       | 13/10                          |

| 512 MB                  | 64M x 64                | 512 Mbit | 64M x 8             | 8                  | 66 lead<br>TSOP | 1                         | 4                       | 13/11                          |

#### Table 2. DDR Device Configurations

## **1.4. AGP Interface**

A single AGP component or connector (not both) is supported by the Intel 845MP/845MZ Chipset MCH-M AGP interface. The AGP buffers operate only in 1.5-V mode. They are not 3.3-V safe.

The AGP interface supports 1x/2x/4x AGP signaling and 2x/4x Fast Writes. AGP semantic cycles to DRAM are not snooped on the host bus. PCI semantic cycles to DRAM are snooped on the host bus. The MCH-M supports PIPE# or SBA[7:0] AGP address mechanisms, but not both simultaneously. Either the PIPE# or the SBA[7:0] mechanism must be selected during system initialization. Both upstream and downstream addressing is limited to 32 bits for AGP and AGP/PCI transactions. The MCH-M contains a 32-deep AGP request queue. High priority accesses are supported. All accesses from the AGP/PCI interface that fall within the Graphics Aperture address range pass through an address translation mechanism with a fully associative 20 entry TLB. Accesses between AGP and hub interface are limited to memory writes originating from the hub interface destined for AGP. The AGP interface is clocked from a dedicated 66MHz clock (66IN). The AGP-to-host/core interface is asynchronous.

Consult the latest AGP Busy and Stop Protocol Specification for more information.

#### **1.5.** Hub Interface

The 8-bit hub interface connects the MCH-M to the ICH3-M. All communication between the MCH-M and the ICH3-M occurs over the hub interface. The hub interface runs at 66 MHz/266 MB/s. Aside from the obvious traffic types, the following communication also occur over hub interface:

- Interrupt related messages

- Power management events as messages

- SMI, SCI, and SERR error indication messages

It is assumed that the hub interface is always connected to an ICH3-M. This is a proprietary interconnect between the MCH-M and the ICH3-M.

## 1.6. MCH-M Clocking

The MCH-M has the following clock input pins:

- Differential BCLK[1:0] for the host interface

- 66-MHz clock input for the AGP and hub interface

Clock Synthesizer chip(s) are responsible for generating the system Host clocks, AGP and hub interface clocks, PCI clocks, and DRAM clocks. The Host target speed is 400 MT/s. The MCH-M does not require any relationship between the HCLKIN host clock and the 66-MHz clock generated for AGP and hub interface; they are totally asynchronous from each other. The AGP and hub interface runs at a constant 66-MHz base frequency. The hub interface runs at 4x, while AGP transfers may be 1x, 2x, or 4x.

The following tables indicate the frequency ratios between the various interfaces that the MCH-M supports.

#### Table 3. MCH-M Clock Ratio Table

| Interface     | Speed       | CPU System Bus Frequency Ratio |

|---------------|-------------|--------------------------------|

| System Memory | DDR 200 MHz | 1:1 synchronous                |

| AGP           | 66 MHz      | Asynchronous                   |

| Hub interface | 66 MHz      | Asynchronous                   |

## **1.7. System Interrupts**

The Intel 845MP/845MZ Chipset MCH-M supports both 8259 and Intel Mobile Pentium 4 Processor-M interrupt delivery mechanisms. The serial APIC interrupt mechanism is not supported.

The 8259 support consists of flushing inbound hub interface write buffers when an Interrupt Acknowledge cycle is forwarded from the system bus to the hub interface.

The Intel 845MP/845MZ Chipset MCH-M supports the Mobile Intel Pentium 4 Processor-M interrupt delivery mechanism. PCI MSI interrupts are generated as Memory Writes. The MCH-M decodes upstream Memory Writes to the range 0FEE0\_0000h - 0FEEF\_FFFh from AGP and the hub interface as message based interrupts. The MCH-M forwards the Memory Writes, along with the associated write data, to the system bus as an Interrupt Message transaction. Note that since this address does not decode as part of main memory, the write cycle and the write data does not get forwarded to DRAM via the write buffer. The Intel 845MP/845MZ Chipset MCH-M provides the response and TRDY# for all Interrupt Message cycles including the ones originating from the MCH-M. The Intel 845MP/845MZ Chipset MCH-M supports interrupt re-direction for inter-processor interrupts (IPIs) as well as upstream interrupt memory writes.

For message based interrupts, system write buffer coherency is maintained by relying on strict ordering of Memory Writes. The Intel 845MP/845MZ Chipset MCH-M ensures that all Memory Writes received from a given interface prior to an interrupt message Memory Write are delivered to the system bus for snooping in the same order that they occur on the given interface.

# 2. Signal Description

This section provides a detailed description of Intel 845MP/845MZ Chipset MCH-M signals. The signals are arranged in functional groups according to their associated interface. The states of all of the signals during reset are provided in the System Reset section.

The "#" symbol at the end of a signal name indicates that the active, or asserted state occurs when the signal is at a low voltage level. When "#" is not present after the signal name, the signal is asserted when at the high voltage level.

The following notations are used to describe the signal type:

| Ι                                                                                       | Input pin                                                                                                                                                                              |  |  |

|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0                                                                                       | Output pin                                                                                                                                                                             |  |  |

| I/O                                                                                     | Bi-directional Input/Output pin                                                                                                                                                        |  |  |

| s/t/s                                                                                   | Sustained Tristate. This pin is driven to its inactive state prior to tri-stating.                                                                                                     |  |  |

| as/t/s                                                                                  | Active Sustained Tristate. This applies to some of the hub interface signals. This pin is weakly driven to its last driven value.                                                      |  |  |

| The signal description also includes the type of buffer used for the particular signal: |                                                                                                                                                                                        |  |  |

| AGTL+                                                                                   | Open Drain AGTL+ interface signal. Refer to the AGTL+ I/O Specification for complete details. The Intel <sup>®</sup> 845MP/845MZ Chipset MCH-M integrates AGTL+ termination resistors. |  |  |

| AGP                                                                                     | AGP interface signals. These signals are compatible with AGP 2.0 1.5v Signaling Environment DC and AC Specifications. The buffers are not 3.3v tolerant.                               |  |  |

| CMOS                                                                                    | CMOS buffers.                                                                                                                                                                          |  |  |

| Ref                                                                                     | Voltage reference signal.                                                                                                                                                              |  |  |

*Note:* System address and data bus signals are logically inverted signals. The actual values are inverted of what appears on the system bus. This must be taken into account and the addresses and data bus signals must be inverted inside the Intel 845MP/845MZ Chipset MCH-M. All processor control signals follow normal convention. A "0" indicates an active level (low voltage) if the signal is followed by "#" symbol, and a "1" indicates an active level (high voltage) if the signal has no "#" suffix.

## 2.1. Host Interface Signals

#### Table 4. Host Interface Signal Descriptions

| Signal Name  | Туре            | Description                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADS#         | I/O<br>AGTL+    | Address Strobe: The system bus owner asserts ADS# to indicate the first of two cycles of a request phase.                                                                                                                                                                                                                                                                                                                |

| BNR#         | I/O<br>AGTL+    | <b>Block Next Request:</b> Used to block the current request bus owner from issuing a new request. This signal is used to dynamically control the system bus pipeline depth.                                                                                                                                                                                                                                             |

| BPRI#        | O<br>AGTL+      | <b>Bus Priority Request:</b> The MCH-M is the only Priority Agent on the system bus. It asserts this signal to obtain the ownership of the address bus. This signal has priority over symmetric bus requests and will cause the current symmetric owner to stop issuing new transactions unless the <b>HLOCK#</b> signal was asserted.                                                                                   |

| BR0#         | I/O<br>AGTL+    | <b>Bus Request 0#:</b> The MCH-M pulls the processor bus' <b>BR0#</b> signal low during <b>CPURST#</b> . The signal is sampled by the processor on the active-to-inactive transition of <b>CPURST#</b> . The minimum setup time for this signal is 4 HCLKs. The minimum hold time is 2 clocks and the maximum hold time is 20 HCLKs. <b>BR0#</b> should be tristated after the hold time requirement has been satisfied. |

| CPURST#      | O<br>AGTL+      | <b>CPU Reset:</b> The <b>CPURST#</b> pin is an output from the MCH-M. The MCH-M asserts <b>CPURST#</b> while <b>RSTIN#</b> (PCIRST# from ICH3-M) is asserted and for approximately 1 ms after <b>RSTIN#</b> is deasserted. The <b>CPURST#</b> allows the processor's to begin execution in a known state.                                                                                                                |

| DBSY#        | I/O<br>AGTL+    | <b>Data Bus Busy:</b> Used by the data bus owner to hold the data bus for transfers requiring more than one cycle.                                                                                                                                                                                                                                                                                                       |

| DEFER#       | O<br>AGTL+      | <b>Defer Response:</b> Signals that the MCH-M will terminate the transaction currently being snooped with either a deferred response or with a retry response.                                                                                                                                                                                                                                                           |

| DBI[3:0]#    | I/O<br>AGTL+ 4x | <b>Dynamic Bus Inversion:</b> Driven along with the <b>HD[63:0]#</b> signals. Indicates if the associated signals are inverted or not. <b>DBI[3:0]#</b> are asserted such that the number of data bits driven electrically low (low voltage) within the corresponding 16-bit group never exceeds 8.                                                                                                                      |

|              |                 | DBI[x]#         Data Bits           DBI3#         HD[63:48]#           DBI2#         HD[47:32]#           DBI1#         HD[31:16]#           DBI0#         HD[15:0]#                                                                                                                                                                                                                                                     |

| DRDY#        | I/O<br>AGTL+    | Data Ready: Asserted for each cycle that data is transferred.                                                                                                                                                                                                                                                                                                                                                            |

| HA[31:3]#    | I/O<br>AGTL+ 2x | Host Address Bus: HA[31:3]# connect to the system address bus. During processor cycles the HA[31:3]# are inputs. The MCH-M drives HA[31:3]# during snoop cycles on behalf of hub interface and AGP/Secondary PCI initiators. HA[31:3]# are transferred at 2x rate. Note that the address is inverted on the system bus.                                                                                                  |

| HADSTB[1:0]# | l/O<br>AGTL+ 2x | Host Address Strobe: The source synchronous strobes used to transfer HA[31:3]# and HREQ[4:0]# at the 2x transfer rate.                                                                                                                                                                                                                                                                                                   |

|              |                 | StrobeAddress BitsHADSTB0#HA[16:3]#, HREQ[4:0]#HADSTB1#HA[31:17]#                                                                                                                                                                                                                                                                                                                                                        |

250687-002

| Signal Name                  | Туре            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HD[63:0]#                    | I/O<br>AGTL+ 4x | <b>Host Data:</b> These signals are connected to the system data bus. <b>HD[63:0]#</b> are transferred at 4x rate. Note that the data signals are inverted on the system bus.                                                                                                                                                                                                                                                                       |

| HDSTBP[3:0]#<br>HDSTBN[3:0]# | I/O<br>AGTL+ 4x | Differential Host Data Strobes: The differential source synchronous strobes used to transfer HD[63:0]# and DBI[3:0]# at the 4x transfer rate.         Strobe       Data Bits                                                                                                                                                                                                                                                                        |

|                              |                 | HDSTBP3#, HDSTBN3#       HD[63:48]#, DBI3#         HDSTBP2#, HDSTBN2#       HD[47:32]#, DBI2#         HDSTBP1#, HDSTBN1#       HD[31:16]#, DBI1#         HDSTBP0#, HDSTBN0#       HD[15:0]#, DBI0#                                                                                                                                                                                                                                                  |

| HIT#                         | I/O<br>AGTL+    | <b>Hit:</b> Indicates that a caching agent holds an unmodified version of the requested line. Also, driven in conjunction with <b>HITM#</b> by the target to extend the snoop window.                                                                                                                                                                                                                                                               |

| HITM#                        | I/O<br>AGTL+    | <b>Hit Modified:</b> Indicates that a caching agent holds a modified version of the requested line and that this agent assumes responsibility for providing the line. Also, driven in conjunction with <b>HIT#</b> to extend the snoop window.                                                                                                                                                                                                      |

| HLOCK#                       | l<br>AGTL+      | Host Lock: All system bus cycles sampled with the assertion of HLOCK# and ADS#, until the negation of HLOCK# must be atomic, i.e. no hub interface or AGP snoopable access to DRAM are allowed when HLOCK# is asserted by the processor.                                                                                                                                                                                                            |

| HREQ[4:0]#                   | I/O<br>AGTL+ 2x | <b>Host Request Command:</b> Defines the attributes of the request. In Enhanced Mode <b>HREQ[4:0]#</b> are transferred at 2x rate. Asserted by the requesting agent during both halves of Request Phase. In the first half the signals define the transaction type to a level of detail that is sufficient to begin a snoop request. In the second half the signals carry additional information to define the complete transaction type.           |

|                              |                 | The transactions supported by the MCH-M Host Bridge are defined in the Host Interface section of this document.                                                                                                                                                                                                                                                                                                                                     |

| HTRDY#                       | O<br>AGTL+      | <b>Host Target Ready:</b> Indicates that the target of the processor transaction is able to enter the data transfer phase.                                                                                                                                                                                                                                                                                                                          |

| RS[2:0]#                     | O<br>AGTL+      | Response Status:       Indicates type of response according to the following the table:         RS[2:0]       Response type         000       Idle state         001       Retry response         010       Deferred response         011       Reserved (not driven by MCH-M)         100       Hard Failure (not driven by MCH-M)         101       No data response         110       Implicit Write back         111       Normal data response |

## 2.2. DDR Interface

#### Table 5. DDR Interface Signal Descriptions

| Signal Name | Туре           | Description                                                                                                                                                                                                                                                                                |

|-------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCS#[3:0]   | O<br>CMOS      | <b>Chip Select:</b> These pins select the particular DDR components during the active state.                                                                                                                                                                                               |

|             |                | <b>Note:</b> There is one SCS# per DDR-SDRAM Physical SO-DIMM device row. These signals can be toggled on every rising System Memory Clock edge.                                                                                                                                           |