## INTEGRATED CIRCUITS

Objective specification File under Integrated Circuits, IC02 June 1994

# **Philips Semiconductors**

**SAA5233**

### **Dual standard PDC decoder**

### FEATURES

- Digital data slicer

- Acquisition and decoding of VPS data (EBU PDC System A)

- Acquisition and decoding of Teletext packet 8/30/2 data (EBU PDC System B)

- Separate storage of VPS data and packet 8/30/2 allowing dual standard PDC decoders

- I<sup>2</sup>C-bus interface with automatic word address increment

- Programmable interrupt for data received

- Programmable error level detection

- Single +5 V power supply.

#### **GENERAL DESCRIPTION**

The SAA5233 is a dual standard Program Delivery Control (PDC) decoder, allowing the reception and decoding of both VPS data (EBU PDC System A) and Teletext packet 8/30/2 data (EBU PDC System B). It is intended for use in European video recorders which are manually programmed, so that they receive broadcast real time switching signals for accurate timing of program recording.

### QUICK REFERENCE DATA

| SYMBOL                | PARAMETER                                            | MIN. | TYP. | MAX. | UNIT |

|-----------------------|------------------------------------------------------|------|------|------|------|

| V <sub>DD</sub>       | supply voltage                                       | 4.5  | 5.0  | 5.5  | V    |

| I <sub>DD</sub>       | supply current                                       | _    | 30   | 45   | mA   |

| f <sub>clk</sub>      | crystal input frequency                              | -    | 27   | -    | MHz  |

| V <sub>sync</sub>     | CVBS sync voltage amplitude                          | 0.1  | 0.3  | 0.6  | V    |

| V <sub>vid(p-p)</sub> | CVBS video voltage amplitude<br>(peak-to-peak value) | 0.7  | 1.0  | 1.4  | V    |

| T <sub>amb</sub>      | operating ambient temperature                        | -20  | -    | +70  | °C   |

| T <sub>stg</sub>      | storage temperature                                  | -55  | -    | +125 | °C   |

### **ORDERING INFORMATION**

| TYPE NUMBER | PACKAGE |              |          |          |  |

|-------------|---------|--------------|----------|----------|--|

|             | PINS    | PIN POSITION | MATERIAL | CODE     |  |

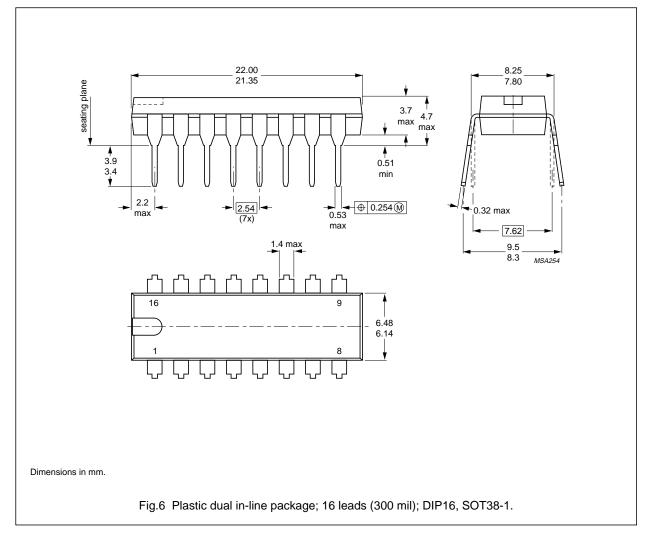

| SAA5233P    | 16      | DIP16        | plastic  | SOT38-1  |  |

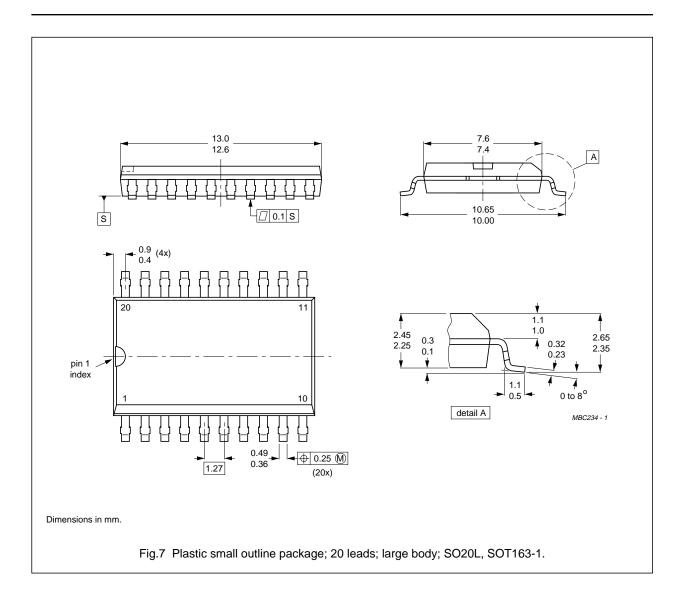

| SAA5233T    | 20      | SO20L        | plastic  | SOT163-1 |  |

## SAA5233

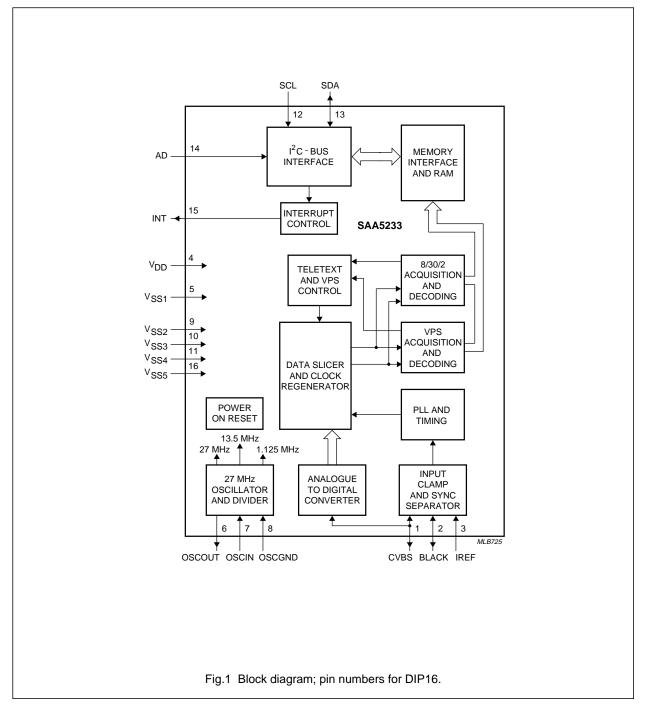

### **BLOCK DIAGRAM**

## SAA5233

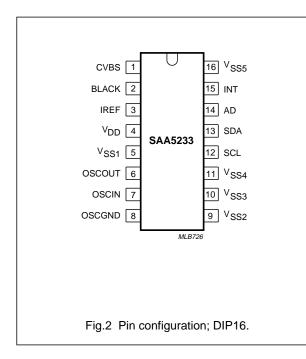

### PINNING

|                  |             | PIN | DECODIDITION                                                 |

|------------------|-------------|-----|--------------------------------------------------------------|

| SYMBOL           | DIP16 SO20L |     | - DESCRIPTION                                                |

| CVBS             | 1           | 1   | composite video input                                        |

| BLACK            | 2           | 2   | video black level storage pin                                |

| n.c.             | -           | 3   | not connected                                                |

| IREF             | 3           | 4   | reference current input                                      |

| V <sub>DD</sub>  | 4           | 5   | +5 V supply                                                  |

| V <sub>SS1</sub> | 5           | 6   | 0 V ground 1 (main ground pin)                               |

| OSCOUT           | 6           | 7   | 27 MHz crystal oscillator output                             |

| n.c.             | -           | 8   | not connected                                                |

| OSCIN            | 7           | 9   | 27 MHz crystal oscillator input                              |

| OSCGND           | 8           | 10  | 27 MHz crystal oscillator ground                             |

| V <sub>SS2</sub> | 9           | 11  | 0 V ground 2; connect to V <sub>SS1</sub>                    |

| V <sub>SS3</sub> | 10          | 12  | 0 V ground 3; connect to V <sub>SS1</sub>                    |

| n.c.             | -           | 13  | not connected                                                |

| V <sub>SS4</sub> | 11          | 14  | connect to V <sub>SS1</sub> in normal operation              |

| SCL              | 12          | 15  | serial clock open-drain input for I <sup>2</sup> C-bus       |

| SDA              | 13          | 16  | serial data open-drain input/output for I <sup>2</sup> C-bus |

| i.c.             | -           | 17  | internally connected; do not connect in normal operation     |

| AD               | 14          | 18  | programmable I <sup>2</sup> C-bus address bit input          |

| INT              | 15          | 19  | interrupt open-drain output                                  |

| V <sub>SS5</sub> | 16          | 20  | connect to V <sub>SS1</sub> in normal operation              |

CVBS 1

BLACK 2

n.c. 3

IREF 4

V<sub>DD</sub> 5

V<sub>SS1</sub> 6

n.c. 8

OSCIN 9

OSCGND 10

OSCOUT 7

SAA5233

20 V<sub>SS5</sub>

19 INT

18 AD

17 i.c.

16 SDA

15 SCL

14 V<sub>SS4</sub>

13 n.c.

12 V<sub>SS3</sub>

11 VSS2

MLB727

Fig.3 Pin configuration; SO20L.

June 1994

## SAA5233

### LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134).

| SYMBOL             | PARAMETER                                | MIN. | MAX.                  | UNIT |

|--------------------|------------------------------------------|------|-----------------------|------|

| V <sub>DD</sub>    | supply voltage                           | -0.3 | +6.5                  | V    |

| V <sub>Imax</sub>  | maximum input voltage (any input)        | -0.3 | V <sub>DD</sub> + 0.3 | V    |

| V <sub>Omax</sub>  | maximum output voltage (any output)      | -0.3 | V <sub>DD</sub> + 0.3 | V    |

| I <sub>IOmax</sub> | maximum DC input or output diode current | -    | ±20                   | mA   |

| I <sub>Omax</sub>  | maximum output current (any output)      | -    | ±10                   | mA   |

| T <sub>amb</sub>   | operating ambient temperature            | -20  | +70                   | °C   |

| T <sub>stg</sub>   | storage temperature                      | -55  | +125                  | °C   |

SAA5233

### QUALITY AND RELIABILITY

This device will meet the requirements of the "Philips Semiconductors General Quality Specification SNW-FQ-611E" in accordance with "Quality Reference Pocketbook (order number 9398 510 34011)". The principal requirements are as shown in Tables 1 to 4.

#### Group A

Table 1

Acceptance tests per lot.

| TEST       | REQUIREMENTS <sup>(1)</sup> |

|------------|-----------------------------|

| Mechanical | cumulative target: <100 ppm |

| Electrical | cumulative target: <100 ppm |

### Group B

Table 2

Processability tests (by package family).

| TEST                   | REQUIREMENTS <sup>(1)</sup> |

|------------------------|-----------------------------|

| Solderability          | <7% LTPD                    |

| Mechanical             | <15% LTPD                   |

| Solder heat resistance | <15% LTPD                   |

### Group C

Table 3 Reliability tests (by process family).

| TEST                            | CONDITIONS                                                                       | REQUIREMENTS <sup>(1)</sup>                                  |

|---------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------|

| Operational life                | 168 hours at T <sub>j</sub> = 150 °C                                             | <1500 FPM; equivalent to <100 FITS at T <sub>j</sub> = 70 °C |

| Humidity life                   | temperature, humidity, bias<br>(1000 hours, 85 °C, 85% RH or<br>equivalent test) | <2000 FPM                                                    |

| Temperature cycling performance | T <sub>stg(min)</sub> to T <sub>stg(max)</sub>                                   | <2000 FPM                                                    |

#### Table 4 Reliability tests (by device type).

| TEST             | CONDITIONS                                              | REQUIREMENTS <sup>(1)</sup> |

|------------------|---------------------------------------------------------|-----------------------------|

| ESD and latch-up | ESD Human body model<br>2000 V; 100 pF; 1.5 kΩ          | <15% LTPD                   |

|                  | ESD Machine model<br>200 V; 200 pF; 0 Ω                 | <15% LTPD                   |

|                  | latch-up 100 mA; $1.5 \times V_{DD}$ (absolute maximum) | <15% LTPD                   |

### Note to Tables 1 to 4.

1. ppm = fraction of defective devices, in parts per million.

LTPD = Lot Tolerance Percent Defective.

FPM = fraction of devices failing at test condition, in Failures Per Million.

FITS = Failures In Time Standard.

## SAA5233

### CHARACTERISTICS

$V_{DD}$  = 4.5 to 5.5 V;  $V_{SS}$  = 0 V;  $T_{amb}$  = –20 to +70  $^\circ C$ ; unless otherwise specified.

| SYMBOL                 | PARAMETER                                       | CONDITIONS                 | MIN.               | TYP.               | MAX.                  | UNIT |

|------------------------|-------------------------------------------------|----------------------------|--------------------|--------------------|-----------------------|------|

| Supplies               |                                                 |                            |                    |                    |                       | •    |

| V <sub>DD</sub>        | supply voltage                                  |                            | 4.5                | 5.0                | 5.5                   | V    |

| I <sub>DD</sub>        | supply current                                  |                            | -                  | 30                 | 45                    | mA   |

| Inputs                 |                                                 |                            |                    |                    |                       |      |

| CVBS                   |                                                 |                            |                    |                    |                       |      |

| V <sub>sync</sub>      | sync voltage amplitude                          |                            | 0.1                | 0.3                | 0.6                   | V    |

| V <sub>vid(p-p)</sub>  | video voltage amplitude<br>(peak-to-peak value) |                            | 0.7                | 1.0                | 1.4                   | V    |

| V <sub>dat(text)</sub> | Teletext data voltage amplitude                 |                            | 0.30               | 0.46               | 0.70                  | V    |

| V <sub>dat(vps)</sub>  | VPS data voltage amplitude                      |                            | 0.30               | 0.50               | 0.70                  | V    |

| Z <sub>source</sub>    | source impedance                                |                            | -                  | -                  | 250                   | Ω    |

| ZI                     | input impedance                                 |                            | 2.5                | 5.0                | -                     | kΩ   |

| CI                     | input capacitance                               |                            | -                  | -                  | 10                    | pF   |

| IREF                   |                                                 |                            |                    |                    |                       |      |

| R <sub>gnd</sub>       | resistor to ground                              |                            | -                  | 27                 | -                     | kΩ   |

| VIREF                  | input reference voltage                         |                            | -                  | 0.5V <sub>DD</sub> | -                     | V    |

| AD                     |                                                 |                            |                    |                    |                       |      |

| VIL                    | LOW level input voltage                         |                            | -0.3               | -                  | +0.3V <sub>DD</sub>   | V    |

| V <sub>IH</sub>        | HIGH level input voltage                        |                            | 0.7V <sub>DD</sub> | -                  | V <sub>DD</sub> + 0.3 | V    |

| I <sub>LI</sub>        | input leakage current                           | $V_{I} = 0$ to $V_{DD}$    | -10                | -                  | +10                   | μA   |

| CI                     | input capacitance                               |                            | -                  | -                  | 10                    | pF   |

| SCL                    |                                                 |                            |                    |                    |                       |      |

| VIL                    | LOW level input voltage                         |                            | -0.3               | -                  | +0.3V <sub>DD</sub>   | V    |

| V <sub>IH</sub>        | HIGH level input voltage                        |                            | 0.7V <sub>DD</sub> | -                  | V <sub>DD</sub> + 0.3 | V    |

| I <sub>LI</sub>        | input leakage current                           | $V_{I} = 0$ to $V_{DD}$    | -10                | -                  | +10                   | μA   |

| Cl                     | input capacitance                               |                            | -                  | -                  | 10                    | pF   |

| f <sub>clk</sub>       | clock frequency                                 |                            | 0                  | -                  | 100                   | kHz  |

| t <sub>r</sub>         | input rise time                                 | $0.3V_{DD}$ to $0.7V_{DD}$ | -                  | -                  | 1000                  | ns   |

| t <sub>f</sub>         | input fall time                                 | $0.7V_{DD}$ to $0.3V_{DD}$ | -                  | -                  | 300                   | ns   |

## SAA5233

| SYMBOL             | PARAMETER                                            | CONDITIONS                                                            | MIN.               | TYP. | MAX.                  | UNIT |

|--------------------|------------------------------------------------------|-----------------------------------------------------------------------|--------------------|------|-----------------------|------|

| Outputs            | 1                                                    | ł                                                                     | ł                  |      |                       |      |

| INT (OPEN-I        | DRAIN OUTPUT)                                        |                                                                       |                    |      |                       |      |

| V <sub>PU</sub>    | pull-up voltage at pin                               |                                                                       | -                  | -    | V <sub>DD</sub>       |      |

| V <sub>OL</sub>    | LOW level output voltage                             | I <sub>OL</sub> = 3 mA                                                | 0                  | -    | 0.4                   | V    |

| I <sub>OL</sub>    | LOW level output current                             |                                                                       | -                  | -    | 4.0                   | mA   |

| CL                 | load capacitance                                     |                                                                       | -                  | -    | 400                   | pF   |

| t <sub>f</sub>     | output fall time                                     | C <sub>L</sub> = 100 pF;<br>0.7V <sub>DD</sub> to 0.3V <sub>DD</sub>  | -                  | -    | 100                   | ns   |

| Inputs/Out         | puts                                                 | •                                                                     |                    | ·    | •                     | •    |

| BLACK              |                                                      |                                                                       |                    |      |                       |      |

| C <sub>black</sub> | storage capacitor to ground                          |                                                                       | -                  | 100  | -                     | nF   |

| ILI                | input leakage current                                | $V_{I} = 0$ to $V_{DD}$                                               | -10                | -    | +10                   | μA   |

| SDA (OPEN          | -DRAIN OUTPUT)                                       | I                                                                     |                    |      |                       |      |

| V <sub>IL</sub>    | LOW level input voltage                              |                                                                       | -0.3               | -    | +0.3V <sub>DD</sub>   | V    |

| V <sub>IH</sub>    | HIGH level input voltage                             |                                                                       | 0.7V <sub>DD</sub> | -    | V <sub>DD</sub> + 0.3 | V    |

| I <sub>LI</sub>    | input leakage current                                | $V_{I} = 0$ to $V_{DD}$                                               | -10                | -    | +10                   | μA   |

| CI                 | input capacitance                                    |                                                                       | -                  | -    | 10                    | pF   |

| CL                 | load capacitance                                     |                                                                       | -                  | -    | 400                   | pF   |

| t <sub>r</sub>     | input rise time                                      | $0.3V_{DD}$ to $0.7V_{DD}$                                            | -                  | -    | 1000                  | ns   |

| t <sub>f</sub>     | input fall time                                      | $0.7V_{DD}$ to $0.3V_{DD}$                                            | -                  | -    | 300                   | ns   |

| V <sub>OL</sub>    | LOW level output voltage                             | I <sub>OL</sub> = 3 mA                                                | 0                  | -    | 0.4                   | V    |

| t <sub>f</sub>     | output fall time                                     | $C_{L} = 400 \text{ pF};$<br>0.7V <sub>DD</sub> to 0.3V <sub>DD</sub> | -                  | -    | 200                   | ns   |

| CRYSTAL OS         | CILLATOR (OSCIN; OSCOUT)                             | •                                                                     |                    |      |                       | •    |

| V <sub>osc</sub>   | oscillator voltage amplitude<br>(peak-to-peak value) |                                                                       | -                  | 1.0  | -                     | V    |

| G <sub>v</sub>     | small signal voltage gain                            |                                                                       | -                  | 1.0  | -                     |      |

| CI                 | input capacitance                                    |                                                                       | -                  | -    | 10                    | pF   |

| C <sub>fb</sub>    | feedback capacitance                                 |                                                                       | -                  | 1    | -                     | pF   |

## SAA5233

| SYMBOL                   | PARAMETER                              | CONDITIONS                 | MIN. | TYP. | MAX.  | UNIT |

|--------------------------|----------------------------------------|----------------------------|------|------|-------|------|

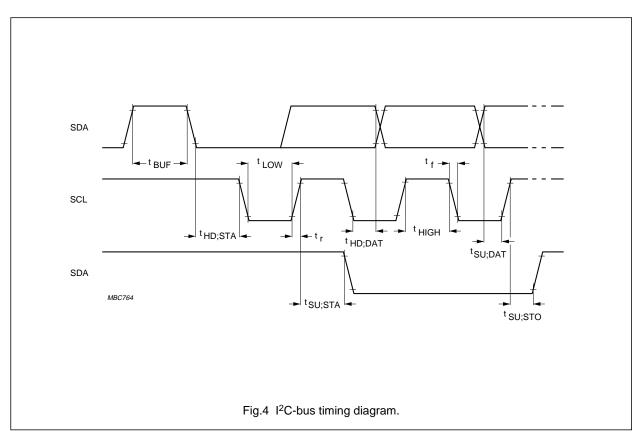

| I <sup>2</sup> C-bus tim | ning (see Fig.4)                       | •                          |      |      |       |      |

| f <sub>clk</sub>         | SCL clock frequency                    |                            | 0    | -    | 100   | kHz  |

| t <sub>BUF</sub>         | bus free time between a STOP and START |                            | 4.7  | -    | -     | μs   |

| t <sub>HD;STA</sub>      | repeated START hold time               | note 1                     | 4.0  | -    | -     | μs   |

| t <sub>LOW</sub>         | SCL clock LOW time                     |                            | 4.7  | -    | -     | μs   |

| t <sub>HIGH</sub>        | SCL clock HIGH time                    |                            | 4.0  | -    | -     | μs   |

| t <sub>SU;STA</sub>      | set-up time for a repeated START       |                            | 4.7  | -    | -     | μs   |

| t <sub>HD;DAT</sub>      | data hold time                         |                            | 0    | -    | -     | ns   |

| t <sub>SU;DAT</sub>      | data set-up time                       |                            | 250  | -    | -     | ns   |

| t <sub>r</sub>           | SDA, SCL input rise time               | $0.3V_{DD}$ to $0.7V_{DD}$ | -    | -    | 1 000 | ns   |

| t <sub>f</sub>           | SDA, SCL input fall time               | $0.7V_{DD}$ to $0.3V_{DD}$ | -    | -    | 300   | ns   |

| t <sub>su;sто</sub>      | set-up time for STOP                   |                            | 4.0  | -    | _     | μs   |

### Note

1. After this time the first clock pulse is generated.

## SAA5233

### FUNCTIONAL DESCRIPTION

#### **Control of device**

The function of the device is controlled via the  $I^2$ C-bus. Pin AD provides a choice of two alternative addresses.

The PDC acquisition section requires little software control apart from enabling the interrupts which occur when data is found. Interrupts can be enabled for either Teletext packet 8/30/2 or VPS and both can be enabled to allow for the presence of both standards being transmitted on the same TV channel. The interrupt register is accessed as address 01 WRITE, see Section "Register 01: Interrupt (reset state X00X XXXX)".

When an interrupt is signalled, a bit is set in the status register to indicate its source. Information about the received PDC data is given in the status register D5 and D6. The microcontroller must service the 'data received' interrupts within 40 ms (VPS) or 200 ms (Teletext packet 8/30/2), since new data may be written after this period. The status register is accessed as address 00 READ; see Section

"Register 00:Control/Status (reset state XXX0 XX00)". When the status register has been read the data received flags and interrupt signal are reset.

Data of both types is constantly received and stored, but can be selectively acquired by setting bits D1 and D0 of the control register. This allows acquisition of only Teletext packet 8/30/2 on every VBI line or only VPS data on every VBI line. The control register is accessed as address 00 WRITE, see Section "Register 00:Control/Status (reset state XXX0 XX00)".

#### Storage of PDC data

The PDC data memory is accessed at address 02 (HEX) to 31 (HEX). The exact addresses of Teletext packet 8/30/2 and VPS data is shown in Table 5.

#### TELETEXT DATA

The Teletext packet 8/30/2 data is stored after hardware Hamming correction. There are 4 data bits stored in the lower nibble of each byte in address 11 (HEX) to 1D (HEX); see Table 13, in the order shown in Table 5. The status message, which is odd parity coded, is stored as a byte which represents a Teletext character in address 1E (HEX) to 31 (HEX); see Table 14.

#### VPS DATA

The VPS data from Line 16 is stored in register address 02 (HEX) to 0F (HEX) in the order shown in Table 5. VPS

data is biphase decoded and stored with 4 data bits stored in the lower nibble of each byte, in the same way as Teletext packet 8/30/2 data; see Tables 11 and 12. In addition to the VCR data, Word 4 (Program Source Identification, ASCII sequential) is stored, which may be useful for future applications.

The stored data is read via the I<sup>2</sup>C-bus in the normal way. Multiple reception/majority error correction of the data is the responsibility of the control software, the device simply stores the data as transmitted after Hamming or biphase decoding. As both VPS and Teletext packet 8/30/2 signals are stored separately, it is possible to deal with future situations where both EBU PDC System A and EBU PDC System B transmissions may be present on the same TV channel, the defaults and level of service being chosen by the software control.

#### Error indication

Indication of errors in the received data is given in two ways and is programmable by setting bit D4 in the control register.

The first is a flag to indicate Hamming or biphase errors and is stored with the related data in bit 0 of the upper nibble of the data byte.

The second is no interrupt which is sent to the microcontroller but the data signal quality bit (D7) is set.

The level of interrupt is controlled by the Interrupt Error Level bit which is D4 of the control register. If this bit is not set then an interrupt only occurs if an error free line of either Teletext packet 8/30/2 or VPS data is received and stored in RAM. If this bit is set then an interrupt occurs if the correct framing code and Teletext packet header 8/30/2 is found, or the correct start code for VPS data is found. The data is then stored in the RAM with any errors indicated in the upper nibble. This may be used by more sophisticated software, which could decide the importance of an error in a particular nibble.

#### I<sup>2</sup>C-bus interface

FEATURES

- Standard I<sup>2</sup>C-bus slave transceiver

- Operates from 0 to 100 kHz

- Acknowledge function is performed

- Auto-increment between registers and direct addressing

- Selectable I<sup>2</sup>C-bus slave address dependent on address pin AD.

### SAA5233

### Register map

The data received when address locations 00 (HEX) to 31 (HEX) are read or written is shown in Table 5.

### Table 5 Register map.

| ADDRESS (HEX) | DATA <sup>(1)</sup> | ADDRESSING                   |

|---------------|---------------------|------------------------------|

| 00            | control/status      | direct                       |

| 01            | interrupt           | direct                       |

| 02            | VPS B5              | direct/auto-increments to 03 |

| 03            | VPS B5              | direct/auto-increments to 04 |

| 04            | VPS B11             | direct/auto-increments to 05 |

| 05            | VPS B11             | direct/auto-increments to 06 |

| 06            | VPS B12             | direct/auto-increments to 07 |

| 07            | VPS B12             | direct/auto-increments to 08 |

| 08            | VPS B13             | direct/auto-increments to 09 |

| 09            | VPS B13             | direct/auto-increments to 0A |

| 0A            | VPS B14             | direct/auto-increments to 0B |

| 0B            | VPS B14             | direct/auto-increments to 0C |

| 0C            | VPS B15             | direct/auto-increments to 0D |

| 0D            | VPS B15             | direct/auto-increments to 0E |

| 0E            | VPS B4              | direct/auto-increments to 0F |

| 0F            | VPS B4              | stop value                   |

| 10            | _                   | direct                       |

| 11            | 8/30/2 B13          | direct/auto-increments to 12 |

| 12            | 8/30/2 B14          | direct/auto-increments to 13 |

| 13            | 8/30/2 B15          | direct/auto-increments to 14 |

| 14            | 8/30/2 B16          | direct/auto-increments to 15 |

| 15            | 8/30/2 B17          | direct/auto-increments to 16 |

| 16            | 8/30/2 B18          | direct/auto-increments to 17 |

| 17            | 8/30/2 B19          | direct/auto-increments to 18 |

| 18            | 8/30/2 B20          | direct/auto-increments to 19 |

| 19            | 8/30/2 B21          | direct/auto-increments to 1A |

| 1A            | 8/30/2 B22          | direct/auto-increments to 1B |

| 1B            | 8/30/2 B23          | direct/auto-increments to 1C |

| 1C            | 8/30/2 B24          | direct/auto-increments to 1D |

| 1D            | 8/30/2 B25          | direct/auto-increments to 1E |

| 1E            | status message      | direct/auto-increments to 1F |

| :             | :                   | direct/auto-increments       |

| 31            | status message      | stop value                   |

#### Note

1. For the address range 02H to 0FH, even addresses hold the least significant nibble and odd addresses hold the most significant nibble. BXX refers to byte definitions, EBU specification of the domestic video PDC system.

SAA5233

### Register 00:Control/Status (reset state XXX0 XX00)

Register 00 is split into two parts. The control part (WRITE only) consisting of bits D4, D1 and D0 and status part (READ only) consisting of bits D7 to D5.

### Table 6Register 00.

| D7  | D6        | D5     | D4  | D3 | D2 | D1         | D0      |

|-----|-----------|--------|-----|----|----|------------|---------|

| _   | —         | -      | IEL | —  | -  | ACQ 8/30/2 | ACQ VPS |

| DSQ | 8/30/2 RF | VPS RF | -   | —  | -  | _          | _       |

Table 7

Register 00 bit description.

| SYMBOL                | BIT      | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IEL                   | D4       | Interrupt Error Level.<br>When logic 0, signal only completely valid data lines from Teletext packet 8/30/2<br>received and VPS received flags.<br>When logic 1, signal valid framing code and Teletext packet header 8/30/2 received or<br>valid start codeword for VPS received.                                                                                                                            |

| ACQ 8/30/2<br>ACQ VPS | D1<br>D0 | Acquire 8/30/2.<br>Acquire VPS.<br>Allows selective decoding of either Teletext packet 8/30/2 data or VPS data. If both are<br>set to the same value the system automatically selects the format being transmitted<br>(see Table 8).                                                                                                                                                                          |

| DSQ                   | D7       | Data Signal Quality.<br>When logic 1, good Teletext or VPS data signal is being received.<br>When logic 0, no Teletext or VPS data signal is being received.                                                                                                                                                                                                                                                  |

| 8/30/2 RF             | D6       | <ul> <li>8/30/2 Received Flag.</li> <li>When logic 1, and IEL (D4) = logic 0 an error-free Teletext packet 8/30/2 has been received, Hamming decoded and stored in the RAM. When logic 1, and IEL(D4) = logic 1 a Teletext packet with a valid framing code and 8/30/2 header has been received, Hamming decoded and stored in RAM.</li> <li>When logic 0 no Teletext packet 8/30/2 data received.</li> </ul> |

| VPS RF                | D5       | VPS Received Flag.<br>When logic 1, and IEL(D4) = logic 0, an error-free VPS data line has been received,<br>biphase decoded and stored in the RAM. When logic 1, and IEL(D4) = logic 1 a VPS<br>data line with valid start code has been received, biphase decoded and stored in RAM.<br>When logic 0 no VPS data received.                                                                                  |

| ACQ 8/30/2 | ACQ VPS | VPS FUNCTION                                  |  |

|------------|---------|-----------------------------------------------|--|

| 0          | 0       | use automatic selection algorithm for line 16 |  |

| 0          | 1       | acquire only VPS data on every VBI line       |  |

| 1          | 0       | acquire only 8/30/2 data on every line 16     |  |

| 1          | 1       | use automatic selection algorithm for line 16 |  |

### SAA5233

### Register 01: Interrupt (reset state X00X XXXX)

Register R01 is WRITE only.

#### Table 9 Register 01.

| D7 | D6        | D5     | D4 | D3 | D2 | D1 | D0 |

|----|-----------|--------|----|----|----|----|----|

| -  | 8/30/2 IE | VPS IE | -  | _  | -  | -  | -  |

#### Table 10 Register 01 bit description.

| SYMBOL    | BIT | FUNCTION                                                                                                                                                                                                                                                                                     |

|-----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8/30/2 IE | D6  | 8/30/2 Interrupt Enable.<br>This allows the reception of Teletext packet 8/30/2 data to be signalled on the INT pin.<br>When logic 0 reception of Teletext packet 8/30/2 data is not signalled on INT pin.<br>When logic 1 reception of Teletext packet 8/30/2 data is signalled on INT pin. |

| VPS IE    | D5  | VPS Interrupt Enable.<br>This allows the reception of VPS data to be signalled on the INT pin.<br>When logic 0 reception of VPS data is not signalled on INT pin.<br>When logic 1 reception of VPS data is signalled on INT pin.                                                             |

#### Register 02 to 0F (HEX): VPS data bytes

A single VPS data bytes is stored as two memory bytes, the least significant nibble of both memory bytes is the data making up the single VPS data byte. The most significant nibble of each memory byte is used to indicate a biphase error in the least significant nibble. This is indicated by the least significant bit being set, the top three bits are not used and are fixed to logic 0 (see Table 11).

#### Table 11 VPS data bytes.

| ADDRESS (HEX) | REGISTER                        | DATA                     |

|---------------|---------------------------------|--------------------------|

| 02            | VPS B5 least significant nibble | 0000 1100 <sup>(1)</sup> |

| 03            | VPS B5 most significant nibble  | 0000 0101 <sup>(1)</sup> |

#### Note

1. Equivalent to VPS B5 0101 1100 (MSB to LSB).

#### Table 12 Register 02.

| D7 | D6 | D5 | D4        | D3         | D2         | D1         | D0         |

|----|----|----|-----------|------------|------------|------------|------------|

| _  | -  | -  | BIPHASE   | DATA BIT 3 | DATA BIT 2 | DATA BIT 1 | DATA BIT 0 |

|    |    |    | ERROR BIT |            |            |            |            |

### Register 11 to 1D (HEX): Teletext packet 8/30/2 data bytes

Data is stored as single bytes. The four least significant bits represent the data. The fifth bit if set indicates a Hamming error in the stored data. The top three bits of the byte are not used and are fixed to logic 0.

### Table 13 Register 11.

| D7 | D6 | D5 | D4        | D3         | D2         | D1         | D0         |

|----|----|----|-----------|------------|------------|------------|------------|

| -  | _  | _  | HAMMING   | DATA BIT 3 | DATA BIT 2 | DATA BIT 1 | DATA BIT 0 |

|    |    |    | ERROR BIT |            |            |            |            |

### SAA5233

#### Register 1E to 31D (HEX): Status display message

Data is stored as bytes which represent a Teletext character. The data is odd parity checked, if a parity error occurs this causes the byte not to be written to the RAM. The MSB is not used and is fixed to logic 0.

#### Table 14 Register 11.

| D7 | D6         | D5         | D4         | D3         | D2         | D1         | D0         |

|----|------------|------------|------------|------------|------------|------------|------------|

| _  | DATA BIT 6 | DATA BIT 5 | DATA BIT 4 | DATA BIT 3 | DATA BIT 2 | DATA BIT 1 | DATA BIT 0 |

#### I<sup>2</sup>C-bus slave address

The slave address for the device can take one of two values dependent on the state of the input pin AD.

#### Table 15 Device address.

| AD | SLAVE ADDRESS            |

|----|--------------------------|

| 0  | 0010 001X <sup>(1)</sup> |

| 1  | 0010 000X <sup>(1)</sup> |

#### Note

1. Where X is the  $R/\overline{W}$  bit.

### I<sup>2</sup>C-bus increment

The I<sup>2</sup>C-bus will also increment between registers as listed in Table 16

#### Table 16 Increment between registers.

| ADDRESS        | CONTENTS                              |

|----------------|---------------------------------------|

| 02 to 0F (HEX) | VPS data bytes                        |

| 11 to 31 (HEX) | Teletext packet 8/30/2 data bytes and |

|                | Status display message                |

Addressing any register in either of these ranges will initialize an increment until the final stop value provided each byte is acknowledged by the receiver.

#### Initialization during power-up

The device has an internal power-on reset unit which is used to reset the I<sup>2</sup>C-bus interface to be a slave transceiver. It also initializes the device to receive only completely valid Teletext packet 8/30/2 and VPS data. The interrupt signals for both Teletext packet 8/30/2 and VPS are disabled.

## SAA5233

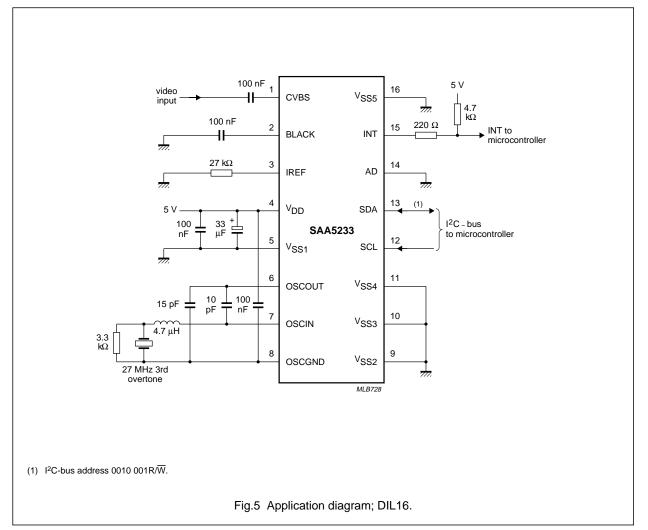

### APPLICATION INFORMATION

| SYMBOL                         | PARAMETER            | TYP. | MAX.                    | UNIT               |  |

|--------------------------------|----------------------|------|-------------------------|--------------------|--|

| Crystal (27 MHz, 3rd overtone) |                      |      |                         |                    |  |

| C1                             | series capacitance   | 1.7  | -                       | pF                 |  |

| C0                             | parallel capacitance | 5.2  | -                       | pF                 |  |

| CL                             | load capacitance     | 20   | -                       | pF                 |  |

| R <sub>r</sub>                 | resonance resistance | -    | 50                      | Ω                  |  |

| R1                             | series resistance    | 20   | -                       | Ω                  |  |

| X <sub>a</sub>                 | ageing               | -    | $\pm 5 \times 10^{-6}$  | year <sup>_1</sup> |  |

| Xj                             | adjustment tolerance | -    | $\pm 25 \times 10^{-6}$ |                    |  |

| X <sub>d</sub>                 | drift                | -    | $\pm 25 \times 10^{-6}$ |                    |  |

Table 17 Crystal characteristics.

## SAA5233

### PACKAGE OUTLINES

## SAA5233

## SAA5233

#### SOLDERING

#### Plastic dual in-line packages

#### BY DIP OR WAVE

The maximum permissible temperature of the solder is 260 °C; this temperature must not be in contact with the joint for more than 5 s. The total contact time of successive solder waves must not exceed 5 s.

The device may be mounted up to the seating plane, but the temperature of the plastic body must not exceed the specified storage maximum. If the printed-circuit board has been pre-heated, forced cooling may be necessary immediately after soldering to keep the temperature within the permissible limit.

#### **REPAIRING SOLDERED JOINTS**

Apply a low-voltage soldering iron below the seating plane (or not more than 2 mm above it). If its temperature is below 300  $^{\circ}$ C, it must not be in contact for more than 10 s; if between 300 and 400  $^{\circ}$ C, for not more than 5 s.

#### Plastic small-outline packages

#### BY WAVE

During placement and before soldering, the component must be fixed with a droplet of adhesive. After curing the adhesive, the component can be soldered. The adhesive can be applied by screen printing, pin transfer or syringe dispensing.

Maximum permissible solder temperature is 260 °C, and maximum duration of package immersion in solder bath is 10 s, if allowed to cool to less than 150 °C within 6 s. Typical dwell time is 4 s at 250 °C.

A modified wave soldering technique is recommended using two solder waves (dual-wave), in which a turbulent wave with high upward pressure is followed by a smooth laminar wave. Using a mildly-activated flux eliminates the need for removal of corrosive residues in most applications. BY SOLDER PASTE REFLOW

Reflow soldering requires the solder paste (a suspension of fine solder particles, flux and binding agent) to be applied to the substrate by screen printing, stencilling or pressure-syringe dispensing before device placement.

Several techniques exist for reflowing; for example, thermal conduction by heated belt, infrared, and vapour-phase reflow. Dwell times vary between 50 and 300 s according to method. Typical reflow temperatures range from 215 to 250 °C.

Preheating is necessary to dry the paste and evaporate the binding agent. Preheating duration: 45 min at 45 °C.

REPAIRING SOLDERED JOINTS (BY HAND-HELD SOLDERING IRON OR PULSE-HEATED SOLDER TOOL)

Fix the component by first soldering two, diagonally opposite, end pins. Apply the heating tool to the flat part of the pin only. Contact time must be limited to 10 s at up to 300 °C. When using proper tools, all other pins can be soldered in one operation within 2 to 5 s at between 270 and 320 °C. (Pulse-heated soldering is not recommended for SO packages.)

For pulse-heated solder tool (resistance) soldering of VSO packages, solder is applied to the substrate by dipping or by an extra thick tin/lead plating before package placement.

### SAA5233

### DEFINITIONS

| Data sheet status                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                      |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|--|

| Objective specification                                                                                                                                                                                                                                                                                                                                                                                                                                   | This data sheet contains target or goal specifications for product development.      |  |  |  |

| Preliminary specification                                                                                                                                                                                                                                                                                                                                                                                                                                 | This data sheet contains preliminary data; supplementary data may be published later |  |  |  |

| Product specification                                                                                                                                                                                                                                                                                                                                                                                                                                     | This data sheet contains final product specifications.                               |  |  |  |

| Limiting values                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                      |  |  |  |

| Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability. |                                                                                      |  |  |  |

| Application information                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                      |  |  |  |

| Where application informat                                                                                                                                                                                                                                                                                                                                                                                                                                | ion is given, it is advisory and does not form part of the specification.            |  |  |  |

#### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.

### PURCHASE OF PHILIPS I<sup>2</sup>C COMPONENTS

Purchase of Philips I<sup>2</sup>C components conveys a license under the Philips' I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C system provided the system conforms to the I<sup>2</sup>C specification defined by Philips. This specification can be ordered using the code 9398 393 40011.

## Philips Semiconductors – a worldwide company

Argentina: IEROD, Av. Juramento 1992 - 14.b, (1428) BUENOS AIRES, Tel. (541)786 7633, Fax. (541)786 9367 Australia: 34 Waterloo Road, NORTH RYDE, NSW 2113, Tel. (02)805 4455, Fax. (02)805 4466 Austria: Triester Str. 64, A-1101 WIEN, P.O. Box 213, Tel. (01)60 101-1236, Fax. (01)60 101-121 Belgium: Postbus 90050, 5600 PB EINDHOVEN, The Netherlands, Tel. (31)40 783 749, Fax. (31)40 788 399 Brazil: Rua do Rocio 220 - 5<sup>th</sup> floor, Suite 51, CEP: 04552-903-SÃO PAULO-SP, Brazil. P.O. Box 7383 (01064-970) Tel. (011)821-2333, Fax. (011)829-1849 Canada: INTEGRATED CIRCUITS: Tel. (800)234-7381, Fax. (708)296-8556 DISCRETE SEMICONDUCTORS: 601 Milner Ave, SCARBOROUGH, ONTARIO, M1B 1M8, Tel. (0416)292 5161 ext. 2336, Fax. (0416)292 4477 Chile: Av. Santa Maria 0760, SANTIAGO, Tel. (02)773 816, Fax. (02)777 6730 Colombia: IPRELENSO LTDA, Carrera 21 No. 56-17, 77621 BOGOTA, Tel. (571)249 7624/(571)217 4609, Fax. (571)217 4549 Denmark: Prags Boulevard 80, PB 1919, DK-2300 COPENHAGEN S, Tel. (032)88 2636, Fax. (031)57 1949 Finland: Sinikalliontie 3, FIN-02630 ESPOO, Tel. (9)0-50261, Fax. (9)0-520971 France: 4 Rue du Port-aux-Vins, BP317, 92156 SURESNES Cedex, Tel. (01)4099 6161, Fax. (01)4099 6427 Germany: PHILIPS COMPONENTS UB der Philips G.m.b.H., P.O. Box 10 63 23, 20043 HAMBURG, Tel. (040)3296-0, Fax. (040)3296 213. Greece: No. 15, 25th March Street, GR 17778 TAVROS, Tel. (01)4894 339/4894 911, Fax. (01)4814 240 Hong Kong: PHILIPS HONG KONG Ltd., Components Div., 6/F Philips Ind. Bldg., 24-28 Kung Yip St., KWAI CHUNG, N.T., Tel. (852)424 5121, Fax. (852)428 6729 India: Philips INDIA Ltd, Components Dept, Shivsagar Estate, A Block , Dr. Annie Besant Rd. Worli, Bombay 400 018 Tel. (022)4938 541, Fax. (022)4938 722 Indonesia: Philips House, Jalan H.R. Rasuna Said Kav. 3-4, P.O. Box 4252, JAKARTA 12950, Tel. (021)5201 122, Fax. (021)5205 189 Ireland: Newstead, Clonskeagh, DUBLIN 14, Tel. (01)640 000, Fax. (01)640 200 Italy: PHILIPS COMPONENTS S.r.I. Viale F. Testi, 327, 20162 MILANO Tel. (02)6752.3302, Fax. (02)6752 3300. Japan: Philips Bldg 13-37, Kohnan2-chome, Minato-ku, TOKYO 108, Tel. (03)3740 5028, Fax. (03)3740 0580 Korea: (Republic of) Philips House, 260-199 Itaewon-dong, Yongsan-ku, SEOUL, Tel. (02)794-5011, Fax. (02)798-8022 Malaysia: No. 76 Jalan Universiti, 46200 PETALING JAYA, SELANGOR, Tel. (03)750 5214, Fax. (03)757 4880 Mexico: Philips Components, 5900 Gateway East, Suite 200, EL PASO, TX 79905, Tel. 9-5(800)234-7381, Fax. (708)296-8556 Netherlands: Postbus 90050, 5600 PB EINDHOVEN, Bldg. VB Tel. (040)783749, Fax. (040)788399 New Zealand: 2 Wagener Place, C.P.O. Box 1041, AUCKLAND,

**Jew Zealand:** 2 Wagener Place, C.P.O. Box 1041, AUCKLAND Tel. (09)849-4160, Fax. (09)849-7811 Norway: Box 1, Manglerud 0612, OSLO, Tel. (022)74 8000, Fax. (022)74 8341 Pakistan: Philips Electrical Industries of Pakistan Ltd., Exchange Bldg. ST-2/A, Block 9, KDA Scheme 5, Clifton, KARACHI 75600, Tel. (021)587 4641-49, Fax. (021)577035/5874546. Philippines: PHILIPS SEMICONDUCTORS PHILIPPINES Inc, 106 Valero St. Salcedo Village, P.O. Box 2108 MCC, MAKATI, Metro MANILA, Tel. (02)810 0161, Fax. (02)817 3474 Portugal: PHILIPS PORTUGUESA, S.A. Rua dr. António Loureiro Borges 5, Arquiparque - Miraflores, Apartado 300. 2795 LINDA-A-VELHA. Tel. (01)14163160/4163333, Fax. (01)14163174/4163366. Singapore: Lorong 1, Toa Payoh, SINGAPORE 1231, Tel. (65)350 2000, Fax. (65)251 6500 South Africa: S.A. PHILIPS Pty Ltd., Components Division, 195-215 Main Road Martindale, 2092 JOHANNESBURG, P.O. Box 7430 Johannesburg 2000, Tel. (011)470-5911, Fax. (011)470-5494. Spain: Balmes 22, 08007 BARCELONA. Tel. (03)301 6312, Fax. (03)301 42 43 Sweden: Kottbygatan 7, Akalla. S-164 85 STOCKHOLM, Tel. (0)8-632 2000, Fax. (0)8-632 2745 Switzerland: Allmendstrasse 140, CH-8027 ZÜRICH, Tel. (01)488 2211, Fax. (01)481 77 30 Taiwan: PHILIPS TAIWAN Ltd., 23-30F, 66, Chung Hsiao West Road, Sec. 1. Taipeh, Taiwan ROC, P.O. Box 22978, TAIPEI 100, Tel. (02)388 7666, Fax. (02)382 4382. Thailand: PHILIPS ELECTRONICS (THAILAND) Ltd., 209/2 Sanpavuth-Bangna Road Prakanong, Bangkok 10260, THAILAND, Tel. (662)398-0141, Fax. (662)398-3319 Turkey: Talatpasa Cad. No. 5, 80640 GÜLTEPE/ISTANBUL, Tel. (0212)279 2770, Fax. (0212)269 3094 United Kingdom: Philips Semiconductors Limited, P.O. Box 65, Philips House, Torrington Place, LONDON, WC1E 7HD, Tel. (071)436 41 44, Fax. (071)323 03 42 United States: INTEGRATED CIRCUITS: 811 East Argues Avenue, SUNNYVALE, CA 94088-3409, Tel. (800)234-7381, Fax. (708)296-8556 DISCRETE SEMICONDUCTORS: 2001 West Blue Heron Blvd., P.O. Box 10330, RIVIERA BEACH, FLORIDA 33404. Tel. (800)447-3762 and (407)881-3200, Fax. (407)881-3300 Uruguay: Coronel Mora 433, MONTEVIDEO, Tel. (02)70-4044, Fax. (02)92 0601 For all other countries apply to: Philips Semiconductors, International Marketing and Sales, Building BAF-1, P.O. Box 218, 5600 MD, EINDHOVEN, The Netherlands Telex 35000 phtcnl, Fax. +31-40-724825 SCD32 © Philips Electronics N.V. 1994 All rights are reserved. Reproduction in whole or in part is prohibited without the

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.

The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights. Printed in The Netherlands

533061/01/1500/pp20 Document order number: Date of release: June 1994 9397 736 20011

# **Philips Semiconductors**