LB1952/LB1952M

# 3-phase Brushless Motor Driver for VTR Capstans

## **Functions**

- 3-phase full-wave current linear drive system

- Torque ripple correction circuit built in (variable correction factor)

- · Current limiting circuit built in

- Output stage upper/lower oversaturation prevention circuit built in (no external capacitor required)

- FG amplifier built in

- · Thermal shutdown circuit built in

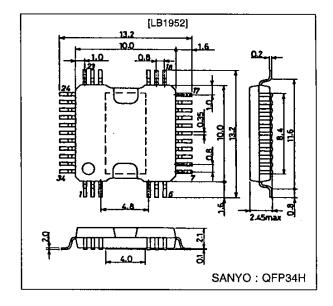

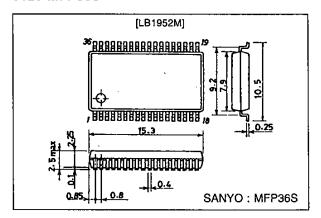

## **Package Dimensions**

unit: mm

#### 3206-QFP34H

#### 3129-MFP36S

## **Specifications**

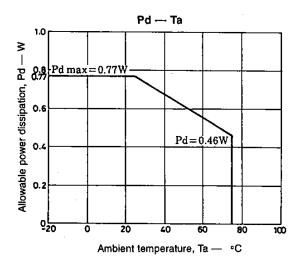

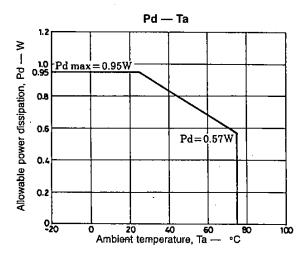

## Absolute Maximum Ratings at Ta = 25 °C

| Parameter                   | Symbol              | Conditions                         | Ratings     | Unit |

|-----------------------------|---------------------|------------------------------------|-------------|------|

| Maximum supply voltage      | V <sub>CC</sub> max |                                    | 7           | V    |

|                             | V <sub>S</sub> max  |                                    | 24          | V    |

| Maximum output current      | I <sub>O</sub> max  |                                    | 1.3         | Α    |

|                             |                     | Arbitrarily large heat sink LB1952 | 12.5        | W    |

| Allowable power dissipation | Pd max              | Independent IC LB1952              | 0.77        | W    |

|                             |                     | Independent IC LB1952M             | 0.95        | W    |

| Operating temperature       | Topr                |                                    | -20 to +75  | °C   |

| Storage temperature         | Tstg                |                                    | -55 to +150 | °C   |

## Allowable Operating Ranges at Ta = 25 °C

| Parameter            | Symbol              | Conditions                     | Ratings        | Unit              |

|----------------------|---------------------|--------------------------------|----------------|-------------------|

| Supply voltage       | Vs                  |                                | 5 to 22        | ٧                 |

| Supply voltage       | V <sub>CC</sub>     |                                | 4.5 to 5.5     | ٧                 |

| Hall input amplitude | V <sub>HALL</sub>   | Between Hall inputs            | ±30 to ±80     | mV <sub>0-P</sub> |

| GSENSE input range   | V <sub>GSENSE</sub> | Relative to control system GND | -0.20 to +0.20 | V                 |

## Electrical Characteristics at Ta = 25 °C, $V_{\text{CC}}$ = 5 V, $V_{\text{S}}$ = 15 V

| Parameter                                | Symbol                | Conditions                                                                                                                  | min  | typ  | max  | Unit       |

|------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------|------|------|------|------------|

| V <sub>CC</sub> supply current           | lcc                   | R <sub>L</sub> = ∞ (when stopped), V <sub>CTL</sub> = 0 V, V <sub>LIM</sub> = 0 V                                           |      | 12   | 18   | mΑ         |

| [Output]                                 |                       |                                                                                                                             |      |      | •••• |            |

| Output saturation voltage                | V <sub>Osat</sub> 1   | $I_O$ = 500 mA, Rf = 0.5 $\Omega$ , Sink + Source<br>$V_{CTL}$ = $V_{LIM}$ = 5 V (with saturation prevention)               |      | 2.1  | 2.6  | ٧          |

| ,                                        | V <sub>Osat</sub> 2   | $I_O = 1.0$ A, Rf = 0.5 $\Omega$ , Sink + Source<br>$V_{CTL} = V_{LIM} = 5$ V (with saturation prevention)                  |      | 2.6  | 3.5  | ٧          |

| Output leakage current                   | loleak                |                                                                                                                             |      |      | 1.0  | mΑ         |

| [FR]                                     |                       |                                                                                                                             |      |      |      |            |

| FR pin input threshold voltage           | V <sub>FSR</sub>      |                                                                                                                             | 2.25 | 2.50 | 2.75 | V          |

| FR pin input bias current                | lb (FSR)              |                                                                                                                             | -5.0 |      |      | μA         |

| [Control]                                |                       |                                                                                                                             | •    |      |      |            |

| CTLREF pin voltage                       | V <sub>CREF</sub>     |                                                                                                                             | 2.05 | 2.15 | 2.25 | V          |

| CTLREF pin input range                   | V <sub>CREF</sub> IN  |                                                                                                                             | 1.50 |      | 3.50 | V          |

| CTL pin input bias current               | lb (CTL)              | With V <sub>CTL</sub> = 5 V, CTLREF : Open                                                                                  |      |      | 4.0  | μΑ         |

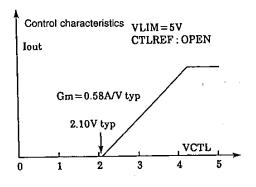

| CTL pin control start voltage            | V <sub>CTL</sub> (ST) | With Rf = $0.5 \Omega$ , $V_{L1M} = 5 V$ , $V_{O} \ge 10 \text{ mA}$ , Hall input logic fixed, (u, v, w = H, H, L)          | 2.00 | 2.15 | 2.30 | ٧          |

| CTL pin control Gm                       | Gm (CTL)              | With Rf = $0.5 \Omega$ , $\Delta I_O = 200 \text{ mA}$ ,<br>Hall input logic fixed, (u, v, w = H, H, L)                     | 0.46 | 0.58 | 0.70 | <b>A</b> > |

| [Current Limit]                          |                       |                                                                                                                             |      |      |      |            |

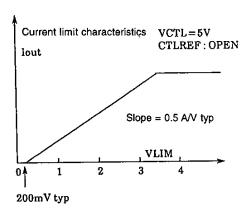

| LIM current limit offset voltage         | Voff (LIM)            | With Rf = 0.5 $\Omega$ , V <sub>CTL</sub> = 5 V, I <sub>O</sub> $\ge$ 10 mA,<br>Hall input logic fixed, (u, v, w = H, H, L) | 140  | 200  | 260  | mV         |

| LIM pin input bias current               | lb (LIM)              | With V <sub>CTL</sub> = 5 V, CTLREF : Open.<br>V <sub>LIM</sub> = 0 V                                                       | -2.5 |      |      | μΑ         |

| LIM pin current limit level              | l lim                 | With Rf = 0.5 Ω, V <sub>CTL</sub> = 5 V, V <sub>LIM</sub> = 2.06 V,<br>Hall input logic fixed, (u, v, w = H, H, L)          | 830  | 900  | 970  | mA         |

| [Hall Amplifier]                         |                       |                                                                                                                             | •    |      |      |            |

| Hall amplifier input offset voltage      | Voff (HALL)           |                                                                                                                             | -6   |      | +6   | mV         |

| Hall amplifier input bias current        | Ib (HALL)             |                                                                                                                             |      | 1.0  | 3.0  | μА         |

| Hall amplifier common-mode input voltage | Vcm (HALL)            |                                                                                                                             | 1.3  |      | 3.3  | ٧          |

| [TRC]                                    |                       |                                                                                                                             |      |      |      |            |

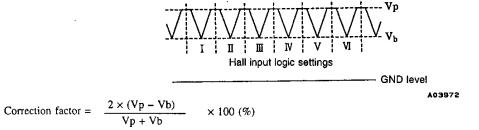

| Torque ripple correction factor          | T <sub>RC</sub>       | At bottom and peak in Rf waveform at I $_{\rm O}$ = 200 mA (RF=0.5 $\Omega$ , ADJ-OPEN) Note 2                              |      | 9    |      | %          |

| ADJ pin voltage                          | Vadj                  |                                                                                                                             | 2.37 | 2.50 | 2.63 | ٧          |

Continued on next page.

#### Continued from proceeding page.

| Parameter                                       | Symbol                  | Conditions                                                                                          | min   | typ  | max   | Unit |

|-------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------|-------|------|-------|------|

| [FG Amplifier]                                  |                         |                                                                                                     | •     |      |       |      |

| FG amplifier input offset voltage               | Voff (FG)               |                                                                                                     | -8    |      | +8    | mV   |

| FG amplifier input bias current                 | lb (FG)                 |                                                                                                     | -100  |      |       | nΑ   |

| FG amplifier output saturation voltage          | V <sub>Osat</sub> (FG)  | At internal pull-up resistor load on sink side                                                      |       |      | 0.5   | ٧    |

| FG amplifier common-mode input voltage          | V <sub>CM</sub> (FG)    |                                                                                                     | 0.5   |      | 4.0   | V    |

| [Saturation]                                    |                         |                                                                                                     |       |      |       |      |

| Saturation prevention circuit lower set voltage | V <sub>Osat</sub> (DET) | Voltage between each Out and Rf at $I_O$ = 10 mA, Rf = 0.5 $\Omega$ , $V_{CTL}$ = $V_{LIM}$ = 5 $V$ | 0.175 | 0.25 | 0.325 | ٧    |

| [TSD]                                           | *                       |                                                                                                     |       |      |       |      |

| TSD operation temperature                       | T-TSD                   | (Design target) Note 1                                                                              |       | 180  |       | ۰c   |

| TSD temperature hysteresis width                | ΔTSD                    | (Design target) Note 1                                                                              |       | 20   |       | ô    |

Note 1: No measurements are performed for any values listed in the condition column as design targets.

Note 2: The torque ripple correction factor is calculated using the Rf voltage waveform as follows.

#### **Truth Table & Control Function**

|   | Source → Sink     | H   | lali inpu | it | FR |  |

|---|-------------------|-----|-----------|----|----|--|

|   | Source → Sink     | U   | ٧         | W  | rm |  |

|   | $V \rightarrow W$ | Ξ   | н         | _  | Н  |  |

| ' | $W \rightarrow V$ | "   | п         | L  | L  |  |

| 2 | U → W             | н   | L         | _  | Н  |  |

| - | W → U             | , , | -         |    | L  |  |

| 3 | $U \rightarrow V$ | н   | L         | н  | Н  |  |

| " | $V \rightarrow U$ | "   |           |    | L  |  |

| 4 | $W \rightarrow V$ | L   | L         | н  | Н  |  |

| * | $V \rightarrow W$ | -   | -         |    | L. |  |

| 5 | W → U             | Ĺ   | н         | Н  | Н  |  |

| 3 | U → W             | -   | "         | "  | L  |  |

| 6 | V → U             | ı   | Н         | ı  | Н  |  |

|   | U → V             |     | "         |    | L  |  |

Note: "H" in the FR column represents a voltage of 2.75V or more; "L" represents a voltage of 2.25V or less. (At  $V_{CC} = 5 \text{ V}$ )

Note: "H" in the hall input columns represents a state in which "+" has a potential which is higher by 0.01 V or more than that of the "-" phase inputs.

Conversely, "L" represents a state in which "+" has a potential which is lower by 0.01V or more than that of the "-" phase input.

Note: Since 180° conduction is used as the drive system, other phases than the sink and source phases are turned off.

## **Control Function & Current Limit Function**

#### **Pin Functions**

The pin numbers in ( ) are for MFP.

| Pin name                               | Pin No.                                               | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|----------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| FR                                     | 1 (33)                                                | Forward/reverse select pin. The pin voltage selects forward/reverse. (Vth = 2.5 V typ at V <sub>CC</sub> = 5 V)                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| GND                                    | 2 (34)                                                | GND for other than output transistor. Minimum potential of output transistor is at Rf pin.                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| FGin (–)                               | 5 (3)                                                 | Input pin when FG amplifier is used with inverted input. Feedback resistor is connected between this pin and FG-OUT.                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| FGin (+)                               | 6 (4)                                                 | Noninverting input pin when FG amplifier is used with differential input. Internal bias is not applied.                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| FG-OUT                                 | 8 (5)                                                 | FG amplifier output pin. Resistive load provided internally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| CTL                                    | 9 (6)                                                 | Speed control pin. Control is exercised by constant-current drive with current feedback applied from Rf. Gm = 0.58 AV typ at Rf=0.5 $\Omega$                                                                                                                                                                                                                                                                                                                                                                                    |  |

| CTLREF                                 | 10 (7)                                                | Control reference voltage pin. The voltage is set internally to approx. 0.43 x $V_{CC}$ but this can be varied by applying voltage through a low impedance (input impedance = approx. 4.3 k $\Omega$ ).                                                                                                                                                                                                                                                                                                                         |  |

| LIM                                    | 11 (8)                                                | Current limiting function control pin. The output current is varied linearly by this pin voltage; slope = 0.5 A/V typ at Rf = 0.5 $\Omega$ .                                                                                                                                                                                                                                                                                                                                                                                    |  |

| FC                                     | 12 (9)                                                | Speed control loop frequency characteristic correction pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Uin+, Uin-<br>Vin+, Vin-<br>Win+, Win- | 13, 14 (10, 11)<br>15, 16 (12, 13)<br>17, 18 (14, 15) | U-phase Hall device input pin; logic "H" represent IN+ > IN V-phase Hall device input pin; logic "H" represent IN+ > IN W-phase Hall device input pin; logic "H" represent IN+ > IN                                                                                                                                                                                                                                                                                                                                             |  |

| V <sub>CC</sub>                        | 19 (16)                                               | Power supply pin for supplying power to all circuits except output section in IC; this voltage must be stabilized so as to eliminate ripple and noise.                                                                                                                                                                                                                                                                                                                                                                          |  |

| V <sub>S</sub>                         | 22 (21)                                               | Output section power supply pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| ADJ                                    | 23 (22)                                               | Pin for external adjustment of torque ripple correction factor. When this factor is to be adjusted, a voltage is externally applied to the ADJ pin through a low impedance. If the voltage applied is increased, the factor drops; conversely, if it is reduced, the factor rises. The factor varies between 0 and 2 times that of the open state. (The voltage is set to approx. $V_{CC}/2$ internally, and the input impedance is approx. $5  \mathrm{k}\Omega$ .)                                                            |  |

| Rf (PWR)<br>Rf (SNS)                   | 24 (23)<br>33 (31)                                    | Output current detection pin. Current feedback is applied to the control section by connecting Rf between this pin and GND. The lower oversaturation prevention circuit and torque ripple correction circuit are activated in accordance with this pin voltage. Since the oversaturation prevention level is set with this voltage, the lower oversaturation prevention effect may deteriorate in the high current range if the Rf value is reduced to an extremely low level. The PWR and SENSE pins must always be connected. |  |

| Uout<br>Vout<br>Wout                   | 27 (26)<br>29 (27)<br>31 (28)                         | U-phase output pin V-phase output pin (Built-in spark killer diode) W-phase output pin                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| GSENSE                                 | 34 (32)                                               | GND sensing pin. By connecting this pin to the neighboring GND on the Rf resistor side of the motor GND wire which contains Rf, the effect that GND common impedance exerts on Rf can be eliminated. (This pin must not be left open.)                                                                                                                                                                                                                                                                                          |  |

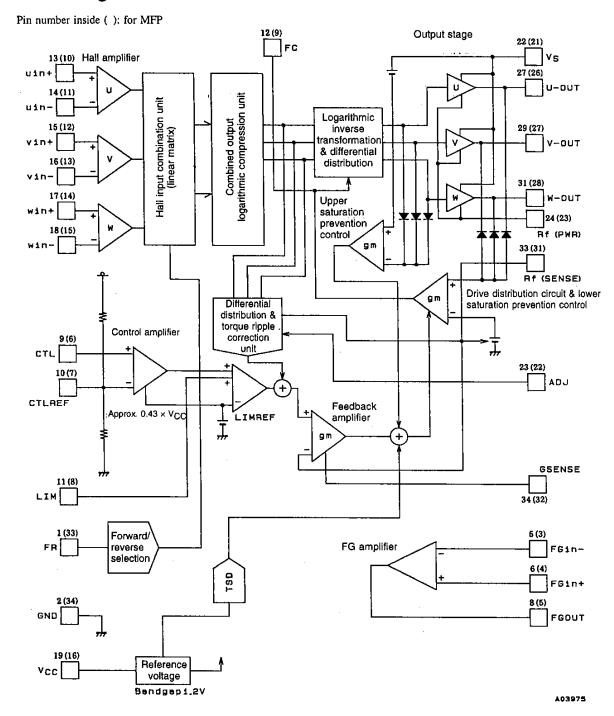

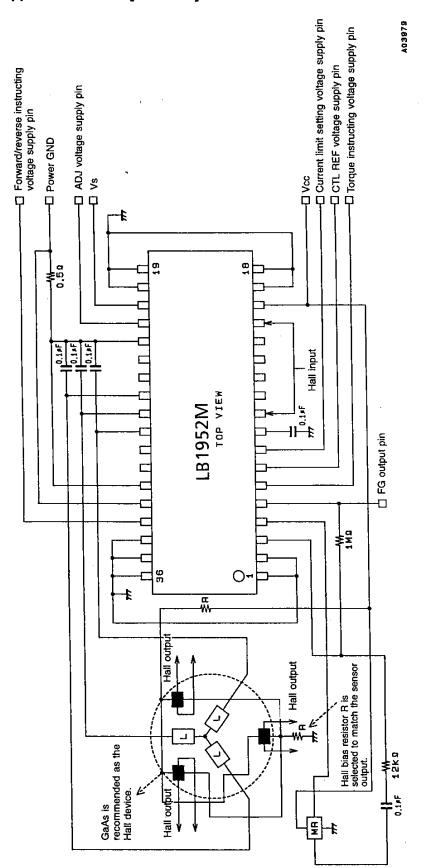

## **Block Diagram**

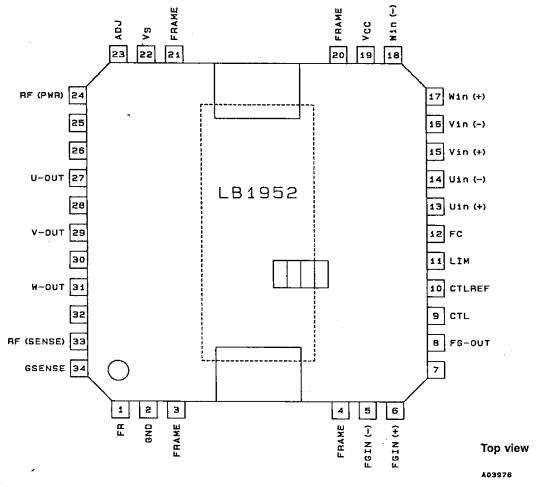

## Pin Assignment [LB1952]

(PACKAGE: QFP-34H-A)

Note: FRAME must be connected to GND for GND potential stabilization.

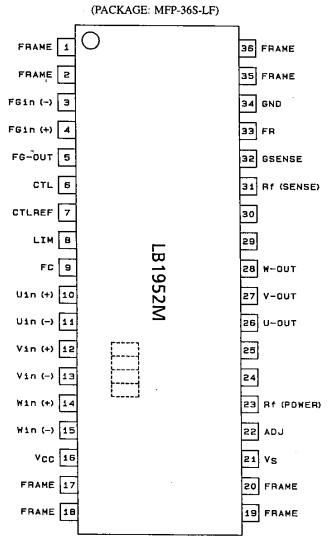

### Pin Assignment [LB1952M]

A03977 Top view

Note: Although there is no internal connections between the FRAME pin and GND, FRAME must be connected to GND externally for GND potential stabilization.

## Sample Application Circuit [LB1952]

Note: The constants provided in this sample application circuit are provided by way of example and are not intended to guarantee the characteristics.

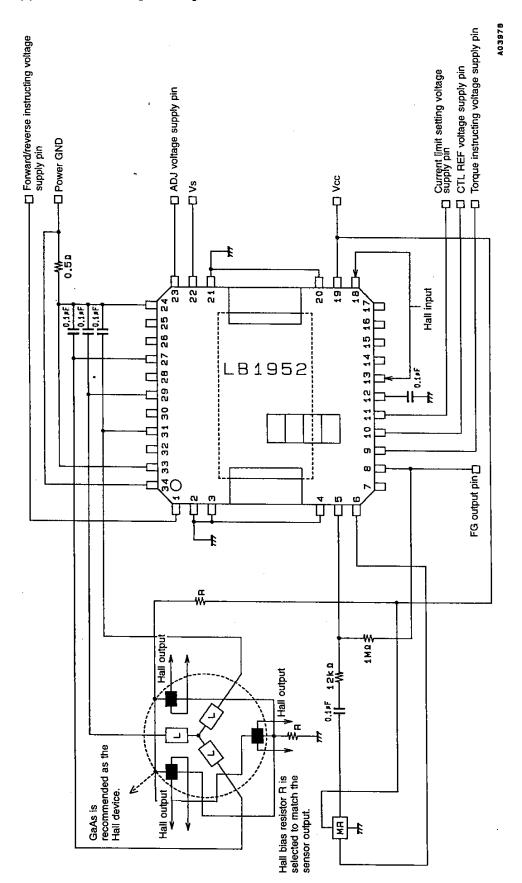

## Sample Application Circuit [LB1952M]

Note: The constants provided in this sample application circuit are provided by way of example and are not intended to guarantee the characteristics.

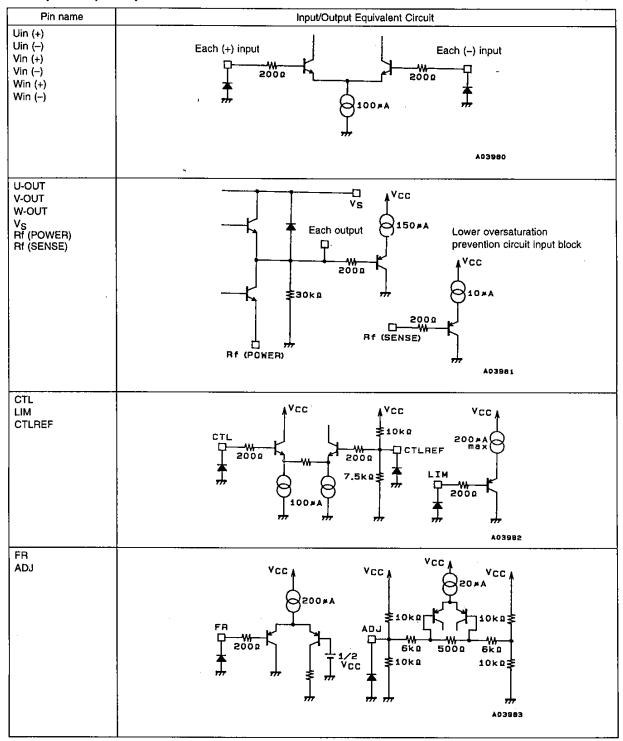

## Pin Input/Output Equivalent Circuit

Continued on next page.

### Continued from proceeding page.

| Pin name    | Input/Output Equivalent Circuit |

|-------------|---------------------------------|

| FGin (+)    | FGin (-) FGin (+)               |

| FGOUT<br>FC | VCC VCC VCC VCC VCC A03888      |

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of September, 1995. Specifications and information herein are subject to change without notice.