## 64-Channel Serial To Parallel Converter With P-Channel Open Drain Controllable Output Current

#### **Ordering Information**

|         | Package Options                                                       |           |          |                                                              |  |  |  |

|---------|-----------------------------------------------------------------------|-----------|----------|--------------------------------------------------------------|--|--|--|

| Device  | Device 80-Lead Quad 80 Lead Quad<br>Ceramic Gullwing Plastic Gullwing |           | Die      | 80 Lead Quad<br>Ceramic Gullwing<br>(MIL-Std-833 Processed*) |  |  |  |

| HV57009 | HV57009DG                                                             | HV57009PG | HV57009X | RBHV57009DG                                                  |  |  |  |

\* For Hi-Rel process flows, refer to page 5-3 of the Databook.

#### Features

- □ Processed with HVCMOS<sup>®</sup> technology

- □ 5V CMOS Logic

- Output voltage up to -85V

- Output current source control

- 16MHz equivalent data rate

- Latched data outputs

- Given Service State And Servic

- $\Box$  Diode to V<sub>DD</sub> allows efficient power recovery

- □ Hi-Rel processing available

# **Absolute Maximum Ratings**

| Supply voltage, V <sub>DD</sub> <sup>1</sup>                  | -0.5V to +7.5V                 |                                |  |  |

|---------------------------------------------------------------|--------------------------------|--------------------------------|--|--|

| Output Voltage, V <sub>NN</sub> <sup>1</sup>                  | V <sub>DD</sub> + 0.5V to -95V |                                |  |  |

| Logic input levels <sup>1</sup>                               | -0.3V                          | ' to V <sub>DD</sub> +0.3V     |  |  |

| Ground Current <sup>2</sup>                                   |                                | 1.5A                           |  |  |

| Continuous total power dissipation <sup>3</sup>               | Plastic<br>Ceramic             | 1200mW<br>1900mW               |  |  |

| Operating temperature range                                   |                                | 40°C to +85°C<br>5°C to +125°C |  |  |

| Storage temperature range                                     | -65                            | 5°C to +150°C                  |  |  |

| Lead temperature 1.6mm (1/16 inch<br>from case for 10 seconds | )                              | 260°C                          |  |  |

#### Notes:

1. All voltages are referenced to V<sub>ss</sub>.

2. Limited by the total power dissipated in the package.

For operation above 25°C ambient derate linearly to maximum operating temperature at 20mW/°C for plastic and at 19mW/°C for ceramic.

# **General Description**

The HV570 is a low-voltage serial to high-voltage parallel converter with P-channel open drain outputs. This device has been designed for use as a driver for plasma panels.

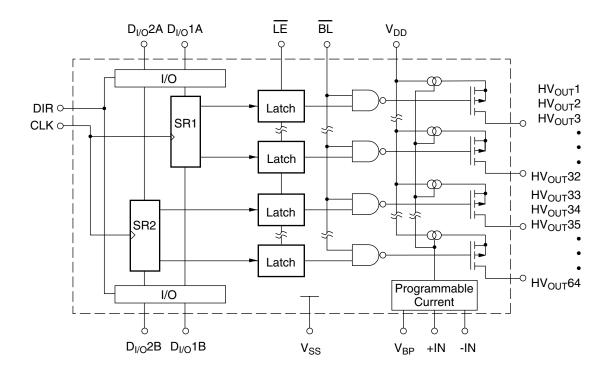

The device has two parallel 32-bit shift registers, permitting data rate twice the speed of one (they are clocked together). There are also 64 latches and control logic to perform the blanking of the outputs.  $HV_{OUT}$ 1 is connected to the first stage of the first shift register through the blanking logic. Data is shifted through the shift registers on the logic low to high transition of the clock. The DIR pin causes CCW shifting when connected to  $V_{SS}$ , and CW shifting when connected to  $V_{DD}$ . A data output buffer is provided for cascading devices. This output reflects the current status of the last bit of the shift register ( $HV_{OUT}$ 64). Operation of the shift registers to latches occurs when the  $\overline{LE}$  input is high. The data in the latches is stored when  $\overline{LE}$  is low.

The HV570 has 64 channels of output constant current sourcing capability. They are adjustable from 0.1 to 2.0mA through one external resistor or a current source.

#### 03/12/02

Supertex Inc. does not recommend the use of its products in life support applications and will not knowingly sell its products for use in such applications unless it receives an adequate "products liability indemnification insurance agreement." Supertex does not assume responsibility for use of devices described and limits its liability to the replacement of devices determined to be defective due to workmanship. No responsibility is assumed for possible omissions or inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications, refer to the Supertex website: http://www.supertex.com. For complete liability information on all Supertex products, refer to the most current databook or to the Legal/Disclaimer page on the Supertex website.

# **Electrical Characteristics**

| DC Characteristics | (All voltages are referenced to $V_{ss}$ | , V <sub>ss</sub> = 0, TA = 25°C) |

|--------------------|------------------------------------------|-----------------------------------|

|--------------------|------------------------------------------|-----------------------------------|

| Symbol           | Parameter                                             |                   | Min                  | Max             | Units | Conditions                                                             |

|------------------|-------------------------------------------------------|-------------------|----------------------|-----------------|-------|------------------------------------------------------------------------|

| I <sub>DD</sub>  | V <sub>DD</sub> supply current                        |                   |                      | 15              | mA    | $V_{DD} = V_{DD}$ , max<br>$f_{CLK} = 8MHz$                            |

| I <sub>NN</sub>  | High voltage supply current                           |                   |                      | -10             | μΑ    | Outputs off, HV <sub>OUT</sub> = -85V<br>(total of all outputs)        |

| I <sub>DDQ</sub> | Quiescent V <sub>DD</sub> supply current              |                   |                      | 100             | μΑ    | All inputs = $V_{DD}$ , except<br>+IN = $V_{SS}$ = GND                 |

| V <sub>OH</sub>  | High-level output                                     | Data out          | V <sub>DD</sub> -0.5 |                 | V     | I <sub>O</sub> = -100μA                                                |

|                  |                                                       | HV <sub>OUT</sub> | +1                   | V <sub>DD</sub> | V     | I <sub>O</sub> = -2mA                                                  |

| V <sub>OL</sub>  | Low-level output                                      | Data out          |                      | +0.5            | V     | I <sub>O</sub> = 100μA                                                 |

| I <sub>IH</sub>  | High-level logic input current                        |                   |                      | 1               | μΑ    | $V_{IH} = V_{DD}$                                                      |

| I <sub>IL</sub>  | Low-level logic input current                         |                   |                      | -1              | μΑ    | $V_{IL} = 0V$                                                          |

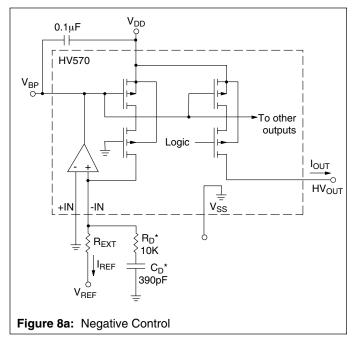

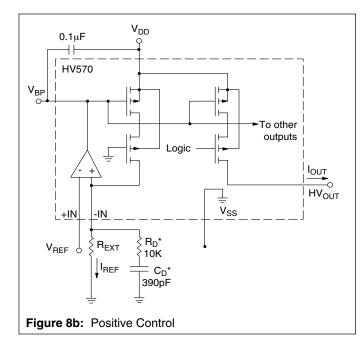

| I <sub>CS</sub>  | HV output source current                              |                   |                      | -2              | mA    | V <sub>REF</sub> = 2V, R <sub>EXT</sub> = 1K,<br>see Figures 8a and 8b |

|                  |                                                       |                   | -0.1                 |                 | mA    | $V_{\text{REF}} = 0.1V, R_{\text{EXT}} = 1K,$<br>see Figure 8a and 8b  |

| $\Delta I_{CS}$  | HV output source current for I <sub>REF</sub> = 2.0mA |                   |                      | 10              | %     | $V_{REF} = 2V, R_{EXT} = 1K$                                           |

Notes 1: Current going out of the chip is considered negative.

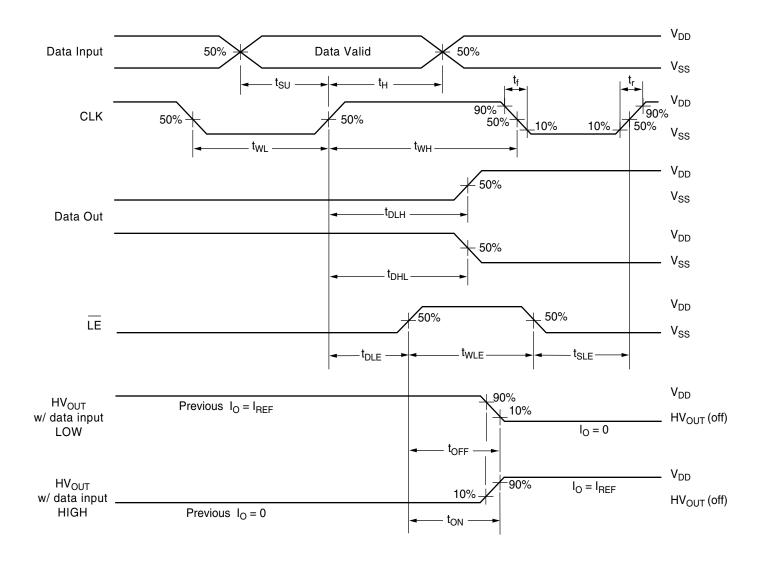

#### **AC Characteristics** (Logic signal inputs and Data inputs have $t_r$ , $t_f \le 5ns$ [10% and 90% points] for measurements)

| Symbol                             | Parameter                                                       | Min | Max | Units | Conditions            |

|------------------------------------|-----------------------------------------------------------------|-----|-----|-------|-----------------------|

| f <sub>CLK</sub>                   | Clock frequency                                                 | DC  | 8   | MHz   | Per register          |

| t <sub>WL</sub> , t <sub>WH</sub>  | Clock width high or low                                         | 62  |     | ns    |                       |

| t <sub>SU</sub>                    | Data set-up time before clock rises                             | 10  |     | ns    |                       |

| t <sub>H</sub>                     | Data hold time after clock rises                                | 15  |     | ns    |                       |

| t <sub>ON</sub> , t <sub>OFF</sub> | Time for latch enable to HV <sub>OUT</sub>                      |     | 500 | ns    | C <sub>L</sub> = 15pF |

| t <sub>DHL</sub>                   | Delay time clock to data high to low                            |     | 70  | ns    | C <sub>L</sub> = 15pF |

| t <sub>DLH</sub>                   | Delay time clock to data low to high                            |     | 70  | ns    | C <sub>L</sub> = 15pF |

| t <sub>DLE</sub>                   | Delay time clock to $\overline{LE}$ low to high                 | 25  |     | ns    |                       |

| t <sub>WLE</sub>                   | Width of LE pulse                                               | 25  |     | ns    |                       |

| t <sub>SLE</sub>                   | LE set-up time before clock rises                               | 0   |     | ns    |                       |

| t <sub>r</sub> , t <sub>f</sub>    | Maximum allowable clock rise and fall time (10% and 90% points) |     | 100 | ns    |                       |

# **Recommended Operating Conditions**

| Symbol            | Parameter                              | Min                     | Max             | Units |    |

|-------------------|----------------------------------------|-------------------------|-----------------|-------|----|

| V <sub>DD</sub>   | Logic supply voltage                   | 4.5                     | 5.5             | V     |    |

| HV <sub>OUT</sub> | HV output off voltage                  | -85                     | V <sub>DD</sub> | V     |    |

| V <sub>IH</sub>   | High-level input voltage               | V <sub>DD</sub> - 1.2V  | V <sub>DD</sub> | V     |    |

| V <sub>IL</sub>   | Low-level input voltage                | Low-level input voltage |                 |       |    |

| f <sub>CLK</sub>  | Clock frequency per register           | DC                      | 8               | MHz   |    |

| T <sub>A</sub>    | Operating free-air temperature Plastic |                         | -40             | +85   | °C |

|                   |                                        | Ceramic                 | -55             | +125  | °C |

Note:

Power-up sequence should be the following:

- Connect ground.

- Apply V<sub>DD</sub>.

3. Set all inputs to a known state.

Power-down sequence should be the reverse of the above.

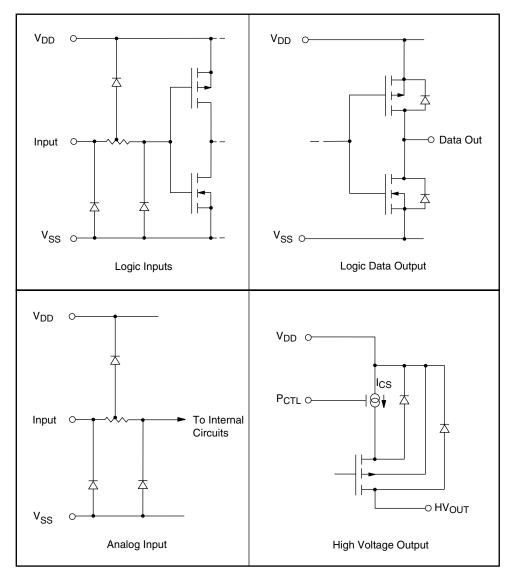

# Figure 1: Input and Output Equivalent Circuits

# Figure 2: Switching Waveforms

# Figure 3: Functional Block Diagram

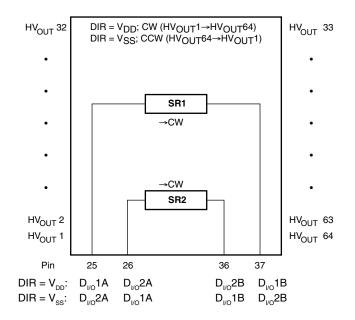

Note: Each SR (shift register) provides 32 outputs. SR1 supplies outputs 1 to 32 and SR2 supplies outputs 33 to 64.

|                        | Inputs                |     |    |    |     | Outputs                          |                             |                       |  |

|------------------------|-----------------------|-----|----|----|-----|----------------------------------|-----------------------------|-----------------------|--|

| Function               | Data In               | CLK | LE | BL | DIR | Shift Reg                        | HV Outputs                  | Data Out              |  |

| All O/P High           | Х                     | Х   | Х  | L  | Х   | *                                | ON                          | *                     |  |

| Data Falls Through     | L                     |     | Н  | н  | х   | LL                               | ON                          | L                     |  |

| (Latches Tansparent)   | н                     |     | н  | н  | x   | нн                               | OFF                         | н                     |  |

| Data Stored in Latches | Х                     | х   | L  | Н  | х   | *                                | Inversion of<br>Stored Data | *                     |  |

| I/O Relation           | D <sub>1/0</sub> 1-2A |     | Н  | н  | Н   | Q <sub>n</sub> →Q <sub>n+1</sub> | New ON or OFF               | D <sub>1/0</sub> 1-2B |  |

|                        | D <sub>i/0</sub> 1-2A |     | L  | н  | Н   | $Q_n \rightarrow Q_{n+1}$        | Previous ON or OFF          | D <sub>1/0</sub> 1-2B |  |

|                        | D <sub>I/0</sub> 1-2B |     | L  | Н  | L   | Q <sub>n</sub> →Q <sub>n-1</sub> | Previous ON or OFF          | D <sub>I/0</sub> 1-2A |  |

|                        | D <sub>I/0</sub> 1-2B |     | Н  | Н  | L   | Q <sub>n</sub> →Q <sub>n-1</sub> | New ON or OFF               | D <sub>1/0</sub> 1-2A |  |

## Figure 4: Function Table

Notes:

\* = dependent on previous stage's state. See Figure 7 for  $D_{_{\rm IN}}$  and  $D_{_{\rm OUT}}$  pin designation for CW and CCW shift.

$H = V_{DD}$  (Logic)/ $V_{NN}$  (HV Outputs)

$L = V_{SS}^{UU}$

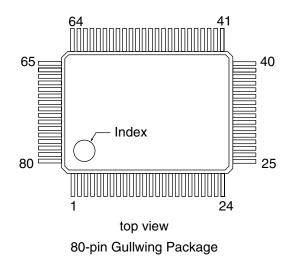

## **Figure 5: Pin Configurations**

## 80-pin Gullwing Package

| Pin | Function             | Pin | Function             |

|-----|----------------------|-----|----------------------|

| 1   | HV <sub>OUT</sub> 24 | 41  | ΗV <sub>ουτ</sub> 64 |

| 2   | HV <sub>OUT</sub> 23 | 42  | ΗV <sub>ουτ</sub> 63 |

| 3   | HV <sub>OUT</sub> 22 | 43  | ΗV <sub>ουτ</sub> 62 |

| 4   | ΗV <sub>ουτ</sub> 21 | 44  | ΗV <sub>ουτ</sub> 61 |

| 5   | ΗV <sub>ουτ</sub> 20 | 45  | ΗV <sub>ουτ</sub> 60 |

| 6   | ΗV <sub>ουτ</sub> 19 | 46  | ΗV <sub>ουτ</sub> 59 |

| 7   | ΗV <sub>ουτ</sub> 18 | 47  | ΗV <sub>ουτ</sub> 58 |

| 8   | ΗV <sub>ουτ</sub> 17 | 48  | ΗV <sub>ουτ</sub> 57 |

| 9   | ΗV <sub>ουτ</sub> 16 | 49  | $HV_{OUT}56$         |

| 10  | ΗV <sub>ουτ</sub> 15 | 50  | $HV_{OUT}55$         |

| 11  | ΗV <sub>ουτ</sub> 14 | 51  | $HV_{OUT}54$         |

| 12  | ΗV <sub>ουτ</sub> 13 | 52  | $HV_{OUT}$ 53        |

| 13  | ΗV <sub>ουτ</sub> 12 | 53  | $HV_{OUT}52$         |

| 14  | ΗV <sub>ουτ</sub> 11 | 54  | $HV_{OUT}51$         |

| 15  | ΗV <sub>ουτ</sub> 10 | 55  | $HV_{OUT}50$         |

| 16  | HV <sub>out</sub> 9  | 56  | $HV_{OUT}$ 49        |

| 17  | HV <sub>OUT</sub> 8  | 57  | $HV_{OUT}$ 48        |

| 18  | ΗV <sub>ουτ</sub> 7  | 58  | $HV_{OUT}47$         |

| 19  | HV <sub>OUT</sub> 6  | 59  | $HV_{OUT}$ 46        |

| 20  | ΗV <sub>ουτ</sub> 5  | 60  | $HV_{OUT}$ 45        |

| 21  | HV <sub>OUT</sub> 4  | 61  | $HV_{OUT}$ 44        |

| 22  | HV <sub>OUT</sub> 3  | 62  | $HV_{OUT}$ 43        |

| 23  | HV <sub>OUT</sub> 2  | 63  | $HV_{OUT}$ 42        |

| 24  | HV <sub>OUT</sub> 1  | 64  | HV <sub>OUT</sub> 41 |

| 25  | D <sub>1/0</sub> 1A  | 65  | $HV_{OUT}40$         |

| 26  | D <sub>1/0</sub> 2A  | 66  | HV <sub>OUT</sub> 39 |

| 27  | N/C                  | 67  | HV <sub>OUT</sub> 38 |

| 28  | N/C                  | 68  | ΗV <sub>ουτ</sub> 37 |

| 29  | LE                   | 69  | HV <sub>OUT</sub> 36 |

| 30  | CLK                  | 70  | HV <sub>OUT</sub> 35 |

| 31  | BL                   | 71  | HV <sub>OUT</sub> 34 |

| 32  | V <sub>ss</sub>      | 72  | HV <sub>OUT</sub> 33 |

| 33  | DIR                  | 73  | HV <sub>OUT</sub> 32 |

| 34  | V <sub>DD</sub>      | 74  | HV <sub>OUT</sub> 31 |

| 35  | -IN                  | 75  | HV <sub>OUT</sub> 30 |

| 36  | D <sub>1/0</sub> 2B  | 76  | ΗV <sub>ουτ</sub> 29 |

| 37  | D <sub>I/0</sub> 1B  | 77  | $HV_{OUT}$ 28        |

| 38  | N/C                  | 78  | $HV_{OUT}$ 27        |

| 39  | +IN                  | 79  | $HV_{OUT}^{}26$      |

| 40  | $V_{BP}$             | 80  | $HV_{OUT}$ 25        |

Notes:

1. Pin designation for  $DIR = V_{DD}$ .

2. A  $0.1\mu$ F capacitor is needed between V<sub>DD</sub> and V<sub>BP</sub> (pin 40) for better output current stability and to prevent transient cross-coupling between outputs. See Fig. 8a and 8b.

## Figure 6: Package Outline

# **Figure 7: Shift Register Operation**

## Typical Current Programming Circuits

\*Required if R<sub>EXT</sub> > 10K or R<sub>EXT</sub> is replaced by a constant current source.

Since

$$I_{OUT} = I_{REF} = \frac{|V_{REF}|}{R_{FXT}}$$

Therefore, if I<sub>OUT</sub> = 2mA and V<sub>REF</sub> = -5V  $\rightarrow$  R<sub>EXT</sub> = 2.5K $\Omega$ . If I<sub>OUT</sub> = 1mA and R<sub>EXT</sub> = 1K $\Omega \rightarrow$  V<sub>REF</sub> = -1V.

If  $R_{_{\rm EXT}}$  >10K $\Omega,~$  add series network  $R_{_{\rm D}}$  and  $C_{_{\rm D}}$  to ground for stability as shown.

This control method behaves linearly as long as the operational amplifier is not saturated. However, it requires a negative power source and needs to provide a current  $I_{REF} = I_{OUT}$  for each HV570 chip being controlled.

If  $HV_{OUT} \ge +1V$ , the  $HV_{OUT}$  cascode may no longer operate as a perfect current source, and the output current will diminish. This effect depends on the magnitude of the output current.

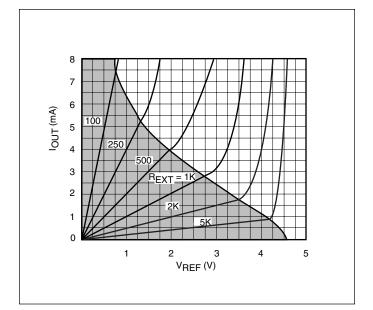

Given  $I_{_{OUT}}$  and  $V_{_{REF}}$ , the  $R_{_{EXT}}$  can be calculated by using:

$$R_{EXT} = \frac{V_{REF}}{I_{REF}} = \frac{V_{REF}}{I_{OUT}}$$

The intersection of a set of I<sub>OUT</sub> and V<sub>REF</sub> values can be located in the graph shown below. The value picked for R<sub>EXT</sub> must always be in the shaded area for linear operation. This control method has the advantage that V<sub>REF</sub> is positive, and draws only leakage current. If R<sub>EXT</sub> > 10K, add series network R<sub>D</sub> and C<sub>D</sub> to ground for stability as shown.

Note: Lower reference current  $I_{_{\text{REF}}}$  results in higher distortion,  $\Delta I_{_{\text{CS}}}$  on the output.

03/12/02

1235 Bordeaux Drive, Sunnyvale, CA 94089 TEL: (408) 744-0100 • FAX: (408) 222-4895 www.supertex.com