#### **SECTION 13**

### **ELECTRICAL SPECIFICATIONS**

This section contains the electrical specifications and associated timing information for the MC68HC11G5.

## 13.1 MAXIMUM RATINGS <sup>†</sup>

| Rating                                        | Symbol           | Value                                             | Unit        |

|-----------------------------------------------|------------------|---------------------------------------------------|-------------|

| Supply Voltage                                | ۷ <sub>DD</sub>  | - 0.5 to 7.0                                      | ٧           |

| Input Voltage                                 | V <sub>in</sub>  | V <sub>SS</sub> – 0.5 to<br>V <sub>DD</sub> + 0.5 | <b>&gt;</b> |

| Operating Temperature Range                   | Тд               | T <sub>L</sub> to T <sub>H</sub> - 40 to 85       | °C          |

| Storage Temperature Range                     | T <sub>stg</sub> | - 65 to 150                                       | °C          |

| Current Drain per Pin * Excluding VDD and VSS | ΙD               | 25                                                | mA          |

<sup>\*</sup> One pin at a time, observing maximum power dissipation limits.

<sup>†</sup> This device contains protective circuitry against damage due to high static voltages or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (eg. either GND or VDD).

### 13.2 THERMAL CHARACTERISTICS

| Characteristic             | Symbol | Value | Unit |

|----------------------------|--------|-------|------|

| Thermal Resistance Plastic | θJΑ    | 50    | °C/W |

#### 13.3 POWER CONSIDERATIONS

The average chip junction temperature, T<sub>J</sub>, in degrees Celsius can be obtained from the following equation:

$$T_{J} = T_{A} + (P_{D} \bullet \theta_{JA}) \tag{1}$$

Where:

T<sub>A</sub> = Ambient temperature (°C)

θ<sub>JA</sub> = Package thermal resistance, junction-to-ambient (<sup>O</sup>C/W)

$P_D = P_{INT} + P_{I/O}$

$P_{INT}$  = Internal chip power =  $I_{DD} \times V_{DD}$  (W)

$P_{UO}$  = Power dissipation on input and output pins (W) — user determined)

Note: For most applications P<sub>I/O</sub> < P<sub>INT</sub> and can be neglected.

An approximate relationship between PD and TJ (if PI/O is neglected) is:

$$P_D = K + (T_J + 273^{\circ}C)$$

(2)

Solving equations (1) and (2) for K gives:

$$K = P_D \bullet (T_A + 273^{\circ}C) + \theta_{JA} \bullet P_D^2$$

(3)

Where K is a constant pertaining to the particular part. K can be determined from equation (3) by measuring  $P_D$  (at equilibrium) for known  $T_A$ . Using this value of K, the values of  $P_D$  and  $T_J$  can be obtained by solving equations (1) and (2) for any value of  $T_A$ .

### 13.4 DC ELECTRICAL CHARACTERISTICS

$(V_{DD} = 5.0 \text{ Vdc} \pm 10\%, V_{SS} = 0 \text{ Vdc}, T_A = T_L \text{ to } T_H \text{ unless otherwise noted})$

|                                                             | Characteristic                        | Symbol          | Min                   | Max             | Unit |

|-------------------------------------------------------------|---------------------------------------|-----------------|-----------------------|-----------------|------|

| Output Voltage                                              | Ail outputs                           | VOL             | _                     | 0.1             | V    |

| $I_{Load} = \pm 10.0 \mu A$ (See Note 1)                    | All outputs except RESET and MODA     | ۷он             | V <sub>DD</sub> -0.1  | _               |      |

| Output High Voltage                                         | All outputs except                    | Voн             | V <sub>DD</sub> - 0.8 | _               | V    |

| I <sub>Load</sub> = - 0.8mA, V <sub>DD</sub> = 4.5V (See No | ote 1) RESET, XTAL and MODA           |                 |                       |                 |      |

| Output Low Voltage                                          | All outputs except XTAL               | VOL             | _                     | 0.4             | V    |

| ILoad = 1.6mA                                               |                                       |                 |                       |                 |      |

| Input High Voltage                                          | RESET                                 | VIH             | 0.8 x V <sub>DD</sub> | VDD             | V    |

|                                                             | All inputs except RESET               | VIH             | 0.7 x V <sub>DD</sub> | ۷ <sub>DD</sub> |      |

| Input Low Voltage                                           | All Inputs                            | VIL             | _                     | 0.8             | V    |

| ILoad = 1.6mA                                               |                                       |                 |                       |                 |      |

| I/O Ports, Three-state Leakage                              | PA0-7, PC0-7, PD0-5, PG0-7,           | loz             | _                     | ±10             | μΑ   |

| Vin = VIH or VIL                                            | PH0-7, PJ0-3, MODA/LIR, RESET         |                 |                       |                 |      |

| Input Current                                               | All Inputs                            | l <sub>in</sub> | _                     | ±1.0            | μΑ   |

| Vin = VDD or VSS                                            |                                       |                 |                       |                 |      |

| RAM Standby Voltage                                         | Powerdown                             | V <sub>SB</sub> | 2.0                   | $v_{DD}$        | V    |

| RAM Standby Current                                         | Powerdown                             | ISB             | _                     | 20              | μΑ   |

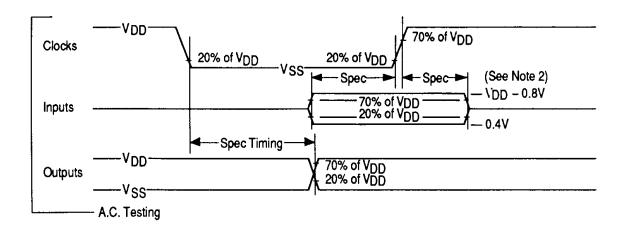

| Total Supply Current (See Note 2)                           |                                       | <sup>I</sup> DD |                       |                 |      |

| RUN:                                                        |                                       |                 |                       |                 |      |

| Single-Chip Mode                                            | IDD (run)                             |                 | _                     | 30              | mA   |

| WAIT: (All Peripheral Functions Shut                        | Down)                                 |                 |                       |                 |      |

| Single-Chip Mode                                            | I <sub>DD</sub> (wait)                |                 | _                     | 15              | mA   |

| STOP: (No Clocks)                                           |                                       |                 |                       |                 | 1    |

| Single-Chip Mode                                            | I <sub>DD</sub> (stop)                |                 | _                     | 100             | μΑ   |

| Input Capacitance                                           | ĪRQ, XIRQ, EXTAL                      | C <sub>in</sub> | _                     | 12              | pF   |

| MOD                                                         | A/LIR, RESET, all Ports except Port E | Cin             | _                     | 12              | pF   |

#### NOTES:

1. V<sub>OH</sub> specification for RESET and MODA is not applicable because they are open-drain pins.

VOH specification is not applicable to ports C and D in wired-OR mode.

2. All ports configured as inputs,

$V_{IL} \leq 0.2V$ ,

$V_{IL} \ge V_{DD} - 0.2V$

No dc loads,

EXTAL is driven with a square wave, and

$t_{CYC}$  = 476.5ns.

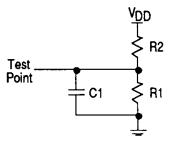

## Equivalent Test Load 1

| Pins                               | R1     | R2     | C1    |

|------------------------------------|--------|--------|-------|

| PA0-7, PB0-7, PC0-7, PD0, PD5,     | 3.26kΩ | 2.38kΩ | 90pF  |

| PF0-7, PG0-7, PH0-7, PJ0-3, E, R/W |        |        |       |

| PD1-PD4                            | 3.26kΩ | 2.38kΩ | 200pF |

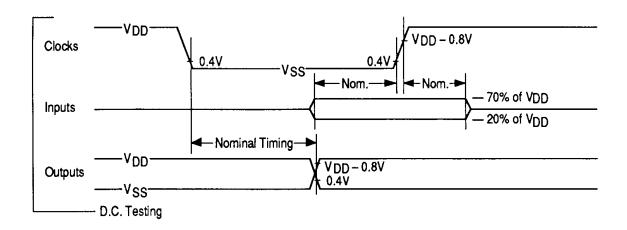

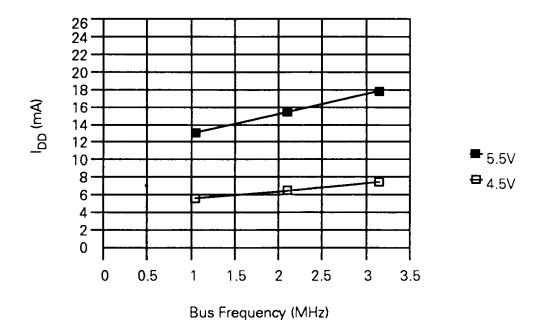

Notes: 1. Full test loads are applied during all DC electrical tests and AC timing measurements.

2. During AC timing measurements, inputs are driven to 0.4 volts and VDD – 0.8 volts while timing measurements are taken at the 20% and 70% of VDD points.

Figure 13-1. Test Methods

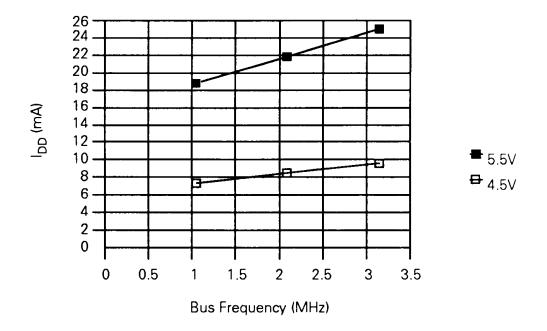

Figure 13-2. Run I<sub>DD</sub> vs Bus Frequency (Single Chip Mode – 4.5V, 5.5V)

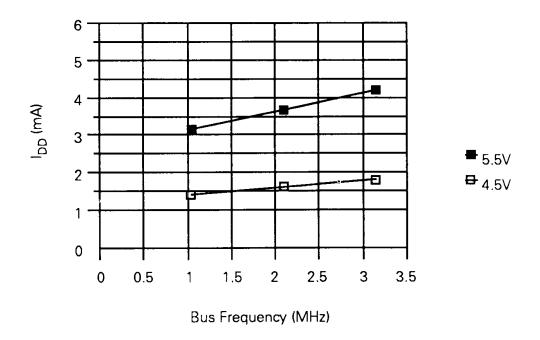

Figure 13-3. Run I<sub>DD</sub> vs Bus Frequency (Expanded Mode – 4.5V, 5.5V)

Downloaded from Elcodis.com electronic components distributor

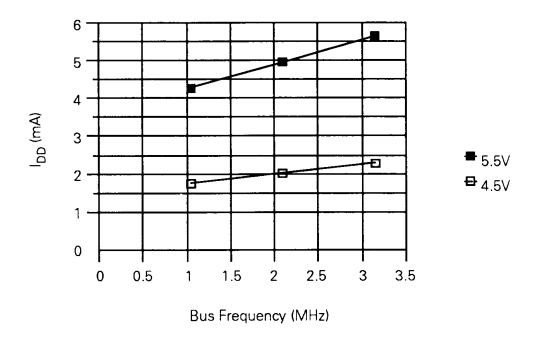

Figure 13-4. Wait I<sub>DD</sub> vs Bus Frequency (Single Chip Mode – 4.5V, 5.5V)

Figure 13-5. Wait I<sub>DD</sub> vs Bus Frequency (Expanded Mode – 4.5V, 5.5V)

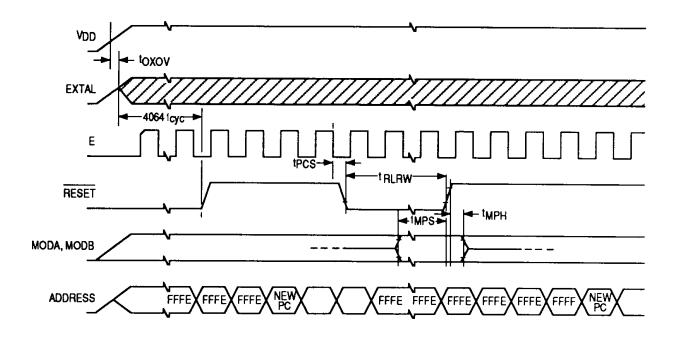

### 13.5 CONTROL TIMING

( $V_{DD}$  = 5.0 Vdc ± 10%,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$  unless otherwise noted)

|                                                                                                                                       |                                                                      | Symbol                   | Min           | Max        | Unit                                 |

|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------|---------------|------------|--------------------------------------|

| External Oscillator Frequency                                                                                                         | Crystal option<br>External clock option                              | fXTAL<br>4f <sub>o</sub> | _<br>DC       | 8.4<br>8.4 | MHz<br>MHZ                           |

| Internal Operating Frequency                                                                                                          | Crystal (f <sub>XTAL</sub> /4)<br>External clock                     | fo<br>fo                 | <br>DC        | 2.1<br>2.1 | MHz<br>MHZ                           |

| Cycle Time                                                                                                                            | All outputs except XTAL                                              | tcyc                     | 476           |            | ns                                   |

| Crystal Oscillator Startup Time                                                                                                       |                                                                      | toxov                    | _             | 100        | ms                                   |

| Stop Recovery Startup Time                                                                                                            | DLY = 0<br>DLY = 1                                                   | tsrs<br>tsrs             | _             | 4<br>4064  | t <sub>cyc</sub><br>t <sub>cyc</sub> |

| Wait Recovery Startup Time                                                                                                            |                                                                      | twrs                     |               | 4          | tcyc                                 |

| Reset Input Pulse Width (See Note 1)  (To guarantee external reset vector)  (Minimum input time; may be pre-empted by internal reset) |                                                                      | trlrh                    | 8<br>1        | _<br>_     | <sup>†</sup> cyc                     |

| Mode Programming                                                                                                                      | Setup time<br>Hold time                                              | tMPS<br>tMPH             | 2<br>0        |            | t <sub>cyc</sub>                     |

| Interrupt Pulse Width, IRQ Edge Sensitive Mode                                                                                        | tiLIH = t <sub>cyc</sub> + 20ns                                      | tiLiH                    | 496           | _          | ns                                   |

| Interrupt Pulse Period                                                                                                                |                                                                      | tjLjL                    | Note 2        |            | tcyc                                 |

| Processor Control RESET, WAIT, IRQ MRDY                                                                                               | (tpcs = 1/4 t <sub>cyc</sub> - 50ns)                                 | tPCS<br>tPCS             | 69<br>50      | _          | ns<br>ns                             |

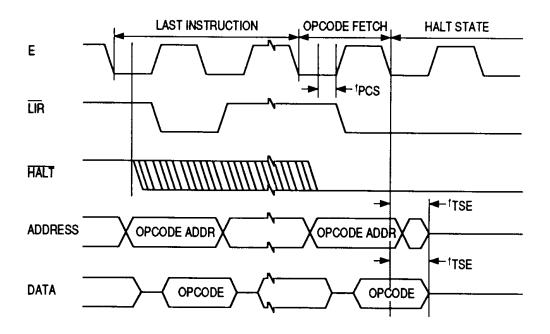

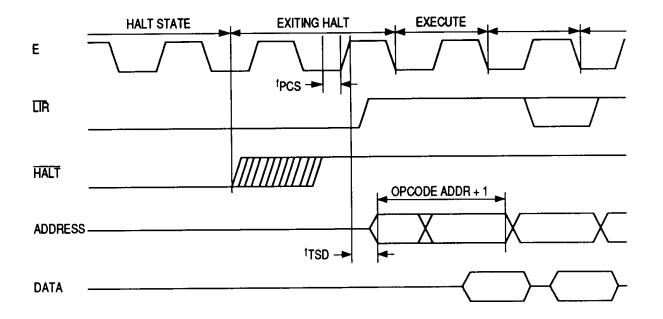

| HALT<br>Bus Tri State Enable<br>Bus Tri State Disable                                                                                 | $(t_{PCS} = 1/4 t_{CyC} + 20ns)$<br>$(t_{TSE} = 1/4 t_{CyC} + 40ns)$ | tPCS<br>tTSE<br>tTSD     | 170<br>—<br>— | 159<br>65  | ns<br>ns<br>ns                       |

#### NOTES:

- RESET will be recognised during the first clock cycle it is held low. Internal circuitry then drives the pin low for four clock cycles, releases the pin, and samples the pin level two cycles later to determine the source of the interrupt.

- 2. The minimum period t |L|L should not be less than the number of cycles it takes to execute the interrupt service routine plus 21 t cyc.

- 3. All timing is shown with respect to 20% V  $_{DD}$  and 70%  $_{DD}$  unless otherwise noted.

Figure 13-6. POR External RESET Timing Diagram

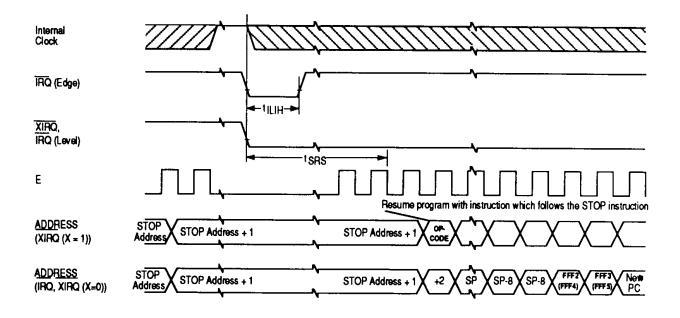

Figure 13-7. STOP Recovery Timing Diagram

Figure 13-8. WAIT Recovery from Interrupt Timing Diagram

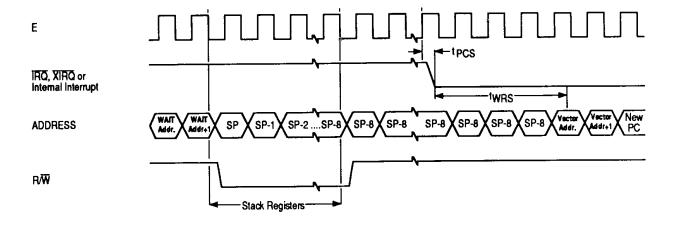

Figure 13-9. Interrupt Timing Diagram

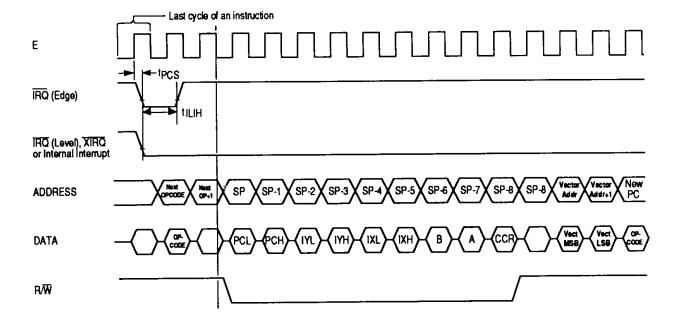

Figure 13-10. Memory Ready Timing Diagram

Figure 13-11. Entering HALT

Figure 13-12. Exiting HALT

### 13.6 PERIPHERAL PORT CHARACTERISTICS

(VDD = 5.0 Vdc  $\pm$  10%, VSS = 0 Vdc,  $T_A = T_L$  to  $T_H$  unless otherwise noted)

| Characteristic Frequency of Operation (E Clock) |                                        | Symbol | Min        | Max | Unit |

|-------------------------------------------------|----------------------------------------|--------|------------|-----|------|

|                                                 |                                        | fo     | _          | 2.1 | MHz  |

| E Clock Period                                  |                                        | tcyc   | 476        | _   | ns   |

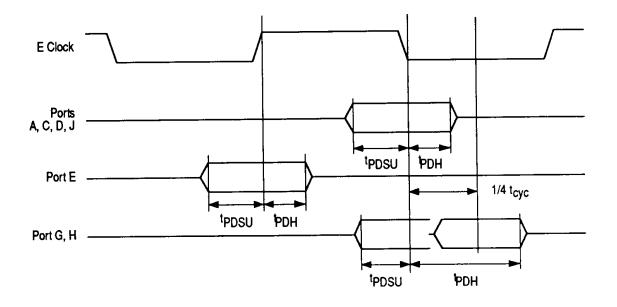

| Peripheral Data Setup Time                      |                                        |        | ) <u> </u> | 4   |      |

| Port A, C, D, J                                 |                                        | tPDSU  | 100        |     | ns   |

| Port E                                          |                                        | tPDSU  | 100        | _   | ns   |

| Port G, H                                       | (tpDSU = -1/4 t <sub>cyc</sub> + 93ns) | tPDSU  | - 26       |     | ns   |

| Peripheral Data Hold Time                       |                                        |        |            |     |      |

| Port A, C, D, J                                 |                                        | tPDH   | 80         | _   | ns   |

| Port E                                          |                                        | tPDH   | 80         | _   | ns   |

| Port G, H                                       | (tPDH = 1/4 t <sub>cyc</sub> + 130ns)  | tPDH   | 249        |     | ns   |

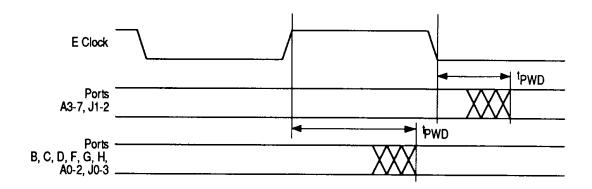

| Delay Time, Peripheral Data Write               |                                        |        |            |     |      |

| Port J1, J2, A3, A4, A5, A6, A7                 |                                        | tPWD   | _          | 150 | ns   |

| Port B, C, D, F, G, H, A0, A1, A2, J0, J3       | (tpwD= 1/4 t <sub>cyc</sub> + 90ns)    | tPWD   | _          | 209 | ns   |

#### NOTES:

1. All timing is shown with respect to 20% V  $_{DD}$  and 70% V  $_{DD}$  unless otherwise noted.

Figure 13-13. Port Write Timing Diagram

Figure 13-14. Port Read Timing Diagram

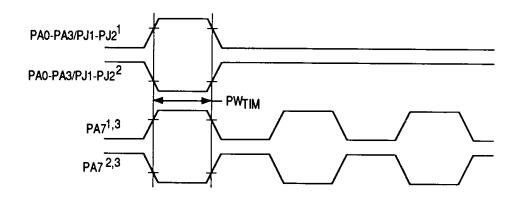

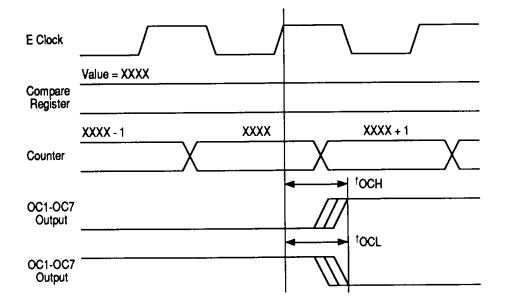

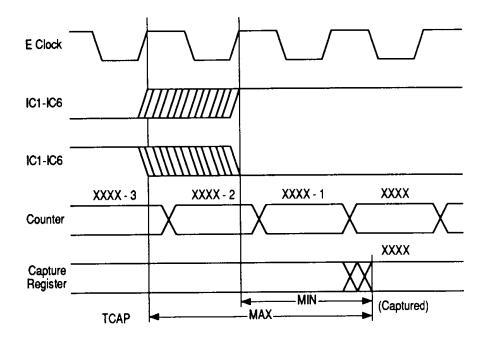

#### 13.7 **TIMER CHARACTERISTICS**

$(V_{DD} = 5.0 \text{ Vdc} \pm 10\%, V_{SS} = 0 \text{ Vdc}, T_A = T_L \text{ to } T_H \text{ unless otherwise noted})$

| Characteristic                                          |                                   | Symbol           | Min | Max  | Unit |

|---------------------------------------------------------|-----------------------------------|------------------|-----|------|------|

| Timer Pulse Width Input Capture Pulse Accumulator Input | (PWTIM = t <sub>cyc</sub> + 20ns) | PWTIM            | 496 |      | ns   |

| Timer Output Compare High Valid                         |                                   | toch             | _   | 310  | ns   |

| Timer Output Compare Low Valid                          |                                   | tocl             | _   | 295  | ns   |

| Timer Input Capture Response Delay  Min = t cyc + 20ns  |                                   | <sup>t</sup> CAP | 496 | 1172 | ns   |

#### NOTES:

1. All timing is shown with respect to 20% V DD and 70% VDD unless otherwise noted.

### Notes:

- Rising edge sensitive input.

Failing edge sensitive input.

Maximum pulse accumulator clocking rate is E frequency divided by 2.

Figure 13-15. Timer Inputs Timing Diagram

Figure 13-16. Output Compare Timing Diagram

Figure 13-17. Input Capture Timing Diagram

### 13.8 A/D CONVERTER CHARACTERISTICS

$(V_{DD} = 5.0 \text{ Vdc} \pm 10\%, V_{SS} = 0 \text{ Vdc}, T_A = T_L \text{ to } T_H, E = 750 \text{kHz to } 2.1 \text{MHz unless otherwise noted})$

|                                         |                                                                                                                                          |                       | ,        |                           |                        |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------|---------------------------|------------------------|

| Characteristic                          | Parameter                                                                                                                                | Min                   | Absolute | Max                       | Unit                   |

| Resolution                              | Number of bits resolved by the A/D                                                                                                       | 10                    |          | _                         | Bits                   |

| Nonlinearity                            | Maximum deviation from the ideal A/D transfer characteristics                                                                            |                       | _        | TBD                       | LSB                    |

| Zero Error                              | Difference between the output of an ideal and an actual A/D for zero input voltage                                                       | _                     |          | TBD                       | LSB                    |

| Full Scale Error                        | Difference between the output of an ideal and an actual A/D for full scale input voltage                                                 | _                     | _        | TBD                       | LSB                    |

| Total Unadjusted Error                  | Maximum sum of Nonlinearity, zero error and full scale error                                                                             | _                     | _        | TBD                       | LSB                    |

| Quantization Error                      | Uncertainty due to converter resolution                                                                                                  | _                     |          | ±0.5                      | LSB                    |

| Absolute Accuracy<br>(See Note 1)       | Difference between the actual input voltage and the full scale weighted equivalent of the binary output code, all error sources included | _                     |          | TBD                       | LSB                    |

| Conversion Range<br>(See Notes 3 and 4) | Analog input voltage range                                                                                                               | V <sub>rl</sub>       | _        | V <sub>rh</sub>           | ٧                      |

| V <sub>rh</sub> (See Note 2)            | Maximum analog reference voltage                                                                                                         | V <sub>rl</sub>       | _        | V <sub>DD</sub> + 0.1     | V                      |

| V <sub>rl</sub> (See Note 2)            | Minimum analog reference voltage                                                                                                         | V <sub>SS</sub> - 0.1 | _        | V <sub>rh</sub>           | ٧                      |

| Delta V <sub>r</sub> (See Note 2)       | Minimum difference between V <sub>rh</sub> and V <sub>rl</sub>                                                                           | 0                     | -        | _                         | ٧                      |

| Conversion Time                         | Total time to perform a single analog to digital conversion:  1. E Clock  2. Internal RC Oscillator                                      | _                     | 36<br>—  | <br>t <sub>cyc</sub> + 24 | <sup>t</sup> cyc<br>µs |

| Monotonicity                            | Conversion result never decreases with an increase in input voltage and has no missing codes                                             |                       | Guarar   | <u> </u>                  | μσ                     |

| Zero Input Reading<br>(See Note 3)      | Conversion result when V in = V <sub>rI</sub>                                                                                            | \$000                 | _        | _                         | Hex                    |

| Full Scale reading<br>(See Note 4)      | Conversion result when V in = V <sub>rh</sub>                                                                                            |                       | _        | \$3FF                     | Hex                    |

| Sample Acquisition Time                 | Analog Input Acquisition sampling time:  1. E Clock  2. Internal RC Oscillator                                                           | _                     | 13<br>—  | —<br>8.7                  | t <sub>cyc</sub><br>μs |

| Sample Hold Capacitance                 | Input capacitance during sample PE0-PE7                                                                                                  | _                     | 35 (Typ) | _                         | pF                     |

| Input Leakage                           | Input leakage on A/D pins:<br>PE0-PE7<br>Vrl, Vrh                                                                                        | <u> </u>              |          | 100<br>250                | nA<br>μA               |

#### NOTES:

- 1. Source impedances greater then  $10k\Omega$  will adversely affect accuracy, due mainly to input leakage.

- 2. Performance verified down to 2.5V Delta  $V_{f}$ , but accuracy is tested and guaranteed at Delta  $V_{f} = 5V \pm 10\%$ .

- 3. Minimum analog input voltage should not go below V  $_{\mbox{SS}}$  0.3V.

- 4. Maximum analog input voltage should not exceed 1.125V rh.

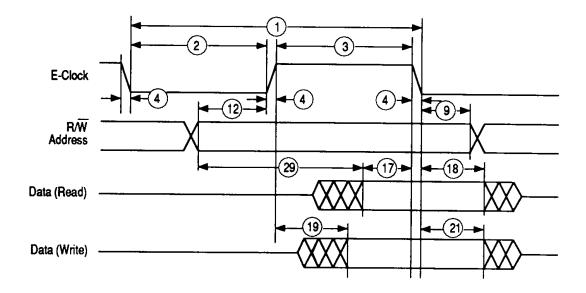

### 13.9 EXPANSION BUS TIMING

$(V_{DD} = 5.0 \text{ Vdc} \pm 10\%, V_{SS} = 0 \text{ Vdc}, T_A = T_L \text{ to } T_H \text{ unless otherwise noted})$

| Num | Characteristic                                                                         | Symbol                          | Min | Max | Unit |

|-----|----------------------------------------------------------------------------------------|---------------------------------|-----|-----|------|

|     | Frequency of Operation (E-Clock)                                                       | fo                              | _   | 2.1 | MHz  |

| 1   | Cycle Time                                                                             | t <sub>cyc</sub>                | 476 | _   | ns   |

| 2   | Pulse Width E Low (1/2 t <sub>cyc</sub> - 23ns)                                        | t ELEH                          | 215 | _   | ns   |

| 3   | Pulse Width E High (1/2 t <sub>cyc</sub> - 28ns)                                       | t EHEL                          | 210 | _   | ns   |

| 4   | E Rise and Fall Time                                                                   | t <sub>R</sub> , t <sub>F</sub> |     | 20  | ns   |

| 9   | Address Hold Time (t <sub>AH</sub> = 1/8 t <sub>cyc</sub> - 29.5ns)<br>(See Note 1(A)) | tAH                             | 30  |     | ns   |

| 12  | Address Valid Time to E Rise (See Note 1(B))                                           | tAV                             | 120 | _   | ns   |

| 17  | Read Data Setup Time                                                                   | tDSR                            | 30  | _   | ns   |

| 18  | Read Data Hold Time                                                                    | tDHR                            | 10  | _   | ns   |

| 19  | Write Data Delay Time                                                                  | tDDW                            | _   | 80  | ns   |

| 21  | Write Data Hold Time                                                                   | tDHW                            | 50  |     | ns   |

| 29  | MPU Address Access Time (tACCA = tAV + tR + tEHEL - tDSR (See Note 1(A))               | tACCA                           | 320 |     | ns   |

#### NOTES:

- 1. Input clock with duty cycle other than 50% will affect the bus performance. Timing parameters affected by the input clock duty cycle are identified by (A) and (B). To re-calculate approximate bus timing values, substitute the following expressions in place of 1/8 t cyc in the above formulae where applicable:

- (A) (1-DC) x 1/4 t cyc

- (B) DC x 1/4t<sub>cvc</sub>

where DC is the decimal value of duty cycle percentage (High time).

2. All timing is shown with respect to 20% V DD and 70% VDD.

Figure 13-18. Non-multiplexed Expanded Bus

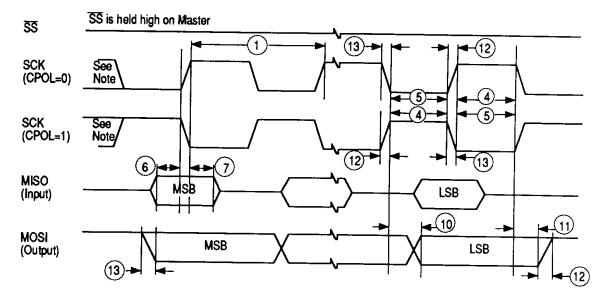

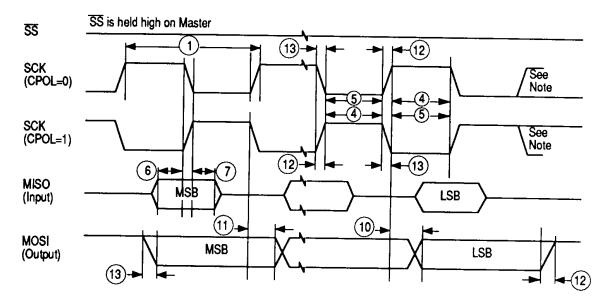

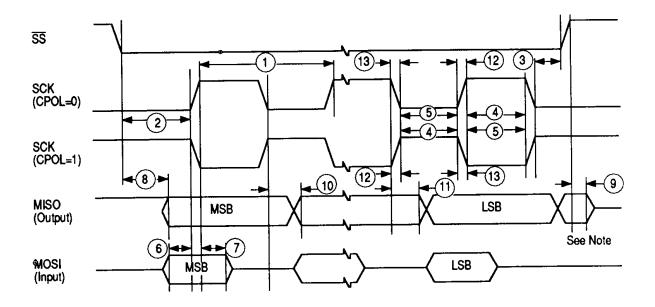

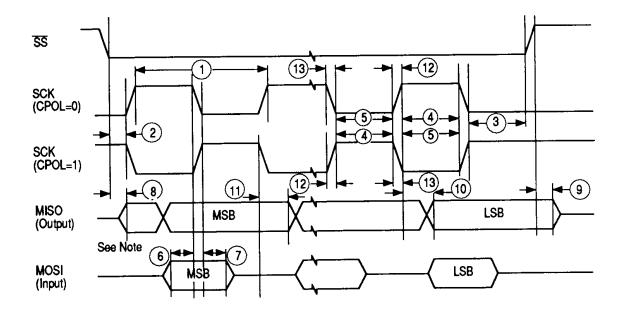

# 13.10 SERIAL PERIPHERAL INTERFACE (SPI) TIMING

$(V_{DD} = 5.0 \text{ Vdc} \pm 10\%, V_{SS} = 0 \text{ Vdc}, T_A = T_L \text{ to } T_H \text{ unless otherwise noted})$

| Num | Characteristic                                                                                                                                       |                 | Symbol                                       | Min        | Max        | Unit                  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------------------------------|------------|------------|-----------------------|

|     | Operating Frequency                                                                                                                                  | Master<br>Slave | fop(m)<br>fop(s)                             | dc<br>dc   | 0.5<br>2.1 | f <sub>o</sub><br>MHz |

| 1   | Cycle Time                                                                                                                                           | Master<br>Slave | tcyc(m)<br>tcyc(s)                           | 2.0<br>480 | _<br>      | t <sub>cyc</sub>      |

| 2   | Enable Lead Time                                                                                                                                     | Master<br>Slave | <sup>t</sup> lead(m)<br><sup>t</sup> lead(s) | •<br>240   | _<br>      | ns<br>ns              |

| 3   | Enable Lag Time                                                                                                                                      | Master<br>Slave | tlag(m)<br>tlag(s)                           | 240        | _<br>_     | ns<br>ns              |

| 4   | Clock (SCK) High Time                                                                                                                                | Master<br>Slave | tw(SCKH)m                                    | 340<br>190 | _<br>_     | ns<br>ns              |

| 5   | Clock (SCK) Low Time                                                                                                                                 | Master<br>Slave | tw(SCKL)m<br>tw(SCKL)s                       | 340<br>190 | <u>-</u>   | ns<br>ns              |

| 6   | Data Setup Time                                                                                                                                      | Master<br>Slave | t <sub>su(m)</sub><br>t <sub>su(s)</sub>     | 100<br>100 | _<br>      | ns<br>ns              |

| 7   | Data Hold Time                                                                                                                                       | Master<br>Slave | <sup>t</sup> h(m)<br><sup>t</sup> h(s)       | 100<br>100 | _<br>      | ns<br>ns              |

| 8   | Access Time (Time to Data Active from High-Impedance State)                                                                                          | Slave           | t <sub>a</sub>                               | 0_         | 120        | ns                    |

| 9   | Disable Time<br>(Hold Time to High-Impedance State)                                                                                                  | Slave           | <sup>†</sup> dis                             |            | 240        | ns                    |

| 10  | Data Valid (After Enable Edge)**                                                                                                                     |                 | tv(s)                                        |            | 240        | ns                    |

| 11  | Data Hold Time (Outputs) (After Enable Edge)                                                                                                         |                 | tho                                          | - 40       |            | ns                    |

| 12  | Rise Time (20% V DD to 70% VDD, CL = 200pF) SPI Outputs (SCK, MOSI, MISO) SPI Inputs (SCK, MOSI, MISO, SS)                                           |                 | tr(m)                                        | _<br>      | 100<br>2.0 | ns<br>µs              |

| 13  | Fall Time (70% V <sub>DD</sub> to 20% V <sub>DD</sub> , C <sub>L</sub> = 200pF)<br>SPI Outputs (SCK, MOSI, MISO)<br>SPI Inputs (SCK, MOSI, MISO, SS) |                 | tf(m)                                        | _<br>      | 100<br>2.0 | ns<br>µs              |

#### NOTES:

- Signal production depends on software.

- \*\* Assumes 200 pF load on all SPI pins.

- 1. All timing is shown with respect to 20% V DD and 70% V DD unless otherwise noted.

Note: This first edge is generated internally but is not seen at the SCK pin.

Figure 13-19. SPI Master Timing (CPHA = 0)

Note: This last edge is generated internally but is not seen at the SCK pin.

Figure 13-20. SPI Master Timing (CPHA = 1)

Note: Not defined but normally MSB of character just received.

Figure 13-21. SPI Slave Timing (CPHA = 0)

Note: Not defined but normally LSB of character previously transmitted.

Figure 13-22. SPI Slave Timing (CPHA = 1)

### 13.11 EVENT COUNTER CHARACTERISTICS

Table 13.1. Clock Input (Required Limit)

### Clock Input (Required Limit)

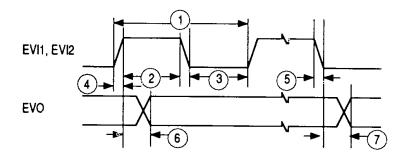

| Num | Characteristic                     | Symbol | Min                  | Max                   | Unit |

|-----|------------------------------------|--------|----------------------|-----------------------|------|

| 1   | Cycle Time of External Clock Input | tcycex | 3xt <sub>cyc</sub>   | _                     | ns   |

| 2   | Clock High Time                    | twckh  | 1.5xt <sub>cyc</sub> |                       | ns   |

| 3   | Clock Low Time                     | twckl  | 1xt <sub>cyc</sub>   | _                     | ns   |

| 4   | Rise Time                          | trck   | _                    | 0.25xt <sub>cyc</sub> | ns   |

| 5   | Fall Time                          | tfck   | _                    | 0.25xt <sub>cyc</sub> | ns   |

Table 13.2. Clock Input (Guaranteed Limit)

### **Clock Input (Guaranteed Limit)**

| Num | Characteristic                                     | Symbol | Min                  | Max                        | Unit |

|-----|----------------------------------------------------|--------|----------------------|----------------------------|------|

| 6   | Propagation Delay External Clock Rise to EVO Valid | tovr   | 1.5xt <sub>cyc</sub> | 2.5xt <sub>cyc</sub> + 240 | ns   |

| 7   | Propagation Delay External Clock Fall to EVO Valid | tovf   | 1.5xt <sub>cyc</sub> | 2.5xt <sub>cyc</sub> + 240 | ns   |

Figure 13-23. Event Counter Mode 1, 2, 3 - Clock Input Timing Diagram

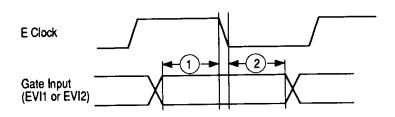

Table 13.3. Clock Gate Input (Guaranteed Limit)

Clock Gate Input (Required Limit)

| Num | Characteristic                  | Symbol           | Min                   | Max | Unit |

|-----|---------------------------------|------------------|-----------------------|-----|------|

| 1   | Gate Input Setup Time to E Fall | tgsu             | 0.25xt <sub>cyc</sub> |     | ns   |

| 2   | Gate Input Hold Time to E Fall  | <sup>t</sup> gh_ | 0.5xt <sub>cyc</sub>  |     | ns   |

Figure 13-24. Event Counter Mode 1, 2, 3 - Clock Gate Input Timing Diagram