## **Preliminary**

## X3100/X3101

## 4 cell / 3 cell

## 3 or 4 Cell Li-Ion Battery Protection and Monitor IC

#### **FEATURE**

- Software Selectable Protection Levels and Variable Protect Detection/Release Times

- Integrated FET Drive Circuitry

- Cell Voltage and Current Monitoring

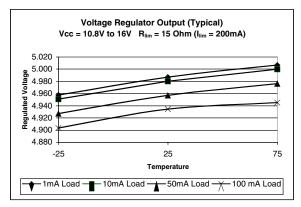

- 0.5% Accurate Voltage Regulator

- Integrated 4kbit EEPROM

- Flexible Power Management with 1µA Sleep Mode

- Cell Balancing Control

#### **BENEFIT**

- Optimize protection for chosen cells to allow maximum use of pack capacity.

- Reduce component count and cost

- . Simplify implementation of gas gauge

- Accurate voltage and current measurements

- Record battery history to optimize gas gauge, track pack failures and monitor system use

- · Reduce power to extend battery life

- Increase battery capacity and improve cycle life battery life

#### **DESCRIPTION**

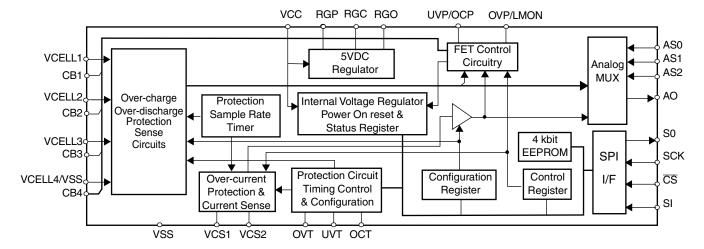

The X3100 is a protection and monitor IC for use in battery packs consisting of 4 series Lithium-Ion battery cells. The X3101 is designed to work in 3 cell applications. Both devices provide internal overcharge, over-discharge, and over-current protection circuitry, internal EEPROM memory, an internal voltage regulator, and internal drive circuitry for external FET devices that control cell charge, discharge, and cell voltage balancing.

Over-charge, over-discharge, and over-current thresholds reside in an internal EEPROM memory register and are selected independently via software using a 3MHz SPI serial interface. Detection and timeout delays can also be individually varied using external capacitors.

Using an internal analog multiplexer, the X3100 or X3101 allow battery parameters such as cell voltage and current (using a sense resistor) to be monitored externally by a separate microcontroller with A/D converter. Software on this microcontroller implements gas gauge and cell balancing functionality in software.

The X3100 and X3101 contain a current sense amplifier. Selectable gains of 10, 25, 80 and 160 allow an external 10 bit A/D converter to achieve better resolution than a more expensive 14 bit converter.

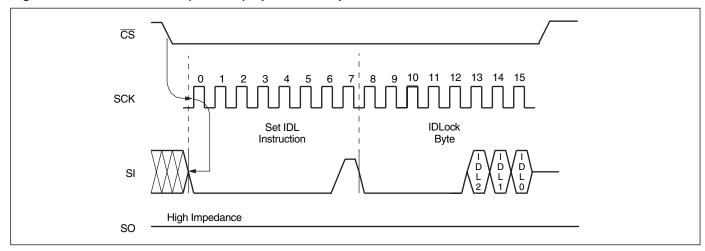

An internal 4kbit EEPROM memory featuring  $IDLock^{TM}$ , allows the designer to partition and "lock in" written battery cell/pack data.

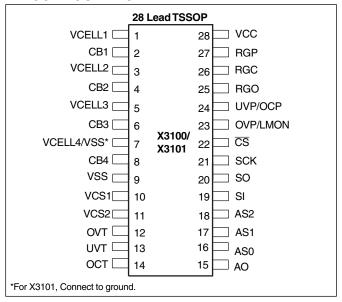

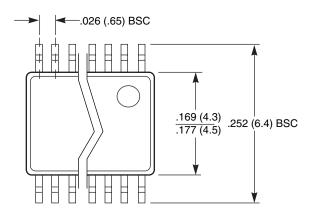

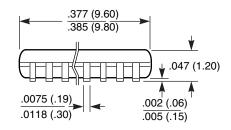

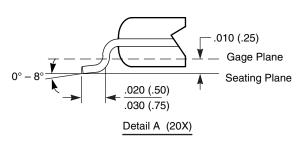

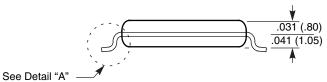

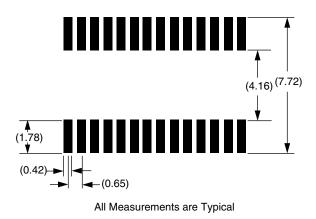

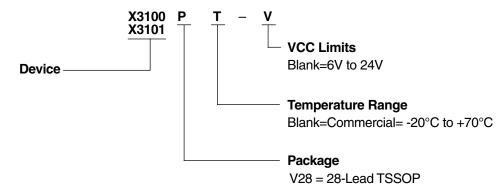

The X3100 and X3101 are each housed in a 28 Pin TSSOP package.

#### **FUNCTIONAL DIAGRAM**

#### PRINCIPLES OF OPERATION

The X3100 and X3101 provide two distinct levels of functionality and battery cell protection:

First, in Normal mode, the device periodically checks each cell for an over-charge and over-discharge state, while continuously watching for a pack over-current condition. A protection mode violation results from an over-charge, over-discharge, or over-current state. The thresholds for these states are selected by the user through software. When one of these conditions occur, a Discharge FET or a Charge FET or both FETs are turned off to protect the battery pack. In an over-discharge condition, the X3100 and X3101 devices go into a low power sleep mode to conserve battery power. During sleep, the voltage regulator turns off, removing power from the microcontroller to further reduce pack current.

Second, in Monitor mode, a microcontroller with A/D converter measures battery cell voltage and pack current via pin AO and the X3100 or X3101 on-board MUX. The user can thus implement protection, charge/discharge, cell balancing or gas gauge software algorithms to suit the specific application and characteristics of the cells used. While monitoring these voltages, all protection circuits are on continuously.

In a typical application, the microcontroller is also programmed to provide an SMBus interface along with the Smart Battery System interface protocols. These additions allow an X3100 or X3101 based module to adhere to the latest industry battery pack standards.

#### PIN CONFIGURATION

#### **PIN NAMES**

| Pin | Symbol         | Description                                                         |

|-----|----------------|---------------------------------------------------------------------|

| 1   | VCELL1         | Battery cell 1 voltage input                                        |

| 2   | CB1            | Cell balancing FET control output 1                                 |

| 3   | VCELL2         | Battery cell 2 voltage                                              |

| 4   | CB2            | Cell balancing FET control output 2                                 |

| 5   | VCELL3         | Battery cell 3 voltage                                              |

| 6   | CB3            | Cell balancing FET control output 3                                 |

| 7   | VCELL4/<br>VSS | Battery cell 4 voltage (X3100)<br>Ground (X3101)                    |

| 8   | CB4            | Cell balancing FET control output 4                                 |

| 9   | VSS            | Ground                                                              |

| 10  | VCS1           | Current sense voltage pin 1                                         |

| 11  | VCS2           | Current sense voltage pin 2                                         |

| 12  | OVT            | Over-charge detect/release time input                               |

| 13  | UVT            | Over-discharge detect/release time input                            |

| 14  | OCT            | Over-current detect/release time input                              |

| 15  | AO             | Analog multiplexer output                                           |

| 16  | AS0            | Analog output select pin 0                                          |

| 17  | AS1            | Analog output select pin 1                                          |

| 18  | AS2            | Analog output select pin 2                                          |

| 19  | SI             | Serial data input                                                   |

| 20  | SO             | Serial data output                                                  |

| 21  | SCK            | Serial data clock input                                             |

| 22  | <del>CS</del>  | Chip select input pin                                               |

| 23  | OVP/<br>LMON   | Over-charge Voltage Protection output/<br>Load Monitor output       |

| 24  | UVP/<br>OCP    | Over-discharge protection output/<br>Over-current protection output |

| 25  | RGO            | Voltage regulator output pin                                        |

| 26  | RGC            | Voltage regulator control pin                                       |

| 27  | RGP            | Voltage regulator protection pin                                    |

| 28  | VCC            | Power supply                                                        |

#### **PIN DESCRIPTIONS**

#### **Battery Cell Voltage (VCELL1-VCELL4):**

These pins are used to monitor the voltage of each battery cell internally. The voltage of an individual cell can also be monitored externally at pin AO.

The X3100 monitors 4 battery cells. The X3101 monitors 3 battery cells. For the X3101 device connect the VCELL4/VSS pin to ground.

#### Cell Voltage Balancing Control (CB1-CB4):

These outputs are used to switch external FETs in order to perform cell voltage balancing control. This function can be used to adjust individual cell voltages (e.g. during cell charging). CB1–CB4 can be driven high (Vcc) or low (Vss) to switch external FETs ON/OFF. When using the X3101, the CB4 pin can be left unconnected, or the FET control can be used for other purposes.

#### Current Sense Inputs (VCS1-VCS2):

A sense resistor ( $R_{SENSE}$ ) is connected between VCS1 and VCS2 (Figure 1).  $R_{SENSE}$  has a resistance in the order of  $20m\Omega$  to  $100m\Omega$ , and is used to monitor current flowing through the battery terminals, and protect against over-current conditions. The voltage at each end of  $R_{SENSE}$  can also be monitored at pin AO.

#### Over-charge Voltage detect Time control (OVT):

This pin is used to control the delay time  $(T_{OV})$  associated with the detection of an over-charge condition (see section "Over-charge Protection" on page 13).

#### Over-discharge detect/release time control (UVT):

This pin is used to control the delay times associated with the detection  $(T_{UV})$  and release  $(T_{UVR})$  of an over-discharge (under-voltage) condition (see section "Over-discharge Protection" on page 15).

#### Over-current detect/release time control (OCT):

This pin is used to control the delay times associated with the detection ( $T_{OC}$ ) and release ( $T_{OCR}$ ) of an over-current condition (see section "Over-Current Protection" on page 18).

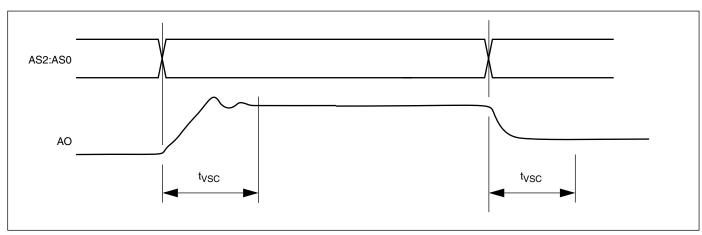

#### **Analog Output (AO):**

The analog output pin is used to externally monitor various battery parameter voltages. The voltages which can be monitored at AO (see section "Analog Multiplexer Selection" on page 20) are:

- Individual cell voltages

- Voltage across the current sense resistor (R<sub>SENSE</sub>).

This voltage is amplified with a gain set by the user in the control register (see section "Current Monitor Function" on page 20.)

The analog select pins pins AS0–AS2 select the desired voltage to be monitored on the AO pin.

#### Analog Output Select (AS0-AS2):

These pins select which voltage is to be multiplexed to the output AO (see section "Sleep Control (SLP)" on page 10 and section "Current Monitor Function" on page 20)

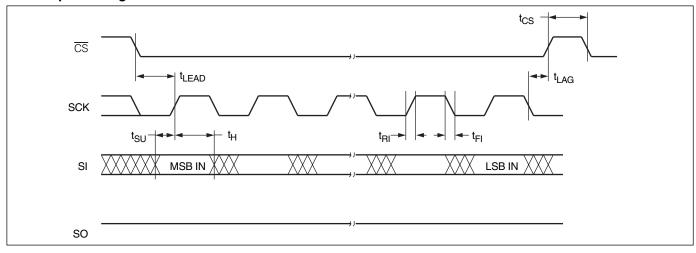

#### Serial Input (SI):

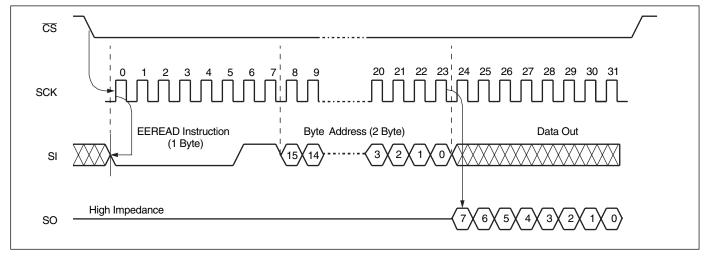

SI is the serial data input pin. All opcodes, byte addresses, and data to be written to the device are input on this pin.

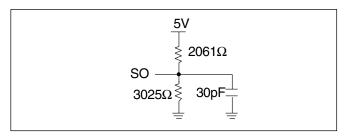

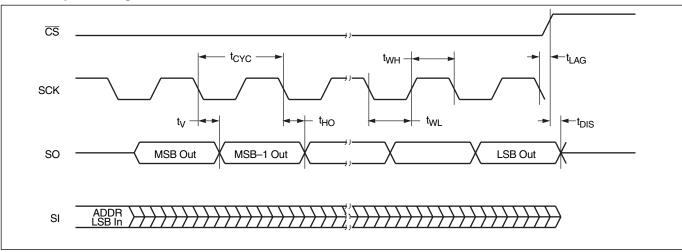

#### Serial Output (SO):

SO is a push/pull serial data output pin. During a read cycle, data is shifted out on this pin. Data is clocked out by the falling edge of the serial clock. While  $\overline{CS}$  is HIGH, SO will be in a High Impedance state.

**Note:** SI and SO may be tied together to form one line (SI/SO). In this case, all serial data communication with the X3100 or X3101 is undertaken over one I/O line. This is permitted ONLY if no simultaneous read/write operations occur.

#### Serial Clock (SCK):

The Serial Clock controls the serial bus timing for data input and output. Opcodes, addresses, or data present on the SI pin are latched on the rising edge of the clock input, while data on the SO pin change after the falling edge of the clock input.

#### Chip Select (CS):

When  $\overline{CS}$  is HIGH, the device is deselected and the SO output pin is at high impedance.  $\overline{CS}$  LOW enables the SPI serial bus.

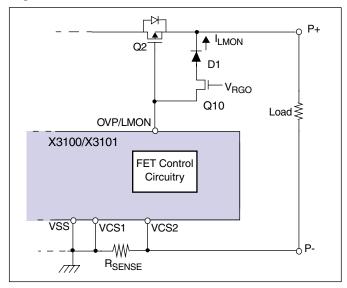

# Over-charge Voltage Protection/Load Monitor (OVP/LMON):

This one pin performs two functions depending upon the present mode of operation of the X3100 or X3101.

#### —Over-charge Voltage Protection (OVP)

This pin controls the switching of the battery pack charge FET. This power FET is a P-channel device. As such, cell charge is possible when OVP/LMON=V<sub>SS</sub>, and cell charge is prohibited when OVP/LMON=V<sub>CC</sub>. In this configuration the X3100 and X3101 turn off the charge voltage when the cells reach the over-charge limit. This prevents damage to the battery cells due to the application of charging voltage for an extended period of time (see section "Over-charge Protection" on page 13).

#### -Load Monitor (LMON)

In Over-current Protection mode, a small test current  $(7.5\mu A\ typ.)$  is passed out of this pin to sense the load resistance. The measured load resistance determines whether or not the X3100 or X3101 returns from an over-current protection mode (see section "Over-Current Protection" on page 18).

#### Over-discharge (Under Voltage) Protection/ Over-current Protection (UVP/OCP):

Pin UVP/OCP controls the battery cell discharge via an external power FET. This P-channel FET allows cell discharge when UVP/OCP=Vss, and prevents cell discharge when UVP/OCP=Vcc. The X3100 and X3101 turn the external power FET off when the X3100 or X3101 detects either:

#### —Over-discharge Protection (UVP)

In this case, pin 24 is referred to as "Over-discharge (Under-Voltage) protection (UVP)" (see section "Over-discharge Protection" on page 15). UVP/OCP turns off the FET to prevent damage to the battery cells by being discharged to excessively low voltages.

#### —Over-current protection (OCP)

In this case, pin 24 is referred to as "Over-current protection (OCP)" (see section "Over-Current Protection" on page 18). UVP/OCP turns off the FET to prevent damage to the battery pack caused by excessive current drain (e.g. as in the case of a surge current resulting from a stalled disk drive).

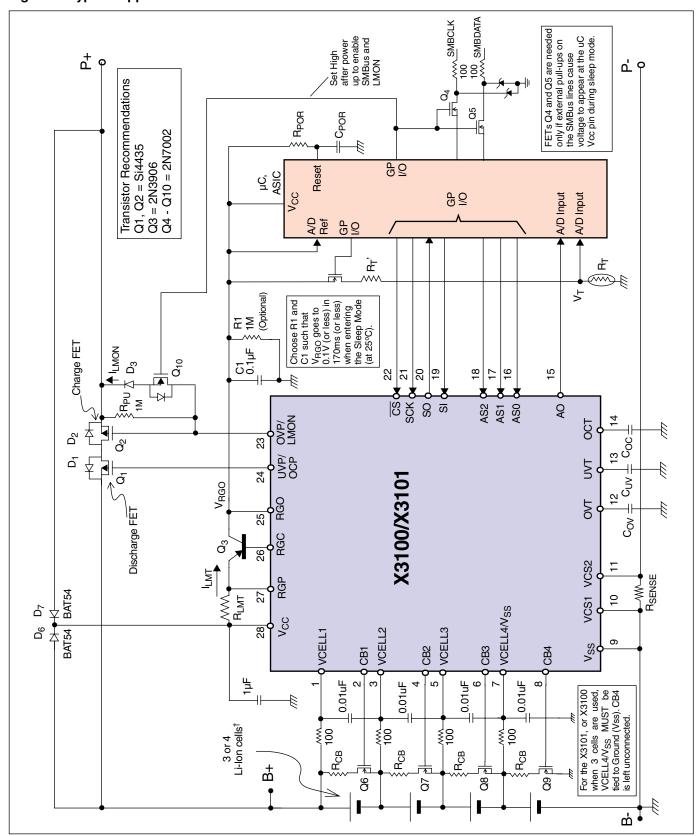

#### TYPICAL APPLICATION CIRCUIT

The X3100 and X3101 have been designed to operate correctly when used as connected in the Typical Application Circuit (see Figure 1 on page 5).

The power MOSFET's Q1 and Q2 are referred to as the "Discharge FET" and "Charge FET," respectively. Since these FETs are p-channel devices, they will be ON when the gates are at V<sub>SS</sub>, and OFF when the gates are at V<sub>CC</sub>. As their names imply, the discharge FET is used to control cell discharge, while the charge FET is used to control cell charge. Diode D1 allows the battery cells to receive charge even if the Discharge FET is OFF, while diode D2 allows the cells to discharge even if the charge FET is OFF. D1 and D2 are integral to the Power FETs. It should be noted that the cells can neither charge nor discharge if both the charge FET and discharge FET are OFF.

Power to the X3100 or X3101 is applied to pin VCC via diodes D6 and D7. These diodes allow the device to be

powered by the Li-lon battery cells in normal operating conditions, and allow the device to be powered by an external source (such as a charger) via pin P+ when the battery cells are being charged. These diodes should have sufficient current and voltage ratings to handle both cases of battery cell charge and discharge.

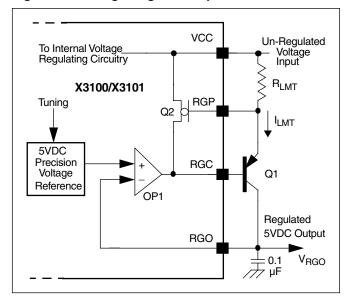

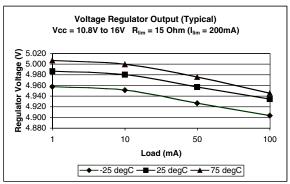

The operation of the voltage regulator is described in section "Voltage Regulator" on page 21. This regulator provides a 5VDC±0.5% output. The capacitor (C1) connected from RGO to ground provides some noise filtering on the RGO output. The recommended value is 0.1µF or less. The value chosen must allow  $V_{RGO}$  to decay to 0.1V in 170ms or less when the X3100 or X3101 enter the sleep mode. If the decay is slower than this, a resistor (R1) can be placed in parallel with the capacitor.

During an initial turn-on period ( $T_{PUR} + T_{OC}$ ),  $V_{RGO}$  has a stable, regulated output in the range of 5VDC  $\pm$  10% (see Figure 2). The selection of the microcontroller should take this into consideration. At the end of this turn on period, the X3100 and X3101 "self-tunes" the output of the voltage regulator to 5V+/-0.5%. As such,  $V_{RGO}$  can be used as a reference voltage for the A/D converter in the microcontroller. Repeated power up operations, consistently re-apply the same "tuned" value for  $V_{RGO}$ .

Figure 1 shows a battery pack temperature sensor implemented as a simple resistive voltage divider, utilizing a thermistor (R<sub>T</sub>) and resistor (R<sub>T</sub>'). The voltage  $V_T$  can be fed to the A/D input of a microcontroller and used to measure and monitor the temperature of the battery cells.  $R_T$ ' should be chosen with consideration of the dynamic resistance range of  $R_T$  as well as the input voltage range of the microcontroller A/D input. An output of the microcontroller can be used to turn on the thermistor divider to allow periodic turn-on of the sensor. This reduces power consumption since the resistor string is not always drawing current.

Diode D3 is included to facilitate load monitoring in an Over-current protection mode (see section "Over-Current Protection" on page 18), while preventing the flow of current into pin OVP/LMON during normal operation. The N-Channel transistor turns off this function during the sleep mode.

Resistor R<sub>PU</sub> is connected across the gate and drain of the charge FET (Q2). The discharge FET Q1 is turned off by the X3100 or X3101, and hence the voltage at pin OVP/LMON will be (at maximum) equal to the voltage of the battery terminal, minus one forward biased diode voltage drop ( $V_{P+}$ – $V_{D7}$ ). Since the drain of Q2 is connected to a higher potential ( $V_{P+}$ ) a pull-up resistor

**Figure 1. Typical Application Circuit**

$(R_{PU})$  in the order of 1M  $\!\Omega$  should be used to ensure that the charge FET is completely turned OFF when OVP/LMON=V $_{CC}$ .

The capacitors on the  $V_{CELL1}$  to  $V_{CELL4}$  inputs are used in a first order low pass filter configuration, at the battery cell voltage monitoring inputs (VCELL1–VCELL4) of the X3100 or X3101. This filter is used to block any unwanted interference signals from being inadvertently injected into the monitor inputs. These interference signals may result from:

- Transients created at battery contacts when the battery pack is being connected/disconnected from the charger or the host.

- Electrostatic discharge (ESD) from something/someone touching the battery contacts.

- Unfiltered noise that exists in the host device.

- RF signals which are induced into the battery pack from the surrounding environment.

Such interference can cause the X3100 or X3101 to operate in an unpredictable manner, or in extreme cases, damage the device. As a guide, the capacitor should be in the order of  $0.01\mu F$  and the resistor, should be in the order of  $10K\Omega$ . The capacitors should be of the ceramic type. In order to minimize interference, PCB tracks should be made as short and as wide as possible to reduce their impedance. The battery cells should also be placed as close to the X3100 or X3101 monitor inputs as possible.

Resistors R<sub>CB</sub> and the associated n-channel MOSFET's (Q<sub>6</sub>–Q<sub>9</sub>) are used for battery cell voltage balancing. The X3100 and X3101 provide internal drive circuitry which allows the user to switch FETs Q6-Q9 ON or OFF via the microcontroller and SPI port (see section "Cell Voltage Balance Control (CBC1-CBC4)" on page 11). When any of the these FETs are switched ON, a current, limited by resistor RCB, flows across the particular battery cell. In doing so, the user can control the voltage across each individual battery cell. This is important when using Li-Ion battery cells since imbalances in cell voltages can, in time, greatly reduce the usable capacity of the battery pack. Cell voltage balancing may be implemented in various ways, but is usually performed towards the end of cell charging ("Top-of-charge method"). Values for R<sub>CB</sub> will vary according to the specific application.

The internal 4kbit EEPROM memory can be used to store the cell characteristics for implementing such functions as gas gauging, battery pack history, charge/ discharge cycles, and minimum/maximum conditions. Battery pack manufacturing data as well as serial number information can also be stored in the EEPROM array. An SPI serial bus provides the communication link to the EEPROM.

A current sense resistor (R<sub>SENSE</sub>) is used to measure and monitor the current flowing into/out of the battery terminals, and is used to protect the pack from over-current conditions (see section "Over-Current Protection" on page 18). R<sub>SENSE</sub> is also used to externally monitor current via a microcontroller (see section "Current Monitor Function" on page 20).

FETs Q4 and Q5 may be required on general purpose I/Os of the microcontroller that connect outside of the package. In some cases, without FETs, pull-up resistors external to the pack force a voltage on the  $V_{\rm CC}$  pin of the microcontroller during a pack sleep condition. This voltage can affect the proper tuned voltage of the X3100/X3101 regulator. These FETs should be turned-on by the microcontroller. (See Figure 1.)

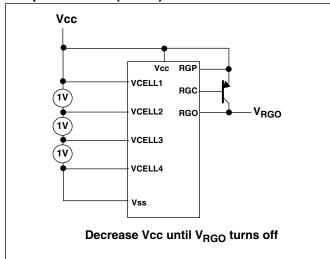

#### **POWER ON SEQUENCE**

Initial connection of the Li-lon cells in the battery pack will not normally power up the battery pack. Instead, the X3100 or X3101 enters and remains in the SLEEP mode. To exit the SLEEP mode, after the initial power up sequence, or following any other SLEEP MODE, a minimum of 16V (X3100  $\rm V_{SLR})$  or 12V (X3101  $\rm V_{SLR})$  is applied to the VCC pin, as would be the case during a battery charge condition. (See Figure 2.)

When  $V_{SLR}$  is applied to VCC, the analog select pins (AS2-AS0) and the SPI communication pins ( $\overline{CS}$ , CLK, SI, SO) must be low, so the X3100 and X3101 power up correctly into the normal operating mode. This can be done by using a power-on reset circuit.

When entering the normal operating mode, either from initial power up or following the SLEEP MODE, all bits in the control register are zero. With UVPC and OVPC bits at zero, the charge and discharge FETs are off. The microcontroller must turn these on to activate the pack. The microcontroller would typically check the voltage and current levels prior to turning on the FETs via the SPI port. The software should prevent turning on the FETs throughout an initial measurement/calibration period. The duration of this period is  $T_{OV}+200 \, \text{ms}$  or  $T_{UV}+200 \, \text{ms}$ , whichever is longer.

$T_{PUR}$  $V_{\mathsf{SLR}}$ VCC 0V 5V±10% (Stable and Repeatable) V<sub>RGO</sub> Tuned to 5V±0.5%  $V_{RGO}$ 0V 2ms (Typ.) Voltage Regulator Output Status (Internal Signal)  $T_{OC}$ 1 = X3100/1 in Over-Current Protection Mode Over-current Detection Status 0 = X3100/1 NOT in Over-Current Protection Mode (Internal Signal) OCDS 0 1 = X3100/1 in Over-Current Protection Mode OR VRGO Not Yet Tuned Status Register Bit 0 0 = X3100/1 NOT in Over-Current Protection Mode AND VRGO Tuned **VRGS+OCDS** T<sub>OV</sub>+200ms Status Register Bit 2 (SWCEN=0) CCES+OVDS 1 = V<sub>CELL</sub> < V<sub>CE</sub> OR X3100/1 in Over-charge Protection Mode 0 = V<sub>CELL</sub> > V<sub>CE</sub> OR X3100/1 NOT in Over-charge Protection Mode Status Register Bit 2 **OVDS** (SWCEN=1) 1 = X3100/1 in Over-charge Protection Mode 0 = X3100/1 NOT in Over-charge Protection Mode Microcontrolle AS2\_AS0 T<sub>OV</sub>+200ms OR T<sub>UV</sub>+200ms (whichever is longer) SPI PORT Charge, Discharge FETs can be Any Read or Write Operation, except turned on here. turn-on of FETs can start here.

Figure 2. Power Up Timing (Initial Power Up or after Sleep Mode)

#### **CONFIGURATION REGISTER**

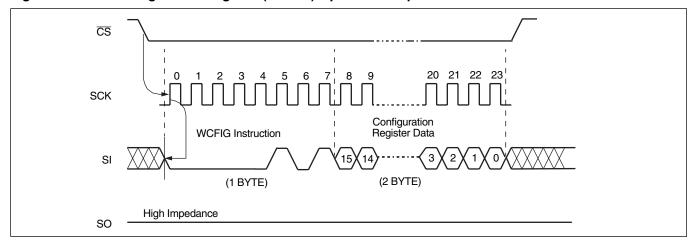

The X3100 and X3101 can be configured for specific user requirements using the Configuration Register.

**Table 1. Configuration Register Functionality**

| Bit(s) | Name                                                   | Function                                            |

|--------|--------------------------------------------------------|-----------------------------------------------------|

| 0-5    | _                                                      | (don't care)                                        |

| 6      | SWCEN                                                  | Switch Cell Charge Enable threshold function ON/OFF |

| 7      | CELLN Set the number of Li-lon bat cells used (3 or 4) |                                                     |

| 8-9    | VCE1-VCE0                                              | Select Cell Charge Enable threshold                 |

| 10-11  | VOC1-VOC0                                              | Select over-current threshold                       |

| 12-13  | VUV1-VUV0                                              | Select over-discharge (under voltage) threshold     |

| 14-15  | VOV1-VOV0                                              | Select over-charge voltage threshold                |

Table 2. Configuration Register—Upper Byte

| 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    |

|------|------|------|------|------|------|------|------|

| VOV1 | VOV0 | VUV1 | VUV0 | VOC1 | VOC0 | VCE1 | VCE0 |

X3100 Default = 30H; X3101 Default = 00H.

Table 3. Configuration Register—Lower Byte

| 7     | 6     | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-------|---|---|---|---|---|---|

| CELLN | SWCEN | Х | Х | х | Х | х | х |

X3100 Default = C0H; X3101 Default = 40H.

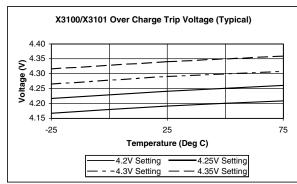

#### Over-charge Voltage Settings

VOV1 and VOV0 control the cell over-charge level. See section "Over-charge Protection" on page 13.

Table 4. Over-charge Voltage Threshold Selection

| Configuration Register<br>Bits |      |                                   |

|--------------------------------|------|-----------------------------------|

| VOV1                           | VOV0 | Operation                         |

| 0                              | 0    | V <sub>OV</sub> = 4.20V (Default) |

| 0                              | 1    | V <sub>OV</sub> = 4.25V           |

| 1                              | 0    | V <sub>OV</sub> = 4.30V           |

| 1                              | 1    | V <sub>OV</sub> = 4.35V           |

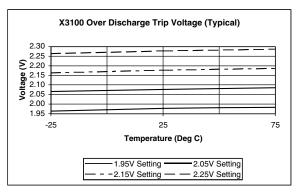

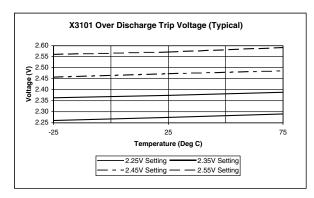

#### **Over-discharge Settings**

VUV1 and VUV0 control the cell over-discharge (under voltage threshold) level. See section "Over-discharge Protection" on page 15.

Table 5. Over-discharge Threshold Selection.

|      | uration<br>er Bits | Operation                                 |                                           |  |

|------|--------------------|-------------------------------------------|-------------------------------------------|--|

| VUV1 | VUV0               | X3100                                     | X3101                                     |  |

| 0    | 0                  | V <sub>UV</sub> =1.95V                    | V <sub>UV</sub> =2.25V<br>(X3101 default) |  |

| 0    | 1                  | V <sub>UV</sub> =2.05V                    | V <sub>UV</sub> =2.35V                    |  |

| 1    | 0                  | V <sub>UV</sub> =2.15V                    | V <sub>UV</sub> =2.45V                    |  |

| 1    | 1                  | V <sub>UV</sub> =2.25V<br>(X3100 default) | V <sub>UV</sub> =2.55V                    |  |

### **Over-current Settings**

VOC1 and VOC0 control the pack over-current level. See section "Over-Current Protection" on page 18.

Table 6. Over-Current Threshold Voltage Selection.

| Configuration | Register Bits |                                   |

|---------------|---------------|-----------------------------------|

| VOC1          | VOC0          | Operation                         |

| 0             | 0             | V <sub>OC</sub> =0.075V (Default) |

| 0             | 1             | V <sub>OC</sub> =0.100V           |

| 1             | 0             | V <sub>OC</sub> =0.125V           |

| 1             | 1             | V <sub>OC</sub> =0.150V           |

#### **Cell Charge Enable Settings**

VCE1, VCE0 and SWCEN control the pack charge enable function. SWCEN enables or disables a circuit that prevents charging if the cells are at too low a voltage. VCE1 and VCE0 select the voltage that is recognized as too low. See section "Sleep Mode" on page 15.

**Table 7. Cell Charge Enable Function**

| Configuration<br>Register Bit |                             |

|-------------------------------|-----------------------------|

| SWCEN                         | Operation                   |

| 0                             | Charge enable function: ON  |

| 1                             | Charge enable function: OFF |

Table 8. Cell Charging Threshold Voltage Selection.

| Configuration |   |                         |

|---------------|---|-------------------------|

| VCE1 VCE0     |   | Operation               |

| 0             | 0 | V <sub>CE</sub> = 0.5V  |

| 0             | 1 | V <sub>CE</sub> = 0.80V |

| 1             | 0 | V <sub>CE</sub> = 1.10V |

| 1             | 1 | V <sub>CE</sub> = 1.40V |

#### **Cell Number Selection**

The X3100 is designed to operate with four (4) Li-Ion battery cells. The X3101 is designed to operate with three (3) Li-Ion battery cells. The CELLN bit of the configuration register (Table 9) sets the number of cells recognized. For the X3101, the value for CELLN should always be zero.

Table 9. Selection of Number of Battery Cells<sup>1</sup>

| Configuration<br>Register Bit |                                         |

|-------------------------------|-----------------------------------------|

| CELLN                         | Operation                               |

| 1                             | 4 Li-Ion battery cells (X3100 default)  |

| 0                             | 3 Li-Ion battery cells (X3100 or X3101) |

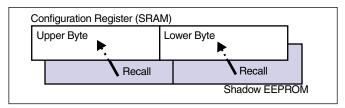

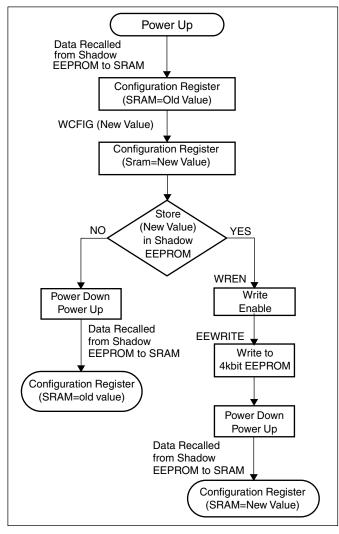

The configuration register consists of 16 bits of NOVRAM memory (Table 2, Table 3). This memory features a high-speed static RAM (SRAM) overlaid bit-for-bit with non-volatile "Shadow" EEPROM. An automatic array recall operation reloads the contents of the shadow EEPROM into the SRAM configuration register upon power-up (Figure 3).

Figure 3. Power up of Configuration Register

The configuration register is designed for unlimited write operations to SRAM, and a minimum of 1,000,000 store operations to the EEPROM. Data retention is specified to be greater than 100 years.

It should be noted that the bits of the shadow EEPROM are for the dedicated use of the configuration register, and are NOT part of the general purpose 4kbit EEPROM array.

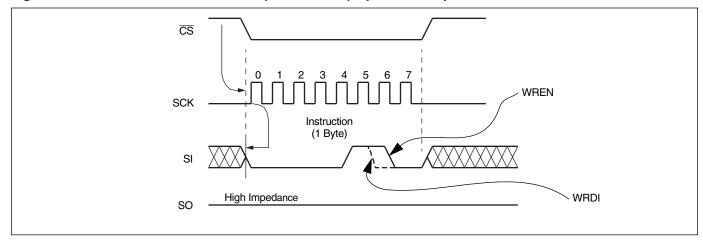

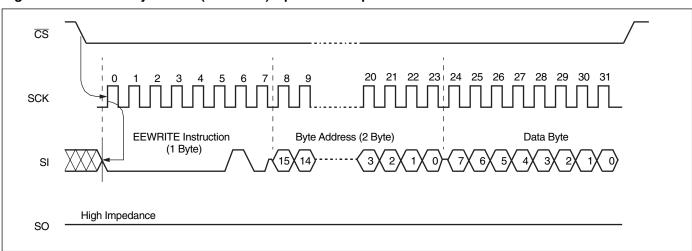

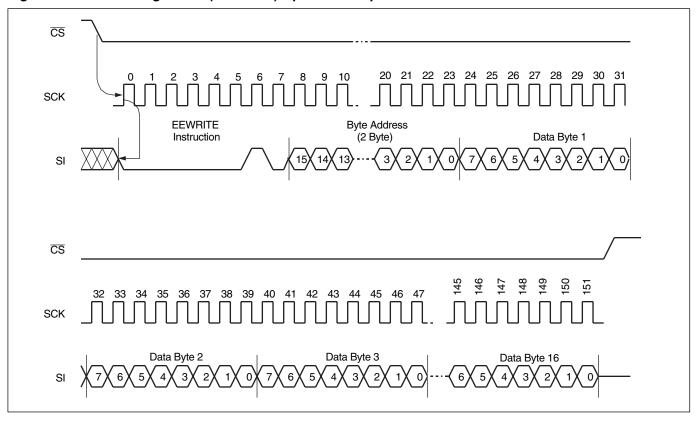

The WCFIG command writes to the configuration register, see Table 30 and section "X3100/X3101 SPI Serial Communication" on page 22.

After writing to this register using a WCFIG instruction, data will be stored only in the SRAM of the configuration register. In order to store data in shadow EEPROM, a WREN instruction, followed by a EEWRITE to any address of the 4kbit EEPROM memory array must occur, see Figure 4. This sequence initiates an internal nonvolatile write cycle which permits data to be stored in the shadow EEPROM cells. It must be noted that even though a EEWRITE is made to the general purpose 4kbit EEPROM array, the value and address to which it is written, is unimportant. If this procedure is not followed, the configuration register will power up to the last previously stored values following a power down sequence.

In the case that the X3100 or X3101 is configured for use with only three Li-lon battery cells (i.e. CELLN=0), then VCELL4 (pin 7) MUST be tied to Vss (pin 9) to ensure correct operation.

Figure 4. Writing to Configuration Register

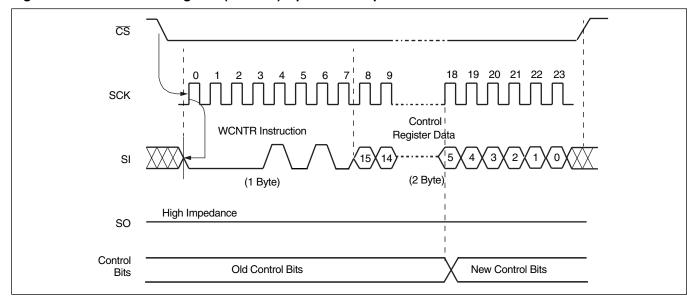

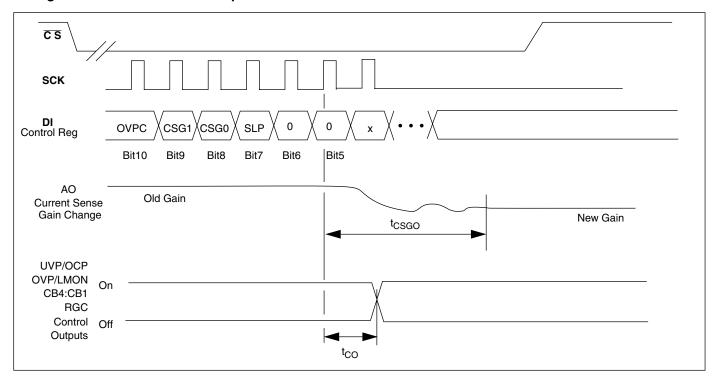

#### **CONTROL REGISTER**

The Control Register is realized as two bytes of volatile RAM (Table 10, Table 11). This register is written using the WCNTR instruction, see Table 30 and section "X3100/X3101 SPI Serial Communication" on page 22.

Table 10. Control Register—Upper Byte

| 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    |

|------|------|------|------|------|------|------|------|

| CBC4 | CBC3 | CBC2 | CBC1 | UVPC | OVPC | CSG1 | CSG0 |

Table 11. Control Register—Lower Byte

| 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----|---|---|---|---|---|---|---|

| SLP | 0 | 0 | х | х | х | х | х |

Since the control register is volatile, data will be lost following a power down and power up sequence. The default value of the control register on initial power up or when exiting the SLEEP MODE is 00h (for both upper and lower bytes respectively). The functions that can be manipulated by the Control Register are shown in Table 12.

**Table 12. Control Register Functionality**

| Bit(s) | Name          | Function                                                       |

|--------|---------------|----------------------------------------------------------------|

| 0-4    | _             | (don't care)                                                   |

| 5,6    | 0, 0          | Reserved—write 0 to these locations.                           |

| 7      | SLP           | Select sleep mode.                                             |

| 8,9    | CSG1,<br>CSG0 | Select current sense voltage gain                              |

| 10     | OVPC          | OVP control: switch pin OVP = V <sub>CC</sub> /V <sub>SS</sub> |

| 11     | UVPC          | UVP control: switch pin UVP = V <sub>CC</sub> /V <sub>SS</sub> |

| 12     | CBC1          | CB1 control: switch pin CB1 = V <sub>CC</sub> /V <sub>SS</sub> |

| 13     | CBC2          | CB2 control: switch pin CB2 = V <sub>CC</sub> /V <sub>SS</sub> |

| 14     | CBC3          | CB3 control: switch pin CB3 = V <sub>CC</sub> /V <sub>SS</sub> |

| 15     | CBC4          | CB4 control: switch pin CB4 = V <sub>CC</sub> /V <sub>SS</sub> |

#### Sleep Control (SLP)

Setting the SLP bit to '1' forces the X3100 or X3101 into the sleep mode, if  $V_{CC}$  <  $V_{SLP}$  See section "Sleep Mode" on page 15.

**Table 13. Sleep Mode Selection**

| Control Register Bits |                          |

|-----------------------|--------------------------|

| SLP                   | Operation                |

| 0                     | Normal operation mode    |

| 1                     | Device enters Sleep mode |

#### **Current Sense Gain (CSG1, CSG0)**

These bits set the gain of the current sense amplifier. These are x10, x25, x80 and x160. For more detail, see section "Current Monitor Function" on page 20.

**Table 14. Current Sense Gain Control**

| Control Re | gister Bits |                             |

|------------|-------------|-----------------------------|

| CSG1       | CSG0        | Operation                   |

| 0          | 0           | Set current sense gain=x10  |

| 0          | 1           | Set current sense gain=x25  |

| 1          | 0           | Set current sense gain=x80  |

| 1          | 1           | Set current sense gain=x160 |

#### Charge/Discharge Control (OVPC, UVPC)

The OVPC and UVPC bits allow control of cell charge and discharge externally, via the SPI port. These bits control the OVP/LMON and UVP/OCP pins, which in turn control the external power FETs.

Using P-channel power FETs ensures that the FET is on when the pin voltage is low (Vss), and off when the pin voltage is high (Vcc).

OVP/LMON and UVP/OCP can be controlled by using the WCNTR Instruction to set bits OVPC and UVPC in the Control register (See page 10).

**Table 15. UVP/OVP Control**

| Control Re | gister Bits |                                   |

|------------|-------------|-----------------------------------|

| OVPC       | UVPC        | Operation                         |

| 1          | Х           | Pin OVP=V <sub>SS</sub> (FET ON)  |

| 0          | Х           | Pin OVP=V <sub>CC</sub> (FET OFF) |

| х          | 1           | Pin UVP=V <sub>SS</sub> (FET ON)  |

| х          | 0           | Pin UVP=V <sub>CC</sub> (FET OFF) |

It is possible to set/change the values of OVPC and UVPC during a protection mode. A change in the state of the pins OVP/LMON and UVP/OCP, however, will not take place until the device has returned from the protection mode.

### Cell Voltage Balance Control (CBC1-CBC4)

This function can be used to adjust individual battery cell voltage during charging. Pins CB1–CB4 are used to control external power switching devices. Cell voltage balancing is achieved via the SPI port.

Table 16. CB1—CB4 Control

| Co   | ntrol Re |      |      |                               |

|------|----------|------|------|-------------------------------|

| CBC4 | CBC3     | CBC2 | CBC1 | Operation                     |

| х    | х        | х    | 1    | Set CB1=V <sub>CC</sub> (ON)  |

| х    | х        | х    | 0    | Set CB1=V <sub>SS</sub> (OFF) |

| х    | х        | 1    | х    | Set CB2=V <sub>CC</sub> (ON)  |

| х    | х        | 0    | х    | Set CB2=V <sub>SS</sub> (OFF) |

| х    | 1        | х    | х    | Set CB3=V <sub>CC</sub> (ON)  |

| х    | 0        | х    | х    | Set CB3=V <sub>SS</sub> (OFF) |

| 1    | х        | х    | х    | Set CB4=V <sub>CC</sub> (ON)  |

| 0    | Х        | Х    | Х    | Set CB4=V <sub>SS</sub> (OFF) |

CB1–CB4 can be controlled by using the WCNTR Instruction to set bits CBC1–CBC4 in the control register (Table 16).

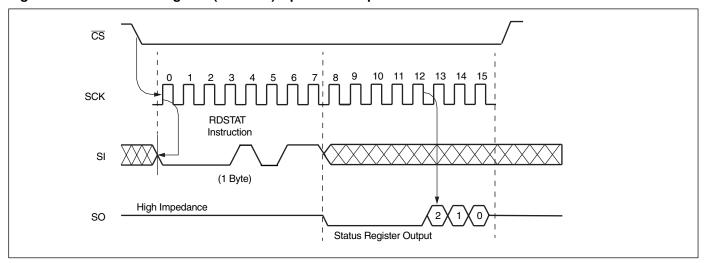

#### **STATUS REGISTER**

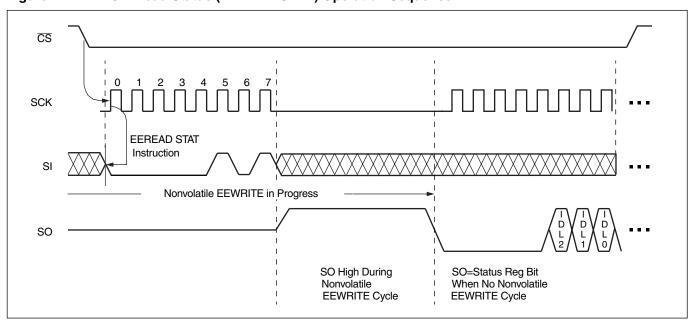

The status of the X3100 or X3101 can be verified by using the RDSTAT command to read the contents of the Status Register (Table 17).

Table 17. Status Register.

| 7 | 6 | 5 | 4 | 3 | 2             | 1    | 0             |

|---|---|---|---|---|---------------|------|---------------|

| 0 | 0 | 0 | 0 | 0 | CCES+<br>OVDS | UVDS | VRGS+<br>OCDS |

The function of each bit in the status register is shown in Table 18.

Bit 0 of the status register (VRGS+OCDS) actually indicates the status of two conditions of the X3100 or X3101. Voltage Regulator Status (VRGS) is an internally generated signal which indicates that the output of the Voltage Regulator (VRGO) has reached an output of 5VDC  $\pm$  0.5%. In this case, the voltage regulator is said to be "tuned". Before the signal VRGS goes low (i.e. before the voltage regulator is tuned), the voltage at the output of the regulator is nominally 5VDC  $\pm$  10% (See section "Voltage Regulator" on page 21.) Over-current Detection Status (OCDS) is another internally generated signal which indicates whether or not the X3100 or X3101 is in over-current protection mode.

Signals VRGS and OCDS are logically OR'ed together (VRGS+OCDS) and written to bit 0 of the status register (See Table 18, Table 17 and Figure 2).

Bit 1 of the status register simply indicates whether or not the X3100 or X3101 is in over-discharge protection mode.

Bit 2 of the status register (CCES+OVDS) indicates the status of two conditions of the X3100 or X3101. Cell Charge Enable Status (CCES) is an internally generated signal which indicates the status of any cell voltage (V<sub>CELL</sub>) with respect to the Cell Charge Enable Voltage (V<sub>CE</sub>). Over-charge Voltage Detection Status (OVDS) is an internally generated signal which indicates whether

or not the X3100 or X3101 is in over-charge protection mode.

When the cell charge enable function is switched ON (configuration bit SWCEN=0), the signals CCES and OVDS are logically OR'ed (CCES+OVDS) and written to bit 2 of the status register. If the cell charge enable function is switched OFF (configuration bit SWCEN=1), then bit 2 of the status register effectively only represents information about the over-charge status (OVDS) of the X3100 or X3101 (See Table 18, Table 17 and Figure 2).

Table 18. Status Register Functionality.

| Bit(s) | Name        | Description                           | Case                                      | Status | Interpretation                                                                                                     |

|--------|-------------|---------------------------------------|-------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------|

|        |             | Voltage regulator status              |                                           | 1      | V <sub>RGO</sub> not yet tuned (V <sub>RGO</sub> =5V ± 10%) <b>OR</b> X3100/X3101 in over-current protection mode. |

| 0      | VRGS+OCDS   | +<br>Over-current<br>detection status | -                                         | 0      | $V_{RGO}$ tuned ( $V_{RGO}$ =5V ± 0.5%) <b>AND</b> X3100/X3101 NOT in over-current protection mode.                |

| 4      | UVDS        | Over-discharge                        | -                                         | 1      | X3100/X3101 in over-discharge protection mode                                                                      |

| '      | 0003        | detection status                      |                                           | 0      | X3100/X3101 NOT in over-discharge protection mode                                                                  |

|        | 2 CCES+OVDS | ES+OVDS + Over-charge                 | SWCEN=0 <sup>†</sup> SWCEN=1 <sup>†</sup> | 1      | V <sub>CELL</sub> < V <sub>CE</sub> <b>OR</b><br>X3100/X3101 in over-charge protection mode                        |

| 2      |             |                                       |                                           | 0      | V <sub>CELL</sub> > V <sub>CE</sub> <b>AND</b><br>X3100/X3101 NOT in over-charge protection mode                   |

|        |             |                                       |                                           | 1      | X3100/X3101 in over-charge protection mode                                                                         |

|        |             |                                       |                                           | 0      | X3100/X3101 NOT in over-charge protection mode                                                                     |

| 3–7    | -           |                                       | -                                         | 0      | Not used (always return zero)                                                                                      |

**Notes:** † This bit is set in the configuration register.

#### X3100/X3101 INTERNAL PROTECTION FUNCTIONS

The X3100 and the X3101 provide periodic monitoring (see section "Periodic Protection Monitoring" on page 12) for over-charge and over-discharge states and continuous monitoring for an over-current state. It has automatic shutdown when a protection mode is encountered, as well as automatic return after the device is released from a protection mode. When sampling voltages through the analog port (Monitor Mode), over-charge and over-discharge protection monitoring is also performed on a continuous basis.

Voltage thresholds for each of these protection modes  $(V_{OV}, V_{UV}, and V_{OC})$  respectively) can be individually selected via software and stored in an internal non-volatile register. This feature allows the user to avoid the restrictions of mask programmed voltage thresholds, and is especially useful during prototype/evaluation design

stages or when cells with slightly different characteristics are used in an existing design.

Delay times for the detection of, and release from protection modes ( $T_{OV}$ ,  $T_{UV}/T_{UVR}$ , and  $T_{OC}/T_{OCR}$  respectively) can be individually varied by setting the values of external capacitors connected to pins OVT, UVT, OCT.

#### **Periodic Protection Monitoring**

In normal operation, the analog select pins are set such that AS2=L, AS1=L, AS0=L. In this mode the X3100 and X3101 conserve power by sampling the cells for over or over-discharge conditions.

In this state over-charge and over-discharge protection circuitry are usually off, but are periodically switched on by the internal Protection Sample Rate Timer (PSRT). The

over-charge and over-discharge protection circuitry is on for approximately 2ms in each 125ms period. Overcurrent monitoring is continuous. In monitor mode (see page 20) over-charge and over-discharge monitoring is also continuous.

#### **Over-charge Protection**

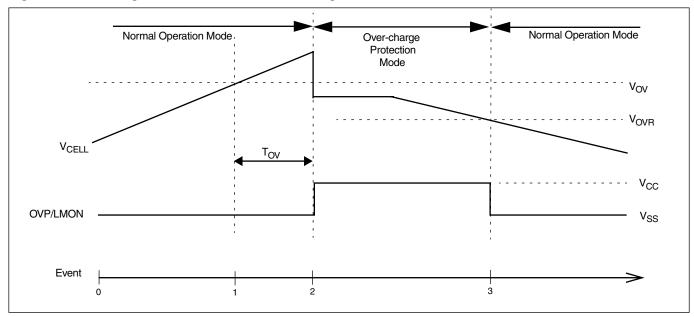

The X3100 and X3101 monitor the voltage on each battery cell ( $V_{CELL}$ ). If for any cell,  $V_{CELL} > V_{OV}$  for a time exceeding  $T_{OV}$ , then the Charge FET will be switched OFF (OVP/LMON= $V_{CC}$ ). The device has now entered Over-charge protection mode (Figure 5). The status of the discharge FET (via pin UVP) will remain unaffected.

While in over-charge protection mode, it is possible to change the state of the OVPC bit in the control register such that OVP/LMON=Vss (Charge FET=ON). Although the OVPC bit in the control register can be changed, the change will not be seen at pin OVP until the X3100 or X3101 returns from over-charge protection mode.

The over-charge detection delay  $T_{OV}$ , is varied using a capacitor ( $C_{OV}$ ) connected between pin OVT and GND.

A typical delay time is shown in Table 10. The delay  $T_{OV}$  that results from a particular capacitance  $C_{OV}$ , can be approximated by the following linear equation:

$$T_{OV}$$

(s)  $\approx 10 \text{ x C}_{OV}$  ( $\mu F$ ).

Table 19. Typical over-charge detection time

| Symbol          | C <sub>OV</sub> | Delay      |

|-----------------|-----------------|------------|

| T <sub>OV</sub> | 0.1µF           | 1.0s (Typ) |

The device further continues to monitor the battery cell voltages, and is released from over-charge protection mode when  $V_{CELL} < V_{OVR}$ , for all cells. When the X3100 or X3101 is released from over-charge protection mode, the charge FET is automatically switched ON (OVP/LMON= $V_{SS}$ ). When the device returns from over-charge protection mode, the status of the discharge FET (pin UVP/OCP) remains unaffected.

The value of  $V_{OV}$  can be selected from the values shown in Table 4 by setting bits VOV1, VOV0. These bits are set by using the WCFIG instruction to write to the configuration register.

Figure 5. Over-charge Protection Mode—Event Diagram

### Table 20. Over-charge Protection Mode—Event Diagram Description

| Event | Event Description                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [0,1) | <ul> <li>— Discharge FET is ON (UVP/OCP=V<sub>SS</sub>).</li> <li>— Charge FET is ON (OVP/LMON=V<sub>SS</sub>), and hence battery cells are permitted to receive charge.</li> <li>— All cell voltages (V<sub>CELL</sub>-V<sub>CELL4</sub>) are below the over-charge voltage threshold (V<sub>OV</sub>).</li> <li>— The device is in normal operation mode (i.e. not in a protection mode).</li> </ul>                                                        |

| [1]   | <ul> <li>The voltage of one or more of the battery cells (V<sub>CELL</sub>), exceeds V<sub>OV</sub>.</li> <li>The internal over-charge detection delay timer begins counting down.</li> <li>The device is still in normal operation mode</li> </ul>                                                                                                                                                                                                           |

| (1,2) | The internal over-charge detection delay timer continues counting for T <sub>OV</sub> seconds.                                                                                                                                                                                                                                                                                                                                                                |

| [2]   | The internal over-charge detection delay timer times out  AND  V <sub>CELL</sub> still exceeds V <sub>OV</sub> .  —Therefore, the internal over-charge sense circuitry switches the charge FET OFF (OVP/LMON=Vcc).  —The device has now entered over-charge protection mode.                                                                                                                                                                                  |

| (2,3) | While in over-charge protection mode:  — The battery cells are permitted to discharge via the discharge FET, and diode D <sub>2</sub> across the charge FET  — The X3100 or X3101 monitors the voltages V <sub>CELL1</sub> -V <sub>CELL4</sub> to determine whether or not they have all fallen below the "Return from over-charge threshold" (V <sub>OVR</sub> ).  — (It is possible to change the status of UVP/OCP or OVP/LMON using the control register) |

| [3]   | <ul> <li>— All cell voltages fall below V<sub>OVR</sub>—The device is now in normal operation mode.</li> <li>— The X3100/X3101 automatically switches charge FET=ON (OVP/LMON=Vss)</li> <li>— The status of the discharge FET remains unaffected.</li> <li>— Charging of the battery cells can now resume.</li> </ul>                                                                                                                                         |

#### Over-discharge Protection

If  $V_{CELL} < V_{UV}$ , for a time exceeding  $T_{UV}$ , the cells are said to be in a over-discharge state (Figure 6). In this instance, the X3100 and X3101 automatically switch the discharge FET OFF (UVP/OCP=Vcc), and then enter sleep mode.

The over-discharge (under-voltage) value,  $V_{UV}$ , can be selected from the values shown in Table 5 by setting bits VUV1, VUV0 in the configuration register. These bits are set using the WCFIG command. Once in the sleep mode, the following steps must occur before the X3100 or X3101 allows the battery cells to discharge:

- The X3100 and X3101 must wake from sleep mode (see section "Voltage Regulator" on page 21).

- The charge FET must be switched ON by the microcontroller (OVP/LMON=V<sub>SS</sub>), via the control register (see section "Control Register Functionality" on page 10).

- All battery cells must satisfy the condition: V<sub>CELL</sub> > V<sub>UVR</sub> for a time exceeding T<sub>UVR</sub>.

- The discharge FET must be switched ON by the microcontroller (UVP/OCP=V<sub>SS</sub>), via the control register (see section "Control Register Functionality" on page 10)

The times  $T_{UV}/T_{UVR}$  are varied using a capacitor ( $C_{UV}$ ) connected between pin UVT and GND (Table 13). The delay  $T_{UV}$  that results from a particular capacitance  $C_{UV}$ , can be approximated by the following linear equation:

$$T_{UV}$$

(s)  $\approx$  10 x  $C_{UV}$  ( $\mu$ F)

$T_{UVR}$  (ms)  $\approx$  70 x  $C_{UV}$  ( $\mu$ F)

**Table 21. Typical Over-discharge Delay Times**

| Symbol           | Description                    | CUV   | Delay      |

|------------------|--------------------------------|-------|------------|

| T <sub>UV</sub>  | Over-discharge detection delay | 0.1μF | 1.0s (Typ) |

| T <sub>UVR</sub> | Over-discharge release time    | 0.1μF | 7ms (Typ)  |

#### Sleep Mode

The X3100 or X3101 can enter sleep mode in two ways:

- i) The device enters the over-discharge protection mode.

- The user sends the device into sleep mode using the control register.

A sleep mode can be induced by the user, by setting the SLP bit in the control register (Table 13) using the WCNTR Instruction.

In sleep mode, power to all internal circuitry is switched off, minimizing the current drawn by the device to  $1\mu A$  (max). In this state, the discharge FET and the charge FET are switched OFF (OVP/LMON=V\_CC and UVP/OCP=V\_CC), and the 5VDC regulated output (V\_RGO) is 0V. Control of UVP/OCP and OVP/LMON via bits UVPC and OVPC in the control register is also prohibited.

The device returns from sleep mode when  $V_{CC} \ge V_{SLR}$ . (e.g. when the battery terminals are connected to a battery charger). In this case, the X3100 or the X3101 restores the 5VDC regulated output (section "Voltage Regulator" on page 21), and communication via the SPI port resumes.

If the Cell Charge Enable function is enabled when  $V_{CC}$  rises above  $V_{SLR}$ , the X3100 and X3101 internally verifies that the individual battery cell voltages ( $V_{CELL}$ ) are larger than the cell charge enable voltage ( $V_{CE}$ ) before allowing the FETs to be turned on. The value of  $V_{CE}$  is selected by using the WCFIG command to set bits VCE1–VCE0 in the configuration register.

Only if the condition " $V_{CELL} > V_{CE}$ " is satisfied can the state of charge and discharge FETs be changed via the control register. Otherwise, if  $V_{CELL} < V_{CE}$  for any battery cell then both the Charge FET and the discharge FET are OFF (OVP/LMON=Vcc and UVP/OCP= $V_{CC}$ ). Thus both charge and discharge of the battery cells via terminals P+/P- is prohibited<sup>1</sup>.

The cell charging threshold function can be switched ON or OFF by the user, by setting bit SWCEN in the configuration register (Table 7) using the WCFIG command. In the case that this cell charge enable function is switched OFF, then  $V_{CE}$  is effectively set to OV.

Neither the X3100 nor the X3101 enter sleep mode (automatically or manually, by setting the SLP bit) if  $V_{CC} \ge V_{SLR}$ . This is to ensure that the device does not go into a sleep mode while the battery cells are at a high voltage (e.g. during cell charging).

In this case, charging of the battery may resume ONLY if the cell charge enable function is switched OFF by setting bit SWCEN = 1 in the configuration register (See Above, "Configuration Register Functionality" on page 8).

VCC Cell Charge Prohibited if SWCEN=0 AND V<sub>CELL</sub> < V<sub>CE</sub> **VCELL** 0.7V  $V_{UV}$  $T_{\mathsf{UV}}$ Note 3 Over-discharge Protection Mode UVP/OCP The Longer of TOV+200ms OR TUV+200ms Note; 1  $V_{SS}$ OVP/LMON **RGO** Sleep Mode 5V **Event** ż 5 Note 1: If SWEN=0 and  $V_{CELL} < V_{CE}$ , then OVP/LMON stays high and charging is prohibited. Note 2: OVP/LMON stays high until the microcontroller writes a "1" to the OVPC bit in the control register. This sets the signal low, which turns on the charge FET. It cannot be turned on prior to this time. Note 3: UVP/OCP stays high until the microcontroller writes a "1" to the UVPC bit in the control register. This sets the signal low, which turns on the

Figure 6. Over-discharge Protection Mode—Event Diagram

discharge FET. The FET cannot be turned on prior to this time.

Table 22. Over-discharge Protection Mode—Event Diagram Description

| Event | Event Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [0,1) | <ul> <li>Charge FET is ON (OVP/LMON=V<sub>SS</sub>)</li> <li>Discharge FET is ON (UVP/OCP=V<sub>SS</sub>), and hence battery cells are permitted to discharge.</li> <li>All cell voltages (VCELL<sub>1</sub>-VCELL<sub>4</sub>) are above the Over-discharge threshold voltage (V<sub>UV</sub>).</li> <li>The device is in normal operation mode (i.e. not in a protection mode).</li> </ul>                                                                                         |

| [1]   | <ul> <li>The voltage of one or more of the battery cells (V<sub>CELL</sub>), falls below V<sub>UV</sub>.</li> <li>The internal over-discharge detection delay timer begins counting down.</li> <li>The device is still in normal operation mode</li> </ul>                                                                                                                                                                                                                           |

| (1,2) | The internal over-discharge detection delay timer continues counting for T <sub>UV</sub> seconds.                                                                                                                                                                                                                                                                                                                                                                                    |

| [2]   | <ul> <li>The internal over-discharge detection delay timer times out, AND V<sub>CELL</sub> is still below V<sub>UV</sub>.</li> <li>The internal over-discharge sense circuitry switches the discharge FET OFF (UVP/OCP=Vcc).</li> <li>The charge FET is switched OFF (OVP/LMON=V<sub>CC</sub>).</li> <li>The device has now entered over-discharge protection mode.</li> <li>At the same time, the device enters sleep mode (See section "Voltage Regulator" on page 21).</li> </ul> |

## Table 22. Over-discharge Protection Mode—Event Diagram Description (Continued)

| Event |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Event Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| (2,3) | While device is in sleep (in over-discharge protection) mode:  — The power to ALL internal circuits is switched OFF limiting power consumption to less than 1µA.  — The output of the 5VDC voltage regulator (RGO) is 0V.  — Access to the X3100/X3101 via the SPI port is NOT possible.                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| [3]   | Return from sleep mode (but still in over-discharge protection mode):  — Vcc rises above the "Return from Sleep mode threshold Voltage" (V <sub>SLR</sub> )—This would normally occur in the case that the battery pack was connected to a charger. The X3100/X3101 is now powered via P+/P-, and not the battery pack cells.  — Power is returned to ALL internal circuitry  — 5VDC output is returned to the regulator output (RGO).  — Access is enabled to the X3100/X3101 via the SPI port.  — The status of the discharge FET remains OFF (It is possible to change the status of UVPC in the control register, although it will have no effect at this time).       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| (3,4) | If the cell charge enable function is switched ON AND V <sub>CELL</sub> > V <sub>CE</sub> OR Charge enable function is switched OFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <ul> <li>The X3100/X3101 initiates a reset operation that takes the longer of T<sub>OV</sub>+200ms or T<sub>UV</sub>+200ms to complete. Do not write to the FET control bits during this time.</li> <li>The charge FET is switched On (OVP/LMON=Vss) by the microcontroller by writing a "1" to the OVPC bit in the control register.</li> <li>The battery cells now receive charge via the charge FET and diode D1 across the discharge FET (which is OFF).</li> <li>The X3100/X3101 monitors the V<sub>CELL</sub> voltage to determine whether or not it has risen above V<sub>UVR</sub>.</li> </ul> |  |

|       | If the cell charge enable function is switched ON  AND  VCELL < VCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <ul> <li>— Charge/discharge of the battery cells via P+ is no longer permitted (Charge FET and discharge FET are held OFF).</li> <li>— (Charging may re-commence only when the Cell Charge Enable function is switched OFF - See Sections: "Configuration Register" page 4, and "Sleep mode" page 17.)</li> </ul>                                                                                                                                                                                                                                                                                      |  |

| [4]   | — The voltage of all of the battery cells (V <sub>CELL</sub> ), have risen above V <sub>UVR</sub> .  — The internal Over-discharge release timer begins counting down.  — The X3100/X3101 is still in over-discharge protection mode.                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| (4,5) | <ul> <li>The internal over-discharge release timer continues counting for t<sub>UVR</sub> seconds.</li> <li>The X3100/X3101 should be in monitor mode (AS2:AS0 not all low) for recovery time based on t<sub>UVR</sub>. Otherwise recovery is based on two successive samples about 120ms apart.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| [5]   | <ul> <li>The internal over-discharge release timer times out, AND V<sub>CELL</sub> is still above V<sub>UVR</sub>.</li> <li>The device returns from over-discharge protection mode, and is now in normal operation mode.</li> <li>The Charger voltage can now drop below VSLR and the X3100/X3101 will not go back to sleep.</li> <li>The discharge FET is can now be switched ON (UVP/OCP=V<sub>SS</sub>) by the microcontroller by writing a "1" to the UVPC bit of the control register.</li> <li>The status of the charge FET remains unaffected (ON)</li> <li>The battery cells continue to receive charge via the charge FET and discharge FET (both ON).</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

#### **Over-Current Protection**

In addition to monitoring the battery cell voltages, the X3100 and X3101 continually monitor the voltage VCS $_{21}$  (VCS $_{2}$ –VCS $_{1}$ ) across the current sense resistor (RSENSE). If VCS $_{21}$  > V $_{OC}$  for a time exceeding T $_{OC}$ , then the device enters over-current protection mode (Figure 7). In this mode, the X3100 and X3101 automatically switch the discharge FET OFF (UVP/OCP=Vcc) and hence prevent current from flowing through the terminals P+ and P-.

Figure 7. Over-Current Protection

The 5VDC voltage regulator output (V<sub>RGO</sub>) is always active during an over-current protection mode.

Once the device enters over-current protection mode, the X3100 and X3101 begin a load monitor state. In the load monitor state, a small current (I<sub>LMON</sub>=7.5µA typ.) is passed out of pin OVP/LMON in order to determine the load resistance. The load resistance is the impedance seen looking out of pin OVP/LMON, between terminal P+ and pin VSS (See Figure 7.)

If the load resistance >  $150k\Omega$  ( $I_{LMON}=0\mu A$ ) for a time exceeding  $T_{OCR}$ , then the X3100 or X3101 is released from over-current protection mode. The discharge FET is then automatically switched ON (UVP/OCP=Vss) by the X3100 or X3101, unless the status of UVP/OCP has been changed in control register (by manipulating bit UVPC) during the over-current protection mode.

$T_{OC}/T_{OCR}$  are varied using a capacitor ( $C_{OC}$ ) connected between pin OCT and VSS. A list of typical delay times is shown in Table 23. Note that the value  $C_{OC}$  should be larger than 1nF.

The delay  $T_{OC}$  and  $T_{OCR}$  that results from a particular capacitance  $C_{OC}$  can be approximated by the following equations:

$$T_{OC}$$

(ms)  $\approx 10,000 \times C_{OC}$  ( $\mu$ F)

$T_{OCR}$  (ms)  $\approx 10,000 \times C_{OC}$  ( $\mu$ F)

**Table 23. Typical Over-Current Delay Times**

| Symbol           | Description                  | C <sub>OC</sub> | Delay      |

|------------------|------------------------------|-----------------|------------|

| T <sub>OC</sub>  | Over-current detection delay | 0.001µF         | 10ms (Typ) |

| T <sub>OCR</sub> | Over-current release time    | 0.001µF         | 10ms (Typ) |

The value of  $V_{OC}$  can be selected from the values shown in Table 6, by setting bits VOC1, VOC0 in the configuration register using the WCFIG command.

Note: If the Charge FET is turned off, due to an overcharge condition or by direct command from the microcontroller, the cells are not in an undervoltage condition and the pack has a load, then excessive current may flow through Q10 and diode D1. To eliminate this effect, the gate of Q10 can be turned off by the microcontroller through an unused X3101 cell balance output, or directly from a microcontroller port instead of connecting to  $V_{\rm RGO}$ .

Normal Operation Mode

Over-Current Protection Mode

Normal Operation Mode

P+ = (RLOAD+RSENSE) x ILMON

Voc

VCS<sub>2</sub>

V<sub>SS</sub>

V<sub>SS</sub>

V<sub>SS</sub>

Event

Event

Figure 8. Over-Current Protection Mode—Event Diagram

Table 24. Over-Current Protection Mode—Event Diagram Description

| Event | Event Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [0,1) | <ul> <li>Discharge FET is ON (OCP=Vss). Battery cells are permitted to discharge.</li> <li>VCS<sub>21</sub> (VCS<sub>2</sub>-VCS<sub>1</sub>) is less than the over-current threshold voltage (V<sub>OC</sub>).</li> <li>The device is in normal operation mode (i.e. not in a protection mode).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| [1]   | <ul> <li>Excessive current flows through the battery terminals P+, dropping the voltage. (See Figure 8.).</li> <li>The positive battery terminal voltage (P+) falls, and VCS<sub>21</sub> exceeds V<sub>OC</sub>.</li> <li>The internal over-current detection delay timer begins counting down.</li> <li>The device is still in Normal Operation Mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                           |

| (1,2) | The internal Over-current detection delay timer continues counting for T <sub>OC</sub> seconds.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| [2]   | <ul> <li>The internal over-current detection delay timer times out, AND VCS<sub>21</sub> is still above V<sub>OC</sub>.</li> <li>The internal over-current sense circuitry switches the discharge FET OFF (UVP/OCP=Vcc).</li> <li>The device now begins a load monitor state by passing a small test current (I<sub>LMON</sub>=7.5µA) out of pin OVP/LMON. This senses if an over-current condition (i.e. if the load resistance &lt; 150kΩ) still exists across P+/P</li> <li>The device has now entered over-current protection mode.</li> <li>It is possible to change the status of UVPC and OVPC in the control register, although the status of pins UVP/OCP and OVP/LMON will not change until the device has returned from over-current protection mode.</li> </ul> |

| (2,3) | —The X3100/X3101 now continuously monitors the load resistance to detect whether or not an over-<br>current condition is still present across the battery terminals P+/P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Table 24. Over-Current Protection Mode—Event Diagram Description (Continued)

| Event | Event Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

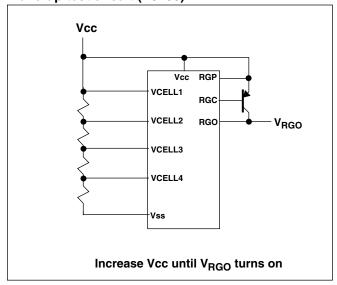

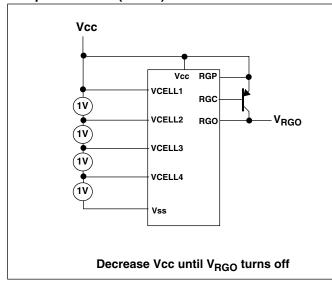

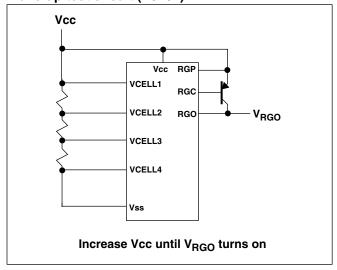

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|