# **Features**

- Incorporates the ARM926EJ-S™ ARM® Thumb® Processor

- DSP Instruction Extensions

- ARM Jazelle® Technology for Java® Acceleration

- 16 Kbyte Data Cache, 16 Kbyte Instruction Cache, Write Buffer

- 210 MIPS at 190 MHz

- Memory Management Unit

- EmbeddedlCE<sup>™</sup>, Debug Communication Channel Support

- Mid-level implementation Embedded Trace Macrocell<sup>™</sup>

- Additional Embedded Memories

- 32 Kbytes of Internal ROM, Single-cycle Access at Maximum Bus Speed

- 16 Kbytes of Internal SRAM, Single-cycle Access at Bus Speed

- External Bus Interface (EBI)

- Supports SDRAM, Static Memory, NAND Flash and CompactFlash®

- LCD Controller

- Supports Passive or Active Displays

- Up to 16-bits per Pixel in STN Color Mode

- Up to 16M Colors in TFT Mode (24-bit per Pixel), Resolution up to 2048 x 2048

- USB

- USB 2.0 Full Speed (12 Mbits per second) Host Double Port

- Dual On-chip Transceivers

- Integrated FIFOs and Dedicated DMA Channels

- USB 2.0 Full Speed (12 Mbits per second) Device Port

- On-chip Transceiver, 2 Kbyte Configurable Integrated FIFOs

- Bus Matrix

- Handles Five Masters and Five Slaves

- Boot Mode Select Option

- Remap Command

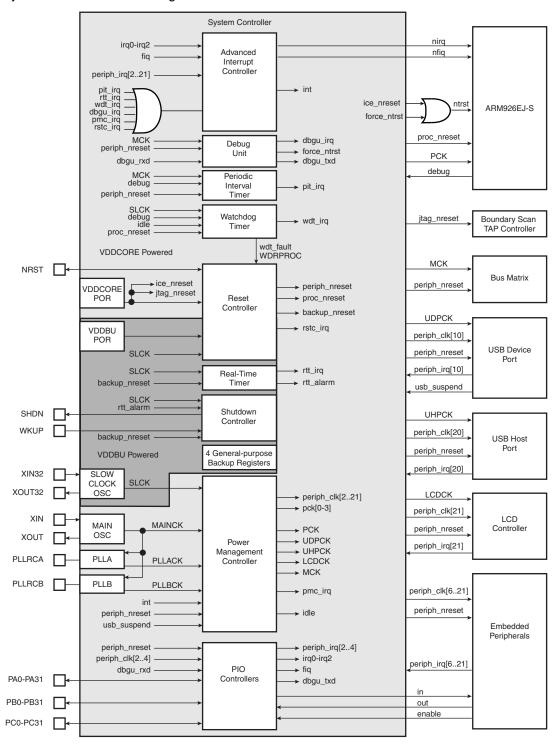

- Fully Featured System Controller (SYSC) for Efficient System Management, including

- Reset Controller, Shutdown Controller, Four 32-bit Battery Backup Registers for a Total of 16 Bytes

- Clock Generator and Power Management Controller

- Advanced Interrupt Controller and Debug Unit

- Periodic Interval Timer, Watchdog Timer and Real-time Timer

- Three 32-bit PIO Controllers

- Reset Controller (RSTC)

- Based on Power-on Reset Cells, Reset Source Identification and Reset Output

- Shutdown Controller (SHDWC)

- Programmable Shutdown Pin Control and Wake-up Circuitry

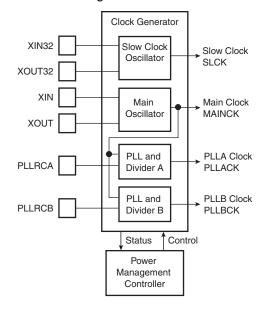

- Clock Generator (CKGR)

- 32,768 Hz Low-power Oscillator on Battery Backup Power Supply, Providing a Permanent Slow Clock

- 3 to 20 MHz On-chip Oscillator and two PLLs

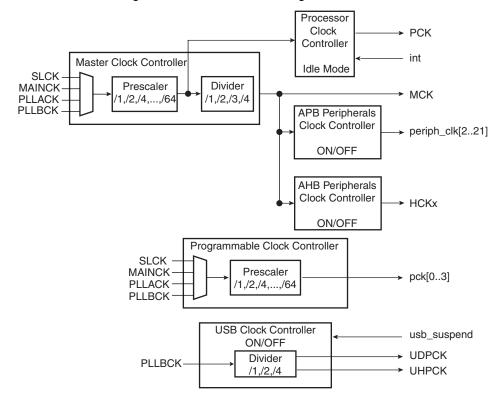

- Power Management Controller (PMC)

- Very Slow Clock Operating Mode, Software Programmable Power Optimization Capabilities

- Four Programmable External Clock Signals

# AT91 ARM Thumb-based Microcontrollers

# AT91SAM9261S

# **Summary**

6242DS-ATARM-06-Jan-09

- Advanced Interrupt Controller (AIC)

- Individually Maskable, Eight-level Priority, Vectored Interrupt Sources

- Three External Interrupt Sources and One Fast Interrupt Source, Spurious Interrupt Protected

- Debug Unit (DBGU)

- 2-wire USART and support for Debug Communication Channel, Programmable ICE Access Prevention

- Mode for General Purpose Two-wire UART Serial Communication

- Periodic Interval Timer (PIT)

- 20-bit Interval Timer plus 12-bit Interval Counter

- Watchdog Timer (WDT)

- Key Protected, Programmable Only Once, Windowed 12-bit Counter, Running at Slow Clock

- Real-Time Timer (RTT)

- 32-bit Free-running Backup Counter Running at Slow Clock

- Three 32-bit Parallel Input/Output Controllers (PIO) PIOA, PIOB and PIOC

- 96 Programmable I/O Lines Multiplexed with up to Two Peripheral I/Os

- Input Change Interrupt Capability on Each I/O Line

- Individually Programmable Open-drain, Pull-up Resistor and Synchronous Output

- Nineteen Peripheral DMA (PDC) Channels

- Multimedia Card Interface (MCI)

- SDCard and MultiMediaCard<sup>™</sup> Compliant

- Automatic Protocol Control and Fast Automatic Data Transfers with PDC, MMC and SDCard Compliant

- Three Synchronous Serial Controllers (SSC)

- Independent Clock and Frame Sync Signals for Each Receiver and Transmitter

- I2S Analog Interface Support, Time Division Multiplex Support

- High-speed Continuous Data Stream Capabilities with 32-bit Data Transfer

- Three Universal Synchronous/Asynchronous Receiver Transmitters (USART)

- Individual Baud Rate Generator, IrDA® Infrared Modulation/Demodulation

- Support for ISO7816 T0/T1 Smart Card, Hardware and Software Handshaking, RS485 Support

- Two Master/Slave Serial Peripheral Interface (SPI)

- 8- to 16-bit Programmable Data Length, Four External Peripheral Chip Selects

- One Three-channel 16-bit Timer/Counters (TC)

- Three External Clock Inputs, Two multi-purpose I/O Pins per Channel

- Double PWM Generation, Capture/Waveform Mode, Up/Down Capability

- Two-wire Interface (TWI)

- Master Mode Support, All Two-wire Atmel EEPROMs Supported

- IEEE® 1149.1 JTAG Boundary Scan on All Digital Pins

- Required Power Supplies:

- 1.08V to 1.32V for VDDCORE and VDDBU

- 3.0V to 3.6V for VDDOSC and for VDDPLL

- 2.7V to 3.6V for VDDIOP (Peripheral I/Os)

- 1.65V to 1.95V and 3.0V to 3.6V for VDDIOM (Memory I/Os)

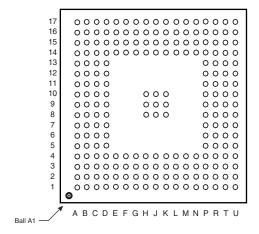

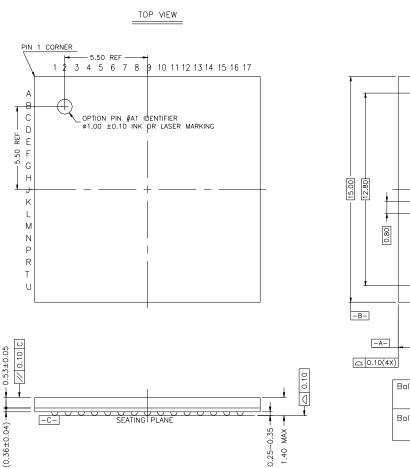

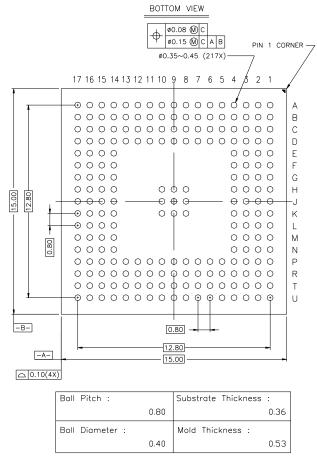

- Available in a 217-ball LFBGA RoHS-compliant Package

# 1. Description

The AT91SAM9261S is a complete system-on-chip built around the ARM926EJ-S ARM Thumb processor with an extended DSP instruction set and Jazelle Java accelerator. It achieves 210 MIPS at 190 MHz.

The AT91SAM9261S is an optimized host processor for applications with an LCD display. Its integrated LCD controller supports BW and up to 16M color, active and passive LCD displays. The 16 Kbyte integrated SRAM can be configured as a frame buffer minimizing the impact for LCD refresh on the overall processor performance. The External Bus Interface incorporates controllers for synchronous DRAM (SDRAM) and Static memories and features specific interface circuitry for CompactFlash and NAND Flash.

The AT91SAM9261S integrates a ROM-based Boot Loader supporting code shadowing from, for example, external DataFlash® into external SDRAM. The software controlled Power Management Controller (PMC) keeps system power consumption to a minimum by selectively enabling/disabling the processor and various peripherals and adjustment of the operating frequency.

The AT91SAM9261S also benefits from the integration of a wide range of debug features including JTAG-ICE, a dedicated UART debug channel (DBGU) and an embedded real time trace. This enables the development and debug of all applications, especially those with real-time constraints.

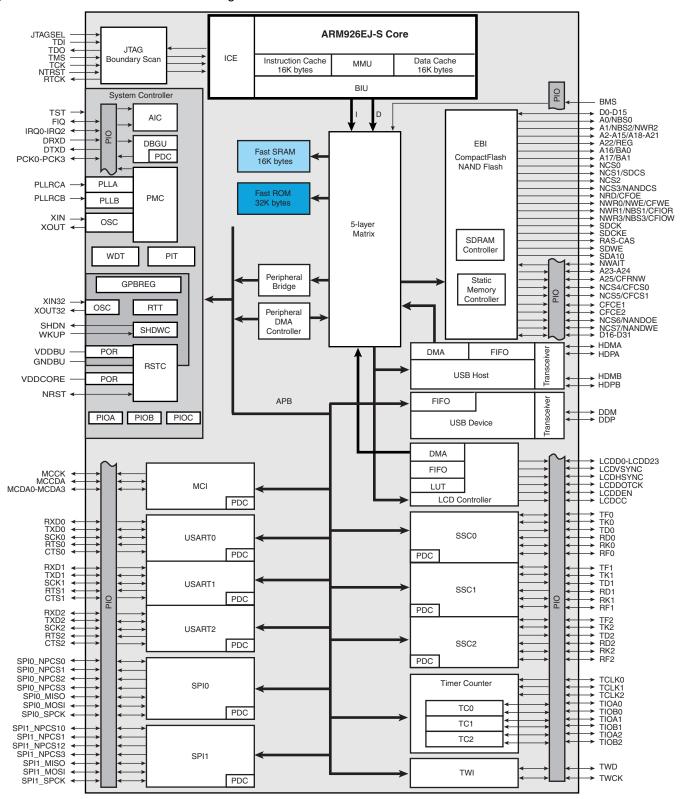

# 2. Block Diagram

Figure 2-1. AT91SAM9261S Block Diagram

# 3. Signal Description

Table 3-1.

Signal Description by Peripheral

| Signal Name | Function                           | Туре            | Active Level | Comments                                          |

|-------------|------------------------------------|-----------------|--------------|---------------------------------------------------|

|             | Р                                  | ower            |              |                                                   |

| VDDIOM      | EBI I/O Lines Power Supply         | Power           |              | 1.65 V to 1.95V and 3.0V to 3.6V                  |

| VDDIOP      | Peripherals I/O Lines Power Supply | Power           |              | 2.7V to 3.6V                                      |

| VDDBU       | Backup I/O Lines Power Supply      | Power           |              | 1.08V to 1.32V                                    |

| VDDPLL      | PLL Power Supply                   | Power           |              | 3.0V to 3.6V                                      |

| VDDOSC      | Oscillator Power Supply            | Power           |              | 3.0V to 3.6V                                      |

| VDDCORE     | Core Chip Power Supply             | Power           |              | 1.08V to 1.32V                                    |

| GND         | Ground                             | Ground          |              |                                                   |

| GNDPLL      | PLL Ground                         | Ground          |              |                                                   |

| GNDOSC      | Oscillator Ground                  | Ground          |              |                                                   |

| GNDBU       | Backup Ground                      | Ground          |              |                                                   |

|             | Clocks, Osci                       | llators and PLL | _S           |                                                   |

| XIN         | Main Oscillator Input              | Input           |              |                                                   |

| XOUT        | Main Oscillator Output             | Output          |              |                                                   |

| XIN32       | Slow Clock Oscillator Input        | Input           |              |                                                   |

| XOUT32      | Slow Clock Oscillator Output       | Output          |              |                                                   |

| PLLRCA      | PLL Filter                         | Input           |              |                                                   |

| PLLRCB      | PLL Filter                         | Input           |              |                                                   |

| PCK0 - PCK3 | Programmable Clock Output          | Output          |              |                                                   |

|             | Shutdown,                          | Wakeup Logic    |              |                                                   |

| SHDN        | Shutdown Control                   | Output          |              | Do not tie over VDDBU.                            |

| WKUP        | Wake-Up Input                      | Input           |              | Accepts between 0V and VDDBU.                     |

|             | ICE a                              | nd JTAG         |              |                                                   |

| TCK         | Test Clock                         | Input           |              | No pull-up resistor.                              |

| RTCK        | Returned Test Clock                | Output          |              | No pull-up resistor.                              |

| TDI         | Test Data In                       | Input           |              | No pull-up resistor.                              |

| TDO         | Test Data Out                      | Output          |              |                                                   |

| TMS         | Test Mode Select                   | Input           |              | No pull-up resistor.                              |

| NTRST       | Test Reset Signal                  | Input           | Low          | Pull-up resistor.                                 |

| JTAGSEL     | JTAG Selection                     | Input           |              | Pull-down resistor. Accepts between 0V and VDDBU. |

|             | Res                                | et/Test         |              |                                                   |

| NRST        | Microcontroller Reset              | I/O             | Low          | Pull-up resistor                                  |

| TST         | Test Mode Select                   | Input           |              | Pull-down resistor.                               |

| BMS         | Boot Mode Select                   | Input           |              |                                                   |

|             | Deb                                | ug Unit         |              |                                                   |

| DRXD        | Debug Receive Data                 | Input           |              |                                                   |

| DTXD        | Debug Transmit Data                | Output          |              |                                                   |

|             |                                    |                 |              |                                                   |

Table 3-1.

Signal Description by Peripheral (Continued)

| Signal Name   | Function                       | Туре             | Active Level | Comments                 |  |

|---------------|--------------------------------|------------------|--------------|--------------------------|--|

|               | ·                              | AIC              |              |                          |  |

| IRQ0 - IRQ2   | External Interrupt Inputs      | Input            |              |                          |  |

| FIQ           | Fast Interrupt Input           | Input            |              |                          |  |

|               |                                | PIO              |              |                          |  |

| PA0 - PA31    | Parallel IO Controller A       | I/O              |              | Pulled-up input at reset |  |

| PB0 - PB31    | Parallel IO Controller B       | I/O              |              | Pulled-up input at reset |  |

| PC0 - PC31    | Parallel IO Controller C       | I/O              |              | Pulled-up input at reset |  |

|               |                                | EBI              |              |                          |  |

| D0 - D31      | Data Bus                       | I/O              |              | Pulled-up input at reset |  |

| A0 - A25      | Address Bus                    | Output           |              | 0 at reset               |  |

| NWAIT         | External Wait Signal           | Input            | Low          |                          |  |

|               |                                | SMC              |              |                          |  |

| NCS0 - NCS7   | Chip Select Lines              | Output           | Low          |                          |  |

| NWR0 - NWR3   | Write Signal                   | Output           | Low          |                          |  |

| NRD           | Read Signal                    | Output           | Low          |                          |  |

| NWE           | Write Enable                   | Output           | Low          |                          |  |

| NBS0 - NBS3   | Byte Mask Signal               | Output           | Low          |                          |  |

|               | Compact                        | Flash Support    |              |                          |  |

| CFCE1 - CFCE2 | CompactFlash Chip Enable       | Output           | Low          |                          |  |

| CFOE          | CompactFlash Output Enable     | Output           | Low          |                          |  |

| CFWE          | CompactFlash Write Enable      | Output           | Low          |                          |  |

| CFIOR         | CompactFlash IO Read           | Output           | Low          |                          |  |

| CFIOW         | CompactFlash IO Write          | Output           | Low          |                          |  |

| CFRNW         | CompactFlash Read Not Write    | Output           |              |                          |  |

| CFCS0 - CFCS1 | CompactFlash Chip Select Lines | Output           | Low          |                          |  |

|               | NAND F                         | lash Support     |              |                          |  |

| NANDOE        | NAND Flash Output Enable       | Output           | Low          |                          |  |

| NANDWE        | NAND Flash Write Enable        | Output           | Low          |                          |  |

| NANDCS        | NAND Flash Chip Select         | Output           | Low          |                          |  |

|               | SDRAM                          | M Controller     |              |                          |  |

| SDCK          | SDRAM Clock                    | Output           |              |                          |  |

| SDCKE         | SDRAM Clock Enable             | Output           | High         |                          |  |

| SDCS          | SDRAM Controller Chip Select   | Output           | Low          |                          |  |

| BA0 - BA1     | Bank Select                    | Output           |              |                          |  |

| SDWE          | SDRAM Write Enable             | Output           | Low          |                          |  |

| RAS - CAS     | Row and Column Signal          | Output           | Output Low   |                          |  |

| SDA10         | SDRAM Address 10 Line          | Output           |              |                          |  |

|               | Multimedia                     | a Card Interface |              | 1                        |  |

| MCCK          | Multimedia Card Clock          | Output           |              |                          |  |

| MCCDA         | Multimedia Card A Command      | I/O              |              |                          |  |

| MCDA0 - MCDA3 | Multimedia Card A Data         | I/O              |              |                          |  |

Table 3-1.

Signal Description by Peripheral (Continued)

| Signal Name                                              | Function                       | Туре           | Active Level | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|----------------------------------------------------------|--------------------------------|----------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                          |                                | JSART          |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| SCK0 - SCK2                                              | Serial Clock                   | I/O            |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| TXD0 - TXD2                                              | Transmit Data                  | Output         |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| RXD0 - RXD2                                              | Receive Data                   | Input          |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| RTS0 - RTS2                                              | Request To Send                | Output         |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| CTS0 - CTS2                                              | Clear To Send                  | Input          |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| Synchronous Serial Controller                            |                                |                |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| TD0 - TD2                                                | Transmit Data                  | Output         |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| RD0 - RD2                                                | Receive Data                   | Input          |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| TK0 - TK2                                                | Transmit Clock                 | I/O            |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| RK0 - RK2                                                | Receive Clock                  | I/O            |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| TF0 - TF2                                                | Transmit Frame Sync            | I/O            |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| RF0 - RF2                                                | Receive Frame Sync             | I/O            |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                                                          | Time                           | er/Counter     |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| TCLK0 - TCLK2                                            | External Clock Input           | Input          |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| TIOA0 - TIOA2                                            | I/O Line A                     | I/O            |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| TIOB0 - TIOB2                                            | I/O Line B                     | I/O            |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                                                          |                                | SPI            |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| SPI0_MISO -<br>SPI1_MISO                                 | Master In Slave Out            | I/O            |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| SPI0_MOSI -<br>SPI1_MOSI                                 | Master Out Slave In            | I/O            |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| SPI0_SPCK -<br>SPI1_SPCK                                 | SPI Serial Clock               | I/O            |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| SPI0_NPCS0,<br>SPI1_NPCS0                                | SPI Peripheral Chip Select 0   | I/O            | Low          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| SPI0_NPCS1 -<br>SPI0_NPCS3<br>SPI1_NPCS1 -<br>SPI1_NPCS3 | SPI Peripheral Chip Select     | Output         | Low          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                                                          | Two-W                          | /ire Interface |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| TWD                                                      | Two-wire Serial Data           | I/O            |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| TWCK                                                     | Two-wire Serial Clock          | I/O            |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |