# RENESAS

# HN58X25128I HN58X25256I

Serial Peripheral Interface 128k EEPROM (16-kword × 8-bit) 256k EEPROM (32-kword × 8-bit) Electrically Erasable and Programmable Read Only Memory

> REJ03C0059-0300 Rev.3.00 Jul.06.2005

# Description

HN58X25xxx Series is the Serial Peripheral Interface compatible (SPI) EEPROM (Electrically Erasable and Programmable ROM). It realizes high speed, low power consumption and a high level of reliability by employing advanced MONOS memory technology and CMOS process and low voltage circuitry technology. It also has a 64-byte page programming function to make it's write operation faster.

Note: Renesas Technology's serial EEPROM are authorized for using consumer applications such as cellular phones, camcorders, audio equipments. Therefore, please contact Renesas Technology's sales office before using industrial applications such as automotive systems, embedded controllers, and meters.

# Features

- Single supply: 1.8 V to 5.5 V

- Serial Peripheral Interface compatible (SPI bus)

SPI mode 0 (0,0), 3 (1,1)

- Clock frequency: 5 MHz (2.5 V to 5.5 V), 3 MHz (1.8 V to 5.5 V)

- Power dissipation:

- Standby:  $3 \mu A (max)$

- Active (Read): 4 mA (max)

- Active (Write): 4 mA (max)

- Automatic page write: 64-byte/page

- Write cycle time: 5 ms (2.5 V min), 8 ms (1.8 V min)

- Endurance: 10<sup>6</sup> Erase/Write Cycles

- Data retention: 10 Years

- Small size packages: SOP-8pin and TSSOP-14pin

- Shipping tape and reel

- TSSOP-14pin : 2,000 IC/reel

- SOP-8pin : 2,500 IC/reel

- Temperature range: -40 to +85°C

- Lead free product.

# **Ordering Information**

| Type No.       | Internal organization    | Operating voltage | Frequency                 | Package                                  |

|----------------|--------------------------|-------------------|---------------------------|------------------------------------------|

| HN58X25128FPIE | 128-kbit (16834 × 8-bit) | 1.8 V to 5.5 V    | 5 MHz<br>(2.5 V to 5.5 V) | 150mil 8-pin plastic SOP<br>PRSP0008DF-B |

| HN58X25256FPIE | 256-kbit (32768 × 8-bit) | -                 | 3 MHz<br>(1.8 V to 5.5 V) | (FP-8DBV)<br>Lead free                   |

| HN58X25128TIE  | 128-kbit (16834 × 8-bit) | 1.8 V to 5.5 V    | 5 MHz<br>(2.5 V to 5.5 V) | 14-pin plastic TSSOP<br>PTSP0014JA-C     |

| HN58X25256TIE  | 256-kbit (32768 × 8-bit) |                   | 3 MHz<br>(1.8 V to 5.5 V) | (TTP-14DBV)<br>Lead free                 |

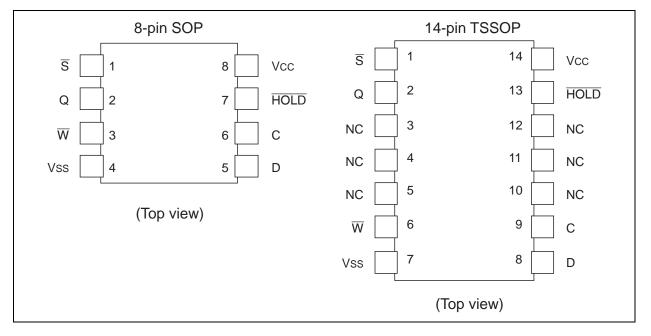

# **Pin Arrangement**

# **Pin Description**

| Pin name        | Function           |

|-----------------|--------------------|

| С               | Serial clock       |

| D               | Serial data input  |

| Q               | Serial data output |

| S               | Chip select        |

| W               | Write protect      |

| HOLD            | Hold               |

| V <sub>cc</sub> | Supply voltage     |

| V <sub>SS</sub> | Ground             |

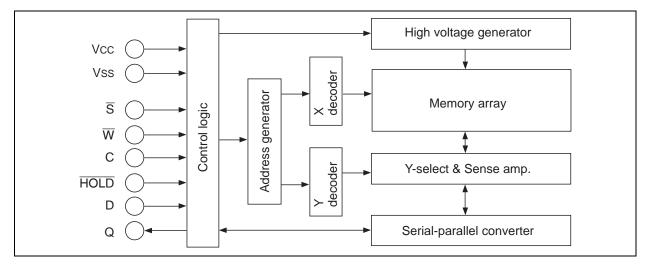

# **Block Diagram**

# **Absolute Maximum Ratings**

| Parameter                                  | Symbol          | Value                      | Unit |

|--------------------------------------------|-----------------|----------------------------|------|

| Supply voltage relative to V <sub>SS</sub> | V <sub>CC</sub> | -0.6 to + 7.0              | V    |

| Input voltage relative to V <sub>SS</sub>  | V <sub>IN</sub> | $-0.5^{*2}$ to $+7.0^{*3}$ | V    |

| Operating temperature range*1              | Topr            | -40 to +85                 | ٥°   |

| Storage temperature range                  | Tstg            | -65 to +125                | ۵°   |

Notes: 1. Including electrical characteristics and data retention.

2.  $V_{IN}$  (min): -3.0 V for pulse width  $\leq$  50 ns.

3. Should not exceed  $V_{CC}$  + 1.0 V.

# **DC Operating Conditions**

| Parameter                   | Symbol          | Min                | Тур | Max                | Unit |

|-----------------------------|-----------------|--------------------|-----|--------------------|------|

| Supply voltage              | V <sub>CC</sub> | 1.8                | —   | 5.5                | V    |

|                             | V <sub>SS</sub> | 0                  | 0   | 0                  | V    |

| Input voltage               | V <sub>IH</sub> | $V_{CC} 	imes 0.7$ | —   | $V_{CC} + 0.5*^2$  | V    |

|                             | V <sub>IL</sub> | -0.3* <sup>1</sup> | —   | $V_{CC} 	imes 0.3$ | V    |

| Operating temperature range | Topr            | -40                | —   | +85                | °C   |

Notes: 1.  $V_{IN}$  (min): -1.0 V for pulse width  $\leq$  50 ns.

2.  $V_{\text{IN}}$  (max):  $V_{\text{CC}}$  + 1.0 V for pulse width  $\leq 50$  ns.

# **DC Characteristics**

| Param                   | eter    | Symbol           | Min                | Max | Unit | Test conditions                                                                                                           |

|-------------------------|---------|------------------|--------------------|-----|------|---------------------------------------------------------------------------------------------------------------------------|

| Input leakage current   |         | ILI              | _                  | 2   | μA   |                                                                                                                           |

| Output leakage curre    | nt      | I <sub>LO</sub>  |                    | 2   | μA   | $V_{CC} = 5.5 \text{ V}, V_{OUT} = 0 \text{ to } 5.5 \text{ V}$ (Q)                                                       |

| V <sub>CC</sub> current | Standby | I <sub>SB</sub>  |                    | 3   | μΑ   | $V_{IN} = V_{SS} \text{ or } V_{CC},$<br>$V_{CC} = 5.5 \text{ V}$                                                         |

|                         | Active  | I <sub>CC1</sub> |                    | 2.5 | mA   | $V_{CC} = 3.6 \text{ V}, \text{ Read at 5 MHz}$ $V_{\text{IN}} = V_{CC} \times 0.1 / V_{CC} \times 0.9$ $Q = \text{OPEN}$ |

|                         |         |                  |                    | 4   | mA   | $V_{CC}$ = 5.5 V, Read at 5 MHz<br>$V_{IN} = V_{CC} \times 0.1 / V_{CC} \times 0.9$<br>Q = OPEN                           |

|                         |         | I <sub>CC2</sub> |                    | 2.5 | mA   | $V_{CC}$ = 3.6 V, Write at 5 MHz<br>$V_{IN} = V_{CC} \times 0.1 / V_{CC} \times 0.9$                                      |

|                         |         |                  |                    | 4   | mA   | $V_{CC}$ = 5.5 V, Write at 5 MHz<br>$V_{IN}$ = $V_{CC} \times 0.1/V_{CC} \times 0.9$                                      |

| Output voltage          |         | V <sub>OL1</sub> | —                  | 0.4 | V    | $V_{CC} = 5.5 \text{ V}, I_{OL} = 2 \text{ mA}$                                                                           |

|                         |         | V <sub>OL2</sub> |                    | 0.4 | V    | $V_{CC} = 2.5 \text{ V}, I_{OL} = 1.5 \text{ mA}$                                                                         |

|                         |         | V <sub>OH1</sub> | $V_{CC} 	imes 0.8$ |     | V    | $V_{CC}$ = 5.5 V, $I_{OL}$ = -2 mA                                                                                        |

|                         |         | V <sub>OH2</sub> | $V_{CC} 	imes 0.8$ |     | V    | $V_{CC} = 2.5 \text{ V}, I_{OL} = -0.4 \text{ mA}$                                                                        |

# **AC Characteristics**

# **Test Conditions**

- Input pules levels:

- $--V_{IL} = V_{CC} \times 0.2$

- $--V_{\rm IH} = V_{\rm CC} \times 0.8$

- Input rise and fall time:  $\leq 10$  ns

- Input and output timing reference levels:  $V_{CC} \times 0.3, \, V_{CC} \times 0.7$

- Output reference levels:  $V_{CC} \times 0.5$

- Output load: 100 pF

| Parameter                                 | Symbol            | Alt                                  | Min             | Max | Unit   | Notes |

|-------------------------------------------|-------------------|--------------------------------------|-----------------|-----|--------|-------|

| Clock frequency                           | f <sub>C</sub>    | f <sub>scк</sub>                     |                 | 5   | MHz    | Notes |

| S active setup time                       | t <sub>SLCH</sub> | t <sub>CSS1</sub>                    | 90              | _   | ns     |       |

| S not active setup time                   |                   |                                      | 90              |     | ns     |       |

| $\overline{S}$ deselect time              | t <sub>SHCH</sub> | t <sub>CSS2</sub><br>t <sub>CS</sub> | 90              |     | ns     |       |

| S active hold time                        | t <sub>SHSL</sub> |                                      | 90              |     | ns     |       |

| $\overline{S}$ not active hold time       | t <sub>CHSH</sub> | t <sub>CSH</sub>                     | 90              |     |        |       |

|                                           | t <sub>CHSL</sub> |                                      |                 |     | ns     | 4     |

| Clock high time                           | t <sub>CH</sub>   | t <sub>CLH</sub>                     | 90              |     | ns     | 1     |

| Clock low time                            | t <sub>CL</sub>   | t <sub>CLL</sub>                     | 90              |     | ns     | 1     |

| Clock rise time                           | t <sub>CLCH</sub> | t <sub>RC</sub>                      |                 | 1   | μs     | 2     |

| Clock fall time                           | t <sub>CHCL</sub> | t <sub>FC</sub>                      |                 | 1   | μs     | 2     |

| Data in setup time                        | t <sub>DVCH</sub> | t <sub>DSU</sub>                     | 20              | —   | ns     |       |

| Data in hold time                         | t <sub>CHDX</sub> | t <sub>DH</sub>                      | 30              |     | ns     |       |

| Clock low hold time after HOLD not active | t <sub>HHCH</sub> |                                      | 70              |     | ns     |       |

| Clock low hold time after HOLD active     | t <sub>HLCH</sub> |                                      | 40              |     | ns     |       |

| Clock high setup time before HOLD active  | t <sub>CHHL</sub> |                                      | 60              |     | ns     |       |

| Clock high setup time before HOLD not     | t <sub>сннн</sub> |                                      | 60              |     | ns     |       |

| active                                    |                   |                                      |                 |     |        |       |

| Output disable time                       | t <sub>SHQZ</sub> | t <sub>DIS</sub>                     |                 | 100 | ns     | 2     |

| Clock low to output valid                 | t <sub>CLQV</sub> | t <sub>v</sub>                       |                 | 70  | ns     |       |

| Output hold time                          | t <sub>CLQX</sub> | t <sub>HO</sub>                      | 0               |     | ns     |       |

| Output rise time                          | t <sub>QLQH</sub> | t <sub>RO</sub>                      |                 | 50  | ns     | 2     |

| Output fall time                          | t <sub>QHQL</sub> | t <sub>FO</sub>                      |                 | 50  | ns     | 2     |

| HOLD high to output low-Z                 | t <sub>HHQX</sub> | t <sub>LZ</sub>                      |                 | 50  | ns     | 2     |

| HOLD low to output low-Z                  | t <sub>HLQZ</sub> | t <sub>HZ</sub>                      |                 | 100 | ns     | 2     |

| Write time                                | t <sub>W</sub>    | t <sub>WC</sub>                      |                 | 5   | ms     |       |

| Erase / Write Endurance                   |                   |                                      | 10 <sup>6</sup> |     | cycles | 3     |

Notes: 1.  $t_{CH} + t_{CL} \geq 1/f_C$

2. Value guaranteed by characterization, not 100% tested in production.

3. Value guaranteed by characterization, not 100% tested in products (Ta = 25°C).

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (Ta                                                    | °C, $V_{CC} = 1.8$ V to 5.5 V)                         |                                                        |                                                        |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|

| Symbol            | Alt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Min                                                    | Max                                                    | Unit                                                   | Notes                                                  |

| f <sub>C</sub>    | f <sub>scк</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                        | 3                                                      | MHz                                                    |                                                        |

| t <sub>SLCH</sub> | t <sub>CSS1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 100                                                    | —                                                      | ns                                                     |                                                        |

| t <sub>SHCH</sub> | t <sub>CSS2</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 100                                                    | —                                                      | ns                                                     |                                                        |

| t <sub>SHSL</sub> | t <sub>CS</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 150                                                    | —                                                      | ns                                                     |                                                        |

| t <sub>CHSH</sub> | t <sub>CSH</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 100                                                    |                                                        | ns                                                     |                                                        |

| t <sub>CHSL</sub> | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 100                                                    |                                                        | ns                                                     |                                                        |

| t <sub>CH</sub>   | t <sub>CLH</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 150                                                    | —                                                      | ns                                                     | 1                                                      |

| t <sub>CL</sub>   | t <sub>CLL</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 150                                                    | —                                                      | ns                                                     | 1                                                      |

| t <sub>CLCH</sub> | t <sub>RC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                        | 1                                                      | μs                                                     | 2                                                      |

| t <sub>CHCL</sub> | t <sub>FC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                        | 1                                                      | μs                                                     | 2                                                      |

| t <sub>DVCH</sub> | t <sub>DSU</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 30                                                     | —                                                      | ns                                                     |                                                        |

| t <sub>CHDX</sub> | t <sub>DH</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 50                                                     | —                                                      | ns                                                     |                                                        |

| t <sub>HHCH</sub> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 140                                                    | —                                                      | ns                                                     |                                                        |

| t <sub>HLCH</sub> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 90                                                     | —                                                      | ns                                                     |                                                        |

| t <sub>CHHL</sub> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 120                                                    | —                                                      | ns                                                     |                                                        |

| t <sub>СННН</sub> | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 120                                                    | —                                                      | ns                                                     |                                                        |

| t <sub>SHQZ</sub> | t <sub>DIS</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                        | 200                                                    | ns                                                     | 2                                                      |

| t <sub>CLQV</sub> | t <sub>v</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                        | 120                                                    | ns                                                     |                                                        |

| t <sub>CLQX</sub> | t <sub>HO</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0                                                      | —                                                      | ns                                                     |                                                        |

| t <sub>QLQH</sub> | t <sub>RO</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _                                                      | 100                                                    | ns                                                     | 2                                                      |

| t <sub>QHQL</sub> | t <sub>FO</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                        | 100                                                    | ns                                                     | 2                                                      |

| t <sub>HHQX</sub> | t <sub>LZ</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                        | 100                                                    | ns                                                     | 2                                                      |

| t <sub>HLQZ</sub> | t <sub>HZ</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                        | 100                                                    | ns                                                     | 2                                                      |

| t <sub>W</sub>    | t <sub>WC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                        | 8                                                      | ms                                                     |                                                        |

| —                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10 <sup>6</sup>                                        |                                                        | cycles                                                 | 3                                                      |

|                   | fc           tslch           tshch           tshch           tchsh           tclov           tclov           tclov           tclov           toloh           theox           thloz | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ |

Notes: 1.  $t_{CH} + t_{CL} \ge 1/f_C$

2. Value guaranteed by characterization, not 100% tested in production.

3. Value guaranteed by characterization, not 100% tested in products (Ta =  $25^{\circ}$ C).

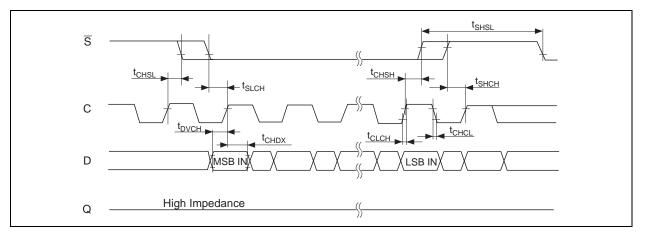

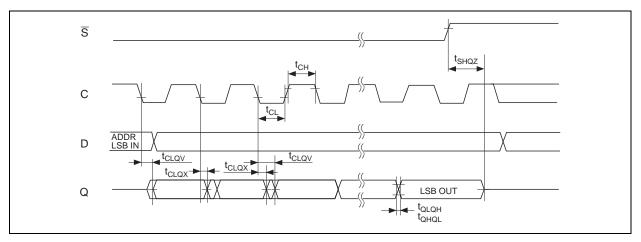

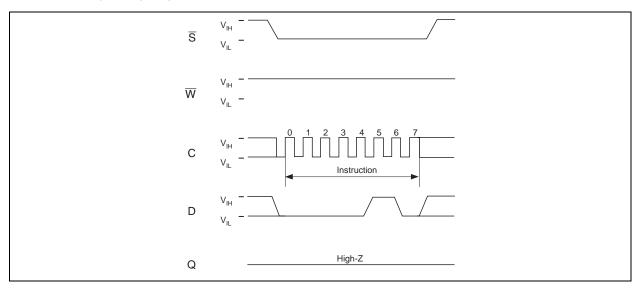

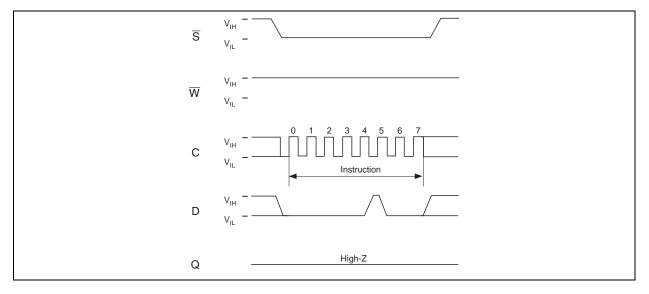

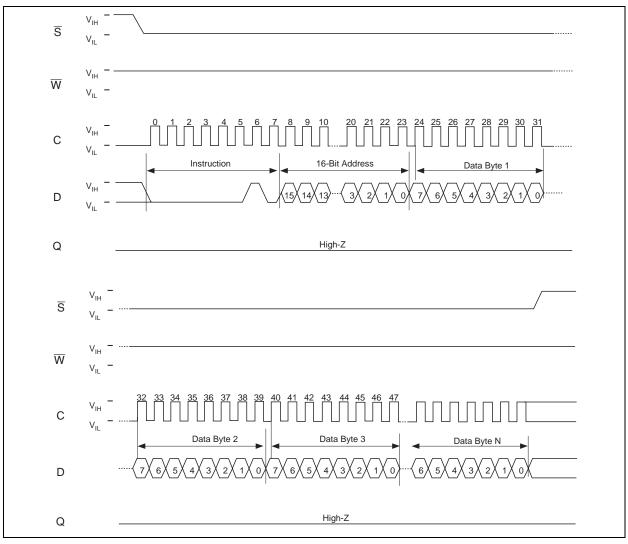

# **Timing Waveforms**

# Serial Input Timing

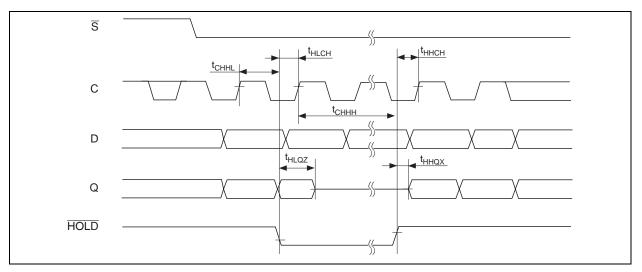

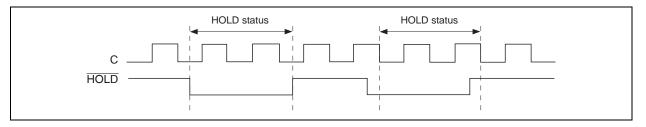

# Hold Timing

# **Output Timing**

Rev.3.00, Jul.06.2005, page 7 of 20

# **Pin Function**

#### Serial data output (Q)

This output signal is used to transfer data serially out of the device. Data is shifted out on the falling edge of serial clock (C).

#### Serial data input (D)

This input signal is used to transfer data serially into the device. It receives instructions, addresses, and the data to be written. Values are latched on the rising edge of serial clock (C).

#### Serial clock (C)

This input signal provides the timing of the serial interface. Instructions, addresses, or data present at serial data input (D) are latched on the rising edge of serial clock (C). Data on serial data output (Q) changes after the falling edge of serial clock (C).

### Chip select $(\overline{S})$

When this input signal is high, the device is deselected and serial data output (Q) is at high impedance. Unless an internal write cycle is in progress, the device will be in the standby mode. Driving chip select  $(\overline{S})$  low enables the device, placing it in the active power mode. After power-up, a falling edge on chip select  $(\overline{S})$  is required prior to the start of any instruction.

#### Hold $(\overline{HOLD})$

The hold ( $\overline{\text{HOLD}}$ ) signal is used to pause any serial communications with the device without deselecting the device. During the hold condition, the serial data output (Q) is high impedance, and serial data input (D) and serial clock (C) are don't care. To start the hold condition, the device must be selected, with chip select ( $\overline{S}$ ) driven low.

#### Write protect $(\overline{W})$

The main purpose of this input signal is to freeze the size of the area of memory that is protected against write instructions (as specified by the values in the BP1 and BP0 bits of the status register). This pin must be driven either high or low, and must be stable during all write operations.

# **Functional Description Functional Description**

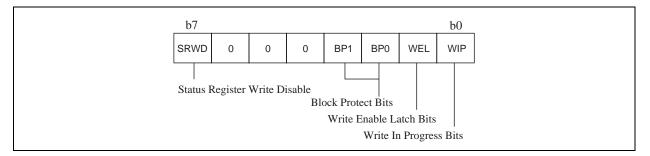

#### **Status Register**

The following figure shows the Status Register Format. The Status Register contains a number of status and control bits that can be read or set (as appropriate) by specific instructions.

#### **Status Register Format**

WIP bit: The Write In Progress (WIP) bit indicates whether the memory is busy with a Write or Write Status Register cycle.

WEL bit: The Write Enable Latch (WEL) bit indicates the status of the internal Write Enable Latch.

BP1, BP0 bits: The Block Protect (BP1, BP0) bits are non-volatile. They define the size of the area to be software protected against Write instructions.

SRWD bit: The Status Register Write Disable (SRWD) bit is operated in conjunction with the write protect  $(\overline{W})$  signal. The Status Register Write Disable (SRWD) bit and write protect  $(\overline{W})$  signal allow the device to be put in the Hardware Protected mode. In this mode, the non-volatile bits of the Status Register (SRWD, BP1, BP0) become read-only bits.

#### Instructions

Each instruction starts with a single-byte code, as summarized in the following table . If an invalid instruction is sent (one not contained in the following table), the device automatically deselects itself.

#### Instruction Set

| Instruction | Description            | Instruction Format |

|-------------|------------------------|--------------------|

| WREN        | Write Enable           | 0000 0110          |

| WRDI        | Write Disable          | 0000 0100          |

| RDSR        | Read Status Register   | 0000 0101          |

| WRSR        | Write Status Register  | 0000 0001          |

| READ        | Read from Memory Array | 0000 0011          |

| WRITE       | Write to Memory Array  | 0000 0010          |

#### Write Enable (WREN):

The Write Enable Latch (WEL) bit must be set prior to each WRITE and WRSR instruction. The only way to do this is to send a Write Enable instruction to the device. As shown in the following figure, to send this instruction to the device, chip select  $(\overline{S})$  is driven low, and the bits of the instruction byte are shifted in, on serial data input (D). The device then enters a wait state. It waits for the device to be deselected, by chip select  $(\overline{S})$  being driven high.

#### Write Enable (WREN) Sequence

#### Write Disable (WRDI):

One way of resetting the Write Enable Latch (WEL) bit is to send a Write Disable instruction to the device. As shown in the following figure, to send this instruction to the device, chip select  $(\overline{S})$  is driven low, and the bits of the instruction byte are shifted in, on serial data input (D).

The device then enters a wait state. It waits for the device to be deselected, by chip select  $(\overline{S})$  being driven high. The Write Enable Latch (WEL) bit, in fact, becomes reset by any of the following events:

- Power-up

- WRDI instruction execution

- WRSR instruction completion

- WRITE instruction completion

### Write Disable (WRDI) Sequence

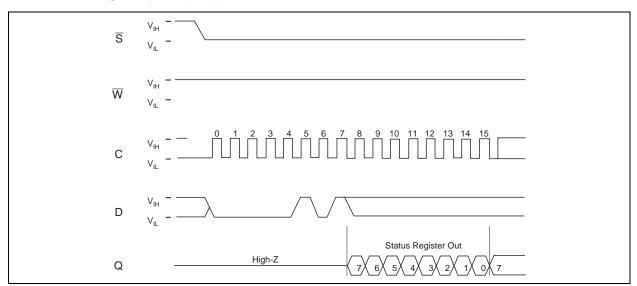

#### Read Status Register (RDSR):

The Read Status Register (RDSR) instruction allows the Status Register to be read. The Status Register may be read at any time, even while a Write or Write Status Register cycle is in progress. When one of these cycles is in progress, it is recommended to check the Write In Progress (WIP) bit before sending a new instruction to the device. It is also possible to read the Status Register continuously, as shown in the following figure.

#### Read Status Register (RDSR) Sequence

The status and control bits of the Status Register are as follows:

WIP bit: The Write In Progress (WIP) bit indicates whether the memory is busy with a Write or Write Status Register cycle. When set to 1, such a cycle is in progress. When reset to 0, no such cycles are in progress.

WEL bit: The Write Enable Latch (WEL) bit indicates the status of the internal Write Enable Latch. When set to 1, the internal Write Enable Latch is set. When set to 0, the internal Write Enable Latch is reset and no Write or Write Status Register instructions are accepted.

BP1, BP0 bits: The Block Protect (BP1, BP0) bits are non-volatile. They define the size of the area to be software protected against Write instructions. These bits are written with the Write Status Register (WRSR) instruction. When one or both of the Block Protect (BP1, BP0) bits are set to 1, the relevant memory area (as defined in the Status Register Format table) becomes protected against Write (WRITE) instructions. The Block Protect (BP1, BP0) bits can be written provided that the Hardware Protected mode has not been set.

SRWD bit: The Status Register Write Disable (SRWD) bit is operated in conjunction with the write protect  $(\overline{W})$  signal. The Status Register Write Disable (SRWD) bit and write protect  $(\overline{W})$  signal allows the device to be put in the Hardware Protected mode (When the Status Register Write Disable (SRWD) bit is set to 1, and write protect  $(\overline{W})$  signal is driven low). In this mode, the non-volatile bits of the Status Register (SRWD, BP1, BP0) become read-only bits and the Write Status Register (WRSR) instruction is no longer accepted for execution.

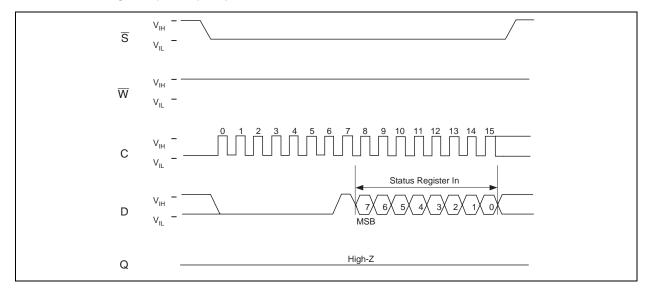

#### Write Status Register (WRSR):

The Write Status Register (WRSR) instruction allows new values to be written to the Status Register. Before it can be accepted, a Write Enable (WREN) instruction must previously have been executed. After the Write Enable (WREN) instruction has been decoded and executed, the device sets the Write Enable Latch(WEL). The instruction sequence is shown in the following figure. The Write Status Register (WRSR) instruction has no effect on b6, b5, b4, b1 and b0 of the Status Register. b6, b5 and b4 are always read as 0. Chip select ( $\overline{S}$ ) must be driven high after the rising edge of serial clock (C) that latches in the eighth bit of the data byte, and before the next rising edge of serial clock (C). Otherwise, the Write Status Register (WRSR) instruction is not executed. As soon as chip select ( $\overline{S}$ ) is driven high, the self-timed Write Status Register may still be read to check the value of the Write In Progress (WIP) bit. The Write In Progress (WIP) bit is 1 during the self-timed Write Status Register cycle, and is 0 when it is completed. When the cycle is completed, Write Enable Latch(WEL) is reset. The Write Status Register (WRSR) instruction allows the user to change the values of the Block Protect (BP1, BP0) bits, to define the size of the area that is to be treated as read-only, as defined in the Status Register Format table.

The Write Status Register (WRSR) instruction also allows the user to set or reset the Status Register Write Disable (SRWD) bit in accordance with the write protect  $(\overline{W})$  signal. The Status Register Write Disable (SRWD) bit and write protect  $(\overline{W})$  signal allows the device to be put in the Hardware Protected Mode (HPM). The Write Status Register (WRSR) instruction is not executed once the Hardware Protected Mode (HPM) is entered.

The contents of the Status Register Write Disable (SRWD) and Block Protect (BP1, BP0) bits are frozen at their current values just before the start of the execution of the Write Status Register (WRSR) instruction. The new, updated values take effect at the moment of completion of the execution of Write Status Register (WRSR) instruction.

#### Write Status Register (WRSR) Sequence

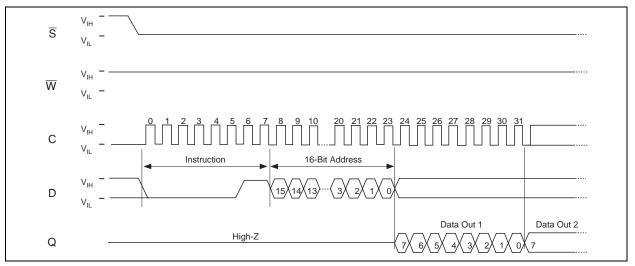

#### Read from Memory Array (READ):

As shown in the following figure, to send this instruction to the device, chip select  $(\overline{S})$  is first driven low. The bits of the instruction byte and the address bytes are then shifted in, on serial data input (D). The addresses are loaded into an internal address register, and the byte of data at that address is shifted out, on serial data output (Q).

If chip select  $(\overline{S})$  continues to be driven low, the internal address register is automatically incremented, and the byte of data at the new address is shifted out.

When the highest address is reached, the address counter rolls over to zero, allowing the Read cycle to be continued indefinitely. The whole memory can, therefore, be read with a single READ instruction.

The Read cycle is terminated by driving chip select  $(\overline{S})$  high. The rising edge of the chip select  $(\overline{S})$  signal can occur at any time during the cycle. The addressed first byte can be any byte within any page. The instruction is not accepted, and is not executed, if a Write cycle is currently in progress.

#### Read from Memory Array (READ) Sequence

Note: 1. Depending on the memory size, as shown in the following table, the most significant address bits are don't care.

#### Address Range Bits

| Device       | HN58X25256I | HN58X25128I |

|--------------|-------------|-------------|

| Address bits | A14 to A0   | A13 to A0   |

Notes: 1. b15 is don't care on the HN58X25256

2. b15 and b14 are don't care on the HN58X25128

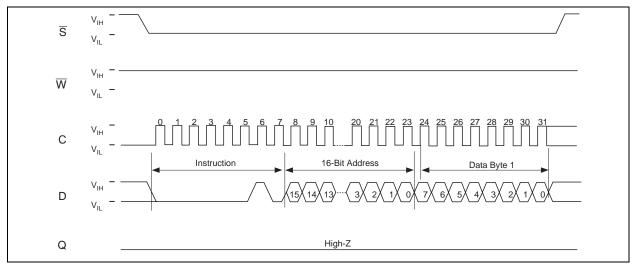

#### Write to Memory Array (WRITE):

As shown in the following figure, to send this instruction to the device, chip select  $(\overline{S})$  is first driven low. The bits of the instruction byte, address byte, and at least one data byte are then shifted in, on serial data input (D).

The instruction is terminated by driving chip select  $(\overline{S})$  high at a byte boundary of the input data. In the case of the following figure, this occurs after the eighth bit of the data byte has been latched in, indicating that the instruction is being used to write a single byte. The self-timed Write cycle starts, and continues for a period t<sub>WC</sub> (as specified in AC Characteristics). At the end of the cycle, the Write In Progress (WIP) bit is reset to 0.

If, though, chip select  $(\overline{S})$  continues to be driven low, as shown in the following figure, the next byte of the input data is shifted in, so that more than a single byte, starting from the given address towards the end of the same page, can be written in a single internal Write cycle.

Each time a new data byte is shifted in, the least significant bits of the internal address counter are incremented. If the number of data bytes sent to the device exceeds the page boundary, the internal address counter rolls over to the beginning of the page, and the previous data there are overwritten with the incoming data. (The page size of these device is 64 bytes).

The instruction is not accepted, and is not executed, under the following conditions:

- If the Write Enable Latch (WEL) bit has not been set to 1 (by executing a Write Enable instruction just before)

- If a Write cycle is already in progress

- If the addressed page is in the region protected by the Block Protect (BP1 and BP0) bits.

#### Byte Write (WRITE) Sequence (1 Byte)

Note: 1. Depending on the memory size, as shown in Address Range Bits table, the most significant address bits are don't care.

Byte Write (WRITE) Sequence (Page)

Note: 1. Depending on the memory size, as shown in Address Range Bits table, the most significant address bits are don't care.

### **Data Protect**

The protection features of the device are summarized in the following table. When the Status Register Write Disable (SRWD) bit of the Status Register is 0 (its initial delivery state), it is possible to write to the Status Register provided that the Write Enable Latch (WEL) bit has previously been set by a Write Enable (WREN) instruction, regardless weather write protect  $(\overline{W})$  is driven high or low.

When the Status Register Write Disable (SRWD) bit of the Status Register is set to 1, two cases need to be considered, depending on the state of write protect ( $\overline{W}$ ):

- If write protect (W) is driven high, it is possible to write to the Status Register provided that the Write Enable Latch (WEL) bit has previously been set by a Write Enable (WREN) instruction.

- If write protect (W) is driven low, it is not possible to write to the Status Register even if the Write Enable Latch (WEL) bit has previously been set by a Write Enable (WREN) instruction. (Attempts to write to the Status Register are rejected, and are not accepted for execution). As a consequence, all the data bytes in the memory area that are software protected (SPM) by the Block Protect (BP1, BP0) bits of the Status Register, are also hardware protected against data modification.

Regardless of the order of the two events, the Hardware Protected Mode (HPM) can be entered:

- By setting the Status Register Write Disable (SRWD) bit after driving write protect ( $\overline{W}$ ) low.

- By driving write protect ( $\overline{W}$ ) low after setting the Status Register Write Disable (SRWD) bit.

The only way to exit the Hardware Protected Mode (HPM) once entered is to pull write protect ( $\overline{W}$ ) high.

If write protect ( $\overline{W}$ ) is permanently tied high, the Hardware Protected Mode (HPM) can never be activated, and only the Software Protected Mode (SPM), using the Block Protect (BP1, BP0) bits of the Status Register, can be used.

#### Write Protected Block Size

| Status | register bits |                  | Array add     | Array addresses protected |  |  |

|--------|---------------|------------------|---------------|---------------------------|--|--|

| BP1    | BP0           | Protected blocks | HN58X25256I   | HN58X25128I               |  |  |

| 0      | 0             | None             | None          | None                      |  |  |

| 0      | 1             | Upper quarter    | 6000h – 7FFFh | 3000h – 3FFFh             |  |  |

| 1      | 0             | Upper half       | 4000h – 7FFFh | 2000h – 3FFFh             |  |  |

| 1      | 1             | Whole memory     | 0000h – 7FFFh | 0000h – 3FFFh             |  |  |

#### **Protection Modes**

|                 |          |      | Write protection of the                                                                                                                       | Memo                         | ory protect                           |

|-----------------|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------------------------|

| <b>₩</b> signal | SRWD bit | Mode | status register                                                                                                                               | Protected area* <sup>1</sup> | Unprotected area* <sup>1</sup>        |

| 1               | 0        |      | Status register is writable<br>(if the WREN) instruction<br>has set the WEL bit).<br>The values in the BP1<br>and BP0 bits can be<br>changed. | Write protected              | Ready to accept Write<br>instructions |

| 0               | 0        |      |                                                                                                                                               |                              |                                       |

| 1               | 1        |      |                                                                                                                                               |                              |                                       |

| 0               | 1        |      | Status register is<br>hardware write<br>protected. The values in<br>the BP1 and BP0 bits<br>cannot be changed.                                | Write protected              | Ready to accept Write<br>instructions |

Note: 1. As defined by the values in the Block Protected (BP1, BP0) bits of the Status Register, as shown in the former table.

Rev.3.00, Jul.06.2005, page 17 of 20

## Hold Condition

The hold  $(\overline{\text{HOLD}})$  signal is used to pause any serial communications with the device without resetting the clocking sequence.

During the hold condition, the serial data output (Q) is high impedance, and serial data input (D) and serial clock (C) are don't care.

To enter the hold condition, the device must be selected, with chip select  $(\overline{S})$  low.

Normally, the device is kept selected, for the whole duration of the hold condition. Deselecting the device while it is in the hold condition, has the effect of resetting the state of the device, and this mechanism can be used if it is required to reset any processes that had been in progress.

The hold condition starts when the hold ( $\overline{HOLD}$ ) signal is driven low at the same time as serial clock (C) already being low (as shown in the following figure).

The hold condition ends when the hold ( $\overline{\text{HOLD}}$ ) signal is driven high at the same time as serial clock (C) already being low.

The following figure also shows what happens if the rising and falling edges are not timed to coincide with serial clock (C) being low.

#### **Hold Condition Activation**

### Notes

#### Data Protection at V<sub>cc</sub> On/Off

When  $V_{CC}$  is turned on or off, noise on  $\overline{S}$  inputs generated by external circuits (CPU, etc) may act as a trigger and turn the EEPROM to unintentional program mode. To prevent this unintentional programming, this EEPROM have a power on reset function. Be careful of the notices described below in order for the power on reset function to operate correctly.

- $\overline{S}$  should be fixed to  $V_{CC}$  during  $V_{CC}$  on/off. Low to high or high to low transition during  $V_{CC}$  on/off may cause the trigger for the unintentional programming.

- V<sub>CC</sub> should be turned on/off after the EEPROM is placed in a standby state.

- $V_{CC}$  should be turned on from the ground level ( $V_{SS}$ ) in order for the EEPROM not to enter the unintentional programming mode.

- $V_{CC}$  turn on speed should be slower than 10  $\mu$ s/V.

- When WRSR or WRITE instruction is executed before  $V_{CC}$  turns off,  $V_{CC}$  should be turned off after waiting write cycle time (t<sub>w</sub>).

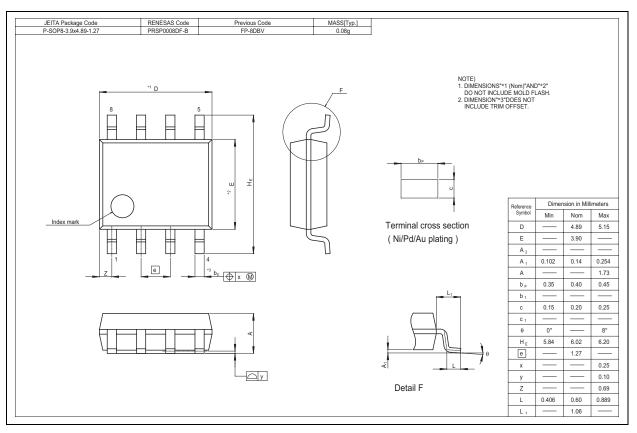

# **Package Dimensions**

HN58X25128FPIE/HN58X25256FPIE (PRSP0008DF-B / Previous Code: FP-8DBV)

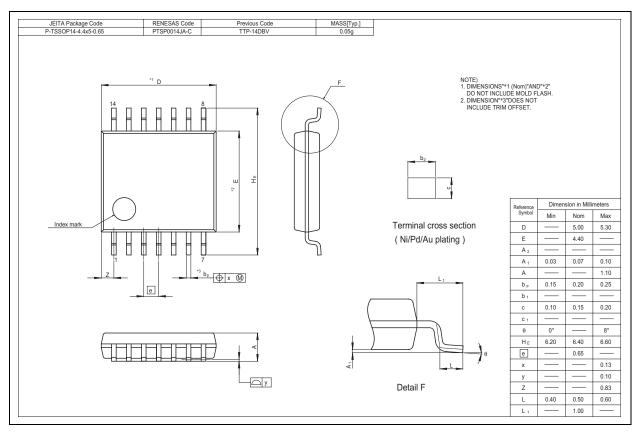

## HN58X25128TIE/HN58X25256TIE (PTSP0014JA-C / Previous Code: TTP-14DBV)

# **Revision History**

| Rev. | Date          |       | Contents of Modification                                                           |

|------|---------------|-------|------------------------------------------------------------------------------------|

|      |               | Page  | Description                                                                        |

| 0.01 | Nov. 15, 2002 |       | Initial issue                                                                      |

| 1.00 | Jun. 20, 2003 | _     | Change format issued by Renesas Technology Corp.                                   |

|      |               | 6     | DC Characteristics                                                                 |

|      |               |       | I <sub>CC1</sub> max (3.6 V): 5 mA to 2.5 mA                                       |

|      |               |       | I <sub>CC1</sub> max (5.5 V): 5 mA to 4 mA                                         |

|      |               |       | I <sub>CC2</sub> max (3.6 V): 5 mA to 2.5 mA                                       |

|      |               |       | I <sub>CC2</sub> max (5.5 V): 5 mA to 4 mA                                         |

|      |               |       | Functional Description                                                             |

|      |               |       | Change of Read from Memory Array (READ)                                            |

|      |               |       | Sequence                                                                           |

|      |               |       | Data Protect: Change of description                                                |

| 2.00 | Aug.24.2004   | 2     | Ordering Information                                                               |

|      |               |       | Deletion of HN58X25128FPI, HN58X25256FPI, HN58X25128TI,                            |

|      |               |       |                                                                                    |

|      |               |       | Addition of HN58X25128FPIE, HN58X25256FPIE, HN58X25128TIE,<br>HN58X25256TIE        |

|      |               | 25-26 | Package Dimensions: Change of Dimensions                                           |

|      |               | 20-20 | FP-8DB to FP-8DBV                                                                  |

|      |               |       | TTP-14D to TTP-14DBV                                                               |

| 2.01 | Mar.31.2005   | 1     | Description and Features                                                           |

|      |               |       | Change Serial Peripheral Interface for Serial Peripheral Interface compatible      |

|      |               | 2     | Ordering Information                                                               |

|      |               |       | Addition of Renesas package codes                                                  |

|      |               | 19-20 | Package Dimensions                                                                 |

|      |               |       | Addition of Renesas package codes                                                  |

|      |               |       | Changed to Renesas formats                                                         |

| 3.00 | Jul.06.2005   | 1     | Features                                                                           |

|      |               |       | Change of Endurance : 10 <sup>5</sup> Cycles to 10 <sup>6</sup> Erase/Write Cycles |

|      |               | 5-6   | AC Characteristics                                                                 |

|      |               |       | Addition of Erase / Write Endurance                                                |

|      |               |       | Addition of Notes 3                                                                |

# RenesasTechnology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

Keep safety first in your circuit designs! 1. Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- Notes regarding these materials

1. These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party.

2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein. The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors. Please also pay attention to information published by Renesas Technology Corp. by various means, including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.com).

4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting product data, diagrams, charts, programs, and algorithms, please b

- product contained nerein for any specific purposes, such as apparatus or systems for transportation, vendation, research, acrospace, re

#### **RENESAS SALES OFFICES**

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

Renesas Technology America, Inc. 450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K. Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology Hong Kong Ltd. 7th Floor, North Tower, World Finance Centre, Harbour City, 1 Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2730-6071

#### Renesas Technology Taiwan Co., Ltd.

10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999

#### Renesas Technology (Shanghai) Co., Ltd.

Unit2607 Ruijing Building, No.205 Maoming Road (S), Shanghai 200020, China Tel: <86> (21) 6472-1001, Fax: <86> (21) 6415-2952

#### Renesas Technology Singapore Pte. Ltd.

1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> 2-796-3115, Fax: <82> 2-796-2145

#### Renesas Technology Malaysia Sdn. Bhd.

Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jalan Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603> 7955-9390, Fax: <603> 7955-9510

http://www.renesas.com