# **SMP Controller For High Performance Process Power Supplies**

#### **FEATURES**

- Runs on 3.3- or 5-V Supplies

- · Adjustable, High Precision Output Voltage

- High Frequency Operation (>1 MHz)

- High Efficiency Synchronous Switching

- · Full Set of Protection Circuitry

- 2000-V ESD Rating (Si9140CQ/DQ)

#### **DESCRIPTION**

Siliconix' Si9140 Buck converter IC is a high-performance, surface-mount switchmode controller made to power the new generation of low-voltage, high-performance microprocessors. The Si9140 has an input voltage range of 3 to 6.5 V to simplify power supply designs in desktop PCs. Its high-frequency switching capability and wide bandwidth feedback loop provide tight, absolute static and transient load regulation. Circuits using the Si9140 can be implemented with low-profile, inexpensive inductors, and will dramatically minimize power supply output and processor decoupling capacitance. The Si9140 is designed to meet the stringent regulation requirements of new and future high-frequency microprocessors, while improving the overall efficiency in new "green" systems.

Today's state-of-the-art microprocessors run at frequencies over 100 MHz. Processor clock speeds are going up and so are current requirements, but operating voltages are going down. These simultaneous changes have made dedicated, high-frequency, point-of-use buck converters an essential part of any system design. These point-of-use converters must operate at higher frequencies and provide wider feedback bandwidths than existing converters, which typically operate at less than 250 kHz and have feedback bandwidths of less than 50 kHz. The Si9140's 100-kHz feedback loop bandwidth ensures a minimum improvement of one-half the required output/decoupling capacitance, resulting in a tremendous reduction in board size and cost of implementation.

With the microprocessing power of any PC representing an investment of hundreds of dollars, designers need to ensure that the reliable operation of the processor will not be affected by the power supply. The Si9140 provides this assurance. A demo board, the Si9140DB, is available.

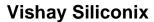

## APPLICATION CIRCUIT

## **ABSOLUTE MAXIMUM RATINGS**

| Voltages Referenced to GND.                 | Thermal Impedance ( $\Theta_{JA}$ )                              |

|---------------------------------------------|------------------------------------------------------------------|

| V <sub>DD</sub> , V <sub>S</sub>            | 16-Pin SOIC (Y Suffix)                                           |

| P <sub>GND</sub>                            | 16-Pin TSSOP (Q Suffix)                                          |

| V <sub>DD</sub> to V <sub>S</sub> 0.3 V     | Operating Temperature                                            |

|                                             | C Suffix                                                         |

| Linear Inputs                               | D Suffix40° to 85°C                                              |

| Logic Inputs                                | Notes                                                            |

| Peak Output Drive Current                   | a. Device mounted with all leads soldered or welded to PC board. |

| Storage Temperature65 to 150°C              | b. Derate 7.2 mW/°C above 25°C.                                  |

| Operating Junction Temperature              | c. Derate 7.4 mW/°C above 25°C.                                  |

| Power Dissipation (Package) <sup>a</sup>    |                                                                  |

| 16-Pin SOIC (Y Suffix) <sup>b</sup>         |                                                                  |

| 16-Pin TSSOP (Q Suffix) <sup>c</sup> 925 mW |                                                                  |

## **RECOMMENDED OPERATING RANGE**

| Voltages Referenced to GND. |                           |

|-----------------------------|---------------------------|

| V <sub>DD</sub>             | C <sub>OSC</sub>          |

| V <sub>S</sub>              | Linear Inputs             |

| f <sub>OSC</sub>            | Digital Inputs            |

| $R_{OSC}$                   | $V_{REF}$ Load Resistance |

| SPECIFICATIONS                                         |                   |                                                                                                                           |                           |                                                |      |                  |          |  |

|--------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------------------------------------|------|------------------|----------|--|

|                                                        |                   | Test Conditions Unless Otherwise Specified <sup>a</sup> $3 \ V \le V_{DD} \le 6.5 \ V, \ V_{DD} = V_{S}$ $GND = P_{GND}$  |                           | Limits C Suffix 0 to 70°C D Suffix -40 to 85°C |      |                  |          |  |

| Parameter                                              | Symbol            |                                                                                                                           |                           | Min <sup>b</sup>                               | Тур  | Max <sup>b</sup> | Unit     |  |

| Reference                                              |                   |                                                                                                                           |                           |                                                |      | •                | -        |  |

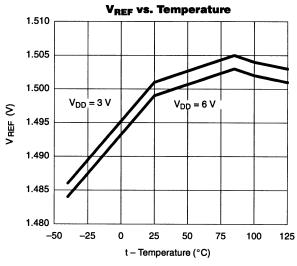

| Output Voltage                                         | V                 | I <sub>REF</sub> = -10 μA                                                                                                 | I <sub>REF</sub> = -10 μA |                                                |      | 1.545            | V        |  |

| Output voltage                                         | V <sub>REF</sub>  |                                                                                                                           | $T_A = 25$ °C             | 1.477                                          | 1.50 | 1.523            | V        |  |

| Oscillator                                             | -                 | •                                                                                                                         | •                         |                                                |      | <u>-</u>         | <u>-</u> |  |

| Maximum Frequency <sup>c</sup>                         | f <sub>MAX</sub>  | $V_{DD}$ = 5 V, $C_{OSC}$ = 47 pF, $R_{OSC}$                                                                              | = $5.0 \text{ k}\Omega$   | 2.0                                            |      |                  |          |  |

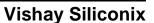

| Accuracy                                               | fosc              | $V_{DD} = 5 \text{ V}$<br>$C_{OSC} = 100 \text{ pF}, R_{OSC} = 7.50 \text{ k}\Omega, T_A = 25^{\circ}\text{C}$            |                           | 0.85                                           | 1.0  | 1.15             | MHz      |  |

| R <sub>OSC</sub> Voltage                               | V <sub>ROSC</sub> |                                                                                                                           |                           |                                                | 1.0  |                  | V        |  |

| Voltage Stability <sup>c</sup>                         | ∆f/f              | $4 \text{ V} \le \text{V}_{DD} \le 6 \text{ V}, \text{ Ref to 5 V}, \text{T}_{A} = 25^{\circ}\text{C}$ Referenced to 25°C |                           | -8                                             |      | 8                | %        |  |

| Temperature Stability <sup>c</sup>                     | Δ1/1              |                                                                                                                           |                           |                                                | ±5   |                  | %        |  |

| Error Amplifier (C <sub>OSC</sub> = GND, OSC Disabled) |                   |                                                                                                                           |                           |                                                |      |                  |          |  |

| Input Bias Current                                     | I <sub>FB</sub>   | $V_{NI} = V_{REF}, V_{FB} = 1.0 $                                                                                         | /                         | -1.0                                           |      | 1.0              | μA       |  |

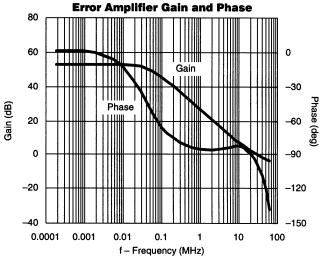

| Open Loop Voltage Gain                                 | A <sub>VOL</sub>  |                                                                                                                           |                           | 47                                             | 55   |                  | dB       |  |

| Offset Voltage                                         | V <sub>OS</sub>   | $V_{NI} = V_{REF}$                                                                                                        |                           | -15                                            | 0    | 15               | mV       |  |

| Unity Gain Bandwidth <sup>c</sup>                      | BW                |                                                                                                                           |                           |                                                | 10   |                  | MHz      |  |

| Output Current I <sub>F</sub>                          | 1                 | Source (V <sub>FB</sub> = 1 V, NI = V                                                                                     |                           |                                                | -2.0 | -1.0             | mA       |  |

| Output Guitetit                                        | I <sub>EA</sub>   | Sink ( $V_{FB} = 2 \text{ V}, \text{ NI} = V_{RE}$                                                                        | :F)                       | 0.4                                            | 0.8  |                  | IIIA     |  |

| Power Supply Rejection <sup>c</sup>                    | P <sub>SRR</sub>  | 3 V < V <sub>DD</sub> < 6.5 V                                                                                             |                           |                                                | 60   |                  | dB       |  |

<sup>\*</sup> Exposure to Absolute Maximum rating conditions for extended periods may affect device reliability. Stresses above Absolute Maximum rating may cause permanent damage. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum rating should be applied at any one time.

| SPECIFICATIONS                                    |                        |                                                                                                                         |                                                |      |                     |      |  |

|---------------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------|---------------------|------|--|

|                                                   |                        | Test Conditions<br>Unless Otherwise Specified <sup>a</sup>                                                              | Limits C Suffix 0 to 70°C D Suffix -40 to 85°C |      |                     |      |  |

| Parameter                                         | Symbol                 | $3 \text{ V} \le \text{V}_{DD} \le 6.5 \text{ V}, \text{V}_{DD} = \text{V}_{S}$<br>$\text{GND} = \text{P}_{\text{GND}}$ | Min <sup>b</sup>                               | Тур  | Max <sup>b</sup>    | Unit |  |

| UVLO <sub>SET</sub> Voltage Monitor               |                        |                                                                                                                         |                                                |      | ·                   |      |  |

| Llader Veltore Leekeut                            | $V_{UVLOHL}$           | UVLO <sub>SET</sub> High to Low                                                                                         | 0.85                                           | 1.0  | 1.15                | V    |  |

| Under Voltage Lockout                             | V <sub>UVLOLH</sub>    | UVLO <sub>SET</sub> Low to High                                                                                         |                                                | 1.2  |                     | V    |  |

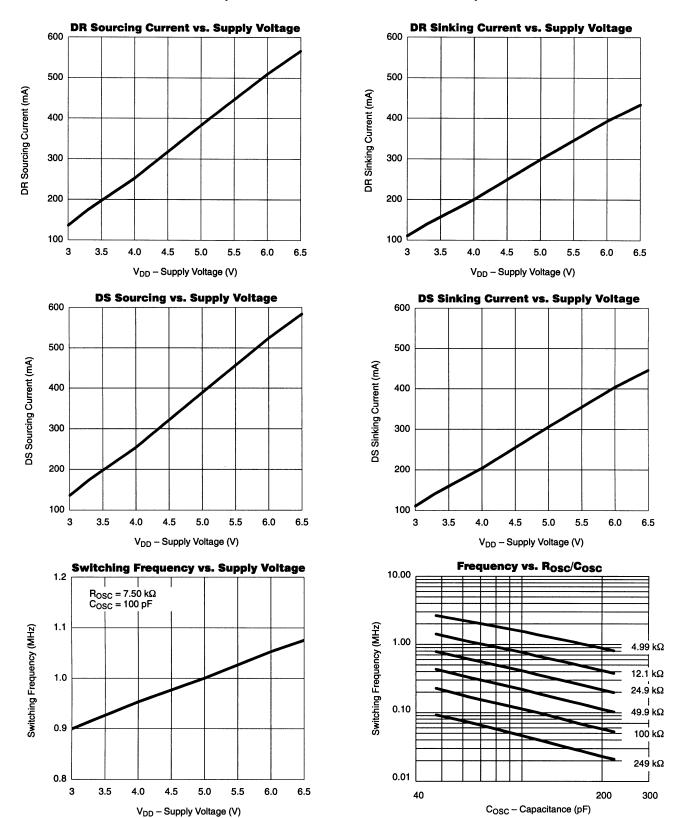

| Hysteresis                                        | V <sub>HYS</sub>       | V <sub>UVLOLH</sub> - V <sub>UVLOHL</sub>                                                                               |                                                | 175  |                     | mV   |  |

| UVLO Input Current                                | I <sub>UVLO(SET)</sub> | $V_{UVLO} = 0$ to $V_{DD}$                                                                                              | -100                                           |      | 100                 | nA   |  |

| Output Drive (D <sub>R</sub> AND D <sub>S</sub> ) |                        |                                                                                                                         |                                                |      |                     |      |  |

| Output High Voltage                               | V <sub>OH</sub>        | $V_{S} = V_{DD} = 5 \text{ V}, I_{OUT} = -10 \text{ mA}$                                                                | 4.7                                            | 4.8  |                     | V    |  |

| Output Low Voltage                                | V <sub>OL</sub>        | V <sub>S</sub> = V <sub>DD</sub> = 5 V, I <sub>OUT</sub> = 10 mA                                                        |                                                | 0.2  | 0.3                 | V    |  |

| Peak Output Current                               | I <sub>SOURCE</sub>    | V <sub>S</sub> = V <sub>DD</sub> = 5 V, V <sub>OUT</sub> = 0 V                                                          |                                                | -380 | -260                | mA   |  |

| Peak Output Current                               | I <sub>SINK</sub>      | $V_{S} = V_{DD} = 5 \text{ V}, V_{OUT} = 5 \text{ V}$                                                                   | 200                                            | 300  |                     |      |  |

| Break-Before-Make                                 | t <sub>BBM</sub>       | V <sub>DD</sub> = 6.5 V                                                                                                 |                                                | 40   |                     | nS   |  |

| Logic                                             |                        |                                                                                                                         | <del>-</del>                                   |      | -                   |      |  |

| ENABLE Turn-On Delay                              | t <sub>dEN</sub>       | ENABLE Delay to Output, EN <sub>LH</sub> , V <sub>DD</sub> = 5 V                                                        |                                                | 1.5  |                     | μs   |  |

| ENABLE Logic Low                                  | V <sub>ENL</sub>       |                                                                                                                         |                                                |      | 0.2 V <sub>DD</sub> | V    |  |

| ENABLE Logic High                                 | V <sub>ENH</sub>       |                                                                                                                         | 0.8 V <sub>DD</sub>                            |      |                     | V    |  |

| ENABLE Input Current                              | I <sub>EN</sub>        | ENABLE = 0 to V <sub>DD</sub>                                                                                           | -1.0                                           |      | 1.0                 | μA   |  |

| V <sub>GOOD</sub> Comparator (Voltag              | e-Good Con             | nparator)                                                                                                               |                                                |      |                     |      |  |

| Input Offset Voltage                              | Vos                    | V. Common Mode Veltage, V. V. E.V.                                                                                      | -45                                            | 0    | 45                  | m\/  |  |

| Input Hysteresis                                  | V <sub>INHYS</sub>     | V <sub>IN</sub> Common Mode Voltage = V <sub>REF</sub> V <sub>DD</sub> = 5 V                                            |                                                | 10   |                     | mV   |  |

| Input Bias Current                                | I <sub>BMON</sub>      | $V_{IN} = V_{REF}, V_{DD} = 5 V$                                                                                        | -1                                             | 0    | 1                   | μΑ   |  |

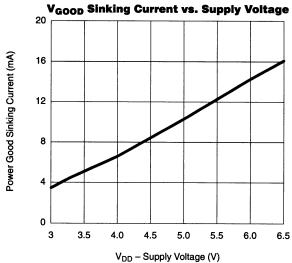

| Output Sink I                                     | I <sub>SINK</sub>      | V <sub>OUT</sub> = 5 V, V <sub>DD</sub> = 5 V                                                                           | 6                                              | 9    |                     | mA   |  |

| Output Low Voltage                                | V <sub>OL</sub>        | $I_{OUT} = 2 \text{ mA}, V_{DD} = 5 \text{ V}$                                                                          |                                                | 350  | 500                 | mV   |  |

| Supply                                            | -                      |                                                                                                                         | <del> </del>                                   |      | -                   |      |  |

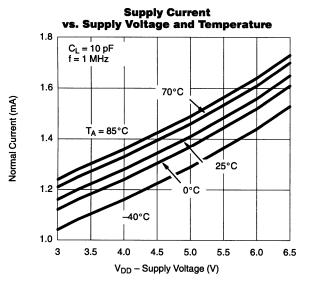

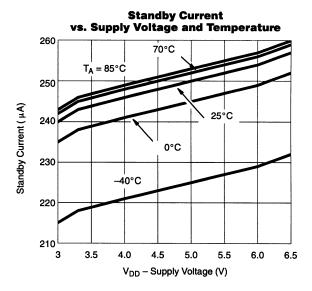

| Supply Current-Normal Mode                        | 1                      | $f_{OSC} = 1 \text{ MHz}, R_{OSC} = 7.50 \text{ k}\Omega$                                                               |                                                | 1.6  | 2.3                 | mA   |  |

| Supply Current-Standby Mode                       | I <sub>DD</sub>        | ENABLE < 0.4 V                                                                                                          |                                                | 250  | 330                 | μA   |  |

#### Notes

a. 100 pF includes  $C_{\mbox{\scriptsize STRAY}}$  on  $C_{\mbox{\scriptsize OSC}}$ .

b. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum, is used in this data sheet.

c. Guaranteed by design, not subject to production testing.

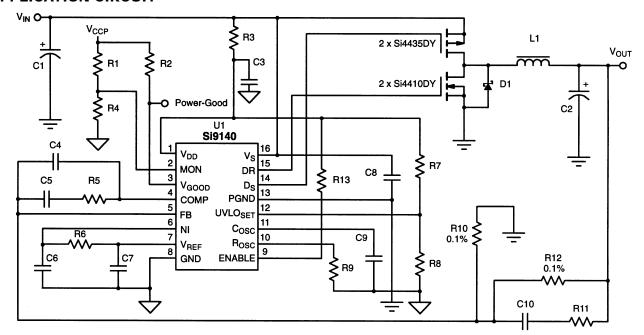

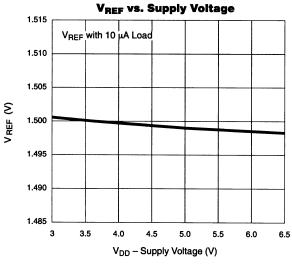

## TYPICAL CHARACTERISTICS (25°C UNLESS OTHERWISE NOTED)

## TYPICAL CHARACTERISTICS (25°C UNLESS OTHERWISE NOTED)

## TYPICAL CHARACTERISTICS (25°C UNLESS OTHERWISE NOTED)

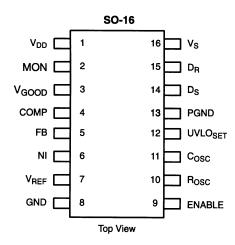

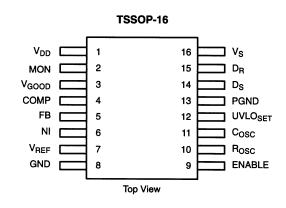

#### **PIN CONFIGURATIONS**

| ORDERING INFORMATION          |          |  |  |

|-------------------------------|----------|--|--|

| Temperature Range Part Number |          |  |  |

| 0° to 70°C                    | Si9140CY |  |  |

| -40° to 85°C                  | Si9140DY |  |  |

| ORDERING INFORMATION |             |  |  |

|----------------------|-------------|--|--|

| Temperature Range    | Part Number |  |  |

| 0° to 70°C           | Si9140CQ    |  |  |

| -40° to 85°C         | Si9140DQ    |  |  |

## **PIN DESCRIPTION**

## Pin 1: V<sub>DD</sub>

The positive power supply for all functional blocks except output driver. A bypass capacitor of 0.1  $\mu F$  (minimum) is recommended.

#### Pin 2: MON

Non-inverting input of a comparator. Inverting input is tied internally to reference voltage. This comparator is typically used to monitor the output voltage and to flag the processor when the output voltage falls out of regulation.

## Pin 3: V<sub>GOOD</sub>

This is an open drain output. It will be held at ground when the voltage at MON (Pin 2) is less than the internal reference. An external pull-up resistor will pull this pin high if the MON pin (Pin 2) is higher than the  $V_{REF}$  (Refer to Pin 2 description.)

## Pin 4: COMP

This pin is the output of the error amplifier. A compensation network is connected from this pin to the FB pin to stabilize the system. This pin drives one input of the internal pulse width modulation comparator.

## Pin 5: FB

The inverting input of the error amplifier. An external resistor divider is connected to this pin to set the regulated output voltage. The compensation network is also connected to this pin.

#### Pin 6: NI

The non-inverting input of the error amplifier. In normal operation it is externally connected to  $V_{\mbox{\scriptsize REF}}$  or an external reference.

## Pin 7: V<sub>RFF</sub>

This pin supplies a 1.5-V reference.

#### Pin 8: GND (Ground)

#### Pin 9: ENABLE

A logic high on this pin allows normal operation. A logic low places the chip in the standby mode. In standby mode normal operation is disabled, supply current is reduced, the oscillator stops and  $D_S$  goes high while  $D_R$  goes low.

# VISHAY

## Pin 10: Rosc

A resistor connected from this pin to ground sets the oscillator's capacitor  $C_{OSC}$ , charge and discharge current. See the oscillator section of the description of operation.

## Pin 11: Cosc

An external capacitor is connected to this pin to set the oscillator frequency.

$$f_{OSC} \cong \frac{0.75}{R_{OSC} \times C_{OSC}} \qquad \text{ (at V}_{DD} = 5.0 \text{ V)}$$

## Pin 12: UVLO<sub>SET</sub>

This pin will place the chip in the standby mode if the  $UVLO_{SET}$  voltage drops below 1.2 V. Once the  $UVLO_{SET}$  voltage exceeds 1.2 V, the chip operates normally. There is a built-in hysteresis of 165 mV.

## Pin 13: P<sub>GND</sub>

The negative return for the V<sub>S</sub> supply.

## Pin 14: D<sub>S</sub>

This CMOS push-pull output pin drives the external p-channel MOSFET. This pin will be high in the standby mode. A break-before-make function between  $D_S$  and  $D_R$  is built-in.

## Pin 15: D<sub>R</sub>

This CMOS push-pull output pin drives the external n-channel MOSFET. This pin will be low in the standby mode. A break-before-make function between the  $D_{\rm S}$  and  $D_{\rm R}$  is built-in.

## Pin 16: V<sub>S</sub>

The positive terminal of the power supply which powers the CMOS output drivers. A bypass capacitor is required.

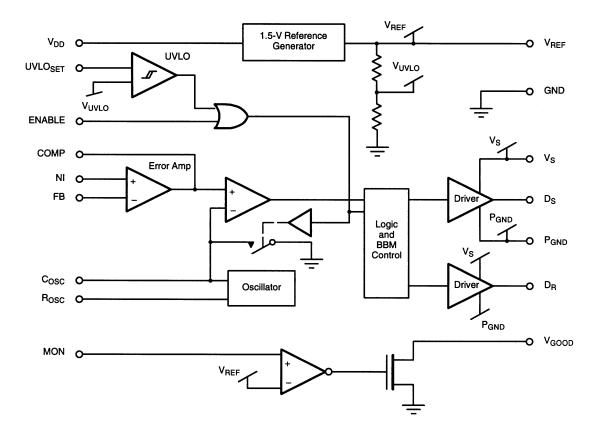

## **FUNCTIONAL BLOCK DIAGRAM**

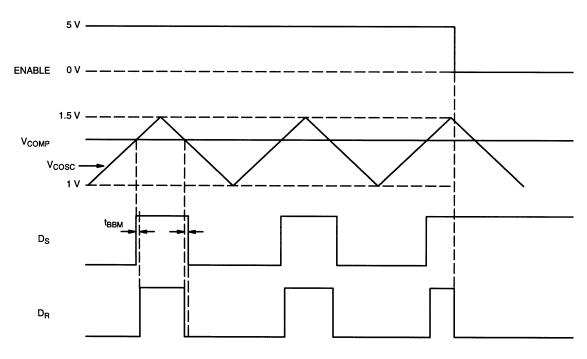

## **TIMING WAVEFORMS**

## **DESCRIPTION OF OPERATION**

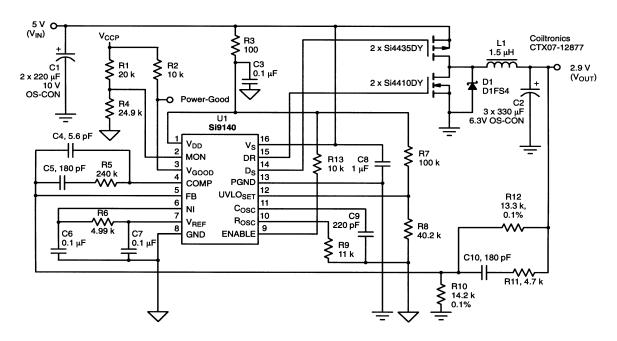

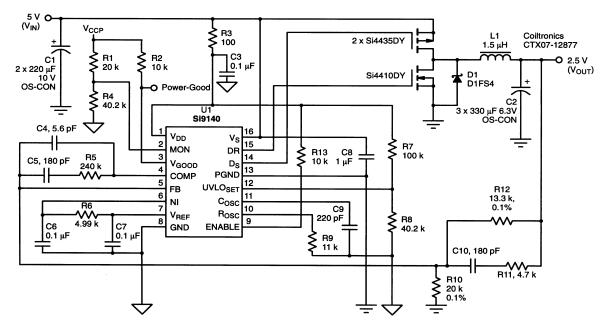

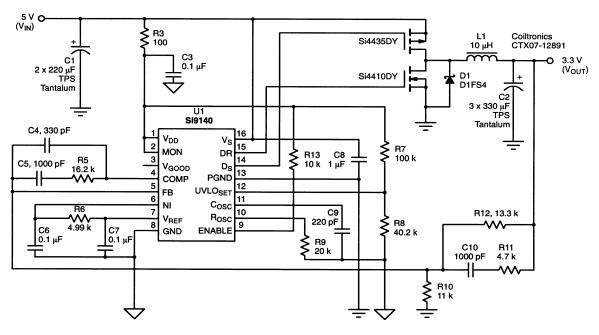

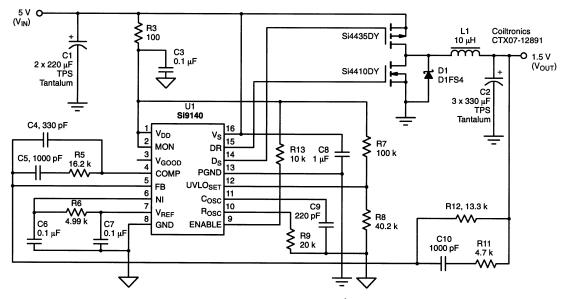

Schematics of the Si9140 dc-to-dc conversion solutions for high-performance PC microprocessors are shown in Figure 1 and 2 respectively. These solutions are geared to meet the extremely demanding transient regulation and power requirements of these new microprocessors at minimal cost

and with a minimal parts count. The two solutions are nearly identical, except for slight variations in output voltage, load transient amplitude, and specified power. Figure 3 is a schematic diagram for a 3.3-V logic converter.

**FIGURE 1.** 2.9 V @ 10 A

**FIGURE 2.** 2.5 V @ 8.5 A

**FIGURE 3.** 3.3 V @ 5 A

FIGURE 4. 1.5-V Converter for GTL+ Bus @ 5 A

Figure 4 is a schematic diagram of a converter which produces 1.5 V for a GTL bus.

Each of these dc-to-dc converters has four major sections:

- · PWM Controller-regulates the output voltage

- Switch and Synchronous Rectification MOSFETs-delivers the power to the load

- · Inductor-filters and stores the energy

- Input/Output Capacitor-filters the ripple

The functions of each circuit are explained in detail below. Design equations are provided to optimize each application circuit.

## **PWM CONTROLLER**

There are generally two types of controllers, voltage mode or current mode. In voltage mode control, an error voltage is generated by comparing the output voltage to the reference voltage. The error voltage is then compared to an artificial ramp, and the result is the duty cycle necessary to regulate the output voltage. In current mode, an actual inductor current is used, in place of the artificial ramp, to sense the voltage across the current sense resistor.

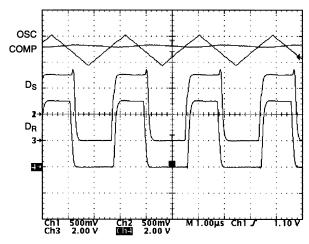

The logic and timing sequence for voltage mode control is shown in Figure 5. The Si9140 offers voltage mode control, which is better suited for applications requiring both fast transient response and high output current.

Current mode control requires a current sense resistor to monitor the inductor current. A  $10\text{-m}\Omega$  sense resistor in a 10-A design will dissipate 1 W, decreasing efficiency by 3.5%. Such a design would require a 2-W resistor to satisfy derating criteria, besides requiring additional board space. Voltage mode control is a second-order LC system and has a faster natural transient response compared to current mode control

(first-order RC system). Current mode has the advantage of providing an inherently good line regulation. But the situations where line voltage is fixed, as in the point-of-use conversion for microprocessors, this feature is wasted. Current mode control also provides automatic pulse-to-pulse current limiting. This feature requires a current sense resistor as stated above. These characteristics make voltage mode control ideal for high-end microprocessor power supplies.

FIGURE 5. Voltage Mode Logic and Timing Diagram

The error amplifier of the PWM controller plays a major role in determining the output voltage, stability, and the transient response of the power supply. In the Si9140, the non-inverting input of the error amplifier is available for use with an external precision reference for tighter tolerance regulation. With a two-pair lead-lag compensation network, it is easy to create a stable 100-kHz closed loop converter with the Si9140 error amplifier.

The Si9140 achieves the 5-µS transient response by generating a 100-kHz closed-loop bandwidth. This is possible only by switching above 400 kHz and utilizing an error amplifier with at least a 10-MHz bandwidth. The Si9140 controller has a 25-MHz unity gain bandwidth error amplifier. The switching frequency must be at least four times greater than the desired closed-loop bandwidth to prevent oscillation. To respond to the stimuli, the error amplifier bandwidth needs to be at least 10 times larger than the desired bandwidth.

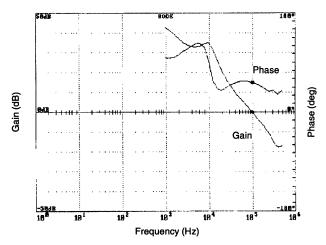

FIGURE 6. 100-kHz BW Synchronous Buck Converter

The Si9140 solution requires only three 330-µF OS-CON capacitors on the output of power supply to meet the 10-A transient requirement. Other converter solutions on the market with 20- to 50-kHz closed loop bandwidths typically require two to five times the output capacitance specified above to match the Si9140's performance.

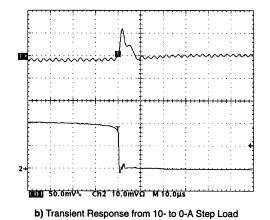

The theoretical issues and analytical steps involved in compensating a feedback network are beyond the scope of this application note. However, to ease the converter design for today's high-performance microprocessors, typical component values for the feedback network are provided in Table 1 for various combinations of output capacitance. Figure 6 shows the Bode plot (frequency domain) of the 2.9-V converter shown schematically in Figure 1.

TABLE 1. Feedback Network Component Values

| Total Output and<br>Decoupling Capacitance                                                           | C4     | <b>C</b> 5 | R5    |

|------------------------------------------------------------------------------------------------------|--------|------------|-------|

| 3 x 330 μF <sup>a</sup> Os-con<br>6 x 100 μF <sup>b</sup> Tantalum<br>25 x 1 μF <sup>b</sup> Ceramic | 5.6 pF | 180 pF     | 240 k |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                | 10 pF  | 220 pF     | 200 k |

| 3 x 330 μF <sup>a</sup>                                                                              | 10 pF  | 100 pF     | 100 k |

Notes:

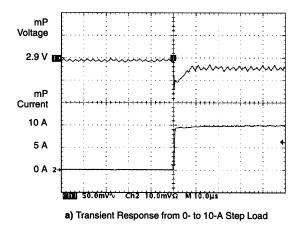

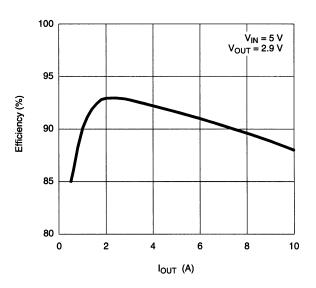

Figure 7 is the measured transient response (time domain) for the 10-A step response. The measured transient response shows the processor voltage regulating to 70 mV, well within the 0.145-V regulation.

The Si9140's switching frequency is determined by the external  $R_{\rm OSC}$  and  $C_{\rm OSC}$  values, allowing designers to set the switching frequency of their choice. For applications where space is the main constraint, the switching frequency can be set as high as 2 MHz to minimize inductor and output capacitor size. In applications where efficiency is the main concern, the switching frequency can be set low to maximize battery life. The switching frequency for high-performance processors applications circuits are set for 400 kHz. The equation for switching frequency is:

$$f_{OSC} \approx \frac{0.75}{R_{OSC} \times C_{OSC}}$$

(at  $V_{DD} = 5.0 \text{ V}$ )

The precision reference is set at  $1.5 \text{ V} \pm 1.5\%$ . The reference is capable of sourcing up to 1 mA. The combination of 1.5% reference and 3.5% transient load regulation safely complies with the  $\pm 5\%$  regulation requirement. If additional margin is desired, an external precision reference can be used in place of the internal 1.5-V reference.

# SWITCHING AND SYNCHRONOUS RECTIFICATION MOSFETS

The synchronous gate drive outputs of Si9140 PWM controller drive the high-side p-channel switch MOSFET and the low-side n-channel synchronous rectifier MOSFET. The physical difference between the non-synchronous to synchronous rectification requires an additional MOSFET across the free-wheeling diode (D1). The inductor current will reach 0 A if the peak-to-peak inductor current equals twice the output current. In synchronous rectification mode, current is allowed to flow backwards from the inductor (L1) through the synchronous MOSFET (Q3) and to the output capacitors (C2) once the current reaches 0 A. Refer to schematic on Figure 1. In non-synchronous rectification, the diode (D1) prevents the current from flowing in the reverse direction. This minor difference has a drastic affect on the performance of a power supply. By allowing the current to flow in the reverse direction, it preserves the continuous inductor current mode, maintaining the wide converter bandwidth and improving efficiency. Also, maintaining the continuous current mode during light load to full load guarantees consistent transient response throughout a wide range of load conditions.

a. Power supply output capacitance.

b. µprocessor decoupling capacitance.

The transition from stop clock and auto halt to active mode is a perfect example. The microprocessor current can vary from 0.5 A to 10 A or greater during these transitions. If the converter were to operate in discontinuous current mode during the stop clock and auto halt modes, the transfer function of the converter would be different compared to

operation in the active mode. In discontinuous current mode, the converter bandwidth can be 10 to 15 times lower than the continuous current mode (Figure 8). Therefore, the response time will also be 10 to 15 times slower, violating the microprocessor's regulator requirements. This could result in unreliable operation of the microprocessor.

FIGURE 7.

For these reasons, synchronous rectification is a must in today's microprocessors power supply design. Pulse-skipping modes are undesirable in high-performance microprocessor power supplies, especially when the minimum load current is as high as 500 mA. This pulse-skipping mode disables the synchronous rectification during light load and generates a random noise spectrum which may produce EMI problems.

Siliconix' TrenchFET<sup>TM</sup> technology has resulted in  $20\text{-m}\Omega$  n-channel (Si4410DY) and  $35\text{-m}\Omega$  p-channel (Si4435DY) MOSFETs in the SO-8 surface-mount package. These LITTLE FOOT® products totally eliminate the need for an external heatsink.

FIGURE 8. Non-Synchronous Converter BW

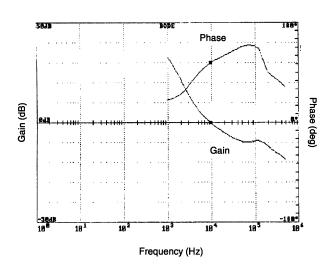

Worst case current of 10 A can be handled with two paralleled Si4435DY and two paralleled Si4410DY MOSFETs, which results in the efficiency levels shown in Figure 9.

Good electrical designs must provide an adequate margin for the specification, but they should not be grossly overdesigned to lower costs. LITTLE FOOT power MOSFETs allow designers to balance cost and performance considerations without sacrificing either. If the design requires only an 8.5-A continuous current, for example, one Si4410DY can be eliminated. Table 2 shows the number of MOSFETs required to handle the various output current levels of today's high-performance microprocessors. For other output power levels, the equations below should be used to calculate the power handling capability of the MOSFET.

FIGURE 9. Efficiency

**TABLE 2.** Converter Requirements Figure 1, 2, and 3)

| I <sub>O</sub> (A)<br>Maximum | Quantity High-side<br>P-Channel SI4435DY | Quantity Low-side<br>N-Channel SI4410DY | Quantity Input (C1-C3)<br>Capacitor OS-CON 220 μF |

|-------------------------------|------------------------------------------|-----------------------------------------|---------------------------------------------------|

| 5 A                           | 1                                        | 1                                       | 1                                                 |

| 8.5 A                         | 2                                        | 1                                       | 2                                                 |

| 10 A                          | 2                                        | 2                                       | 2                                                 |

| 14.5 A                        | 3                                        | 2                                       | 3                                                 |

$$P_{Dissipation} \text{ in switch } = \left. I_{RMS~SW}^{} \right.^{2} \times R_{SW} + \frac{Q_{SW} \times I_{IN} \times f_{OSC}}{2} + \frac{I_{PP} \times V_{O} \times \tau_{C} \times f_{OSC}}{2}$$

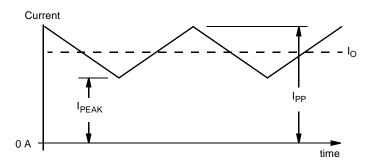

$$I_{\text{RMS SW}} = \sqrt{(I_{\text{PEAK}}^2 + I_{\text{PP}}^2 + I_{\text{PEAK}} \times I_{\text{PP}}) \times \frac{V_0}{3 \times V_{\text{IN}}}}$$

$$I_{\text{RMS RECT}} = \sqrt{\left(I_{\text{PEAK}}^2 + I_{\text{PP}}^2 + I_{\text{PEAK}} \times I_{\text{PP}}\right) \times \frac{V_{\text{IN}} - V_{\text{O}}}{3 \times V_{\text{IN}}}}$$

$$I_{PP} = I_{PEAK} + \Delta I$$

$$\Delta I = \frac{{V_0}^2}{L \times f_{OSC} \times V_{IN}}$$

$$I_{PEAK} \, = \, \frac{P_{IN} - (0.5 \times V_O \times \Delta I)}{V_O}$$

$$P_{IN} = \frac{V_O \times I_O}{n}$$

$I_{RMSSW}$  = Switch rms current  $R_{SW}$  = Switch on resistance

$I_{RMSRECT} = Synchronous rectifier rms current \\ R_{RECT} = Synchronous rectifier on resistance \\ Q_{SW} = Total gate charge of switch$

Q<sub>RECT</sub> = Total gate charge of synchronous rectifier

$V_{IN}$  = Input voltage  $V_{O}$  = Output voltage  $I_{O}$  = Output current  $I_{OSC}$  = Switching frequency

$\eta$  = efficiency  $\tau_C$  = Crossover time

## **INDUCTOR**

The size and value of the inductor are critical in meeting overall circuit dimensional requirements and in assuring proper transient voltage regulation. The size of the core is determined by the output power, the material of the core, and the operating frequency. To handle higher output power, the core must be larger. Luckily, a higher switching frequency will lower the inductance value, decreasing the core size. However, a higher switching frequency can also mean greater core loss.

In applications where the dc flux density is high and the ac flux density swing is only 100 to 200 gauss, the core loss will be negligible compared to the wire loss. Kool Mu is the best material to use at 500 kHz to deliver 30 W in the minimum volume. Ferrite has a lower core cost and loss at this

frequency, but the core size is fairly large. If the power supply is designed on the motherboard and space is not a critical issue, ferrite is a better choice.

The higher switching frequency reduces the core size by decreasing the amount of energy that must be stored between switching periods. It also accelerates the transient response to the load by decreasing the inductance value. The inductance is calculated with following equation:

$$L = \frac{{V_0}^2}{V_{IN} \times \Delta I \times f_{OSC}}$$

$\Delta I$  = desired output current ripple. Typically  $\Delta I$  = 25% of maximum output current.