# **M24LR64-R**

# 64 Kbit EEPROM with password protection & dual interface: 400kHz I<sup>2</sup>C serial bus & ISO 18000-3 mode 1 RF protocol at 13.56MHz

Preliminary data

## **Features**

#### I<sup>2</sup>C interface

- Two-wire I<sup>2</sup>C serial interface supports 400 kHz protocol

- Single supply voltage:

- 1.8 V to 5.5 V

- Byte and Page Write (up to 4 bytes)

- Random and Sequential Read modes

- Self-timed programming cycle

- Automatic address incrementing

- Enhanced ESD/latch-up protection

#### **Contactless interface**

- ISO 15693 and ISO 18000-3 mode 1 compliant

- 13.56 MHz ±7k Hz carrier frequency

- To tag: 10% or 100% ASK modulation using 1/4 (26 Kbit/s) or 1/256 (1.6 Kbit/s) pulse position coding

- From tag: load modulation using Manchester coding with 423 kHz and 484 kHz subcarriers in low (6.6 Kbit/s) or high (26 Kbit/s) data rate mode. Supports the 53 Kbit/s data rate with Fast commands

- Internal tuning capacitance: 28.5 pF

- 64-bit unique identifier (UID)

- Read Block & Write (32-bit Blocks)

### Memory

- 64 Kbit EEPROM organized into:

- 8192 bytes in I<sup>2</sup>C mode

- 2048 blocks of 32 bits in RF mode

- Write time

- I<sup>2</sup>C: 5 ms (Max.)

- RF: 5.75 ms including the internal Verify time

- More than 1 Million erase/write cycles in I<sup>2</sup>C mode

- More than 100 000 erase/write cycles in RF

- Multiple password protection in RF mode

- Single password protection in I<sup>2</sup>C mode

- More than 40-year data retention

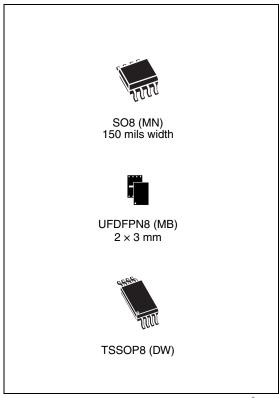

- Package

- ECOPACK2<sup>®</sup> (RoHS compliant and Halogen-free)

February 2010 Doc ID 15170 Rev 8 1/126

Contents M24LR64-R

# **Contents**

| 1     | Desc               | cription .           |                                                       | 12         |

|-------|--------------------|----------------------|-------------------------------------------------------|------------|

| 2     | Sign               | al descri            | ption                                                 | 14         |

|       | 2.1                | Serial C             | lock (SCL)                                            | 14         |

|       | 2.2                | Serial D             | ata (SDA)                                             | 14         |

|       | 2.3                | Chip En              | able (E0, E1)                                         | 14         |

|       | 2.4                | Antenna              | coil (AC0, AC1)                                       | 14         |

|       | 2.5                | V <sub>SS</sub> grou | und                                                   | 14         |

|       | 2.6                | Supply v             | voltage (V <sub>CC</sub> )                            | 15         |

|       |                    | 2.6.1                | Operating supply voltage V <sub>CC</sub>              | 15         |

|       |                    | 2.6.2                | Power-up conditions                                   |            |

|       |                    | 2.6.3                | Device reset                                          | 15         |

|       |                    | 2.6.4                | Power-down conditions                                 | 15         |

| 3     | User               | memory               | organization                                          | 17         |

| 4     | Syst               | em mem               | ory area                                              | 22         |

|       | 4.1                | M24LR6               | 64-R RF block security                                | 22         |

|       | 4.2                | Example              | e of the M24LR64-R security protection                | 24         |

|       | 4.3                | I2C_Wri              | te_Lock bit area                                      | 25         |

|       | 4.4                | System               | parameters                                            | 25         |

|       | 4.5                | M24LR6               | 64-R I <sup>2</sup> C password security               | 26         |

|       |                    | 4.5.1                | I <sup>2</sup> C Present Password command description | 26         |

|       |                    | 4.5.2                | I <sup>2</sup> C Write Password command description   | 27         |

| 5     | I <sup>2</sup> C c | levice op            | eration                                               | 29         |

|       | 5.1                | Start co             | ndition                                               | 29         |

|       | 5.2                | Stop cor             | ndition                                               | 29         |

|       | 5.3                | Acknowl              | edge bit (ACK)                                        | 29         |

|       | 5.4                | Data Inp             | out                                                   | 29         |

|       | 5.5                | Memory               | addressing                                            | 30         |

|       | 5.6                | Write op             | erations                                              | 31         |

|       | 5.7                | Byte Wr              | ite                                                   | 31         |

| 2/126 |                    |                      | Doc ID 15170 Rev 8                                    | <b>57/</b> |

| M24LR64-R | Contents |

|-----------|----------|

|           |          |

|            | 5.8    | Page Write                                 | 31  |

|------------|--------|--------------------------------------------|-----|

|            | 5.9    | Minimizing system delays by polling on ACK | 33  |

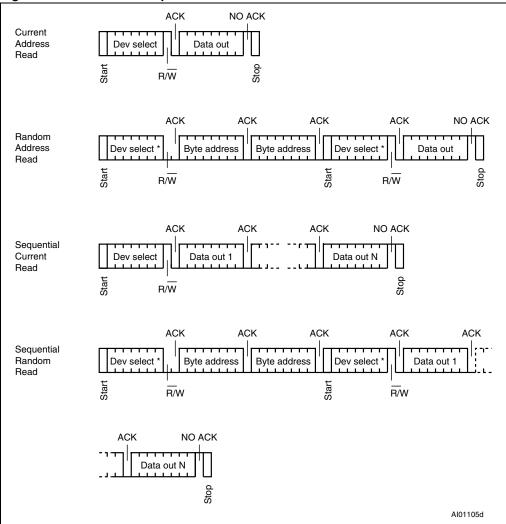

|            | 5.10   | Read operations                            | 35  |

|            | 5.11   | Random Address Read                        | 35  |

|            | 5.12   | Current Address Read                       | 35  |

|            | 5.13   | Sequential Read                            | 35  |

|            | 5.14   | Acknowledge in Read mode                   | 35  |

| 6          | Initia | I delivery state                           | 36  |

| 7          | RF d   | evice operation                            | 36  |

|            | 7.1    | Commands                                   | 37  |

|            | 7.2    | Initial dialog for vicinity cards          | 38  |

|            |        | 7.2.1 Power transfer                       |     |

|            |        | 7.2.2 Frequency                            |     |

|            |        | 7.2.3 Operating field                      | 38  |

| 8          | Com    | munication signal from VCD to M24LR64-R    | 39  |

| 9          | Data   | rate and data coding                       | 41  |

|            | 9.1    | Data coding mode: 1 out of 256             | 41  |

|            | 9.2    | Data coding mode: 1 out of 4               | 42  |

|            | 9.3    | VCD to M24LR64-R frames                    | 44  |

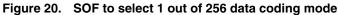

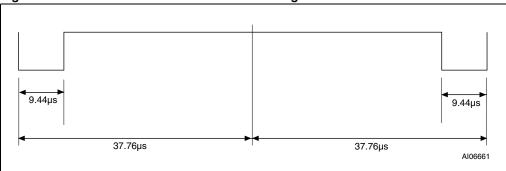

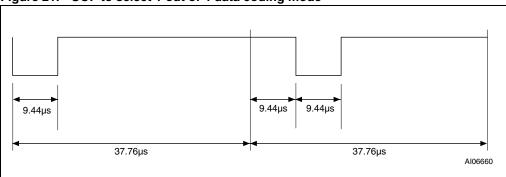

|            | 9.4    | Start of frame (SOF)                       | 44  |

| 10         | Com    | munications signal from M24LR64-R to VCD   | 46  |

|            | 10.1   | Load modulation                            | 46  |

|            | 10.2   | Subcarrier                                 | 46  |

|            | 10.3   | Data rates                                 | 46  |

| 11         | Bit re | epresentation and coding                   | 47  |

|            | 11.1   | Bit coding using one subcarrier            | 47  |

|            |        | 11.1.1 High data rate                      |     |

|            |        | 11.1.2 Low data rate                       |     |

|            | 11.2   | Bit coding using two subcarriers           |     |

|            | 11.3   | High data rate                             | 49  |

| <b>577</b> |        | Doc ID 15170 Rev 8                         | 126 |

Contents M24LR64-R

|                | 11.4                                                                           | Low data rate                                                                                                                               | 49                                           |

|----------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 12             | M24L                                                                           | R64-R to VCD frames                                                                                                                         | 50                                           |

|                | 12.1                                                                           | SOF when using one subcarrier                                                                                                               | 50                                           |

|                | 12.2                                                                           | High data rate                                                                                                                              |                                              |

|                | 12.3                                                                           | Low data rate                                                                                                                               | 50                                           |

|                | 12.4                                                                           | SOF when using two subcarriers                                                                                                              | 51                                           |

|                | 12.5                                                                           | High data rate                                                                                                                              |                                              |

|                | 12.6                                                                           | Low data rate                                                                                                                               | 51                                           |

|                | 12.7                                                                           | EOF when using one subcarrier                                                                                                               | 52                                           |

|                | 12.8                                                                           | High data rate                                                                                                                              | 52                                           |

|                | 12.9                                                                           | Low data rate                                                                                                                               | 52                                           |

|                | 12.10                                                                          | EOF when using two subcarriers                                                                                                              | 53                                           |

|                | 12.11                                                                          | High data rate                                                                                                                              | 53                                           |

|                | 12.12                                                                          | Low data rate                                                                                                                               | 53                                           |

| 13             | Uniqu                                                                          | ie identifier (UID)                                                                                                                         | 54                                           |

|                |                                                                                |                                                                                                                                             |                                              |

| 14             | Appli                                                                          | cation family identifier (AFI)                                                                                                              | 55                                           |

| 14<br>15       | • •                                                                            | storage format identifier (DSFID)                                                                                                           |                                              |

|                | • •                                                                            | ·                                                                                                                                           | 56                                           |

|                | <b>Data</b> 9                                                                  | storage format identifier (DSFID)                                                                                                           | <b>56</b><br>56                              |

| 15             | Data s<br>15.1<br>M24L                                                         | storage format identifier (DSFID)                                                                                                           | <b>56</b><br>56<br><b>57</b>                 |

| 15             | Data s<br>15.1<br>M24L<br>M24L                                                 | Storage format identifier (DSFID)  CRC  R64-R protocol description  R64-R states                                                            | <b>56</b><br>56<br><b>57</b>                 |

| 15             | Data s<br>15.1<br>M24L<br>M24L                                                 | Storage format identifier (DSFID)  CRC  R64-R protocol description  R64-R states                                                            | <b>56</b> 56 <b>57 59</b>                    |

| 15             | Data s<br>15.1<br>M24L<br>M24L<br>17.1                                         | storage format identifier (DSFID)  CRC  R64-R protocol description  R64-R states  Power-off state                                           | <b>56</b> 56 <b>57 59</b> 59                 |

| 15             | Data s<br>15.1<br>M24L<br>M24L<br>17.1<br>17.2                                 | Storage format identifier (DSFID)  CRC  R64-R protocol description  R64-R states  Power-off state  Ready state                              | 56<br>57<br>59<br>59<br>59                   |

| 15             | Data s<br>15.1<br>M24L<br>M24L<br>17.1<br>17.2<br>17.3<br>17.4                 | R64-R states Power-off state Ready state Quiet state                                                                                        | <b>56</b> 56 <b>57 59</b> 59 59              |

| 15<br>16<br>17 | Data s<br>15.1<br>M24L<br>M24L<br>17.1<br>17.2<br>17.3<br>17.4                 | storage format identifier (DSFID)  CRC  R64-R protocol description  R64-R states  Power-off state  Ready state  Quiet state  Selected state | 56<br>57<br>59<br>59<br>59<br>59             |

| 15<br>16<br>17 | Data s<br>15.1<br>M24L<br>M24L<br>17.1<br>17.2<br>17.3<br>17.4<br>Mode         | storage format identifier (DSFID)  CRC  R64-R protocol description  R64-R states  Power-off state  Ready state  Quiet state  Selected state | 56<br>57<br>59<br>59<br>59<br>59<br>61<br>61 |

| 15<br>16<br>17 | Data s<br>15.1<br>M24L<br>M24L<br>17.1<br>17.2<br>17.3<br>17.4<br>Mode<br>18.1 | R64-R protocol description  R64-R states  Power-off state  Ready state  Quiet state  Selected state  Addressed mode                         | 56<br>57<br>59<br>59<br>59<br>59<br>61<br>61 |

| M24LR64-R | Content |

|-----------|---------|

|           |         |

| 19       | <b>Requ</b> e | est format                                                                             |       |

|----------|---------------|----------------------------------------------------------------------------------------|-------|

| 20       | <b>Resp</b> e | onse format                                                                            |       |

|          | 20.2          | Response error code                                                                    |       |

| 21       | Antic         | ollision                                                                               | 66    |

|          | 21.1          | Request parameters                                                                     | 66    |

| 22       | Requ          | est processing by the M24LR64-R                                                        | 68    |

| 23       | Expla         | nation of the possible cases                                                           | 69    |

| 24       | Inven         | tory Initiated command                                                                 | 71    |

| 25       | Timin         | g definition                                                                           | 72    |

|          | 25.1          | t1: M24LR64-R response delay                                                           | 72    |

|          | 25.2          | t2: VCD new request delay                                                              | 72    |

|          | 25.3          | t <sub>3</sub> : VCD new request delay in the absence of a response from the M24LR64-R | 72    |

| 26       | Comr          | mands codes                                                                            | 73    |

|          | 26.1          | Inventory                                                                              | 74    |

|          | 26.2          | Stay Quiet                                                                             | 75    |

|          | 26.3          | Read Single Block                                                                      | 76    |

|          | 26.4          | Write Single Block                                                                     | 78    |

|          | 26.5          | Read Multiple Block                                                                    | 80    |

|          | 26.6          | Select                                                                                 | 82    |

|          | 26.7          | Reset to Ready                                                                         | 83    |

|          | 26.8          | Write AFI                                                                              | 84    |

|          | 26.9          | Lock AFI                                                                               | 86    |

|          | 26.10         | Write DSFID                                                                            | 88    |

|          | 26.11         | Lock DSFID                                                                             | 90    |

|          | 26.12         | Get System Info                                                                        | 92    |

|          | 26.13         | Get Multiple Block Security Status                                                     | 94    |

| <u> </u> |               | Doc ID 15170 Rev 8                                                                     | 5/126 |

|          | 26.14              | Write-sector Password                                |

|----------|--------------------|------------------------------------------------------|

|          | 26.15              | Lock-sector Password 98                              |

|          | 26.16              | Present-sector Password                              |

|          | 26.17              | Fast Read Single Block                               |

|          | 26.18              | Fast Inventory Initiated                             |

|          | 26.19              | Fast Initiate                                        |

|          | 26.20              | Fast Read Multiple Block                             |

|          | 26.21              | Inventory Initiated                                  |

|          | 26.22              | Initiate                                             |

| 27       | Maxin              | num rating                                           |

| 28       | I <sup>2</sup> C D | C and AC parameters                                  |

| 29       | RF DO              | C and AC parameters                                  |

| 30       | Packa              | age mechanical data                                  |

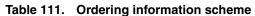

| 31       | Part n             | numbering                                            |

| Appendix | <b>A A</b>         | nticollision algorithm (informative)                 |

|          | A.1                | Algorithm for pulsed slots                           |

| Appendix | B C                | RC (informative)                                     |

|          | B.1                | CRC error detection method                           |

|          | B.2                | CRC calculation example                              |

| Appendix | C A                | pplication family identifier (AFI) (informative) 124 |

| Revision | histor             | y 125                                                |

577

M24LR64-R List of tables

# List of tables

| Table 1.  | Signal names                                                                  | 13 |

|-----------|-------------------------------------------------------------------------------|----|

| Table 2.  | Device select code                                                            |    |

| Table 3.  | Address most significant byte                                                 |    |

| Table 4.  | Address least significant byte                                                |    |

| Table 5.  | Sector details                                                                |    |

| Table 6.  | Sector Security Status Byte area                                              |    |

| Table 7.  | Sector security status byte organization                                      |    |

| Table 8.  | Read / Write protection bit setting                                           |    |

| Table 9.  | Password Control bits                                                         |    |

| Table 10. | Password system area                                                          |    |

| Table 11. | M24LR64-R sector security protection after power-up                           |    |

| Table 12. | M24LR64-R sector security protection after a valid presentation of password 1 |    |

| Table 13. | I2C_Write_Lock bit                                                            |    |

| Table 14. | System parameter sector                                                       |    |

| Table 15. | Operating modes                                                               |    |

| Table 16. | 10% modulation parameters                                                     |    |

| Table 17. | Response data rates.                                                          |    |

| Table 18. | UID format                                                                    |    |

| Table 19. | CRC transmission rules                                                        |    |

| Table 20. | VCD request frame format                                                      |    |

| Table 21. | M24LR64-R Response frame format                                               |    |

| Table 22. | M24LR64-R response depending on Request_flags                                 |    |

| Table 23. | General request format                                                        |    |

| Table 24. | Definition of request flags 1 to 4                                            |    |

| Table 25. | Request flags 5 to 8 when Bit 3 = 0                                           |    |

| Table 26. | Request flags 5 to 8 when Bit 3 = 1                                           | 63 |

| Table 27. | General response format                                                       | 64 |

| Table 28. | Definitions of response flags 1 to 8                                          | 64 |

| Table 29. | Response error code definition                                                | 65 |

| Table 30. | Inventory request format                                                      | 66 |

| Table 31. | Example of the addition of 0-bits to an 11-bit mask value                     | 66 |

| Table 32. | Timing values                                                                 | 72 |

| Table 33. | Command codes                                                                 | 73 |

| Table 34. | Inventory request format                                                      | 74 |

| Table 35. | Inventory response format                                                     | 74 |

| Table 36. | Stay Quiet request format                                                     | 75 |

| Table 37. | Read Single Block request format                                              | 76 |

| Table 38. | Read Single Block response format when Error_flag is NOT set                  | 76 |

| Table 39. | Sector security status                                                        | 76 |

| Table 40. | Read Single Block response format when Error_flag is set                      | 76 |

| Table 41. | Write Single Block request format                                             |    |

| Table 42. | Write Single Block response format when Error_flag is NOT set                 | 78 |

| Table 43. | Write Single Block response format when Error_flag is set                     |    |

| Table 44. | Read Multiple Block request format                                            |    |

| Table 45. | Read Multiple Block response format when Error_flag is NOT set                |    |

| Table 46. | Sector security status                                                        |    |

| Table 47. | Read Multiple Block response format when Error_flag is set                    |    |

| Table 48. | Select request format                                                         |    |

|           |                                                                               |    |

Doc ID 15170 Rev 8

7/126

List of tables M24LR64-R

| Table 49.  | Select Block response format when Error_flag is NOT set                       | 82  |

|------------|-------------------------------------------------------------------------------|-----|

| Table 50.  | Select response format when Error_flag is set                                 | 82  |

| Table 51.  | Reset to Ready request format                                                 | 83  |

| Table 52.  | Reset to Ready response format when Error_flag is NOT set                     | 83  |

| Table 53.  | Reset to ready response format when Error_flag is set                         | 83  |

| Table 54.  | Write AFI request format                                                      | 84  |

| Table 55.  | Write AFI response format when Error_flag is NOT set                          | 84  |

| Table 56.  | Write AFI response format when Error_flag is set                              | 84  |

| Table 57.  | Lock AFI request format                                                       | 86  |

| Table 58.  | Lock AFI response format when Error_flag is NOT set                           | 86  |

| Table 59.  | Lock AFI response format when Error_flag is set                               |     |

| Table 60.  | Write DSFID request format                                                    | 88  |

| Table 61.  | Write DSFID response format when Error_flag is NOT set                        | 88  |

| Table 62.  | Write DSFID response format when Error_flag is set                            | 88  |

| Table 63.  | Lock DSFID request format                                                     | 90  |

| Table 64.  | Lock DSFID response format when Error_flag is NOT set                         | 90  |

| Table 65.  | Lock DSFID response format when Error_flag is set                             |     |

| Table 66.  | Get System Info request format                                                |     |

| Table 67.  | Get System Info response format when Error_flag is NOT set                    | 92  |

| Table 68.  | Get System Info response format when Error_flag is set                        |     |

| Table 69.  | Get Multiple Block Security Status request format                             |     |

| Table 70.  | Get Multiple Block Security Status response format when Error_flag is NOT set |     |

| Table 71.  | Sector security status                                                        |     |

| Table 72.  | Get Multiple Block Security Status response format when Error_flag is set     | 95  |

| Table 73.  | Write-sector Password request format                                          | 96  |

| Table 74.  | Write-sector Password response format when Error_flag is NOT set              | 96  |

| Table 75.  | Write-sector Password response format when Error_flag is set                  | 96  |

| Table 76.  | Lock-sector Password request format                                           |     |

| Table 77.  | Sector security status                                                        | 98  |

| Table 78.  | Lock-sector Password response format when Error_flag is NOT set               | 98  |

| Table 79.  | Lock-sector Password response format when Error_flag is set                   | 98  |

| Table 80.  | Present-sector Password request format                                        | 100 |

| Table 81.  | Present-sector Password response format when Error_flag is NOT set            |     |

| Table 82.  | Present-sector Password response format when Error_flag is set                | 100 |

| Table 83.  | Fast Read Single Block request format                                         | 102 |

| Table 84.  | Fast Read Single Block response format when Error_flag is NOT set             | 102 |

| Table 85.  | Sector security status                                                        | 102 |

| Table 86.  | Fast Read Single Block response format when Error_flag is set                 |     |

| Table 87.  | Fast Inventory Initiated request format                                       |     |

| Table 88.  | Fast Inventory Initiated response format                                      |     |

| Table 89.  | Fast Initiate request format                                                  |     |

| Table 90.  | Fast Initiate response format                                                 |     |

| Table 91.  | Fast Read Multiple Block request format                                       |     |

| Table 92.  | Fast Read Multiple Block response format when Error_flag is NOT set           |     |

| Table 93.  | Sector security status if Option_flag is set                                  |     |

| Table 94.  | Fast Read Multiple Block response format when Error_flag is set               |     |

| Table 95.  | Inventory Initiated request format                                            |     |

| Table 96.  | Inventory Initiated response format                                           |     |

| Table 97.  | Initiate request format                                                       |     |

| Table 98.  | Initiate Initiated response format                                            |     |

| Table 99.  | Absolute maximum ratings                                                      |     |

| Table 100. | I <sup>2</sup> C operating conditions                                         | 111 |

|            |                                                                               |     |

**577**

M24LR64-R List of tables

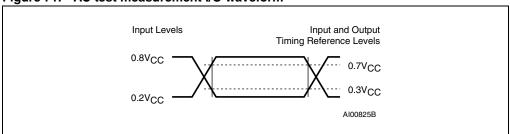

| Table 101. | AC test measurement conditions                                         | 111 |

|------------|------------------------------------------------------------------------|-----|

| Table 102. | Input parameters                                                       | 111 |

| Table 103. | I <sup>2</sup> C DC characteristics                                    | 112 |

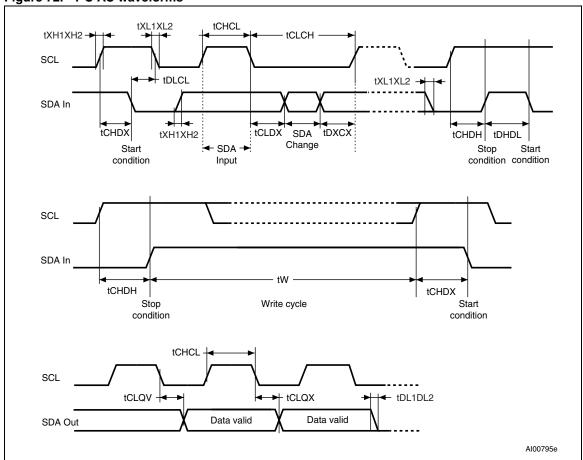

| Table 104. | I <sup>2</sup> C AC characteristics                                    | 113 |

| Table 105. | RF AC characteristics                                                  | 115 |

| Table 106. | RF DC characteristics                                                  | 116 |

| Table 107. | Operating conditions                                                   | 116 |

| Table 108. | SO8N – 8-lead plastic small outline, 150 mils body width, package data | 117 |

| Table 109. | UFDFPN8 (MLP8) – Ultra thin fine pitch dual flat package no lead       |     |

|            | 2 x 3 mm, package mechanical data                                      | 118 |

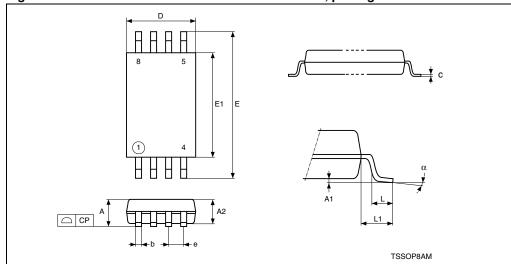

| Table 110. | TSSOP8 – 8-lead thin shrink small outline, package mechanical data     |     |

| Table 111. | Ordering information scheme                                            | 120 |

|            | CRC definition                                                         |     |

| Table 113. | AFI coding                                                             | 124 |

| Table 114. | Document revision history                                              | 125 |

|            |                                                                        |     |

List of figures M24LR64-R

# **List of figures**

| igure 1.  | Logic diagram                                                                                 | . 12 |

|-----------|-----------------------------------------------------------------------------------------------|------|

| igure 2.  | SO8 connections                                                                               | 13   |

| igure 3.  | Device select code                                                                            |      |

| igure 4.  | Maximum R <sub>P</sub> value versus bus parasitic capacitance (C) for an I <sup>2</sup> C bus | 15   |

| igure 5.  | I <sup>2</sup> C bus protocol                                                                 |      |

| igure 6.  | Block diagram                                                                                 |      |

| igure 7.  | Memory sector organization                                                                    | 18   |

| igure 8.  | I <sup>2</sup> C Present Password command                                                     |      |

| igure 9.  | I <sup>2</sup> C Write Password command                                                       |      |

| igure 10. | Write mode sequences with I2C_Write_Lock bit = 1 (data write inhibited)                       |      |

| igure 11. | Write mode sequences with I2C_Write_Lock bit = 0 (data write enabled)                         |      |

| igure 12. | Write cycle polling flowchart using ACK                                                       |      |

| igure 13. | Read mode sequences                                                                           |      |

| igure 14. | 100% modulation waveform                                                                      |      |

| igure 15. | 10% modulation waveform                                                                       |      |

| igure 16. | 1 out of 256 coding mode                                                                      |      |

| igure 17. | Detail of a time period                                                                       |      |

| igure 18. | 1 out of 4 coding mode                                                                        |      |

| igure 19. | 1 out of 4 coding example                                                                     |      |

| igure 20. | SOF to select 1 out of 256 data coding mode                                                   |      |

| igure 21. | SOF to select 1 out of 4 data coding mode                                                     |      |

| igure 22. | EOF for either data coding mode                                                               |      |

| igure 23. | Logic 0, high data rate                                                                       |      |

| igure 24. | Logic 0, high data rate x2                                                                    |      |

| igure 25. | Logic 1, high data rate                                                                       |      |

| igure 26. | Logic 1, high data rate x2                                                                    |      |

| igure 27. | Logic 0, low data rate                                                                        |      |

| igure 28. | Logic 0, low data rate x2                                                                     |      |

| igure 29. | Logic 1, low data rate                                                                        |      |

| igure 30. | Logic 1, low data rate x2                                                                     |      |

| igure 31. | Logic 0, high data rate                                                                       |      |

| igure 32. | Logic 1, high data rate                                                                       |      |

| igure 33. | Logic 0, low data rate                                                                        |      |

| igure 34. | Logic 1, low data rate                                                                        |      |

| igure 35. | Start of frame, high data rate, one subcarrier                                                |      |

| igure 36. | Start of frame, high data rate, one subcarrier x2                                             |      |

| igure 37. | Start of frame, low data rate, one subcarrier                                                 |      |

| igure 38. | Start of frame, low data rate, one subcarrier x2                                              |      |

| igure 39. | Start of frame, high data rate, two subcarriers                                               |      |

| igure 40. | Start of frame, low data rate, two subcarriers                                                |      |

| igure 41. | End of frame, high data rate, one subcarriers                                                 |      |

| igure 42. | End of frame, high data rate, one subcarriers x2                                              |      |

| igure 43. | End of frame, low data rate, one subcarriers                                                  |      |

| igure 44. | End of frame, low data rate, one subcarriers x2                                               |      |

| igure 45. | End of frame, high data rate, two subcarriers                                                 |      |

| igure 46. | End of frame, low data rate, two subcarriers                                                  |      |

| igure 47. | M24LR64-R decision tree for AFI                                                               |      |

| igure 48. | M24LR64-R protocol timing                                                                     | 58   |

|           |                                                                                               |      |

**577**

M24LR64-R List of figures

| Figure 49. | M24LR64-R state transition diagram                                            | 60  |

|------------|-------------------------------------------------------------------------------|-----|

| Figure 50. | Principle of comparison between the mask, the slot number and the UID         |     |

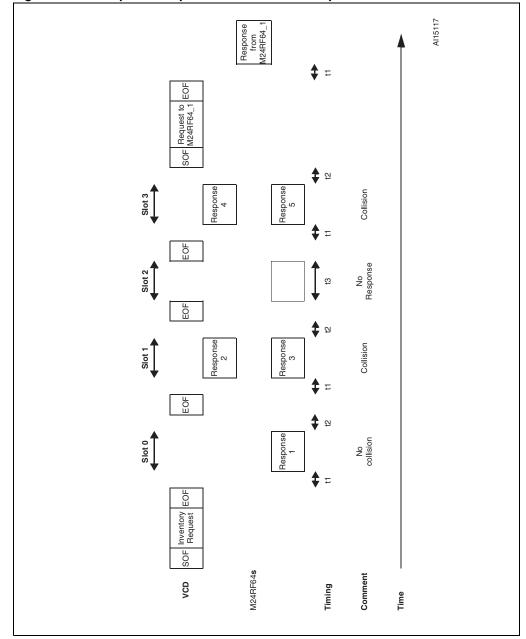

| Figure 51. | Description of a possible anticollision sequence                              |     |

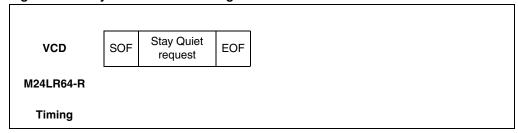

| Figure 52. | Stay Quiet frame exchange between VCD and M24LR64-R                           | 75  |

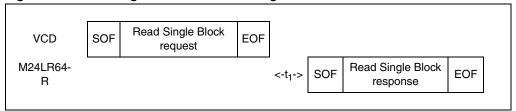

| Figure 53. | Read Single Block frame exchange between VCD and M24LR64-R                    | 77  |

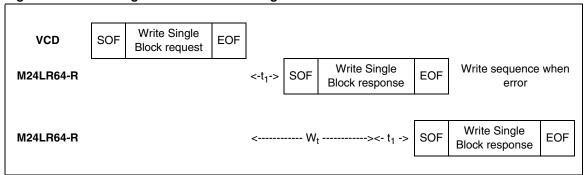

| Figure 54. | Write Single Block frame exchange between VCD and M24LR64-R                   | 79  |

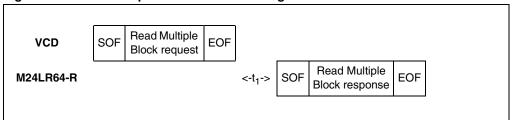

| Figure 55. | Read Multiple Block frame exchange between VCD and M24LR64-R                  | 81  |

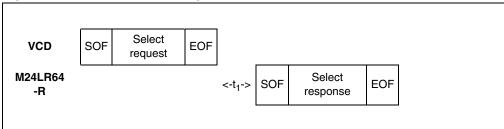

| Figure 56. | Select frame exchange between VCD and M24LR64-R                               |     |

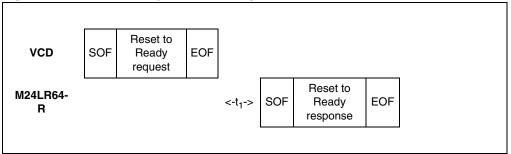

| Figure 57. | Reset to Ready frame exchange between VCD and M24LR64-R                       | 83  |

| Figure 58. | Write AFI frame exchange between VCD and M24LR64-R                            | 85  |

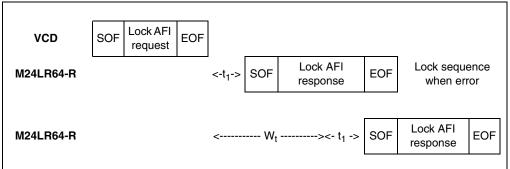

| Figure 59. | Lock AFI frame exchange between VCD and M24LR64-R                             | 87  |

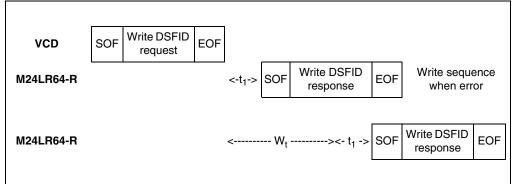

| Figure 60. | Write DSFID frame exchange between VCD and M24LR64-R                          | 89  |

| Figure 61. | Lock DSFID frame exchange between VCD and M24LR64-R                           | 91  |

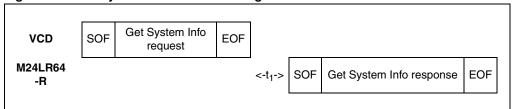

| Figure 62. | Get System Info frame exchange between VCD and M24LR64-R                      | 93  |

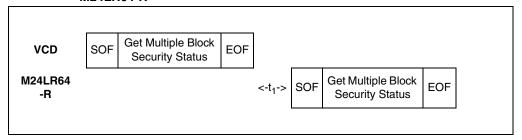

| Figure 63. | Get Multiple Block Security Status frame exchange between VCD and M24LR64-R . | 95  |

| Figure 64. | Write-sector Password frame exchange between VCD and M24LR64-R                | 97  |

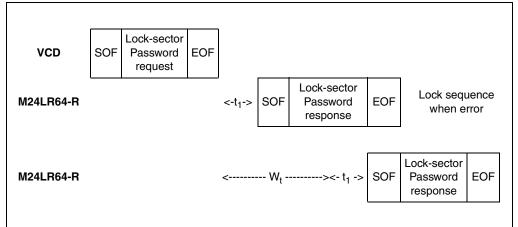

| Figure 65. | Lock-sector Password frame exchange between VCD and M24LR64-R                 | 99  |

| Figure 66. | Present-sector Password frame exchange between VCD and M24LR64-R              | 101 |

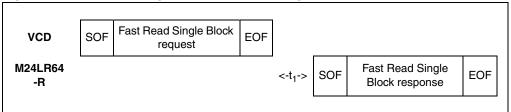

| Figure 67. | Fast Read Single Block frame exchange between VCD and M24LR64-R               | 103 |

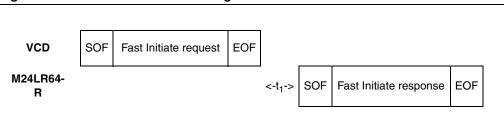

| Figure 68. | Fast Initiate frame exchange between VCD and M24LR64-R                        | 105 |

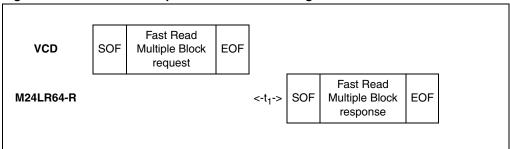

| Figure 69. | Fast Read Multiple Block frame exchange between VCD and M24LR64-R             |     |

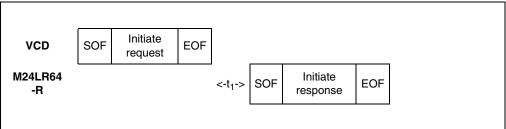

| Figure 70. | Initiate frame exchange between VCD and M24LR64-R                             | 109 |

| Figure 71. | AC test measurement I/O waveform                                              |     |

| Figure 72. | I <sup>2</sup> C AC waveforms                                                 | 114 |

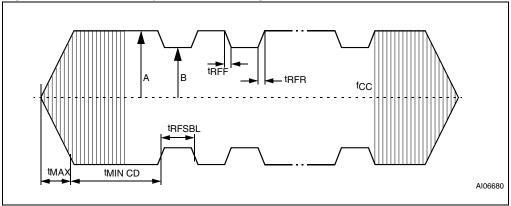

| Figure 73. | M24LR64-R synchronous timing, transmit and receive                            | 116 |

| Figure 74. | SO8N – 8-lead plastic small outline, 150 mils body width, package outline     | 117 |

| Figure 75. | UFDFPN8 (MLP8) – Ultra thin fine pitch dual flat package no lead              |     |

|            | 2 x 3 mm, package outline                                                     |     |

| Figure 76. | TSSOP8 – 8-lead thin shrink small outline, package outline                    | 119 |

Description M24LR64-R

# 1 Description

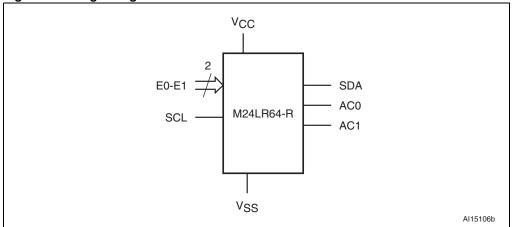

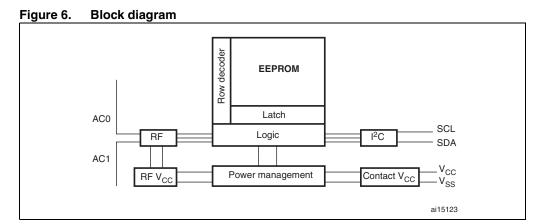

The M24LR64-R device is a dual-interface, electrically erasable programmable memory (EEPROM). It features an I $^2$ C interface and can be operated from a V $_{CC}$  power supply. It is also a contactless memory powered by the received carrier electromagnetic wave. The M24LR64-R is organized as 8192  $\times$  8 bits in the I $^2$ C mode and as 2048  $\times$  32 bits in the ISO 15693 and ISO 18000-3 mode 1 RF mode.

Figure 1. Logic diagram

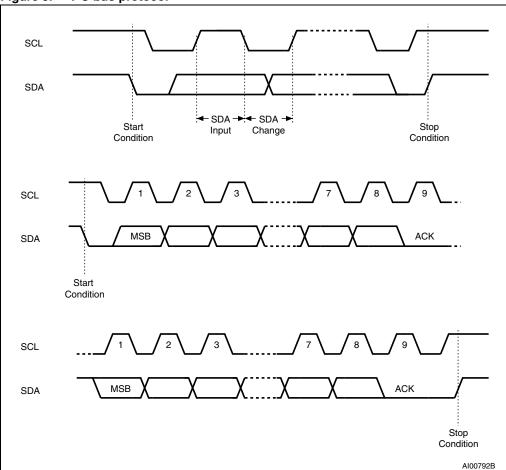

I<sup>2</sup>C uses a two-wire serial interface, comprising a bidirectional data line and a clock line. The devices carry a built-in 4-bit device type identifier code (1010) in accordance with the I<sup>2</sup>C bus definition.

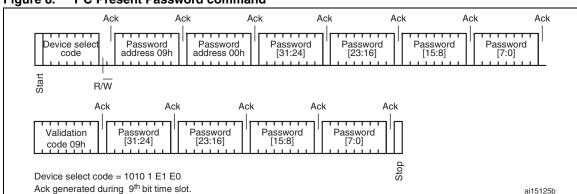

The device behaves as a slave in the  $I^2C$  protocol, with all memory operations synchronized by the serial clock. Read and Write operations are initiated by a Start condition, generated by the bus master. The Start condition is followed by a device select code and Read/Write bit ( $\overline{RW}$ ) (as described in *Table 2*), terminated by an acknowledge bit.

When writing data to the memory, the device inserts an acknowledge bit during the 9<sup>th</sup> bit time, following the bus master's 8-bit transmission. When data is read by the bus master, the bus master acknowledges the receipt of the data byte in the same way. Data transfers are terminated by a Stop condition after an Ack for Write, and after a NoAck for Read.

In the ISO15693/ISO18000-3 mode 1 RF mode, the M24LR64-R is accessed via the 13.56 MHz carrier electromagnetic wave on which incoming data are demodulated from the received signal amplitude modulation (ASK: amplitude shift keying). The received ASK wave is 10% or 100% modulated with a data rate of 1.6 Kbit/s using the 1/256 pulse coding mode or a data rate of 26 Kbit/s using the 1/4 pulse coding mode.

Outgoing data are generated by the M24LR64-R load variation using Manchester coding with one or two subcarrier frequencies at 423 kHz and 484 kHz. Data are transferred from the M24LR64-R at 6.6 Kbit/s in low data rate mode and 26 Kbit/s high data rate mode. The M24LR64-R supports the 53 Kbit/s in high data rate mode in one subcarrier frequency at 423 kHz.

The M24LR64-R follows the ISO 15693 and ISO 18000-3 mode 1 recommendation for radio-frequency power and signal interface.

M24LR64-R Description

Table 1. Signal names

| Signal name     | Function       | Direction |

|-----------------|----------------|-----------|

| E0, E1          | Chip Enable    | Input     |

| SDA             | Serial Data    | I/O       |

| SCL             | Serial Clock   | Input     |

| AC0, AC1        | Antenna coils  | I/O       |

| V <sub>CC</sub> | Supply voltage |           |

| $V_{SS}$        | Ground         |           |

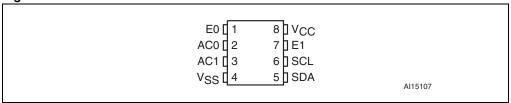

Figure 2. SO8 connections

<sup>1.</sup> See Package mechanical data section for package dimensions, and how to identify pin-1.

Signal description M24LR64-R

#### Signal description 2

#### 2.1 Serial Clock (SCL)

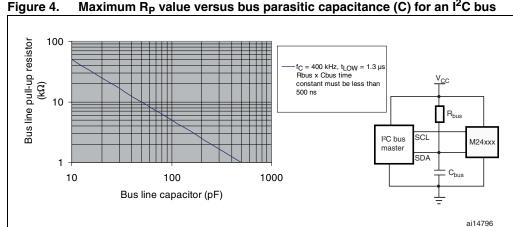

This input signal is used to strobe all data in and out of the device. In applications where this signal is used by slave devices to synchronize the bus to a slower clock, the bus master must have an open drain output, and a pull-up resistor must be connected from Serial Clock (SCL) to  $V_{CC}$ . (Figure 4 indicates how the value of the pull-up resistor can be calculated). In most applications, though, this method of synchronization is not employed, and so the pullup resistor is not necessary, provided that the bus master has a push-pull (rather than open drain) output.

#### 2.2 Serial Data (SDA)

This bidirectional signal is used to transfer data in or out of the device. It is an open drain output that may be wire-OR'ed with other open drain or open collector signals on the bus. A pull up resistor must be connected from Serial Data (SDA) to  $V_{CC}$ . (Figure 4 indicates how the value of the pull-up resistor can be calculated).

#### 2.3 Chip Enable (E0, E1)

These input signals are used to set the value that is to be looked for on the two least significant bits (b2, b1) of the 7-bit device select code. These inputs must be tied to V<sub>CC</sub> or V<sub>SS</sub>, to establish the device select code as shown in Figure 3. When not connected (left floating), these inputs are read as low (0,0).

**Device select code** Figure 3.

#### 2.4 Antenna coil (AC0, AC1)

These inputs are used to connect the device to an external coil. When correctly tuned, the coil is used to power and access the device using the ISO 15693 and ISO 18000-3 mode 1 protocols.

#### V<sub>SS</sub> ground 2.5

$V_{SS}$  is the reference for the  $V_{CC}$  supply voltage.

M24LR64-R Signal description

#### 2.6 Supply voltage (V<sub>CC</sub>)

#### 2.6.1 Operating supply voltage V<sub>CC</sub>

Prior to selecting the memory and issuing instructions to it, a valid and stable V<sub>CC</sub> voltage within the specified [V<sub>CC</sub>(min), V<sub>CC</sub>(max)] range must be applied (see *Table 100*). In order to secure a stable DC supply voltage, it is recommended to decouple the  $V_{CC}$  line with a suitable capacitor (usually of the order of 10 nF to 100 nF) close to the  $V_{\rm CC}/V_{\rm SS}$  package pins.

This voltage must remain stable and valid until the end of the transmission of the instruction and, for a Write instruction, until the completion of the internal I2C write cycle (t<sub>W</sub>).

#### 2.6.2 **Power-up conditions**

When the power supply is turned on,  $V_{CC}$  rises from  $V_{SS}$  to  $V_{CC}$ . The  $V_{CC}$  rise time must not vary faster than 1V/µs.

#### 2.6.3 **Device reset**

In order to prevent inadvertent write operations during power-up, a power-on reset (POR) circuit is included. At power-up (continuous rise of V<sub>CC</sub>), the device does not respond to any instruction until V<sub>CC</sub> has reached the power-on reset threshold voltage (this threshold is lower than the minimum  $V_{CC}$  operating voltage defined in Table 100). When  $V_{CC}$  passes over the POR threshold, the device is reset and enters the Standby Power mode, however, the device must not be accessed until V<sub>CC</sub> has reached a valid and stable V<sub>CC</sub> voltage within the specified  $[V_{CC}(min), V_{CC}(max)]$  range.

In a similar way, during power-down (continuous decrease in  $V_{CC}$ ), as soon as  $V_{CC}$  drops below the power-on reset threshold voltage, the device stops responding to any instruction sent to it.

#### 2.6.4 **Power-down conditions**

During power-down (continuous decay of  $V_{CC}$ ), the device must be in Standby Power mode (mode reached after decoding a Stop condition, assuming that there is no internal write cycle in progress).

577

Doc ID 15170 Rev 8

Signal description M24LR64-R

Figure 5. I<sup>2</sup>C bus protocol

Table 2. Device select code

|                    | Device type identifier <sup>(1)</sup> |    |    | Chip Enable address <sup>(2)</sup> |                   |    | RW |    |

|--------------------|---------------------------------------|----|----|------------------------------------|-------------------|----|----|----|

|                    | b7                                    | b6 | b5 | b4                                 | b3                | b2 | b1 | b0 |

| Device select code | 1                                     | 0  | 1  | 0                                  | E2 <sup>(3)</sup> | E1 | E0 | R₩ |

- 1. The most significant bit, b7, is sent first.

- 2. E0 and E1 are compared against the respective external pins on the memory device.

- 3. E2 is not connected to any external pin. It is however used to address the M24LR64-R as described in Section 3 and Section 4.

Table 3. Address most significant byte

| b15 b14 b13 b12 b11 b10 b | b9 b8 |

|---------------------------|-------|

|---------------------------|-------|

Table 4. Address least significant byte

| b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 | l |

|----|----|----|----|----|----|----|----|---|

# 3 User memory organization

The M24LR64-R is divided into 64 sectors of 32 blocks of 32 bits as shown in *Table 5*. *Figure 7* shows the memory sector organization. Each sector can be individually readand/or write-protected using a specific password command. Read and write operations are possible if the addressed data are not in a protected sector.

The M24LR64-R also has a 64-bit block that is used to store the 64-bit unique identifier (UID). The UID is compliant with the ISO 15963 description, and its value is used during the anticollision sequence (Inventory). This block is not accessible by the user and its value is written by ST on the production line.

The M24LR64-R includes an AFI register that stores the application family identifier, and a DSFID register that stores the data storage family identifier used in the anticollision algorithm.

The M24LR64-R has four additional 32-bit blocks that store an I<sup>2</sup>C password plus three RF password codes.

Sector Area Sector security status 1 Kbit EEPROM sector 0 5 bits 1 Kbit EEPROM sector 1 5 bits 1 Kbit EEPROM sector 2 5 bits 3 1 Kbit EEPROM sector 5 bits 60 1 Kbit EEPROM sector 5 bits 61 1 Kbit EEPROM sector 5 bits 1 Kbit EEPROM sector 62 5 bits 1 Kbit EEPROM sector 5 bits I2C Password System RF Password 1 System RF Password 2 System RF Password 3 System 8 bit DSFID System 8 bit AFI System 64 bit UID System ai15124

Figure 7. Memory sector organization

#### Sector details

The M24LR64-R user memory is divided into 64 sectors. Each sector contains 1024 bits. The protection scheme is described in *Section 4: System memory area*.

In RF mode, a sector provides 32 blocks of 32 bits. Each read and write access are done by block. Read and write block accesses are controlled by a Sector Security Status byte that defines the access rights to all the 32 blocks contained in the sector. If the sector is not protected, a Write command updates the complete 32 bits of the selected block.

In I<sup>2</sup>C mode, a sector provides 128 bytes that can be individually accessed in read and write modes. When protected by the corresponding I2C\_Write\_Lock bit, the entire sector is write-protected. To access the user memory, the device select code used for any I<sup>2</sup>C command must have the E2 Chip Enable address at 0.

Table 5. Sector details

| Sector<br>number | RF block address | I <sup>2</sup> C byte<br>address | Bits [31:24] | Bits [23:16] | Bits [15:8] | Bits [7:0] |

|------------------|------------------|----------------------------------|--------------|--------------|-------------|------------|

|                  | 0                | 0                                | user         | user         | user        | user       |

|                  | 1                | 4                                | user         | user         | user        | user       |

|                  | 2                | 8                                | user         | user         | user        | user       |

|                  | 3                | 12                               | user         | user         | user        | user       |

|                  | 4                | 16                               | user         | user         | user        | user       |

|                  | 5                | 20                               | user         | user         | user        | user       |

|                  | 6                | 24                               | user         | user         | user        | user       |

|                  | 7                | 28                               | user         | user         | user        | user       |

|                  | 8                | 32                               | user         | user         | user        | user       |

|                  | 9                | 36                               | user         | user         | user        | user       |

|                  | 10               | 40                               | user         | user         | user        | user       |

|                  | 11               | 44                               | user         | user         | user        | user       |

|                  | 12               | 48                               | user         | user         | user        | user       |

|                  | 13               | 52                               | user         | user         | user        | user       |

|                  | 14               | 56                               | user         | user         | user        | user       |

| 0                | 15               | 60                               | user         | user         | user        | user       |

| U                | 16               | 64                               | user         | user         | user        | user       |

|                  | 17               | 68                               | user         | user         | user        | user       |

|                  | 18               | 72                               | user         | user         | user        | user       |

|                  | 19               | 76                               | user         | user         | user        | user       |

|                  | 20               | 80                               | user         | user         | user        | user       |

|                  | 21               | 84                               | user         | user         | user        | user       |

|                  | 22               | 88                               | user         | user         | user        | user       |

|                  | 23               | 92                               | user         | user         | user        | user       |

|                  | 24               | 96                               | user         | user         | user        | user       |

|                  | 25               | 100                              | user         | user         | user        | user       |

|                  | 26               | 104                              | user         | user         | user        | user       |

|                  | 27               | 108                              | user         | user         | user        | user       |

|                  | 28               | 112                              | user         | user         | user        | user       |

|                  | 29               | 116                              | user         | user         | user        | user       |

|                  | 30               | 120                              | user         | user         | user        | user       |

|                  | 31               | 124                              | user         | user         | user        | user       |

**577**

Doc ID 15170 Rev 8

Table 5. Sector details (continued)

| Sector<br>number | RF block address | I <sup>2</sup> C byte<br>address | Bits [31:24] | Bits [23:16] | Bits [15:8] | Bits [7:0] |

|------------------|------------------|----------------------------------|--------------|--------------|-------------|------------|

|                  | 32               | 128                              | user         | user         | user        | user       |

|                  | 33               | 132                              | user         | user         | user        | user       |

|                  | 34               | 136                              | user         | user         | user        | user       |

|                  | 35               | 140                              | user         | user         | user        | user       |

| 1                | 36               | 144                              | user         | user         | user        | user       |

|                  | 37               | 148                              | user         | user         | user        | user       |

|                  | 38               | 152                              | user         | user         | user        | user       |

|                  | 39               | 156                              | user         | user         | user        | user       |

|                  |                  |                                  |              |              |             |            |

|                  |                  |                                  |              |              | •••         |            |

Table 5. Sector details (continued)

| Sector<br>number | RF block address | I <sup>2</sup> C byte address | Bits [31:24] | Bits [23:16] | Bits [15:8] | Bits [7:0] |

|------------------|------------------|-------------------------------|--------------|--------------|-------------|------------|

|                  | 2016             | 8064                          | user         | user         | user        | user       |

|                  | 2017             | 8068                          | user         | user         | user        | user       |

|                  | 2018             | 8072                          | user         | user         | user        | user       |

|                  | 2019             | 8076                          | user         | user         | user        | user       |

|                  | 2020             | 8080                          | user         | user         | user        | user       |

|                  | 2021             | 8084                          | user         | user         | user        | user       |

|                  | 2022             | 8088                          | user         | user         | user        | user       |

|                  | 2023             | 8092                          | user         | user         | user        | user       |

|                  | 2024             | 8096                          | user         | user         | user        | user       |

|                  | 2025             | 8100                          | user         | user         | user        | user       |

|                  | 2026             | 8104                          | user         | user         | user        | user       |

|                  | 2027             | 8108                          | user         | user         | user        | user       |

|                  | 2028             | 8112                          | user         | user         | user        | user       |

|                  | 2029             | 8116                          | user         | user         | user        | user       |

|                  | 2030             | 8120                          | user         | user         | user        | user       |

| 63               | 2031             | 8124                          | user         | user         | user        | user       |

| 03               | 2032             | 8128                          | user         | user         | user        | user       |

|                  | 2033             | 8132                          | user         | user         | user        | user       |

|                  | 2034             | 8136                          | user         | user         | user        | user       |

|                  | 2035             | 8140                          | user         | user         | user        | user       |

|                  | 2036             | 8144                          | user         | user         | user        | user       |

|                  | 2037             | 8148                          | user         | user         | user        | user       |

|                  | 2038             | 8152                          | user         | user         | user        | user       |

|                  | 2039             | 8156                          | user         | user         | user        | user       |

|                  | 2040             | 8160                          | user         | user         | user        | user       |

|                  | 2041             | 8164                          | user         | user         | user        | user       |

|                  | 2042             | 8168                          | user         | user         | user        | user       |

|                  | 2043             | 8172                          | user         | user         | user        | user       |

|                  | 2044             | 8176                          | user         | user         | user        | user       |

|                  | 2045             | 8180                          | user         | user         | user        | user       |

|                  | 2046             | 8184                          | user         | user         | user        | user       |

|                  | 2047             | 8188                          | user         | user         | user        | user       |

**577**

Doc ID 15170 Rev 8

System memory area M24LR64-R

# 4 System memory area

# 4.1 M24LR64-R RF block security

The M24LR64-R provides a special protection mechanism based on passwords. Each memory sector of the M24LR64-R can be individually protected by one out of three available passwords, and each sector can also have Read/Write access conditions set.

Each memory sector of the M24LR64-R is assigned with a Sector security status byte including a Sector Lock bit, two Password Control bits and two Read/Write protection bits as shown in *Table 7. Table 6* describes the organization of the Sector security status byte which can be read using the Read Single Block and Read Multiple Block commands with the Option\_flag set to '1'.

On delivery, the default value of the SSS bytes is reset to 00h.

Table 6. Sector Security Status Byte area

| RF address | I <sup>2</sup> C byte a | ddress | Bits [31:24] | Bits [23:16] | Bits [15:8] | Bits [7:0] |

|------------|-------------------------|--------|--------------|--------------|-------------|------------|

| 0          | E2 = 1                  | 0      | SSS 3        | SSS 2        | SSS 1       | SSS 0      |

| 128        | E2 = 1                  | 4      | SSS 7        | SSS 6        | SSS 5       | SSS 4      |

| 256        | E2 = 1                  | 8      | SSS 11       | SSS 10       | SSS 9       | SSS 8      |

| 384        | E2 = 1                  | 12     | SSS 15       | SSS 14       | SSS 13      | SSS 12     |

| 512        | E2 = 1                  | 16     | SSS 19       | SSS 18       | SSS 17      | SSS 16     |

| 640        | E2 = 1                  | 20     | SSS 23       | SSS 22       | SSS 21      | SSS 20     |

| 768        | E2 = 1                  | 24     | SSS 27       | SSS 26       | SSS 25      | SSS 24     |

| 896        | E2 = 1                  | 28     | SSS 31       | SSS 30       | SSS 29      | SSS 28     |

| 1024       | E2 = 1                  | 32     | SSS 35       | SSS 34       | SSS 33      | SSS 32     |

| 1152       | E2 = 1                  | 36     | SSS 39       | SSS 38       | SSS 37      | SSS 36     |

| 1280       | E2 = 1                  | 40     | SSS 43       | SSS 42       | SSS 41      | SSS 40     |

| 1408       | E2 = 1                  | 44     | SSS 47       | SSS 46       | SSS 45      | SSS 44     |

| 1536       | E2 = 1                  | 48     | SSS 51       | SSS 50       | SSS 49      | SSS 48     |

| 1664       | E2 = 1                  | 52     | SSS 55       | SSS 54       | SSS 53      | SSS 52     |

| 1792       | E2 = 1                  | 56     | SSS 59       | SSS 58       | SSS 57      | SSS 56     |

| 1920       | E2 = 1                  | 60     | SSS 63       | SSS 62       | SSS 61      | SSS 60     |

Table 7. Sector security status byte organization

| <br>b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub>     | b <sub>1</sub> | b <sub>0</sub> |

|--------------------|----------------|----------------|----------------|----------------|--------------------|----------------|----------------|

| 0                  | 0              | 0              | Password       | Control bits   | Read / Write<br>bi | •              | Sector<br>Lock |

When the Sector Lock bit is set to '1', for instance by issuing a Lock-sector Password command, the 2 Read/Write protection bits  $(b_1, b_2)$  are used to set the Read/Write access of the sector as described in *Table 8*.

|                |                                 | •                                     |            |         |          |  |                           |

|----------------|---------------------------------|---------------------------------------|------------|---------|----------|--|---------------------------|

| Sector<br>Lock | b <sub>2</sub> , b <sub>1</sub> | Sector access when password presented |            | •       |          |  | nen password not<br>ented |

| 0              | XX                              | Read                                  | Read Write |         | Write    |  |                           |

| 1              | 00                              | Read                                  | Write      | Read    | No Write |  |                           |

| 1              | 01                              | Read                                  | Write      | Read    | Write    |  |                           |

| 1              | 10                              | Read                                  | Write      | No Read | No Write |  |                           |

| 1              | 11                              | Read                                  | No Write   | No Read | No Write |  |                           |

Table 8. Read / Write protection bit setting

The next 2 bits of the Sector security status byte  $(b_3, b_4)$  are the Password Control bits. The value these two bits is used to link a password to the sector as defined in *Table 9*.

Table 9. Password Control bits

| b <sub>4</sub> , b <sub>3</sub> | Password                                  |

|---------------------------------|-------------------------------------------|

| 00                              | The sector is not protected by a Password |

| 01                              | The sector is protected by the Password 1 |

| 10                              | The sector is protected by the Password 2 |

| 11                              | The sector is protected by the Password 3 |

The M24LR64-R password protection is organized around a dedicated set of commands plus a system area of three password blocks where the password values are stored. This system area is described in *Table 10*.

Table 10. Password system area

| Add | 0 7 8 15 16 23 24 |            |          |  |  |  |  |  |

|-----|-------------------|------------|----------|--|--|--|--|--|

| 1   |                   | Password 1 |          |  |  |  |  |  |

| 2   |                   | Password 2 |          |  |  |  |  |  |

| 3   |                   | Pas        | ssword 3 |  |  |  |  |  |

The dedicated password commands are:

## Write-sector Password:

The Write-sector Password command is used to write a 32-bit block into the password system area. This command must be used to update password values. After the write cycle, the new password value is automatically activated. It is possible to modify a password value after issuing a valid Present-sector Password command.

On delivery, the three default password values are set to 0000 0000h and are activated.

#### Lock-sector Password:

The Lock-sector Password command is used to set the Sector security status byte of the selected sector. Bits  $b_4$  to  $b_1$  of the Sector security status byte are affected by the Lock-sector Password command. The Sector Lock bit,  $b_0$ , is set to '1' automatically. After issuing a Lock-sector Password command, the protection settings of the selected sector are activated. The protection of a locked block cannot be changed in RF mode. A Lock-sector Password command sent to a locked sector returns an error code.

577

Doc ID 15170 Rev 8

23/126

System memory area M24LR64-R

#### Present-sector Password:

The Present-sector Password command is used to present one of the three passwords to the M24LR64-R in order to modify the access rights of all the memory sectors linked to that password (*Table 8*) including the password itself. If the presented password is correct, the access rights remain activated until the tag is powered off or until a new Present-sector Password command is issued. If the presented password value is not correct, all the access rights of all the memory sectors are deactivated.

## Sector security status byte area access conditions in I<sup>2</sup>C mode:

In I<sup>2</sup>C mode, read access to the Sector security status byte area is always allowed. Write access depends on the correct presentation of the I<sup>2</sup>C password (see *I2C Present Password command description on page 26*).

To access the Sector security status byte area, the device select code used for any I<sup>2</sup>C command must have the E2 Chip Enable address at 1.

An I<sup>2</sup>C write access to a Sector security status byte re-initializes the RF access condition to the given memory sector.

## 4.2 Example of the M24LR64-R security protection

Table 11 and Table 12 show the sector security protections before and after a valid Present-sector Password command. Table 11 shows the sector access rights of an M24LR64-R after power-up. After a valid Present-sector Password command with password 1, the memory sector access is changed as shown in Table 12.

Table 11. M24LR64-R sector security protection after power-up

| Sector  |                      |         |          | Sector                                       | seci           | urity          | stat           | us b           | yte            |

|---------|----------------------|---------|----------|----------------------------------------------|----------------|----------------|----------------|----------------|----------------|

| address |                      |         |          | b <sub>7</sub> b <sub>6</sub> b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| 0       | Protection: Standard | Read    | No Write | xxx                                          | 0              | 0              | 0              | 0              | 1              |

| 1       | Protection: Pswd 1   | Read    | No Write | xxx                                          | 0              | 1              | 0              | 0              | 1              |

| 2       | Protection: Pswd 1   | Read    | Write    | XXX                                          | 0              | 1              | 0              | 1              | 1              |

| 3       | Protection: Pswd 1   | No Read | No Write | xxx                                          | 0              | 1              | 1              | 0              | 1              |

| 4       | Protection: Pswd 1   | No Read | No Write | XXX                                          | 0              | 1              | 1              | 1              | 1              |

Table 12. M24LR64-R sector security protection after a valid presentation of password 1

| Sector  |                      |      |          | Sector                                       | secu           | ırity                 | stat           | us b           | yte            |

|---------|----------------------|------|----------|----------------------------------------------|----------------|-----------------------|----------------|----------------|----------------|

| address |                      |      |          | b <sub>7</sub> b <sub>6</sub> b <sub>5</sub> | b <sub>4</sub> | <b>b</b> <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| 0       | Protection: Standard | Read | No Write | XXX                                          | 0              | 0                     | 0              | 0              | 1              |

| 1       | Protection: Pswd 1   | Read | Write    | xxx                                          | 0              | 1                     | 0              | 0              | 1              |

| 2       | Protection: Pswd 1   | Read | Write    | xxx                                          | 0              | 1                     | 0              | 1              | 1              |

| 3       | Protection: Pswd 1   | Read | Write    | xxx                                          | 0              | 1                     | 1              | 0              | 1              |

| 4       | Protection: Pswd 1   | Read | No Write | xxx                                          | 0              | 1                     | 1              | 1              | 1              |

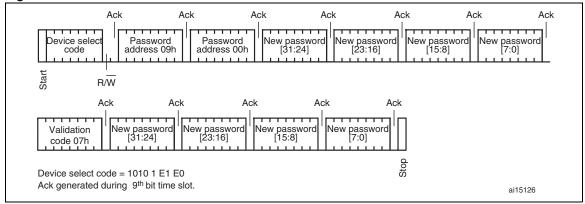

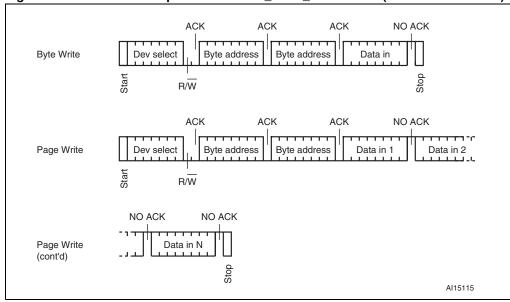

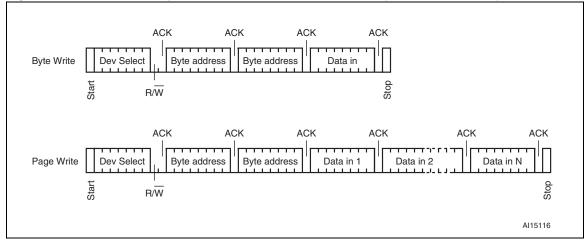

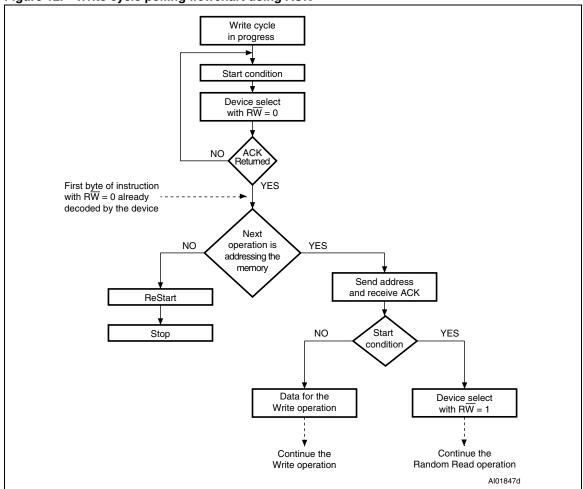

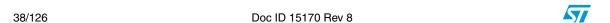

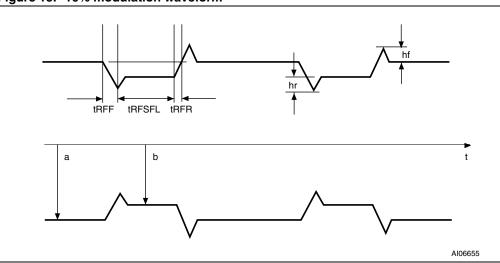

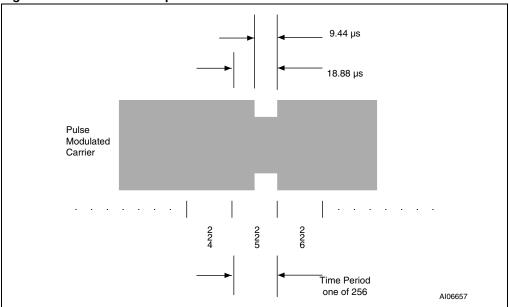

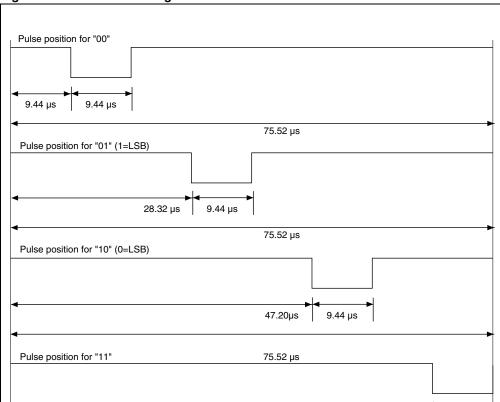

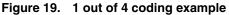

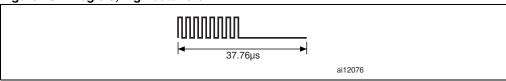

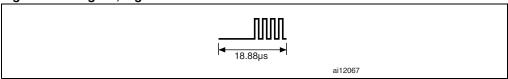

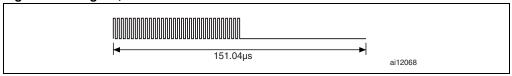

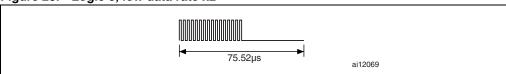

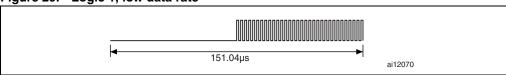

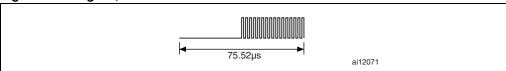

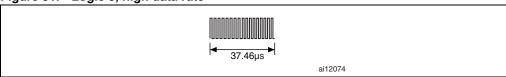

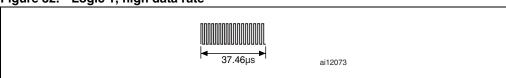

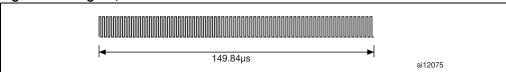

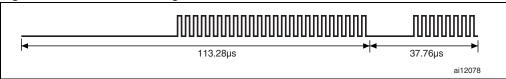

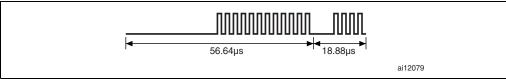

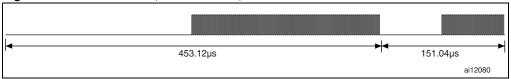

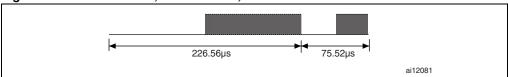

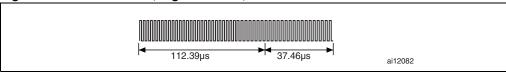

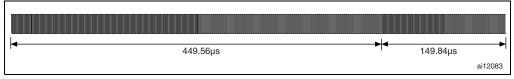

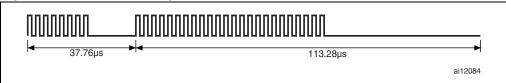

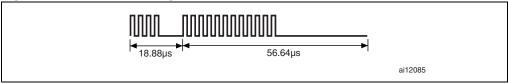

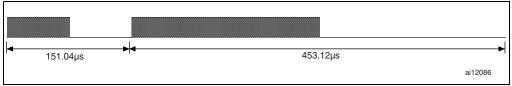

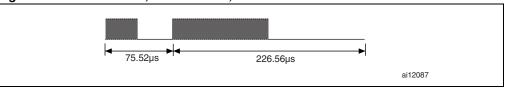

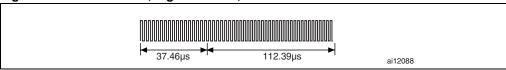

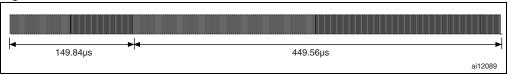

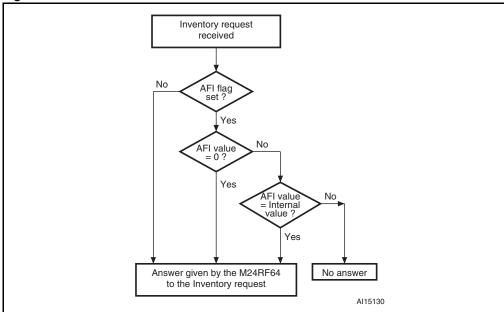

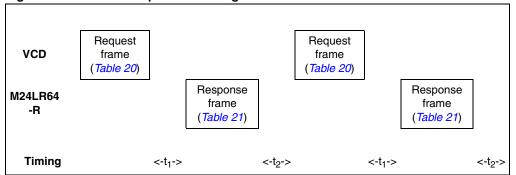

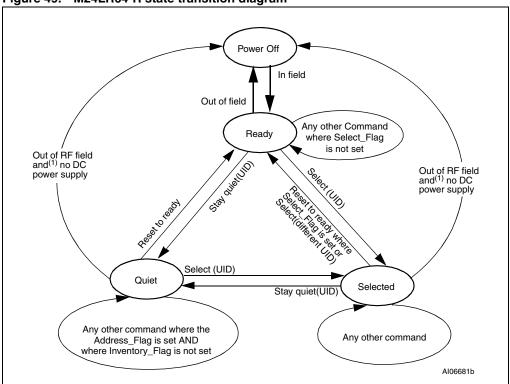

## 4.3 I2C\_Write\_Lock bit area