#### STEP-DOWN, BUILT-IN FET, SYNCHRONOUS S-8550/8551 Series **RECTIFICATION, PWM CONTROL SWITCHING REGULATORS**

1.2 MHz

600 mA

1 ms typ.

0.6 V ±2.0% 92%

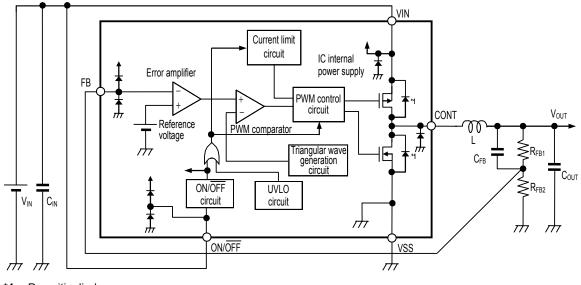

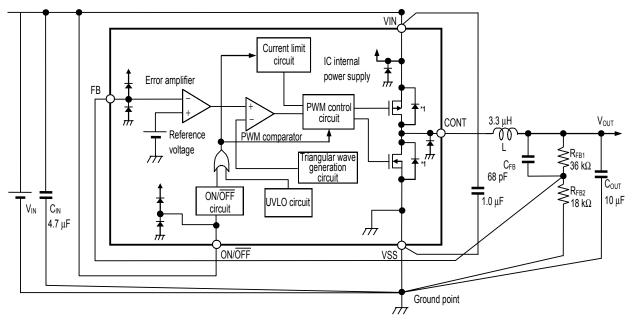

The S-8550/8551 Series is a CMOS synchronous rectification step-down switching regulator which mainly consists of a reference voltage circuit, an oscillator, an error amplifier, a phase compensation circuit, a PWM controller, an under voltage lockout circuit (UVLO), a current limit circuit, and a power MOS FET. The oscillation frequency is high at 1.2 MHz, so a high efficiency, large output current, step-down switching regulator can be achieved by using small external parts.

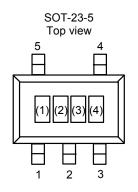

The built-in synchronous rectification circuit makes achieving high efficiency easier compared with conventional step-down switching regulators. A ceramic capacitor can be used as an output capacitor. High-density mounting is supported by adopting a small SOT-23-5 package.

The S-8550 and S-8551 Series are offered according to different pin configuration.

Shutdown current consumption : 1.0 µA max.

## Features

- Oscillation frequency :

- Input voltage range : 2.0 to 5.5 V

- Output voltage range : Arbitrarily settable by external output voltage setting resistor

- Output current :

- Reference voltage :

- Efficiency :

- Soft-start function :

- Shutdown function :

- Built-in current limit circuit

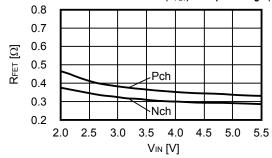

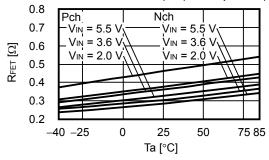

- Pch power MOS FET on-resistance : 0.4 Ω typ.

- Nch power MOS FET on-resistance : 0.3 Ω typ.

- Constant continuous mode operation (no light load mode) SOT-23-5

- Small package :

- Lead-free products

## Applications

· Mobile devices, such as mobile phones, Bluetooth devices, wireless devices, digital audio players, digital still cameras, portable DVD players, and portable CD players

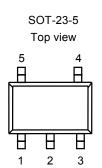

# Package

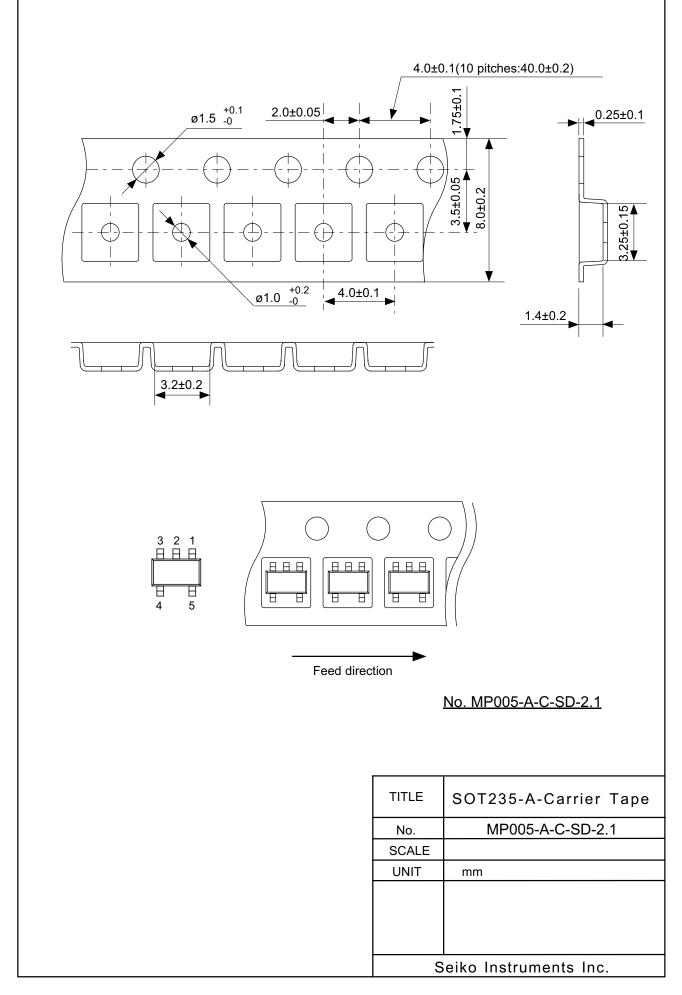

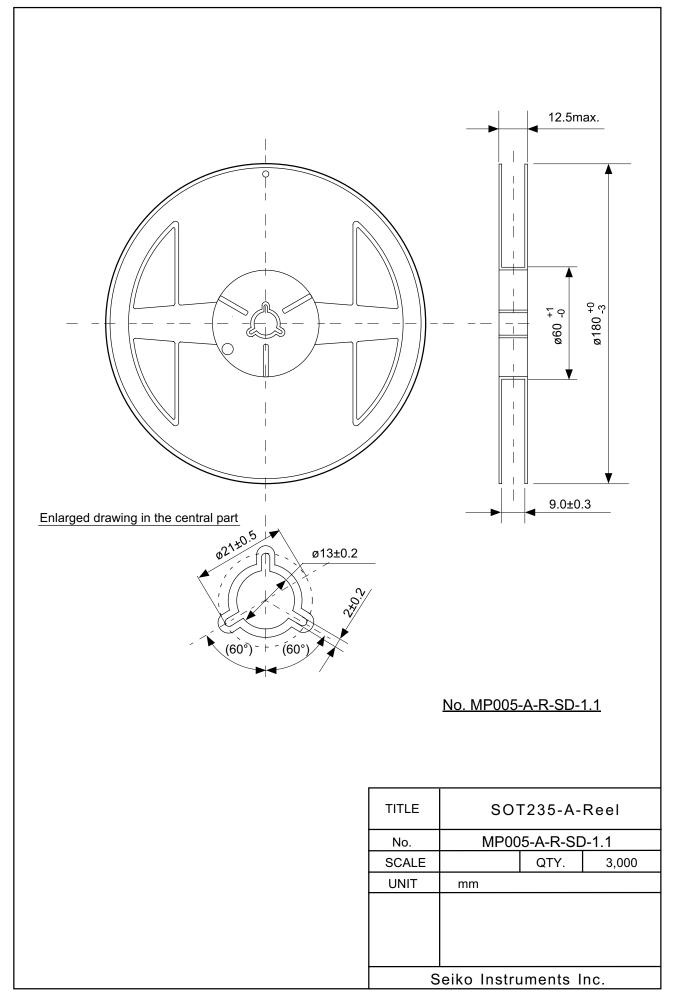

| Dookogo Nomo | Drawing Code |         |         |  |  |

|--------------|--------------|---------|---------|--|--|

| Package Name | Package      | Таре    | Reel    |  |  |

| SOT-23-5     | MP005-A      | MP005-A | MP005-A |  |  |

# Block Diagram

\*1. Parasitic diode

Figure 1

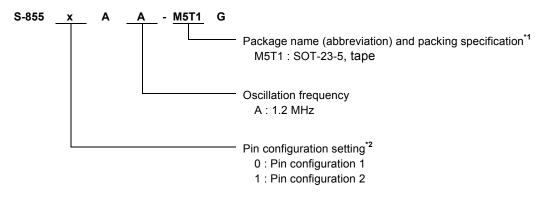

# Product Name Structure

**Product name**

- **\*1.** Refer to the taping specifications at the end of this book.

- \*2. Refer to Table 1 and Table 2 of "

Pin Configurations".

# ■ Pin Configurations

| Pin No. | Symbol | Description                                                                    |  |  |  |

|---------|--------|--------------------------------------------------------------------------------|--|--|--|

| 1       | VIN    | IC power supply pin                                                            |  |  |  |

| 2       | VSS    | GND pin                                                                        |  |  |  |

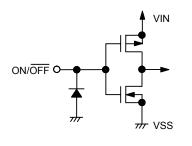

| 3       | ON/OFF | Shutdown pin<br>"H" : Power on (normal operation)<br>"L" : Power off (standby) |  |  |  |

| 4       | FB     | Output voltage feedback pin                                                    |  |  |  |

| 5       | CONT   | External inductor connection pin                                               |  |  |  |

## Table 1 S-8550 Series (Pin Configuration 1)

| Table 2 S-8551 Series (Pin Configuration 2) |        |                                   |  |  |  |

|---------------------------------------------|--------|-----------------------------------|--|--|--|

| Pin No.                                     | Symbol | Description                       |  |  |  |

|                                             |        | Shutdown pin                      |  |  |  |

| 1                                           | ON/OFF | "H" : Power on (normal operation) |  |  |  |

|                                             |        | "L" : Power off (standby)         |  |  |  |

| 2                                           | VSS    | GND pin                           |  |  |  |

| 3                                           | CONT   | External inductor connection pin  |  |  |  |

| 4                                           | VIN    | IC power supply pin               |  |  |  |

| 5                                           | FB     | Output voltage feedback pin       |  |  |  |

Figure 2

# Absolute Maximum Ratings

|                       |                   | (Unless otherwise specified: $Ta = 25^{\circ}$ | $C,V_{SS}=0\;V)$ |

|-----------------------|-------------------|------------------------------------------------|------------------|

| Parameter             | Symbol            | Absolute Maximum Rating                        | Unit             |

| VIN pin voltage       | V <sub>IN</sub>   | $V_{SS}$ – 0.3 to $V_{SS}$ + 6.0               | V                |

| FB pin voltage        | V <sub>FB</sub>   | $V_{SS}$ – 0.3 to $V_{IN}$ + 0.3               | V                |

| CONT pin voltage      | V <sub>CONT</sub> | $V_{SS} - 0.3$ to $V_{IN}$ + 0.3               | V                |

| ON/OFF pin voltage    |                   | $V_{SS}$ – 0.3 to $V_{IN}$ + 0.3               | V                |

| CONT pin current      | ICONT             | 1300                                           | mA               |

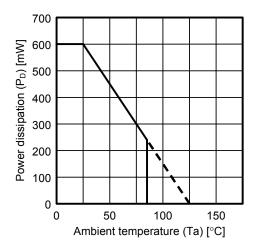

| Power dissipation     | PD                | 600 <sup>*1</sup>                              | mW               |

| Operating temperature | T <sub>opr</sub>  | -40 to +85                                     | °C               |

| Storage temperature   | T <sub>stg</sub>  | -40 to +125                                    | °C               |

#### Table 3 Absolute Maximum Ratings

\*1. When mounted on printed circuit board

[Mounted board]

(1) Board size: 114.3 mm × 76.2 mm × t1.6 mm

(2) Board name: JEDEC STANDARD51-7

- Caution 1. The absolute maximum ratings are rated values exceeding which the product could suffer physical damage. These values must therefore not be exceeded under any conditions.

- 2. Since this IC has a built-in power MOS FET, make sure that dissipation of the power MOS FET does not exceed the allowable power dissipation of the package. (Refer to Figure 3.) Generally, dissipation of a switching regulator can be calculated by the following equation. Dissipation = (100 (%) efficiency (%)) / efficiency (%) × output voltage × load current The greater part of dissipation depends on the built-in power MOS FET, however, dissipation of the inductor is also included.

In addition, since power dissipation of the package also changes according to a mounting board or a mounting state, fully check them using an actually mounted mode.

Figure 3 Power Dissipation of Package (Mounted on Board)

# Electrical Characteristics

| (Unless otherwise specified: $V_{IN} = 3.6$ V, $V_{OUT} = 1.8$ V (the conditions in Table 5), Ta = 25°C |                          |                                                                                                                                                            |       |       |       |        |                 |

|---------------------------------------------------------------------------------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|--------|-----------------|

| Parameter                                                                                               | Symbol                   | Conditions                                                                                                                                                 | Min.  | Тур.  | Max.  | Unit   | Test<br>Circuit |

| Operating input voltage                                                                                 | V <sub>IN</sub>          |                                                                                                                                                            | 2.0   |       | 5.5   | V      | 2               |

| Output voltage range <sup>*1</sup>                                                                      | V <sub>OUT</sub>         | $V_{IN} = V_{OUT(S)} + 0.4 V \text{ to } 5.5 V$                                                                                                            | 1.1   | —     | 4.0   | V      | 2               |

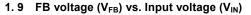

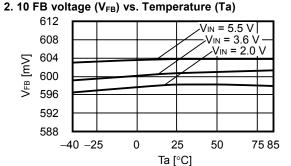

| FB voltage                                                                                              | $V_{\text{FB}}$          | $V_{IN} = V_{OUT(S)} + 0.4 V \text{ to } 5.5 V$                                                                                                            | 0.588 | 0.6   | 0.612 | V      | 2               |

| FB voltage temperature<br>coefficient                                                                   | _ΔV <sub>FB</sub><br>ΔTa | Ta = -40°C to +85°C                                                                                                                                        |       | ±100  | —     | ppm/°C | 2               |

| FB pin input current                                                                                    | I <sub>FB</sub>          | $V_{IN}$ = 2.0 V to 5.5 V, FB pin                                                                                                                          | -0.1  |       | +0.1  | μA     | 1               |

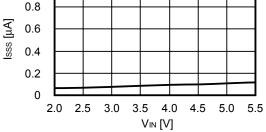

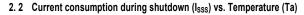

| Current consumption<br>during shutdown                                                                  | I <sub>SSS</sub>         | $V_{IN}$ = 2.0 V to 5.5 V,<br>VON/OFF = 0 V                                                                                                                | _     | _     | 1.0   | μΑ     | 1               |

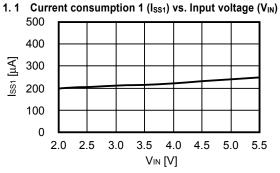

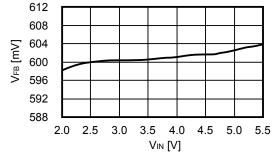

| Current consumption 1                                                                                   | I <sub>SS1</sub>         | $f_{osc}$ = 1.2 MHz, no external parts,<br>V <sub>FB</sub> = V <sub>FB(S)</sub> × 1.1 V                                                                    | _     | 200   | 400   | μA     | 1               |

| Power MOS FET                                                                                           | R <sub>PFET</sub>        | I <sub>CONT</sub> = 100 mA                                                                                                                                 | _     | 0.4   | 0.6   | 0      | 4               |

| on-resistance                                                                                           | R <sub>NFET</sub>        | I <sub>CONT</sub> = -100 mA                                                                                                                                |       | 0.3   | 0.5   | Ω      | 1               |

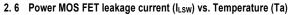

| Power MOS FET<br>leakage current                                                                        | I <sub>LSW</sub>         | $\label{eq:VIN} \begin{array}{l} V_{IN} = 2.0 \; V \; \text{to} \; 5.5 \; V, \\ V_{ON/OFF} = 0 \; V, \; V_{CONT} = 0 \; \text{or} \; 3.6 \; V \end{array}$ |       | ±0.01 | ±0.5  | μA     | 1               |

| Limit current                                                                                           | I <sub>LIM</sub>         | —                                                                                                                                                          | 800   | 1000  | 1200  | mA     | 1               |

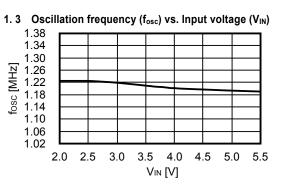

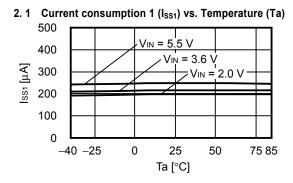

| Oscillation frequency                                                                                   | f <sub>osc</sub>         | —                                                                                                                                                          | 1.02  | 1.2   | 1.38  | MHz    | 2               |

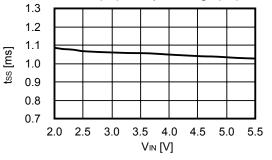

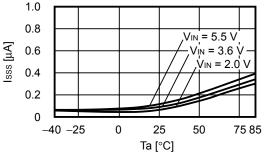

| Soft-start time                                                                                         | t <sub>ss</sub>          | Time required to reach 90% of $V_{OUT(S)}$                                                                                                                 | 0.7   | 1.0   | 1.3   | ms     | 2               |

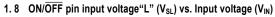

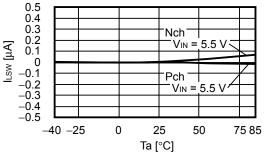

| High level input voltage                                                                                | $V_{SH}$                 | $V_{IN}$ = 2.0 V to 5.5 V, ON/ $\overline{OFF}$ pin                                                                                                        | 0.9   | _     | _     | V      | 2               |

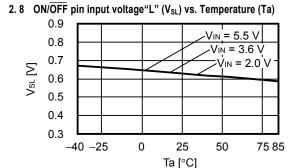

| Low level input voltage                                                                                 | $V_{SL}$                 | $V_{IN}$ = 2.0 V to 5.5 V, ON/ $\overline{OFF}$ pin                                                                                                        |       |       | 0.3   | V      | 2               |

| High level input current                                                                                | I <sub>SH</sub>          | $V_{IN}$ = 2.0 V to 5.5 V, ON/ $\overline{OFF}$ pin                                                                                                        | -0.1  |       | 0.1   | μΑ     | 1               |

| Low level input current                                                                                 | I <sub>SL</sub>          | $V_{IN}$ = 2.0 V to 5.5 V, ON/ $\overline{OFF}$ pin                                                                                                        | -0.1  |       | 0.1   | μΑ     | 1               |

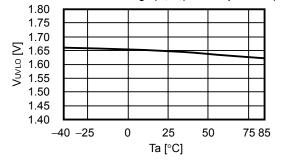

| UVLO detection voltage                                                                                  | $V_{UVLO}$               |                                                                                                                                                            | 1.4   | 1.6   | 1.78  | V      | 2               |

#### Table 4 Electrical Characteristics

\*1. V<sub>OUT(S)</sub> is the output voltage set value, and V<sub>OUT</sub> is the typ. value of the actual output voltage.

V<sub>OUT(S)</sub> can be set depending on the ratio between the V<sub>FB</sub> value and output voltage set resistors (R<sub>FB1</sub>, R<sub>FB2</sub>).

For details, refer to "■ External Parts Selection".

# ■ External Parts When Measuring Electrical Characteristics

### Table 5 External Parts

| Element Name                  | Symbol           | Constant | Manufacturer                   | Part Number       |

|-------------------------------|------------------|----------|--------------------------------|-------------------|

| Inductor                      | L                | 3.3 μH   | Taiyo Yuden Co., Ltd.          | NR4018T3R3M       |

| Input capacitor               | CIN              | 4.7 μF   | TDK Corporation                | C3216X7R1E475K    |

| Output capacitor              | COUT             | 10 μF    | TDK Corporation                | C3216X7R1C106K    |

| Output voltage set resistor 1 | R <sub>FB1</sub> | 36 kΩ    | Rohm Co., Ltd.                 | MCR03 Series 3602 |

| Output voltage set resistor 2 | $R_{FB2}$        | 18 kΩ    | Rohm Co., Ltd.                 | MCR03 Series 1802 |

| Phase compensation capacitor  | C <sub>FB</sub>  | 68 pF    | Murata Manufacturing Co., Ltd. | GRM1882C1H680J    |

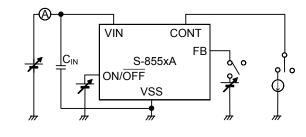

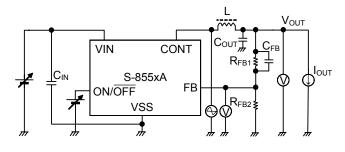

# Test Circuits

1.

2.

Figure 5

# Operation

### 1. Synchronous rectification PWM control step-down switching regulator

#### 1.1 Synchronous rectification

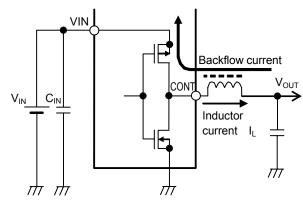

The synchronous rectification method lowers voltage drop to greatly reduce power dissipation since an Nch power MOS FET, having resistance much lower than conventional switching regulators, is used.

In conventional switching regulators, current flows in the diode connected between the GND and CONT pins when the Pch power MOS FET is off. The forward drop voltage ( $V_f$ ) of such diodes is large, between 0.3 to 0.7 V, so the power dissipation used to be very large. Synchronous rectification ultra-low resistance Nch transistors repeat on and off, in synchronization with the operation of the Pch driver, in the reverse cycle of the Pch driver. Moreover, the built-in P and N through prevention circuit helps much reduction of power consumption during operation.

### 1.2 PWM control

The S-8550/8551 Series is a switching regulator using a pulse width modulation method (PWM) and features low current consumption.

In conventional PWM control switching regulators, pulses are skipped when the output load current is low, causing a fluctuation in the ripple frequency of the output voltage, resulting in an increase in the ripple voltage.

In the S-8550/8551 Series, the switching frequency does not change, although the pulse width changes from 0 to 100% corresponding to each load current. The ripple voltage generated from switching can thus be removed easily using a filter because the switching frequency is constant.

#### 2. Soft-start function

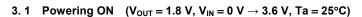

The soft-start circuit built in the S-8550/8551 Series controls the rush current and the overshoot of the output voltage when powering on, the  $ON/\overline{OFF}$  pin is switched from the "L" level to the "H" level, or the UVLO operation is released. A reference voltage adjustment method is adopted as the soft-start method.

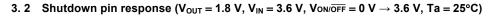

#### 3. Shutdown pin

This pin stops or starts step-up operations.

Switching the shutdown pin to the "L" level stops operation of all the internal circuits and reduces the current consumption significantly. DO NOT use the shutdown pin in a floating state because it is not pulled up or pulled down internally. DO NOT apply voltage of between 0.3 and 0.9 V to the shutdown pin because applying such a voltage increases the current consumption. If the shutdown pin is not used, connect it to the VIN pin.

|              | Table 6                |                |

|--------------|------------------------|----------------|

| Shutdown Pin | CR Oscillation Circuit | Output Voltage |

| "H"          | Operates               | Set value      |

| "L"          | Stops                  | Hi-Z           |

### 4. Current limit circuit

A current limit circuit is built in the S-8550/8551 Series.

The current limit circuit monitors the current that flows in the Pch power MOS FET and limits current in order to prevent thermal destruction of the IC due to an overload or magnetic saturation of the inductor.

When a current exceeding the current limit detection value flows in the Pch power MOS FET, the current limit circuit operates and turns off the Pch power MOS FET since the current limit detection until one clock of the oscillator ends. The Pch power MOS FET is turned on in the next clock and the current limit circuit resumes current detection operation. If the value of the current that flows in the Pch power MOS FET remains the current limit detection value or more, the current limit circuit functions again and the same operation is repeated. Once the value of the current that flows in the Pch power MOS FET is lowered up to the specified value, the normal operation status restores. A slight overshoot is generated in the output voltage when the current limit is released.

The current limit detection value is fixed to 1 A (typ.) in the IC. If the time taken for the current limit to be detected is shorter than the time required for the current limit circuit in the IC to detect, the current value that is actually limited increases. Generally, the voltage difference between the VIN and VOUT pins is large, the current limit detection status is reached faster and the current value increases.

#### 5. 100% duty cycle

The S-8550/8551 Series operates up to the maximum duty cycle at 100%. Even when the input voltage is lowered up to the output voltage value set using the external output voltage setting resistor, the Pch power MOS FET is kept on and current can be supplied to the load. The output voltage at this time is the input voltage from which the voltage drop due to the direct resistance of the inductor and the on-resistance of the Pch power MOS FET are subtracted.

#### 6. UVLO function

The S-8550/8551 Series includes a UVLO (under-voltage lockout) circuit to prevent the IC from malfunctioning due to a transient status when power is applied or a momentary drop of the supply voltage. When UVLO is in the detection state, the Pch and Nch power MOS FETs stop switching operation, and the CONT pin become Hi-Z. Once the S-8550/8551 is in the UVLO detection status, the soft-start function is reset, but the soft-start operates by the releasing operation of UVLO after that.

Note that the other internal circuits operate normally and that the status is different from the power-off status. The hysteresis width is set for the UVLO circuit to prevent a malfunction due to a noise that is generated in the input voltage. A voltage about 150 mV (typ.) higher than the UVLO detection voltage is the release voltage.

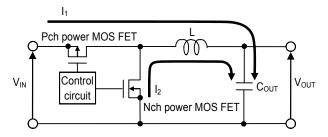

## Operation Principle

The S-8550/8551 Series is a step-down synchronous rectification switching regulator based on constant PWM control. **Figure 7** shows the basic circuit diagram.

A step-down switching regulator starts current supply by the input voltage ( $V_{IN}$ ) when the Pch power MOS FET is turned on and holds energy in the inductor at the same time. When the Pch power MOS FET is turned off, the current held in the inductor is released. The released current flows in the smoothing circuit, with the energy loss held minimum, supplies the output voltage ( $V_{OUT}$ ) lower than  $V_{IN}$ .  $V_{OUT}$  is kept constant by controlling the switching frequency ( $f_{osc}$ ) and ON time ( $t_{on}$ ). With the PWM control method,  $V_{OUT}$  is made constant by controlling the ON time with  $f_{OSC}$  unchanged.

Figure 7 Basic Circuit Drawing of Step-down Switching Regulator

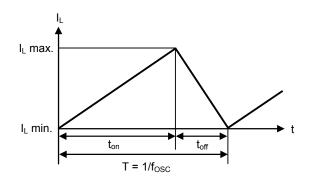

#### 1. Continuous mode

The following explains how the current flows to the inductor when the step-down operation is constant and stable.

When the Pch power MOS FET is turned on, current  $I_1$  flows in the direction shown by the arrow in **Figure 7**, and energy is stored in the inductor (L). When the output capacitor ( $C_{OUT}$ ) is charged, supply of the output current ( $I_{OUT}$ ) is started at the same time. The inductor current ( $I_L$ ) gradually increases in proportion to the ON time ( $t_{ON}$ ) of the Pch power MOS FET as shown in **Figure 8** (changes from  $I_L$  min. to  $I_L$  max.). When the Pch power MOS FET is turned off, the Nch power MOS FET is turned on and  $I_L$  tries to hold  $I_L$  max. Consequently, current  $I_2$  flows in the direction shown by the arrow in **Figure 7**. As a result,  $I_L$  gradually decreases and reaches  $I_L$  min. when the OFF time ( $t_{OFF}$ ) has elapsed. When  $t_{OFF}$  has elapsed, the Nch power MOS FET is turned off and the next cycle is entered. The above sequence is repeated.

As explained in the above, the continuous mode refers to the operation in the current cycle in which  $I_L$  linearly changes from  $I_L$  min. to  $I_L$  max. Even if  $I_L$  min. is less than 0 A,  $I_L$  min. keeps flowing (backflow current flows).

Figure 8 Continuous Mode (Current Cycle of Inductor Current (IL))

Seiko Instruments Inc.

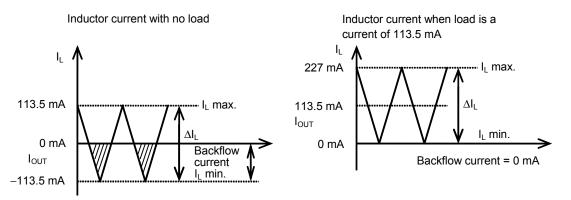

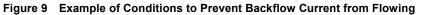

#### 2. Backflow current

The S-8550/8551 Series performs PWM synchronous rectification even if  $I_L$  min. is less than 0 A, so a backflow current is generated in  $V_{IN}$  and the backflow current becomes maximum when no load is applied (see **Figure 9**). Use the following equation to calculate the maximum backflow current value, which should be taken into consideration when designing.

$\begin{array}{l} \text{Duty} \ (I_{\text{OUT}}=0) = V_{\text{OUT}} \ / \ V_{\text{IN}} \\ & \text{Example} : V_{\text{IN}} = 3.6 \ \text{V}, \ V_{\text{OUT}} = 1.8 \ \text{V} \ \dots \ \text{Duty} = 50\% \\ \Delta I_L = \Delta V \ / \ L \times t_{\text{on}} = (V_{\text{IN}} - V_{\text{OUT}}) \times \text{Duty} \ / \ (L \times f_{\text{OSC}}) \\ & \text{Example} : V_{\text{IN}} = 3.6 \ \text{V}, \ V_{\text{OUT}} = 1.8 \ \text{V}, \ f_{\text{OSC}} = 1.2 \ \text{MHz}, \ L = 3.3 \ \mu\text{H} \ \dots \ \Delta I_L = 227 \ \text{mA} \\ I_L \ \text{max.} = \Delta I_L \ / \ 2 = 113.5 \ \text{mA}, \ I_L \ \text{min.} = -\Delta I_L \ / \ 2 = -113.5 \ \text{mA} \end{array}$

The current value waveform of the inductor is a triangular wave, of which the maximum value is  $I_{L}$  max. and the minimum value is  $I_{L}$  min. (negative value), and the negative value (the portion marked by diagonal lines in **Figure 9**) backflows when no load is applied (see **Figure 9**).

If about 113.5 mA of  $I_{OUT}$  flows in the above conditions, the minimum value ( $I_L$  min.) of the triangular wave is made 0 mA and no backflow current flows.

When an input capacitor ( $C_{IN}$ ) is connected, the backflow current is absorbed by  $C_{IN}$ , thus reducing the backflow current to flow in the power supply. Be sure to connect an input capacitor to reduce backflow current to the power supply (see **Figure 10**).

The above presents the conditions required to prevent backflow current from flowing, which is only a guideline. Perform sufficient confirmation using an actual application.

Figure 10 Backflow Current

Seiko Instruments Inc.

# External Parts Selection

## 1. Inductor

The inductance (L value) has a strong influence on the maximum output current ( $I_{OUT}$ ) and efficiency ( $\eta$ ). The peak current ( $I_{PK}$ ) increases by decreasing L and the stability of the circuit improves and  $I_{OUT}$  increases. If L is decreased further, the current drive capability of the external transistor is insufficient and  $I_{OUT}$  decreases. If the L value is increased, the loss due to  $I_{PK}$  of the power MOS FET decreases and the efficiency becomes maximum at a certain L value. Further increasing L decreases the efficiency due to the increased loss of the DC resistance of the inductor.

The recommended L value for the S-8550/8551 Series is 3.3  $\mu\text{H}.$

When selecting an inductor, note the allowable current of the inductor. If a current exceeding this allowable current flows through the inductor, magnetic saturation occurs, substantially lowering the efficiency.

Therefore, select an inductor so that  $I_{PK}$  does not exceed the allowable current.  $I_{PK}$  is expressed by the following equations in the discontinuous mode and continuous mode.

$$I_{PK} = I_{OUT} + \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{2 \times f_{OSC} \times L \times V_{IN}}$$

$f_{\text{OSC}} = \text{Oscillation frequency}$

|                       |                 | 21      |                       |               |                                         |

|-----------------------|-----------------|---------|-----------------------|---------------|-----------------------------------------|

| Manufacturer          | Part Number     | L Value | DC<br>Resistance      | Rated Current | Dimensions $(L \times W \times H)$ [mm] |

| Taiyo Yuden Co., Ltd. | NR4018T3R3M     | 3.3 μΗ  | $0.07~\Omega$ max.    | 1.23 A max.   | $4.0\times4.0\times1.8$                 |

|                       | NR3012T3R3M     | 3.3 μH  | $0.1 \Omega$ max.     | 0.91 A max.   | $3.0\times3.0\times1.2$                 |

| Sumida Corporation    | CDRH3D16/HP-3R3 | 3.3 μΗ  | $0.085 \ \Omega$ max. | 1.40 A max.   | $4.0\times4.0\times1.8$                 |

|                       | CDRH2D11/HP-3R3 | 3.3 μΗ  | $0.173 \ \Omega$ max. | 0.9 A max.    | $3.2\times3.2\times1.2$                 |

| TDK Corporation       | VLF4012AT-3R3M  | 3.3 μΗ  | $0.12 \ \Omega$ max.  | 1.3 A max.    | $3.7\times3.5\times1.2$                 |

|                       | VLF3010AT-3R3M  | 3.3 μΗ  | $0.17~\Omega$ max.    | 0.87 A max.   | $2.6\times2.8\times1.0$                 |

| FDK Corporation       | MIP3226D3R3M    | 3.3 μΗ  | $0.104 \ \Omega$ max. | 1.2 A max.    | $3.2\times2.6\times1.0$                 |

|                       | MIPS2520D3R3M   | 3.3 μΗ  | 0.156 Ω max.          | 1.0 A max.    | $2.5 \times 2.0 \times 1.0$             |

| Table 7 | Typical | Inductors |

|---------|---------|-----------|

|---------|---------|-----------|

## 2. Capacitors (C<sub>IN</sub>, C<sub>OUT</sub>)

A ceramic capacitor can be used for the input ( $C_{IN}$ ) and output ( $C_{OUT}$ ) sides.  $C_{IN}$  lowers the power supply impedance and averages the input current to improve efficiency. Select  $C_{IN}$  according to the impedance of the power supply to be used. The recommended capacitance is 4.7  $\mu$ F for the S-8550/8551 Series when a general lithium ion rechargeable battery is used.

Select as  $C_{OUT}$  a capacitor with large capacitance and small ESR for smoothing the ripple voltage. The optimum capacitor selection depends on the L value, capacitance value, wiring, and application (output load). Select  $C_{OUT}$  after sufficient evaluation under actual use conditions.

#### 3. Output voltage setting resistors (R<sub>FB1</sub>, R<sub>FB2</sub>), capacitor for phase compensation (C<sub>FB</sub>)

With the S-8550/8551 Series,  $V_{OUT}$  can be set to any value by external divider resistors. Connect the divider resistors across the VOUT and VSS pins. Because  $V_{FB} = 0.6$  V typ.,  $V_{OUT}$  can be calculated by this equation.

$$V_{OUT} = \frac{(R_{FB1} + R_{FB2})}{R_{FB2}} \times 0.6$$

Connect divider resistors  $R_{FB1}$  and  $R_{FB2}$  as close to the IC to minimize effects from of noise. If noise does have an effect, adjust the values of  $R_{FB1}$  and  $R_{FB2}$  so that  $R_{FB1} + R_{FB2} < 100 \text{ k}\Omega$ .

C<sub>FB</sub> connected in parallel with R<sub>FB1</sub> is a capacitor for phase compensation.

By setting the zero point (the phase feedback) by adding capacitor  $C_{FB}$  to output voltage setting resistor  $R_{FB1}$  in parallel, the feedback loop gains the phase margin. As a result, the stability can be obtained. In principle, to use the portion how much the phase has feed back by the zero point effectively, define  $C_{FB}$  referring to the following equation.

$$C_{FB} \cong \frac{1}{2 \ x \ \pi \ x \ R_{FB1} \ x \ 70 \ kHz}$$

This equation is the reference.

The followings are explanation regarding the proper setting.

To use the portion how much the phase has feed back by the zero point effectively, set  $R_{FB1}$  and  $C_{FB}$  so that the zero point goes into the higher frequency than the pole frequency of L and  $C_{OUT}$ . The following equations are the pole frequency of L and  $C_{OUT}$  and the zero point frequency by  $C_{FB}$  and  $R_{FB1}$ .

$$\begin{split} f_{\text{pole}} &\cong \frac{1}{2 \; x \; \pi \; x \; \sqrt{L \; x \; \text{Cout}}} \\ f_{\text{zero}} &\cong \frac{1}{2 \; x \; \pi \; x \; \text{RFB1} \; x \; \text{CFB}} \end{split}$$

The transient response can be improved by setting the zero point frequency in the range of lower frequency. However, since the gain becomes higher in the range of high frequency, the total phase of feedback loop delays  $180^{\circ}$  or more by setting the zero point frequency in the significantly lower range. As a result, the gain cannot be 0 dB or lower in the frequency range thus the operation might be unstable. Determine the proper value after the sufficient evaluation under the actual condition.

The typical constants by our evaluation are in Table 8.

Table 8 Constant for External Parts

| V <sub>OUT</sub> (s) [V] | R <sub>FB1</sub> [kΩ] | R <sub>FB2</sub> [kΩ] | С <sub>ғв</sub> [рF] | L [μH] <sup>*1</sup> | С <sub>ОUT</sub> [μF] <sup>*1</sup> |

|--------------------------|-----------------------|-----------------------|----------------------|----------------------|-------------------------------------|

| 1.1                      | 36                    | 43                    | 56                   | 3.3                  | 10                                  |

| 1.8                      | 36                    | 18                    | 68                   | 3.3                  | 10                                  |

| 3.3                      | 36                    | 8                     | 120                  | 3.3                  | 10                                  |

| 4.0                      | 51                    | 9                     | 100                  | 3.3                  | 10                                  |

\*1. The recommended parts in Table 5

Seiko Instruments Inc.

#### STEP-DOWN, BUILT-IN FET, SYNCHRONOUS RECTIFICATION, PWM CONTROL SWITCHING REGULATORS S-8550/8551 Series Rev.2.1\_01

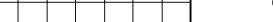

# Standard Circuit

**\*1.** Parasitic diode

#### Figure 11

Caution The above connection diagram and constant will not guarantee successful operation. Perform thorough evaluation using an actual application to set the constants.

## Precaution

- Mount external capacitors, diodes, and inductor as close as possible to the IC.

- Characteristics ripple voltage and spike noise occur in IC containing switching regulators. Moreover rush current flows at the time of a power supply injection. Because these largely depend on the inductor, the capacitor and impedance of power supply used, fully check them using an actually mounted model.

- The 1.0 µF capacitance connected between the VIN and VSS pins is a bypass capacitor. It stabilizes the power supply in the IC when application is used with a heavy load, and thus effectively works for stable switching regulator operation. Allocate the bypass capacitor as close to the IC as possible, prioritized over other parts.

- Although the IC contains a static electricity protection circuit, static electricity or voltage that exceeds the limit of the protection circuit should not be applied.

- The power dissipation of the IC greatly varies depending on the size and material of the board to be connected. Perform sufficient evaluation using an actual application before designing.

- Seiko Instruments Inc. assumes no responsibility for the way in which this IC is used on products created using this IC or for the specifications of that product, nor does Seiko Instruments Inc. assume any responsibility for any infringement of patents or copyrights by products that include this IC either in Japan or in other countries.

14

# Characteristics (Typical Data)

1.0

1.2 Current consumption during shutdown (Isss) vs. Input voltage (VIN)

1. 4 Soft-start time (tss) vs. Input voltage (VIN)

1. 5 Power MOS FET on-resistance (R<sub>FET</sub>) vs. Input voltage (V<sub>IN</sub>)

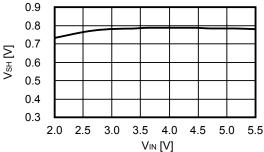

1.7 ON/OFF pin input voltage"H" (V<sub>SH</sub>) vs. Input voltage (V<sub>IN</sub>)

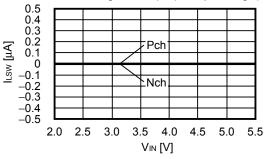

1. 6 Power MOS FET leakage current (I<sub>LSW</sub>) vs. Input voltage (V<sub>IN</sub>)

#### 2. Example of Major Temperature Characteristics (Ta = -40 to 85°C)

2. 5 Power MOS FET on-resistance (R<sub>FET</sub>) vs. Temperature (Ta)

2. 4 Soft-start time (t<sub>ss</sub>) vs. Temperature (Ta)

2. 9 UVLO detection voltage (V<sub>UVLO</sub>) vs. Temperature (Ta)

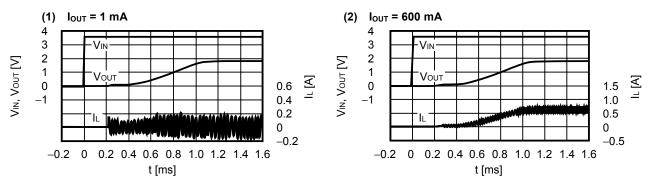

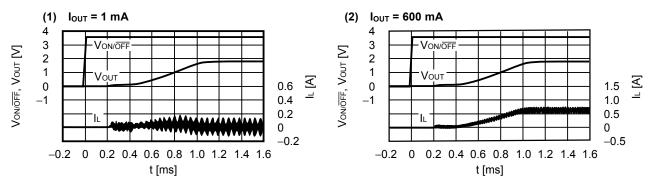

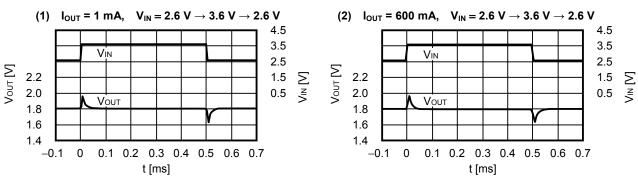

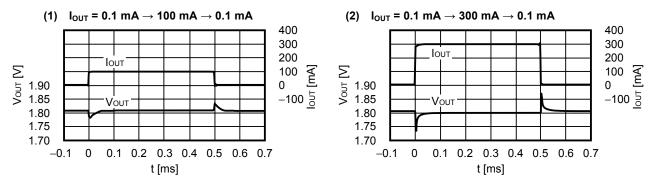

# 3. Examples of Transient Response Characteristics (Unless otherwise specified, the used parts are ones shown in ■ External Parts When Measuring Electrical Characteristics.)

Seiko Instruments Inc.

#### STEP-DOWN, BUILT-IN FET, SYNCHRONOUS RECTIFICATION, PWM CONTROL SWITCHING REGULATORS S-8550/8551 Series Rev.2.1\_01

3. 3 Power supply fluctuations ( $V_{OUT} = 1.8 V$ , Ta = 25°C)

3.4 Load fluctuations ( $V_{OUT} = 1.8 \text{ V}$ ,  $V_{IN} = 3.6 \text{ V}$ ,  $Ta = 25^{\circ}C$ )

# Reference Data

### 1. Reference data for external parts

| Element Name     | Product Name   | Manufacture          | Characteristics                                                             |

|------------------|----------------|----------------------|-----------------------------------------------------------------------------|

| Inductor         | NR4018T3R3M    | Taiyo Yuden Co., Ltd | 3.3 $\mu$ H, DCR <sub>MAX</sub> = 0.07 $\Omega$ , I <sub>MAX</sub> = 1.23 A |

| Input capacitor  | C3216X7R1E475K | TDK Corporation      | 4.7 μF                                                                      |

| Output capacitor | C3216X7R1C106K | TDK Corporation      | 10 μF                                                                       |

Caution The values of the external parts are based on the materials provided by each manufacturer. However, consider the characteristics of the original materials when using the above products.

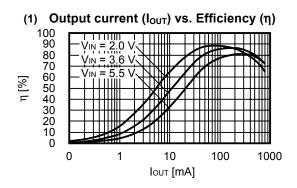

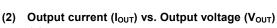

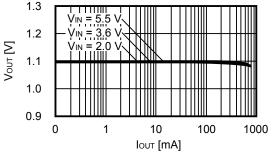

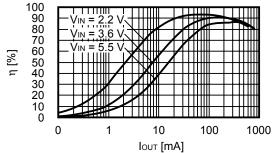

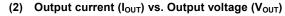

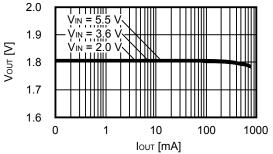

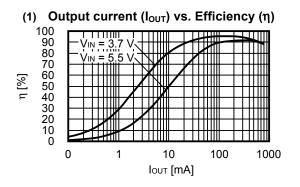

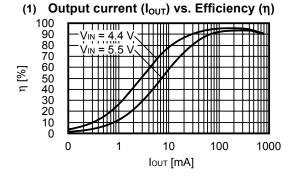

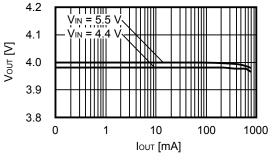

2. Output current (IOUT) vs. Efficiency (η) Characteristics and Output current (IOUT) vs. Output voltage (VOUT) Characteristics

2. 1  $V_{OUT} = 1.1 V (R_{FB1} = 36 k\Omega, R_{FB2} = 43 k\Omega)$

2. 2  $V_{OUT} = 1.8 \text{ V} (R_{FB1} = 36 \text{ k}\Omega, R_{FB2} = 18 \text{ k}\Omega)$

2. 3  $V_{OUT} = 3.3 V (R_{FB1} = 36 k\Omega, R_{FB2} = 8 k\Omega)$

2. 4  $V_{OUT} = 4.0 V (R_{FB1} = 51 k\Omega, R_{FB2} = 9 k\Omega)$

(2) Output current (I<sub>OUT</sub>) vs. Output voltage (V<sub>OUT</sub>) 3.5 3.4 3.3 3.2 3.1 0 1 10 100100

(2) Output current ( $I_{OUT}$ ) vs. Output voltage ( $V_{OUT}$ )

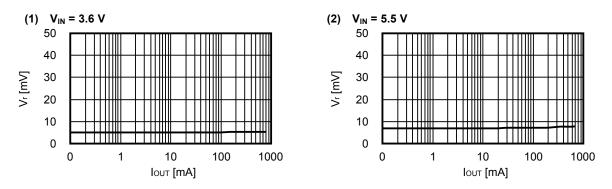

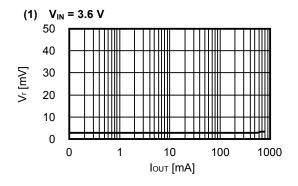

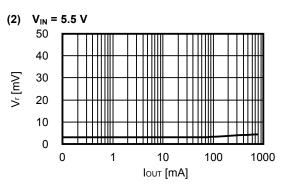

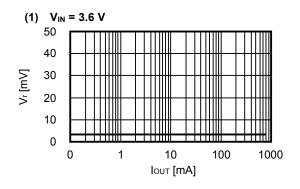

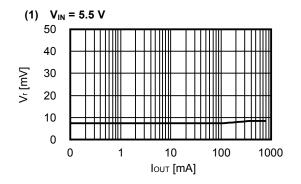

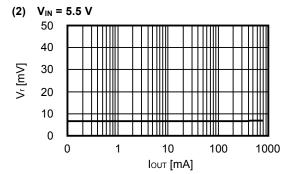

3. Output current (I<sub>OUT</sub>) vs. Ripple voltage (V<sub>r</sub>) Characteristics

3. 1  $V_{OUT} = 1.1 V (R_{FB1} = 36 k\Omega, R_{FB2} = 43 k\Omega)$

3. 2  $V_{OUT} = 1.8 \text{ V} (R_{FB1} = 36 \text{ k}\Omega, R_{FB2} = 18 \text{ k}\Omega)$

3. 3  $V_{OUT} = 3.3 V (R_{FB1} = 36 k\Omega, R_{FB2} = 8 k\Omega)$

3. 4  $V_{OUT} = 4.0 V (R_{FB1} = 51 k\Omega, R_{FB2} = 9 k\Omega)$

# Marking Specification

(1) SOT-23-5

(1) to (3) : (4) :

Product code (Refer to **Product name vs. Product code**.) Lot number

#### Product name vs. Product code

#### (a) S-8550 Series

| Product Name   | Product Code |     |     |

|----------------|--------------|-----|-----|

|                | (1)          | (2) | (3) |

| S-8550AA-M5T1G | R            | 5   | Α   |

#### (b) S-8551 Series

| Product Name   | Product Code |     |     |

|----------------|--------------|-----|-----|

| i loddot Name  | (1)          | (2) | (3) |

| S-8551AA-M5T1G | R            | 5   | С   |

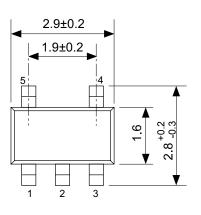

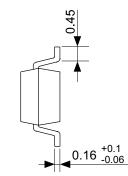

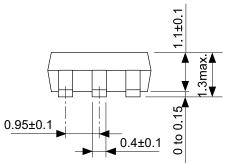

# No. MP005-A-P-SD-1.2

| TITLE | SOT235-A-PKG Dimensions |  |  |

|-------|-------------------------|--|--|

| No.   | MP005-A-P-SD-1.2        |  |  |

| SCALE |                         |  |  |

| UNIT  | mm                      |  |  |

|       |                         |  |  |

|       |                         |  |  |

|       |                         |  |  |

|       |                         |  |  |

| S     | Seiko Instruments Inc.  |  |  |

- The information described herein is subject to change without notice.

- Seiko Instruments Inc. is not responsible for any problems caused by circuits or diagrams described herein whose related industrial properties, patents, or other rights belong to third parties. The application circuit examples explain typical applications of the products, and do not guarantee the success of any specific mass-production design.

- When the products described herein are regulated products subject to the Wassenaar Arrangement or other agreements, they may not be exported without authorization from the appropriate governmental authority.

- Use of the information described herein for other purposes and/or reproduction or copying without the express permission of Seiko Instruments Inc. is strictly prohibited.

- The products described herein cannot be used as part of any device or equipment affecting the human body, such as exercise equipment, medical equipment, security systems, gas equipment, or any apparatus installed in airplanes and other vehicles, without prior written permission of Seiko Instruments Inc.

- Although Seiko Instruments Inc. exerts the greatest possible effort to ensure high quality and reliability, the failure or malfunction of semiconductor products may occur. The user of these products should therefore give thorough consideration to safety design, including redundancy, fire-prevention measures, and malfunction prevention, to prevent any accidents, fires, or community damage that may ensue.