# 300V, 64-Channel Serial to Parallel Converter with High Voltage Push-Pull Outputs

#### **Ordering Information**

|        |                                            | Package Options             |        |  |  |  |

|--------|--------------------------------------------|-----------------------------|--------|--|--|--|

| Device | Recommended Operating V <sub>PP</sub> Max* | 80-Lead Plastic<br>Gullwing | Die    |  |  |  |

| HV507  | 300V                                       | HV507PG                     | HV507X |  |  |  |

<sup>\*</sup> Please consult factory for higher voltage operation.

#### **Features**

- □ HVCMOS® technology

- Operating output voltage of 300V

- Low power level shifting from 5V to 300V

- ☐ Shift register speed 8MHz @ V<sub>DD</sub> = 5V

- ☐ 64 latched data outputs

- Output polarity and blanking

- CMOS compatible inputs

- Forward and reverse shifting options

#### Absolute Maximum Ratings<sup>1</sup>

| pply voltage, V <sub>DD</sub>                                                                          | -0.5V to +6V                               |

|--------------------------------------------------------------------------------------------------------|--------------------------------------------|

| pply voltage, V <sub>PP</sub>                                                                          | V <sub>DD</sub> to 320V                    |

| ic input levels                                                                                        | -0.5V to V <sub>DD</sub> +0.5V             |

| ound current <sup>3</sup>                                                                              | 0.5A                                       |

| h voltage supply current <sup>2</sup>                                                                  | 0.5A                                       |

| ntinuous total power dissipation                                                                       | <sup>3</sup> 1200mW                        |

| erating temperature range                                                                              | 0°C to +70°C                               |

| rage temperature range                                                                                 | -65°C to +150°C                            |

| h voltage supply current <sup>2</sup><br>ntinuous total power dissipation<br>erating temperature range | 0.5<br>3 1200m <sup>1</sup><br>0°C to +70° |

#### Notes:

- 1. All voltages are referenced to GND.

- Connection to all power and ground pads is required. Duty cycle is limited by the total power dissipated in the package.

- 3. For operation above 25°C ambient derate linearly to 70°C at 26.7mW/°C.

#### **General Description**

The HV507 is a low voltage serial to high voltage parallel converter with 64 high voltage push-pull outputs. This device has been designed for use as a printer driver for electrostatic applications. It can also be used in any application requiring multiple high voltage outputs, low current sourcing and sinking capabilities.

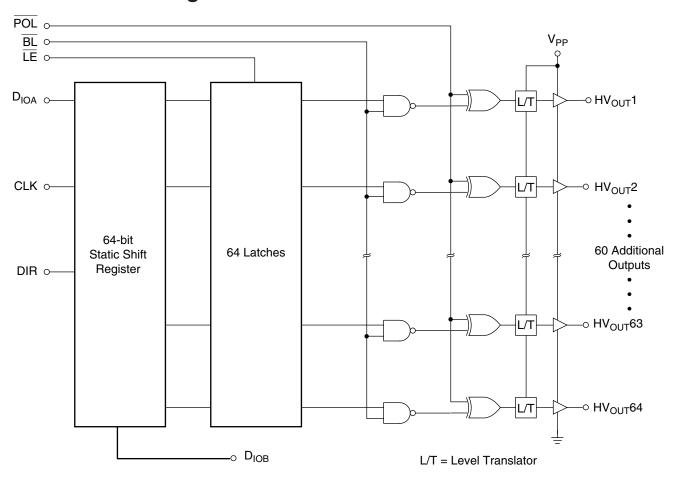

The device consists of a 64-bit shift register, 64 latches, and control logic to perform the polarity select and blanking of the outputs. A DIR pin controls the direction of data shift through the device. With DIR grounded,  $D_{IOA}$  is Data In and  $D_{IOB}$  is Data Out; data is shifted from  $HV_{OUT}64$  to  $HV_{OUT}1$ . When DIR is at logic high,  $D_{IOB}$  is Data In and  $D_{IOA}$  is Data Out: data is then shifted from  $HV_{OUT}1$  to  $HV_{OUT}64$ . Data is shifted through the shift register on the low to high transition of the clock. Data output buffers are provided for cascading devices. Operation of the shift register is not affected by the  $\overline{LE}$ ,  $\overline{BL}$ , or the  $\overline{POL}$  inputs. Transfer of data from the shift register to the latch occurs when the  $\overline{LE}$  is high. The data in the latch is stored during  $\overline{LE}$  transition from high to low.

### **Electrical Characteristics** (for $V_{DD} = 5V$ , $V_{PP} = 300V$ , $T_A = 25^{\circ}C$ )

#### **DC Characteristics**

| Symbol           | Parameter                                |                   | Min                 | Тур | Max                  | Units | Conditions                              |

|------------------|------------------------------------------|-------------------|---------------------|-----|----------------------|-------|-----------------------------------------|

| I <sub>DD</sub>  | V <sub>DD</sub> supply current           |                   |                     |     | 15                   | mA    | $f_{CLK} = 8MHz, f_{DATA} = 4MHz$       |

|                  |                                          |                   |                     |     |                      |       | $\overline{LE} = LOW$                   |

| I <sub>DDQ</sub> | Quiescent V <sub>DD</sub> supply current |                   |                     |     | 200                  | μΑ    | All $V_{IN} = 0V$ or $V_{DD}$           |

| I <sub>PP</sub>  | High voltage supply current              |                   |                     |     | 0.50                 | mA    | V <sub>PP</sub> = 300V All outputs high |

|                  |                                          |                   |                     |     | 0.50                 | mA    | V <sub>PP</sub> = 300V All outputs low  |

| I <sub>IH</sub>  | High-level logic input current           |                   |                     |     | 10                   | μΑ    | $V_{IH} = V_{DD}$                       |

| I <sub>IL</sub>  | Low-level logic input current            |                   |                     |     | -10                  | μΑ    | $V_{IL} = 0V$                           |

| V <sub>OH</sub>  | High-level output HV <sub>OUT</sub>      |                   | 265                 |     |                      | V     | $V_{PP} = 300V$ , $IHV_{OUT} = -1mA$    |

|                  |                                          | Data out          | V <sub>DD</sub> -1V |     |                      | V     | $ID_{OUT} = -100\mu A$                  |

| V <sub>OL</sub>  | Low-level output                         | HV <sub>OUT</sub> |                     |     | 35                   | V     | $V_{DD} = 5V$ , $IHV_{OUT} = 1mA$       |

|                  |                                          | Data out          |                     |     | 1.0                  | V     | ID <sub>OUT</sub> = 100μA               |

| V <sub>oc</sub>  | HV <sub>OUT</sub> clamp voltage          |                   |                     |     | V <sub>PP</sub> +1.5 | V     | $I_{OC} = 1mA$                          |

|                  |                                          |                   |                     |     | -30                  | V     | I <sub>OC</sub> = -1mA                  |

#### **AC Characteristics**<sup>1</sup> (For $V_{DD} = 5V$ , $V_{PP} = 300V$ , $T_{A} = 25$ °C)

| Symbol                             | Parameter                                   | Min | Тур | Max | Units | Conditions            |

|------------------------------------|---------------------------------------------|-----|-----|-----|-------|-----------------------|

| f <sub>CLK</sub>                   | Clock frequency                             |     |     | 8   | MHz   |                       |

| t <sub>W</sub>                     | Clock width high and low                    | 62  |     |     | ns    |                       |

| t <sub>SU</sub>                    | Data setup time before clock rises          | 35  |     |     | ns    |                       |

| t <sub>H</sub>                     | Data hold time after clock rises            | 30  |     |     | ns    |                       |

| t <sub>WLE</sub>                   | Width of latch enable pulse                 | 80  |     |     | ns    |                       |

| t <sub>DLE</sub>                   | LE delay time after rising edge of clock    | 35  |     |     | ns    |                       |

| t <sub>SLE</sub>                   | LE setup time before rising edge of clock   | 40  |     |     | ns    |                       |

| t <sub>ON</sub> , t <sub>OFF</sub> | Time from latch enable to $HV_{\text{OUT}}$ |     |     | 4   | μS    | $C_L = 20pF$          |

| t <sub>DHL</sub>                   | Delay time clock to data out high to low    |     |     | 125 | ns    | $C_L = 20pF$          |

| t <sub>DLH</sub>                   | Delay time clock to data out low to high    |     |     | 125 | ns    | C <sub>L</sub> = 20pF |

| t <sub>r</sub> , t <sub>f</sub>    | All logic inputs                            |     |     | 5   | ns    |                       |

#### Note:

### **Recommended Operating Conditions**

| Symbol          | Parameter                      | Min                  | Тур | Max      | Units |

|-----------------|--------------------------------|----------------------|-----|----------|-------|

| $V_{DD}$        | Logic supply voltage           | 4.5                  | 5.0 | 5.5      | V     |

| V <sub>PP</sub> | High voltage supply            | 60                   |     | 300      | V     |

| V <sub>IH</sub> | High-level input voltage       | V <sub>DD</sub> -0.9 |     | $V_{DD}$ | V     |

| V <sub>IL</sub> | Low-level input voltage        | 0                    |     | 0.9      | V     |

| T <sub>A</sub>  | Operating free-air temperature | 0                    |     | +70      | °C    |

#### Notes:

Power-up sequence should be the following:

- 1. Connect ground.

- 2. Apply V<sub>DD</sub>

- 3. Set all inputs (Data, CLK, Enable, etc.) to a known state.

- ${\rm 4.} \quad {\rm Apply} \; V_{PP}.$

- 5. The  $V_{PP}$  should not drop below  $V_{DD}$  or float during operation.

Power-down sequence should be the reverse of the above.

<sup>1.</sup> Shift register speed can be as low as DC as long as Data Set-up and Hold Time meet the spec.

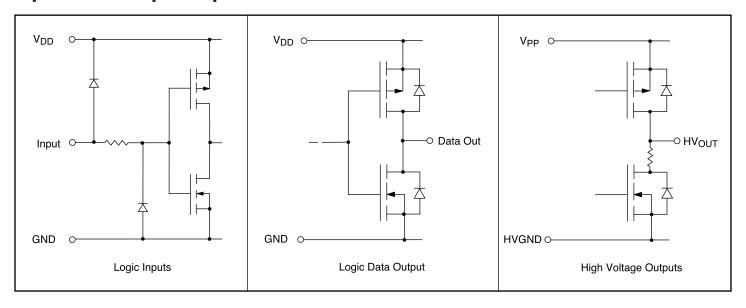

# **Input and Output Equivalent Circuits**

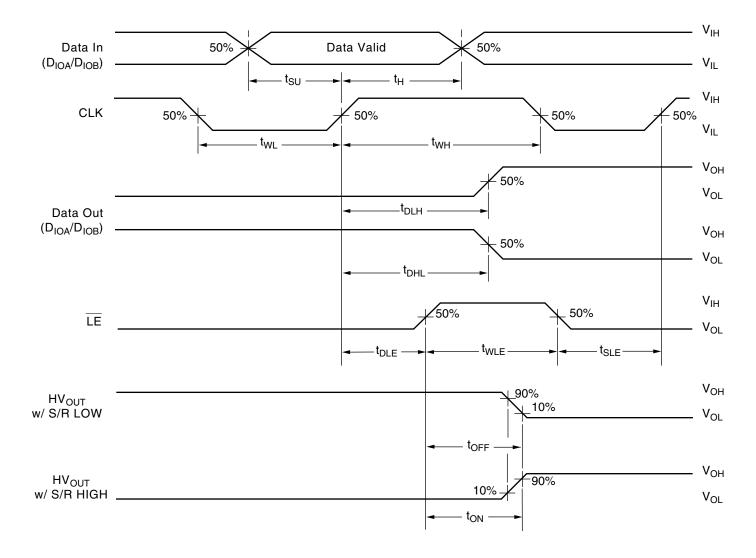

### **Switching Waveforms**

# **Functional Block Diagram**

#### **Function Table**

|               |                  |     | Inp      | uts | Outputs |     |                           |                         |                  |

|---------------|------------------|-----|----------|-----|---------|-----|---------------------------|-------------------------|------------------|

| Function      | Data             | CLK | LE       | BL  | POL     | DIR | <b>Shift Reg</b> 1 264    | <b>HV Outputs</b> 1 264 | Data Out *       |

| All on        | Х                | Х   | Х        | L   | L       | Х   | * * *                     | Н НН                    | *                |

| All off       | Х                | Х   | Х        | L   | Н       | Х   | * * *                     | L LL                    | *                |

| Invert mode   | Х                | Х   | L        | Н   | L       | Х   | * * *                     | * **                    | *                |

| Load S/R      | H or L           | 1   | L        | Н   | Н       | Х   | H or L **                 | * * *                   | *                |

| Store data    | Х                | Х   | <b>↓</b> | Н   | Н       | Х   | * * *                     | * * *                   | *                |

| in latches    | Х                | Х   | <b>↓</b> | Н   | L       | Х   | * * *                     | * **                    | *                |

| Transparent   | L                | 1   | Н        | Н   | Н       | Х   | L **                      | L **                    | *                |

| latch mode    | Н                | 1   | Н        | Н   | Н       | Х   | H **                      | H **                    | *                |

| I/O relation  | D <sub>IOA</sub> | 1   | Х        | Х   | Х       | L   | $Q_n \rightarrow Q_{n-1}$ | _                       | D <sub>IOB</sub> |

| 1/O IGIALIOII | D <sub>IOB</sub> | 1   | Х        | Х   | Х       | Н   | $Q_n \rightarrow Q_{n+1}$ | _                       | D <sub>IOA</sub> |

#### Notes:

$H = high \ level, \ L = low \ level, \ X = irrelevant, \ \uparrow = low-to-high \ transition.$

<sup>\* =</sup> dependent on previous stage's state before the last CLK or last  $\overline{\text{LE}}$  high.

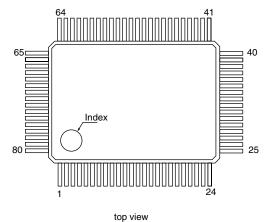

# **Pin Configurations**

#### HV507 80 Pin Gullwing Package

| Pin | Function             | Pin | Function             |

|-----|----------------------|-----|----------------------|

| 1   | HV <sub>OUT</sub> 41 | 41  | HV <sub>OUT</sub> 1  |

| 2   | HV <sub>OUT</sub> 42 | 42  | HV <sub>OUT</sub> 2  |

| 3   | HV <sub>OUT</sub> 43 | 43  | HV <sub>OUT</sub> 3  |

| 4   | HV <sub>OUT</sub> 44 | 44  | HV <sub>OUT</sub> 4  |

| 5   | HV <sub>OUT</sub> 45 | 45  | HV <sub>OUT</sub> 5  |

| 6   | HV <sub>OUT</sub> 46 | 46  | HV <sub>OUT</sub> 6  |

| 7   | HV <sub>OUT</sub> 47 | 47  | $HV_{OUT}$ 7         |

| 8   | HV <sub>OUT</sub> 48 | 48  | HV <sub>OUT</sub> 8  |

| 9   | HV <sub>OUT</sub> 49 | 49  | HV <sub>OUT</sub> 9  |

| 10  | HV <sub>OUT</sub> 50 | 50  | HV <sub>OUT</sub> 10 |

| 11  | HV <sub>OUT</sub> 51 | 51  | HV <sub>OUT</sub> 11 |

| 12  | HV <sub>OUT</sub> 52 | 52  | HV <sub>OUT</sub> 12 |

| 13  | HV <sub>OUT</sub> 53 | 53  | HV <sub>OUT</sub> 13 |

| 14  | HV <sub>OUT</sub> 54 | 54  | HV <sub>OUT</sub> 14 |

| 15  | HV <sub>OUT</sub> 55 | 55  | HV <sub>OUT</sub> 15 |

| 16  | HV <sub>OUT</sub> 56 | 56  | HV <sub>OUT</sub> 16 |

| 17  | HV <sub>OUT</sub> 57 | 57  | HV <sub>OUT</sub> 17 |

| 18  | HV <sub>OUT</sub> 58 | 58  | HV <sub>OUT</sub> 18 |

| 19  | HV <sub>OUT</sub> 59 | 59  | HV <sub>OUT</sub> 19 |

| 20  | HV <sub>OUT</sub> 60 | 60  | HV <sub>OUT</sub> 20 |

| 21  | HV <sub>OUT</sub> 61 | 61  | HV <sub>OUT</sub> 21 |

| 22  | HV <sub>OUT</sub> 62 | 62  | HV <sub>OUT</sub> 22 |

| 23  | HV <sub>OUT</sub> 63 | 63  | HV <sub>OUT</sub> 23 |

| 24  | HV <sub>OUT</sub> 64 | 64  | HV <sub>OUT</sub> 24 |

| 25  | $V_{PP}$             | 65  | HV <sub>OUT</sub> 25 |

| 26  | D <sub>IOA</sub>     | 66  | HV <sub>OUT</sub> 26 |

| 27  | N/C                  | 67  | HV <sub>OUT</sub> 27 |

| 28  | N/C                  | 68  | HV <sub>OUT</sub> 28 |

| 29  | BL                   | 69  | HV <sub>OUT</sub> 29 |

| 30  | POL                  | 70  | HV <sub>OUT</sub> 30 |

| 31  | $V_{DD}$             | 71  | HV <sub>OUT</sub> 31 |

| 32  | DIR                  | 72  | HV <sub>OUT</sub> 32 |

| 33  | GND                  | 73  | HV <sub>OUT</sub> 33 |

| 34  | HVGND                | 74  | HV <sub>OUT</sub> 34 |

| 35  | N/C                  | 75  | HV <sub>OUT</sub> 35 |

| 36  | N/C                  | 76  | HV <sub>OUT</sub> 36 |

| 37  | CLK                  | 77  | HV <sub>OUT</sub> 37 |

| 38  | LE                   | 78  | HV <sub>OUT</sub> 38 |

| 39  | D <sub>IOB</sub>     | 79  | HV <sub>OUT</sub> 39 |

| 40  | $V_{PP}$             | 80  | HV <sub>OUT</sub> 40 |

# **Package Outline**

80-pin Gullwing Package