2.7 V to 5.25 V

### LMP91000

# Sensor AFE System: Configurable AFE Potentiostat for Low-Power Chemical Sensing Applications

### **General Description**

The LMP91000 is a programmable Analog Front End (AFE) for use in micro-power electrochemical sensing applications. It provides a complete signal path solution between a sensor and a microcontroller that generates an output voltage proportional to the cell current. The LMP91000's programmability enables it to support multiple electrochemical sensors such as 3-lead toxic gas sensors and 2-lead galvanic cell sensors with a single design as opposed to the multiple discrete solutions. The LMP91000 supports gas sensitivities over a range of 0.5 nA/ppm to 9500 nA/ppm. It also allows for an easy conversion of current ranges from  $5\mu A$  to  $750\mu A$  full scale.

The LMP91000's adjustable cell bias and transimpedance amplifier (TIA) gain are programmable through the the I²C interface. The I²C interface can also be used for sensor diagnostics. An integrated temperature sensor can be read by the user through the VOUT pin and used to provide additional signal correction in the  $\mu C$  or monitored to verify temperature conditions at the sensor.

The LMP91000 is optimized for micro-power applications and operates over a voltage range of 2.7V to 5.25V. The total current consumption can be less than 10 $\mu$ A. Further power savings are possible by switching off the TIA amplifier and shorting the reference electrode to the working electrode with an internal switch.

#### **Features**

Supply voltage

Typical Values, T<sub>A</sub> = 25°C

| <ul><li>Supply current (average over time)</li></ul> | <10 µA        |

|------------------------------------------------------|---------------|

| <ul> <li>Cell conditioning current up to</li> </ul>  | 10 mA         |

| ■ Reference electrode bias current (85°C)            | 900pA (max)   |

| <ul> <li>Output drive current</li> </ul>             | 750µA         |

| ■ Complete potentiostat circuit to interface to      | most chemical |

| cells                                                |               |

- Programmable cell bias voltage

- Low bias voltage drift

- Programmable TIA gain 2.75kΩ to 350kΩ

- Sink and source capability

- I<sup>2</sup>C compatible digital interface

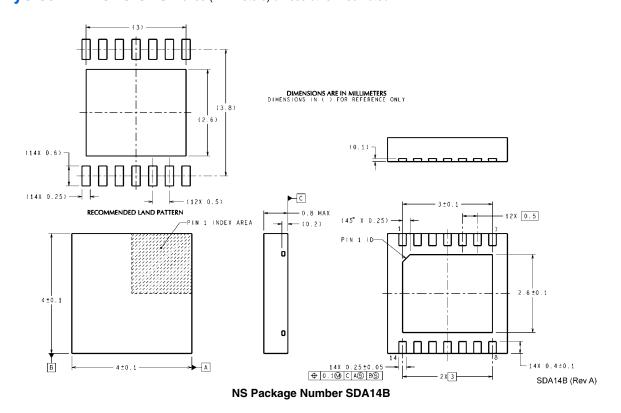

- Ambient operating temperature-40°C to 85°C■ Package14 pin LLP

- Supported by Webench Sensor AFE Designer

#### **Applications**

- Chemical species identification

- Amperometric applications

- Electrochemical blood glucose meter

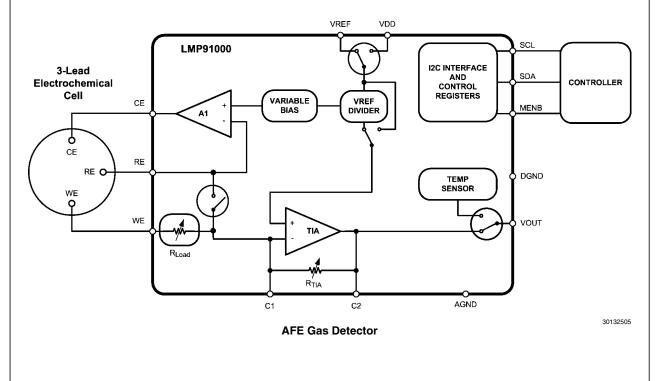

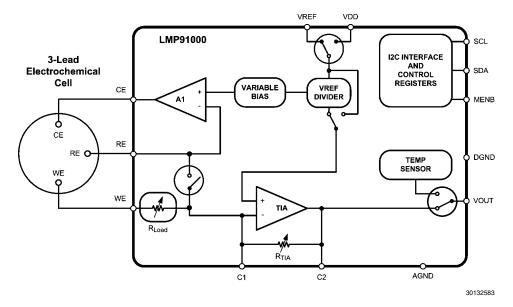

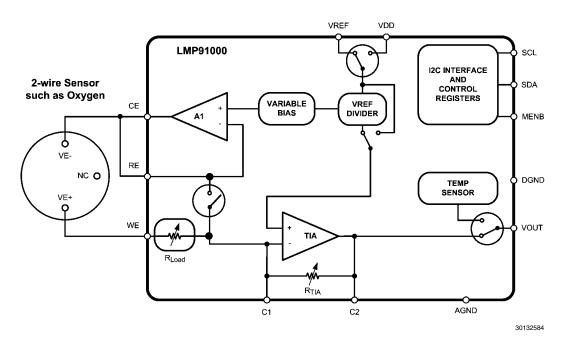

## **Typical Application**

# **Ordering Information**

| Package    | Part Number | Package<br>Marking | Transport Media          | NSC Drawing |

|------------|-------------|--------------------|--------------------------|-------------|

|            | LMP91000SD  |                    | 1k Units Tape and Reel   |             |

| 14-Pin LLP | LMP91000SDE | L91000             | 250 Units Tape and Reel  | SDA14B      |

|            | LMP91000SDX |                    | 4.5k Units Tape and Reel |             |

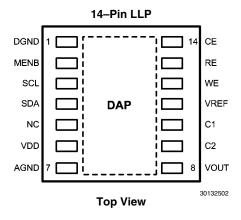

# **Connection Diagram**

# **Pin Descriptions**

| Pin | Name | Description                                                                  |

|-----|------|------------------------------------------------------------------------------|

| 1   | DGND | Connect to ground                                                            |

| 2   | MENB | Module Enable, Active Low                                                    |

| 3   | SCL  | Clock signal for I <sup>2</sup> C compatible interface                       |

| 4   | SDA  | Data for I <sup>2</sup> C compatible interface                               |

| 5   | NC   | Not Internally Connected                                                     |

| 6   | VDD  | Supply Voltage                                                               |

| 7   | AGND | Ground                                                                       |

| 8   | VOUT | Analog Output                                                                |

| 9   | C2   | External filter connector (Filter between C1 and C2)                         |

| 10  | C1   | External filter connector (Filter between C1 and C2)                         |

| 11  | VREF | Voltage Reference input                                                      |

| 12  | WE   | Working Electrode. Output to drive the Working Electrode of the chemical     |

|     |      | sensor                                                                       |

| 13  | RE   | Reference Electrode. Input to drive Counter Electrode of the chemical sensor |

| 14  | CE   | Counter Electrode. Output to drive Counter Electrode of the chemical sensor  |

|     | DAP  | Connect to AGND                                                              |

### **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

ESD Tolerance (Note 2) **Human Body Model** 2kV Charge-Device Model 1kV Machine Model 200V Voltage between any two pins 6.0V Current through VDD or VSS 50mA Current sunk and sourced by CE pin 10mA Current out of other pins(Note 3) 5mA -65°C to 150°C Storage Temperature Range Junction Temperature (Note 4) 150°C

For soldering specifications: see product folder at www.national.com and www.national.com/ms/MS-SOLDERING.pdf

### **Operating Ratings** (Note 1)

Supply Voltage  $V_S$ =(VDD - AGND) 2.7V to 5.25V Temperature Range (*Note 4*) -40°C to 85°C Package Thermal Resistance (*Note 4*) 44 °C/W

### **Electrical Characteristics** (Note 5)

Unless otherwise specified, all limits guaranteed for  $T_A = 25$ °C,  $V_S = (VDD - AGND)$ ,  $V_S = 3.3$ V and AGND = DGND = 0V, VREF= 2.5V, Internal Zero= 20% VREF. **Boldface** limits apply at the temperature extremes.

| Symbol          | Parameter                                                                     | Conditions                                                              | Min<br>(Note 7)    | Typ  | Max<br>(Note 7)   | Units  |

|-----------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------|------|-------------------|--------|

| Power Sup       | ply Specification                                                             |                                                                         | (1000)             | (    | (11010 / /        |        |

| I <sub>S</sub>  | Supply Current                                                                | 3-lead amperometric cell mode<br>MODECN = 0x03                          |                    | 10   | <b>15</b><br>13.5 |        |

|                 |                                                                               | Standby mode<br>MODECN = 0x02                                           |                    | 6.5  | <b>10</b><br>8    |        |

|                 |                                                                               | Temperature Measurement mode with TIA OFF MODECN = 0x06                 |                    | 11.4 | <b>15</b><br>13.5 |        |

|                 |                                                                               | Temperature Measurement mode with TIA ON MODECN = 0x07                  |                    | 14.9 | <b>20</b><br>18   | μA     |

|                 |                                                                               | 2-lead ground referred galvanic cell mode<br>VREF=1.5V<br>MODECN = 0x01 |                    | 6.2  | <b>9</b><br>8     |        |

|                 |                                                                               | Deep Sleep mode<br>MODECN = 0x00                                        |                    | 0.6  | <b>1</b><br>0.85  |        |

| Potentiosta     | at                                                                            |                                                                         |                    |      |                   |        |

| Bias_RW         | Bias Programming range<br>(differential voltage between RE<br>pin and WE pin) | Percentage of voltage referred to VREF or VDD                           |                    | ±24  |                   | %      |

|                 | Bias Programming Resolution                                                   | First two smallest step                                                 |                    | ±1   |                   | %      |

|                 |                                                                               | All other steps                                                         |                    | ±2   |                   | 76     |

|                 | Input bias current at RE pin                                                  | VDD=2.7V;<br>Internal Zero 50% VDD                                      | -90<br><b>-800</b> |      | 90<br><b>800</b>  | pА     |

| I <sub>RE</sub> | input bias current at the piri                                                | VDD=5.25V;<br>Internal Zero 50% VDD                                     | -90<br><b>-900</b> |      | 90<br><b>900</b>  | pΑ     |

| I <sub>CE</sub> | Minimum operating current                                                     | sink                                                                    |                    | 750  |                   | μA     |

|                 | capability                                                                    | source                                                                  |                    | 750  |                   | μΛ     |

|                 | Minimum charging capability                                                   | sink                                                                    |                    | 10   |                   | mA     |

|                 | (Note 9)                                                                      | source                                                                  |                    | 10   |                   | 111/5  |

| AOL_A1          | Open loop voltage gain of control loop op amp (A1)                            | 300mV≤VCE≤Vs-300mV;<br>-750μA≤ICE≤750μA                                 | 104                | 120  |                   | dB     |

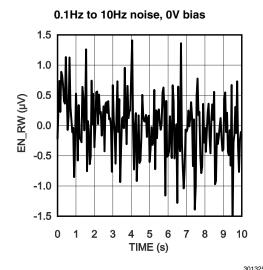

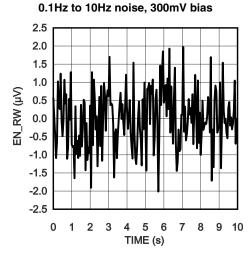

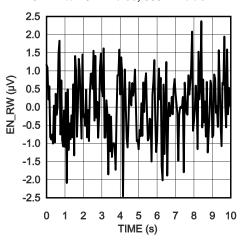

| en_RW           | Low Frequency integrated noise between RE pin and WE pin                      | 0.1Hz to 10Hz, Zero Bias<br>( <i>Note 10</i> )                          |                    | 3.4  |                   | 11\/pp |

|                 |                                                                               | 0.1Hz to 10Hz, with Bias<br>(Note 10, Note 11)                          |                    | 5.1  |                   | μVрр   |

| Symbol               | Parameter                        | Conditions              |                                                                        | Min<br>(Note 7) | Typ<br>( <i>Note 6</i> ) | Max<br>(Note 7) | Unit  |

|----------------------|----------------------------------|-------------------------|------------------------------------------------------------------------|-----------------|--------------------------|-----------------|-------|

|                      |                                  |                         | 0% VREF<br>Internal Zero=20% VREF<br>0% VREF<br>Internal Zero=50% VREF | -550            | (Note 6)                 | 550             |       |

|                      |                                  |                         | 0% VREF Internal Zero=67% VREF ±1% VREF                                | -575            |                          | 575             |       |

|                      |                                  |                         | ±2% VREF                                                               | -610            |                          | 610             |       |

|                      |                                  |                         | ±4% VREF                                                               | -750            |                          | 750             |       |

| V <sub>OS_RW</sub>   | WE Voltage Offset referred to    | BIAS polarity           | ±6% VREF                                                               | -840            |                          | 840             | μ\    |

| U3_HW                | RE                               | (Note 12)               | ±8% VREF                                                               | -930            |                          | 930             |       |

|                      |                                  |                         | ±10% VREF                                                              | -1090           |                          | 1090            |       |

|                      |                                  |                         | ±12% VREF                                                              | -1235           |                          | 1235            |       |

|                      |                                  |                         | ±14% VREF                                                              | -1430           |                          | 1430            |       |

|                      |                                  |                         | ±16% VREF                                                              | -1510           |                          | 1510            |       |

|                      |                                  |                         | ±18% VREF                                                              | -1575           |                          | 1575            |       |

|                      |                                  |                         | ±20% VREF                                                              | -1650           |                          | 1650            |       |

|                      |                                  |                         | ±22% VREF                                                              | -1700           |                          | 1700            |       |

|                      |                                  |                         | ±24% VREF                                                              | -1750           |                          | 1750            |       |

|                      |                                  |                         | 0% VREF<br>Internal Zero=20% VREF                                      |                 |                          |                 |       |

|                      |                                  |                         | 0% VREF<br>Internal Zero=50% VREF                                      | -4              |                          | 4               |       |

|                      |                                  |                         | 0% VREF                                                                |                 |                          |                 |       |

|                      |                                  |                         | Internal Zero=67% VREF                                                 | 4               |                          | 4               |       |

|                      |                                  |                         | ±1% VREF                                                               | -4              |                          |                 |       |

|                      |                                  |                         | ±2% VREF                                                               | -4              |                          | 4               |       |

|                      | WE Voltage Offset Drift referred | BIAS polarity (Note 12) | ±4% VREF                                                               | -5              |                          | 5               | μV/°C |

| ΓcV <sub>OS_RW</sub> | to RE from -40°C to 85°C         |                         | ±6% VREF                                                               | -5              |                          | 5               |       |

|                      | (Note 8)                         |                         | ±8% VREF                                                               | -5              |                          | 5               |       |

|                      |                                  |                         | ±10% VREF                                                              | -6              |                          | 6               |       |

|                      |                                  |                         | ±12% VREF                                                              | -6              |                          | 6               |       |

|                      |                                  |                         | ±14% VREF                                                              | -7              |                          | 7               |       |

|                      |                                  |                         | ±16% VREF                                                              | -7              |                          | 7               |       |

|                      |                                  |                         | ±18% VREF                                                              | -8              |                          | 8               |       |

|                      |                                  |                         | ±20% VREF<br>±22% VREF                                                 | -8<br>-8        |                          | 8               |       |

|                      |                                  |                         |                                                                        |                 |                          | 8               |       |

| TIA_GAIN             | Transimpedance gain accuracy     |                         | ±24% VREF                                                              | -8              | 5                        | 0               | %     |

| IIA_UAIIN            | Linearity                        |                         |                                                                        |                 | ±0.05                    |                 | %     |

|                      | Programmable TIA Gains           | 7 programmable          | gain resistors                                                         |                 | 2.75                     |                 | /(    |

|                      | Trogrammable Tive Game           | 7 programmable          | gamrosiotoro                                                           |                 | 3.5<br>7<br>14<br>35     |                 | ks    |

|                      |                                  |                         |                                                                        |                 | 120<br>350               |                 |       |

|                      | 1                                | Maximum extern          | al gain resistor                                                       |                 | 350                      |                 |       |

| Symbol      | Parameter                              | Conditions        |                                     | Min<br>(Note 7) | Typ<br>(Note 6) | Max<br>(Note 7) | Units     |

|-------------|----------------------------------------|-------------------|-------------------------------------|-----------------|-----------------|-----------------|-----------|

| TIA_ZV      | Internal zero voltage                  | 3 programmable pe | ercentages of VREF                  |                 | 20              |                 |           |

|             |                                        |                   | •                                   |                 | 50              |                 |           |

|             |                                        |                   |                                     |                 | 67              |                 | %         |

|             |                                        | 3 programmable pe | ercentages of VDD                   |                 | 20              |                 | 70        |

|             |                                        |                   |                                     |                 | 50              |                 |           |

|             |                                        |                   |                                     |                 | 67              |                 |           |

|             | Internal zero voltage Accuracy         |                   |                                     |                 | ±0.04           |                 | %         |

| RL          | Programmable Load                      | 4 programmable re | sistive loads                       |                 | 10              |                 |           |

|             |                                        |                   |                                     |                 | 33              |                 | 0         |

|             |                                        |                   |                                     |                 | 50              |                 | Ω         |

|             |                                        |                   |                                     |                 | 100             |                 |           |

|             | Load accuracy                          |                   |                                     |                 | 5               |                 | %         |

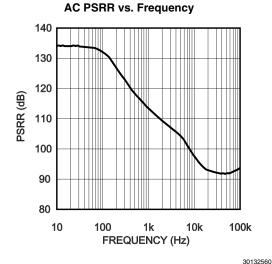

|             | Power Supply Rejection Ratio at RE pin | 12.7 = VDD=3.23V  | Internal zero 20% VREF              |                 |                 |                 |           |

| PSRR        |                                        |                   | Internal zero 50% VREF              | 80              | 110             |                 | dB        |

|             |                                        |                   | Internal zero 67% VREF              |                 |                 |                 | i         |

| Temperatu   | re Sensor Specification (Refer to      | Temperature Sens  | sor <i>Transfer Table</i> in the Fu | nction Des      | cription sec    | ction for de    | etails)   |

|             | Temperature Error                      | TA=-40°C to 85°C  |                                     | -3              |                 | 3               | °C        |

|             | Sensitivity                            | TA=-40°C to 85°C  |                                     |                 | -8.2            |                 | mV/°C     |

|             | Power on time                          |                   |                                     |                 |                 | 1.9             | ms        |

| External re | ference specification                  |                   |                                     |                 |                 |                 |           |

| VREF        | External Voltage reference             |                   |                                     | 1.5             |                 | VDD             | V         |

|             | range                                  |                   |                                     | 1.5             |                 | <b>V</b> DD     | ٧         |

|             | Input impedance                        |                   |                                     |                 | 10              |                 | $M\Omega$ |

|             |                                        |                   |                                     |                 |                 |                 |           |

### I<sup>2</sup>C Interface (Note 5)

Unless otherwise specified, all limits guaranteed for at  $T_A = 25^{\circ}C$ ,  $V_S = (VDD - AGND)$ ,  $2.7V < V_S < 5.25V$  and AGND = DGND = 0V, VREF = 2.5V. **Boldface** limits apply at the temperature extremes

| Symbol          | Parameter                             | Conditions            | Min      | Тур      | Max      | Units |

|-----------------|---------------------------------------|-----------------------|----------|----------|----------|-------|

|                 |                                       |                       | (Note 7) | (Note 6) | (Note 7) |       |

| V <sub>IH</sub> | Input High Voltage                    |                       | 0.7*VDD  |          |          | V     |

| V <sub>IL</sub> | Input Low Voltage                     |                       |          |          | 0.3*VDD  | V     |

| V <sub>OL</sub> | Output Low Voltage                    | I <sub>OUT</sub> =3mA |          |          | 0.4      | V     |

|                 | Hysteresis (Note 14)                  |                       | 0.1*VDD  |          |          | V     |

| C <sub>IN</sub> | Input Capacitance on all digital pins |                       |          | 0.5      |          | pF    |

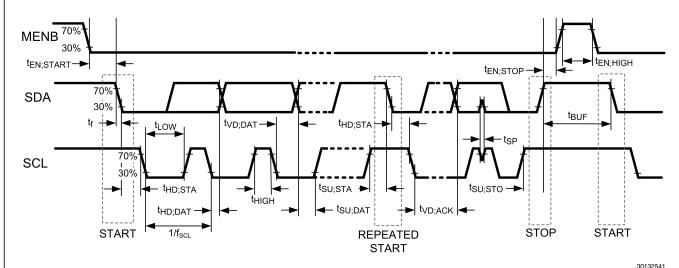

# **Timing Characteristics** (Note 5)

Unless otherwise specified, all limits guaranteed for  $T_A = 25^{\circ}C$ ,  $V_S = (VDD - AGND)$ ,  $V_S = 3.3V$  and AGND = DGND =0V, VREF= 2.5V, Internal Zero= 20% VREF. **Boldface** limits apply at the temperature extremes. Refer to timing diagram in *Figure 1*.

| Symbol              | Parameter                                  | Conditions                                            | Min | Тур | Max | Units |

|---------------------|--------------------------------------------|-------------------------------------------------------|-----|-----|-----|-------|

| f <sub>SCL</sub>    | Clock Frequency                            |                                                       | 10  |     | 100 | kHz   |

| $t_{LOW}$           | Clock Low Time                             |                                                       | 4.7 |     |     | μs    |

| t <sub>HIGH</sub>   | Clock High Time                            |                                                       | 4.0 |     |     | μs    |

| t <sub>HD;STA</sub> | Data valid                                 | After this period, the first clock pulse is generated | 4.0 |     |     | μs    |

| t <sub>SU;STA</sub> | Set-up time for a repeated START condition |                                                       | 4.7 |     |     | μs    |

| t <sub>HD;DAT</sub> | Data hold time(Note 13)                    |                                                       | 0   |     |     | ns    |

| t <sub>SU;DAT</sub> | Data Setup time                            |                                                       | 250 |     |     | ns    |

| t <sub>f</sub>      | SDA fall time (Note 14)                    | IL ≤ 3mA;<br>CL ≤ 400pF                               |     |     | 250 | ns    |

| t <sub>SU;STO</sub> | Set-up time for STOP condition             |                                                       | 4.0 |     |     | μs    |

5

| Symbol                | Parameter                                                                           | Conditions | Min | Тур | Max  | Units |

|-----------------------|-------------------------------------------------------------------------------------|------------|-----|-----|------|-------|

| t <sub>BUF</sub>      | Bus free time between a STOP and START condition                                    |            | 4.7 |     |      | μs    |

| t <sub>VD;DAT</sub>   | Data valid time                                                                     |            |     |     | 3.45 | μs    |

| t <sub>VD;ACK</sub>   | Data valid acknowledge time                                                         |            |     |     | 3.45 | μs    |

| t <sub>SP</sub>       | Pulse width of spikes that must be suppressed by the input filter( <i>Note 14</i> ) |            |     |     | 50   | ns    |

| t_timeout             | SCL and SDA Timeout                                                                 |            | 25  |     | 100  | ms    |

| t <sub>EN;START</sub> | I <sup>2</sup> C Interface Enabling                                                 |            | 600 |     |      | ns    |

| t <sub>EN;STOP</sub>  | I <sup>2</sup> C Interface Disabling                                                |            | 600 |     |      | ns    |

| t <sub>EN;HIGH</sub>  | time between consecutive I <sup>2</sup> C interface enabling and disabling          |            | 600 |     |      | ns    |

Note 1: "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Operating Ratings is not implied. Operating Ratings indicate conditions at which the device is functional and the device should not be operated beyond such conditions.

Note 2: Human Body Model, applicable std. MIL-STD-883, Method 3015.7. Machine Model, applicable std. JESD22-A115-A (ESD MM std. of JEDEC) Field-Induced Charge-Device Model, applicable std. JESD22-C101-C (ESD FICDM std. of JEDEC).

Note 3: All non-power pins of this device are protected against ESD by snapback devices. Voltage at such pins will rise beyond absmax if current is forced into pin.

Note 4: The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_{DMAX} = (T_{J(MAX)}, T_A)/\theta_{JA}$  All numbers apply for packages soldered directly onto a PC board.

**Note 5:** Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_J = T_A$ . No guarantee of parametric performance is indicated in the electrical tables under conditions of internal self-heating where  $T_J > T_A$ . Absolute Maximum Ratings indicate junction temperature limits beyond which the device may be permanently degraded, either mechanically or electrically.

Note 6: Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not guaranteed on shipped production material.

Note 7: Limits are 100% production tested at 25°C. Limits over the operating temperature range are guaranteed through correlations using statistical quality control (SQC) method.

Note 8: Offset voltage temperature drift is determined by dividing the change in VOS at the temperature extremes by the total temperature change.

Starting from the measured voltage offset at temperature T1 ( $V_{OS\_RW}(T1)$ ), the voltage offset at temperature T2 ( $V_{OS\_RW}(T2)$ ) is calculated according the following formula:  $V_{OS\_RW}(T2) = V_{OS\_RW}(T1) + ABS(T2 - T1)^* TcV_{OS\_RW}$ .

Note 9: At such currents no accuracy of the output voltage can be expected.

Note 10: This parameter includes both A1 and TIA's noise contribution.

Note 11: In case of external reference connected, the noise of the reference has to be added.

Note 12: For negative bias polarity the Internal Zero is set at 67% VREF.

Note 13: LMP91000 provides an internal 300ns minimum hold time to bridge the undefined region of the falling edge of SCL.

Note 14: This parameter is guaranteed by design or characterization.

## **Timing Diagram**

FIGURE 1. I<sup>2</sup>C Interface Timing Diagram

#

30132563

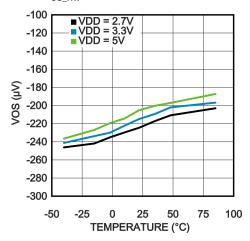

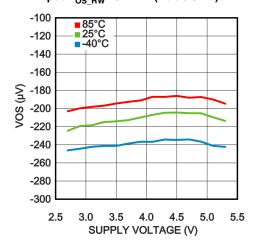

### Input $V_{OS\ RW}$ vs. VDD (Vbias 0mV)

30132562

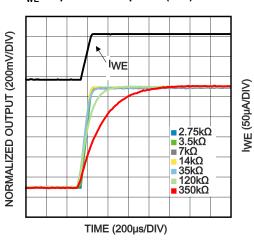

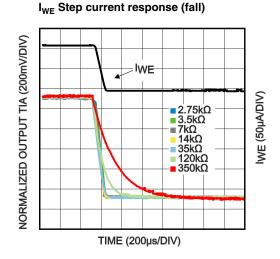

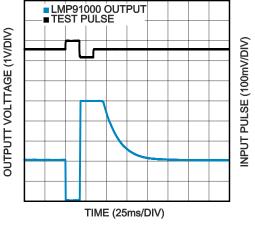

I<sub>WE</sub> Step current response (rise)

30132564

30132566

1320 1318 (a) 1314 1312 1310 2.5 3.0 3.5 4.0 4.5 5.0 5.5 SUPPLY VOLTAGE (V)

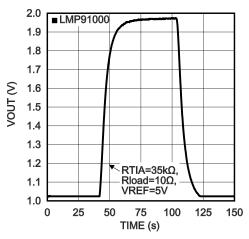

Temperature sensor output vs. VDD (Temperature = 30°C)

30132569

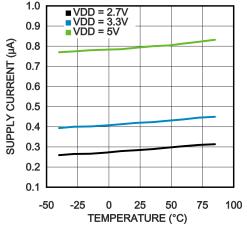

#### Supply current vs. temperature (Deep Sleep Mode)

#### 30132591

# Supply current vs. VDD (Deep Sleep Mode)

30132597

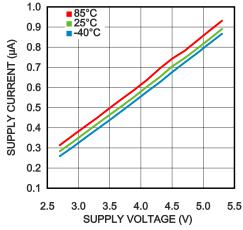

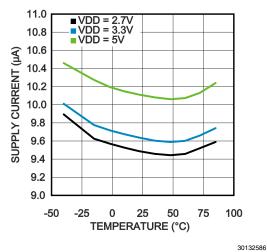

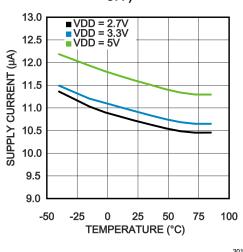

#### Supply current vs. temperature (Standby Mode)

30132587

8

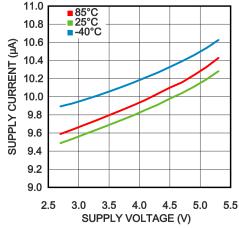

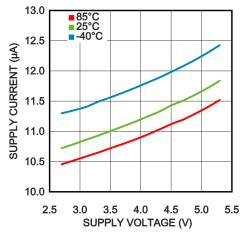

#### Supply current vs. VDD (Standby Mode)

30132592

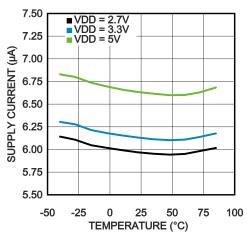

#### Supply current vs. temperature (3-lead amperometric Mode)

Supply current vs. VDD (3-lead amperometric Mode)

30132593

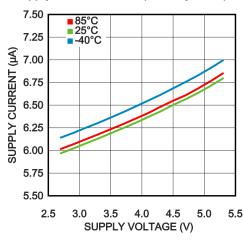

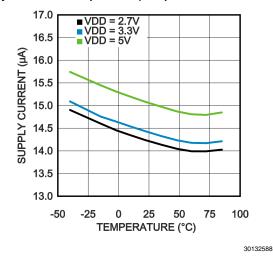

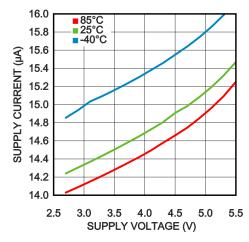

#### Supply current vs. temperature (Temp Measurement TIA ON)

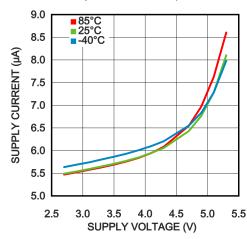

#### Supply current vs. VDD (Temp Measurement TIA ON)

30132594

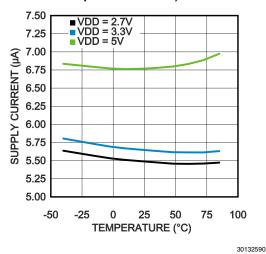

Supply current vs. temperature (Temp Measurement TIA OFF)

Supply current vs. VDD (Temp Measurement TIA OFF)

30132595

# Supply current vs. temperature (2-lead ground referred amperometric Mode)

# Supply current vs. VDD (2-lead ground referred amperometric Mode)

30132596

30132599

#### 0.1Hz to 10Hz noise, 600mV bias

301325100

A VOUT step response 100 ppm to 400 ppm CO (CO gas sensor connected to LMP91000)

30132568

### **Function Description**

#### **GENERAL**

The LMP91000 is a programmable AFE for use in micropower chemical sensing applications. The LMP91000 is designed for 3-lead single gas sensors and for 2-lead galvanic cell sensors. This device provides all of the functionality for detecting changes in gas concentration based on a delta current at the working electrode. The LMP91000 generates an output voltage proportional to the cell current. Transimpedance gain is user programmable through an I²C compatible interface from 2.75k $\Omega$  to 350k $\Omega$  making it easy to convert current ranges from 5 $\mu$ A to 750 $\mu$ A full scale. Optimized for micro-power applications, the LMP91000 AFE works over a voltage range of

2.7V to 5.25 V. The cell voltage is user selectable using the on board programmability. In addition, it is possible to connect an external transimpedance gain resistor. A temperature sensor is embedded and it can be power cycled through the interface. The output of this temperature sensor can be read by the user through the VOUT pin. It is also possible to have both temperature output and output of the TIA at the same time; the pin C2 is internally connected to the output of the transimpedance (TIA), while the temperature is available at the VOUT pin. Depending on the configuration, total current consumption for the device can be less than  $10\mu$ A. For power savings, the transimpedance amplifier can be turned off and instead a load impedance equivalent to the TIA's inputs impedance is switched in.

FIGURE 2. System Block Diagram

#### **POTENTIOSTAT CIRCUITRY**

The core of the LMP91000 is a potentiostat circuit. It consists of a differential input amplifier used to compare the potential between the working and reference electrodes to a required working bias potential (set by the Variable Bias circuitry). The error signal is amplified and applied to the counter electrode (through the Control Amplifier - A1). Any changes in the impedance between the working and reference electrodes will cause a change in the voltage applied to the counter electrode, in order to maintain the constant voltage between working and reference electrodes. A Transimpedance Amplifier connected to the working electrode, is used to provide an output voltage that is proportional to the cell current. The working electrode is held at virtual ground (Internal ground) by the transimpedance amplifier. The potentiostat will compare the reference voltage to the desired bias potential and adjust the voltage at the counter electrode to maintain the proper working-to-reference voltage.

#### Transimpedance amplifier

The transimpedance amplifier (TIA in *Figure 2*) has 7 programmable internal gain resistors. This accommodates the full scale ranges of most existing sensors. Moreover an external gain resistor can be connected to the LMP91000 between C1 and C2 pins. The gain is set through the I<sup>2</sup>C interface.

#### **Control amplifier**

The control amplifier (A1 op amp in *Figure 2*) has two tasks: a) providing initial charge to the sensor, b) providing a bias voltage to the sensor. A1 has the capability to drive up to 10-mA into the sensor in order to to provide a fast initial conditioning. A1 is able to sink and source current according to the connected gas sensor (reducing or oxidizing gas sensor). It can be powered down to reduce system power consumption. However powering down A1 is not recommended, as it may take a long time for the sensor to recover from this situation.

#### Variable Bias

The Variable Bias block circuitry (*Figure 2*) provides the amount of bias voltage required by a biased gas sensor between its reference and working electrodes. The bias voltage can be programmed to be 1% to 24% (14 steps in total) of the supply, or of the external reference voltage. The 14 steps can be programmed through the I<sup>2</sup>C interface. The polarity of the bias can be also programmed.

#### Internal zero

The internal Zero is the voltage at the non-inverting pin of the TIA. The internal zero can be programmed to be either 67%, 50% or 20%, of the supply, or the external reference voltage. This provides both sufficient headroom for the counter electrode of the sensor to swing, in case of sudden changes in the gas concentration, and best use of the ADC's full scale input range.

The Internal zero is provided through an internal voltage divider (Vref divider box in *Figure 2*). The divider is programmed through the I<sup>2</sup>C interface.

#### Temperature sensor

The embedded temperature sensor can be switched off during gas concentration measurement to save power. The temperature measurement is triggered through the I<sup>2</sup>C interface. The temperature output is available at the VOUT pin until the configuration bit is reset. The output signal of the temperature sensor is a voltage, referred to the ground of the LMP91000 (AGND).

#### **Temperature Sensor Transfer Table**

| Temperature | Output<br>Voltage | Temperature | Output<br>Voltage |

|-------------|-------------------|-------------|-------------------|

| (°C)        | (mV)              | (°C)        | (mV)              |

| -40         | 1875              | 23          | 1375              |

| -39         | 1867              | 24          | 1367              |

| -38         | 1860              | 25          | 1359              |

| -37         | 1852              | 26          | 1351              |

| -36         | 1844              | 27          | 1342              |

| -35         | 1836              | 28          | 1334              |

| -34         | 1828              | 29          | 1326              |

| -33         | 1821              | 30          | 1318              |

| -32         | 1813              | 31          | 1310              |

| -31         | 1805              | 32          | 1302              |

| -30         | 1797              | 33          | 1293              |

| -29         | 1789              | 34          | 1285              |

| -28         | 1782              | 35          | 1277              |

| -27         | 1774              | 36          | 1269              |

| -26         | 1766              | 37          | 1261              |

| -25         | 1758              | 38          | 1253              |

| -24         | 1750              | 39          | 1244              |

| -23         | 1742              | 40          | 1236              |

| -22         | 1734              | 41          | 1228              |

| -21         | 1727              | 42          | 1220              |

| -20         | 1719              | 43          | 1212              |

| -19         | 1711              | 44          | 1203              |

| -18         | 1703              | 45          | 1195              |

| -17         | 1695              | 46          | 1187              |

| -16         | 1687              | 47          | 1179              |

| -15         | 1679              | 48          | 1170              |

| -14         | 1671              | 49          | 1162              |

| -13         | 1663              | 50          | 1154              |

| -12         | 1656              | 51          | 1146              |

| -11         | 1648              | 52          | 1137              |

| -10         | 1640              | 53          | 1129              |

| -9          | 1632              | 54          | 1121              |

| -8          | 1624              | 55          | 1112              |

| -7          | 1616              | 56          | 1104              |

| -6          | 1608              | 57          | 1096              |

| -5          | 1600              | 58          | 1087              |

| -4          | 1592              | 59          | 1079              |

| -3          | 1584              | 60          | 1071              |

| -2 | 1576 | 61 | 1063 |

|----|------|----|------|

| -1 | 1568 | 62 | 1054 |

| 0  | 1560 | 63 | 1046 |

| 1  | 1552 | 64 | 1038 |

| 2  | 1544 | 65 | 1029 |

| 3  | 1536 | 66 | 1021 |

| 4  | 1528 | 67 | 1012 |

| 5  | 1520 | 68 | 1004 |

| 6  | 1512 | 69 | 996  |

| 7  | 1504 | 70 | 987  |

| 8  | 1496 | 71 | 979  |

| 9  | 1488 | 72 | 971  |

| 10 | 1480 | 73 | 962  |

| 11 | 1472 | 74 | 954  |

| 12 | 1464 | 75 | 945  |

| 13 | 1456 | 76 | 937  |

| 14 | 1448 | 77 | 929  |

| 15 | 1440 | 78 | 920  |

| 16 | 1432 | 79 | 912  |

| 17 | 1424 | 80 | 903  |

| 18 | 1415 | 81 | 895  |

| 19 | 1407 | 82 | 886  |

| 20 | 1399 | 83 | 878  |

| 21 | 1391 | 84 | 870  |

| 22 | 1383 | 85 | 861  |

Although the temperature sensor is very linear, its response does have a slight downward parabolic shape. This shape is very accurately reflected in the temperature sensor Transfer Table. For a linear approximation, a line can easily be calculated over the desired temperature range from the Table using the two-point equation:

$$V-V_1=((V_2-V_1)/(T_2-T_1))*(T-T_1)$$

Where V is in mV, T is in  ${}^{\circ}C$ , T<sub>1</sub> and V<sub>1</sub> are the coordinates of the lowest temperature, T<sub>2</sub> and V<sub>2</sub> are the coordinates of the highest temperature.

For example, if we want to determine the equation of a line over a temperature range of 20°C to 50°C, we would proceed as follows:

V-1399mV=((1154mV - 1399mV)/(50°C -20°C))\*(T-20°C)

$V-1399mV = -8.16mV/^{\circ}C^{*}(T-20^{\circ}C)$

V=(-8.16mV/°C)\*T+1562.2mV

Using this method of linear approximation, the transfer function can be approximated for one or more temperature ranges of interest.

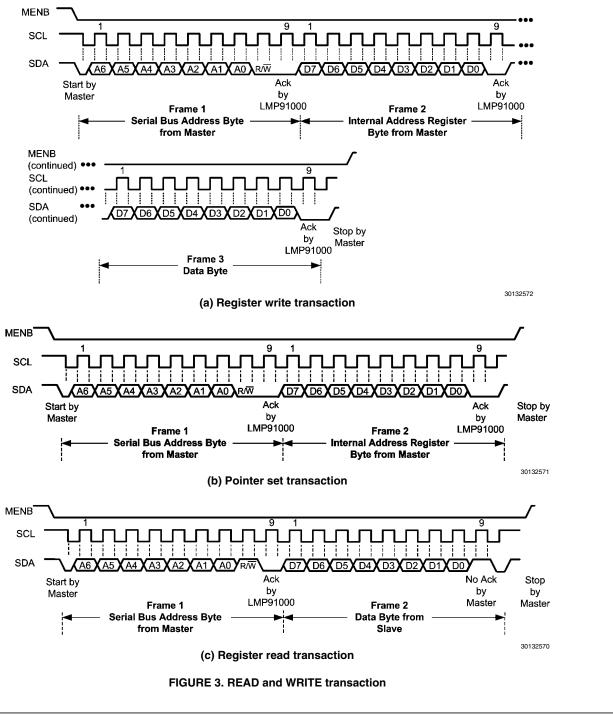

#### **I<sup>2</sup>C INTERFACE**

The I<sup>2</sup>C compatible interface operates in Standard mode (100kHz). Pull-up resistors or current sources are required on the SCL and SDA pins to pull them high when they are not being driven low. A logic zero is transmitted by driving the output low. A logic high is transmitted by releasing the output and allowing it to be pulled-up externally. The appropriate pull-up resistor values will depend upon the total bus capacitance and operating speed. The LMP91000 comes with a 7 bit bus fixed address: 1001 000.

#### WRITE AND READ OPERATION

In order to start any read or write operation with the LMP91000, MENB needs to be set low during the whole communication. Then the master generates a start condition by driving SDA from high to low while SCL is high. The start condition is always followed by a 7-bit slave address and a Read/Write bit. After these 8 bits have been transmitted by the master, SDA is released by the master and the LMP91000 either ACKs or NACKs the address. If the slave address matches, the LMP91000 ACKs the master. For a write operation, the LMP91000 NACKs the master. For a write operation, the master follows the ACK by sending the 8-bit register address pointer. Then the LMP91000 ACKs the transfer by driving SDA low. Next, the master sends the 8-bit data to the LMP91000. Then the LMP91000 ACKs the transfer by driving

SDA low. At this point the master should generate a stop condition and optionally set the MENB at logic high level (refer to *Figure 3*).

A read operation requires the LMP91000 address pointer to be set first, also in this case the master needs setting at low logic level the MENB, then the master needs to write to the device and set the address pointer before reading from the desired register. This type of read requires a start, the slave address, a write bit, the address pointer, a Repeated Start (if appropriate), the slave address, and a read bit (refer to *Figure 3*). Following this sequence, the LMP91000 sends out the 8-bit data of the register.

When just one LMP91000 is present on the I<sup>2</sup>C bus the MENB can be tied to ground (low logic level).

#### **TIMEOUT FEATURE**

The timeout is a safety feature to avoid bus lockup situation. If SCL is stuck low for a time exceeding t\_timeout, the LMP91000 will automatically reset its I²C interface. Also, in the case the LMP91000 hangs the SDA for a time exceeding

<code>t\_timeout</code>, the LMP91000's I²C interface will be reset so that the SDA line will be released. Since the SDA is an open-drain with an external resistor pull-up, this also avoids high power consumption when LMP91000 is driving the bus and the SCL is stopped.

#### **REGISTERS**

The registers are used to configure the LMP91000.

If writing to a reserved bit, user must write only 0. Readback value is unspecified and should be discarded.

#### Register map

| Address           | Name     | Power on default | Access    | Lockable? |

|-------------------|----------|------------------|-----------|-----------|

| 0x00              | STATUS   | 0x00             | Read only | N         |

| 0x01              | LOCK     | 0x01             | R/W       | N         |

| 0x02 through 0x09 | RESERVED |                  |           |           |

| 0x10              | TIACN    | 0x1C             | R/W       | Υ         |

| 0x11              | REFCN    | 0x00             | R/W       | Y         |

| 0x12              | MODECN   | 0x00             | R/W       | N         |

| 0x13 through 0xFF | RESERVED |                  |           |           |

#### STATUS -- Status Register (address 0x00)

The status bit is an indication of the LMP91000's power-on status. If its readback is "0", the LMP91000 is not ready to accept other I<sup>2</sup>C commands.

| Bit   | Name     | Function                                         |

|-------|----------|--------------------------------------------------|

| [7:1] | RESERVED |                                                  |

| 0     | STATUS   | Status of Device  O Not Ready (default)  1 Ready |

#### **LOCK -- Protection Register (address 0x01)**

The lock bit enables and disables the writing of the TIACN and the REFCN registers. In order to change the content of the TIACN and the REFCN registers the lock bit needs to be set to "0".

| Bit   | Name     | Function                                                                                                 |  |  |

|-------|----------|----------------------------------------------------------------------------------------------------------|--|--|

| [7:1] | RESERVED |                                                                                                          |  |  |

| 0     | LOCK     | Write protection 0 Registers 0x10, 0x11 in write mode 1 Registers 0x10, 0x11 in read only mode (default) |  |  |

14

#### **TIACN -- TIA Control Register (address 0x10)**

The parameters in the TIA control register allow the configuration of the transimpedance gain  $(R_{TIA})$  and the load resistance  $(R_{Load})$ .

| Bit   | Name     | Function                          |  |  |

|-------|----------|-----------------------------------|--|--|

| [7:5] | RESERVED | RESERVED                          |  |  |

|       |          | TIA feedback resistance selection |  |  |

|       |          | 000 External resitance            |  |  |

|       |          | 001 2.75kΩ                        |  |  |

|       |          | 010 3.5kΩ                         |  |  |

| [4:2] | TIA_GAIN | 011 7kΩ                           |  |  |

|       |          | 100 14kΩ                          |  |  |

|       |          | 101 35kΩ                          |  |  |

|       |          | 110 120kΩ                         |  |  |

|       |          | 111 350kΩ (default)               |  |  |

|       |          | R <sub>Load</sub> selection       |  |  |

|       |          | 00 10Ω (default)                  |  |  |

| [1:0] |          | 01 33Ω                            |  |  |

|       |          | 10 50Ω                            |  |  |

|       |          | 11 100Ω                           |  |  |

#### **REFCN -- Reference Control Register (address 0x11)**

The parameters in the Reference control register allow the configuration of the Internal zero, Bias and Reference source. When the Reference source is external, the reference is provided by a reference voltage connected to the VREF pin. In this condition the Internal Zero and the Bias voltage are defined as a percentage of VREF voltage instead of the supply voltage.

| Bit   | Name       | Function                                                                                 |  |  |

|-------|------------|------------------------------------------------------------------------------------------|--|--|

|       |            | Reference voltage source selection                                                       |  |  |

| 7     | REF_SOURCE | 0 Internal (default)                                                                     |  |  |

|       |            | 1 external                                                                               |  |  |

|       |            | Internal zero selection (Percentage of the source reference)                             |  |  |

|       |            | 00 20% (default)                                                                         |  |  |

| [6:5] | INT_Z      | 01 50%                                                                                   |  |  |

|       |            | 10 67%                                                                                   |  |  |

|       |            | 11 Internal zero circuitry bypassed (only in O <sub>2</sub> ground referred measurement) |  |  |

|       |            | Selection of the Bias polarity                                                           |  |  |

| 4     | BIAS_SIGN  | 0 Negative (V <sub>WE</sub> - V <sub>RE</sub> )<0V (default)                             |  |  |

|       |            | 1 Positive (V <sub>WE</sub> –V <sub>RE</sub> )>0V                                        |  |  |

|       |            | BIAS selection (Percentage of the source reference)                                      |  |  |

|       |            | 0000 0% (default)                                                                        |  |  |

|       |            | 0001 1%                                                                                  |  |  |

|       |            | 0010 2%                                                                                  |  |  |

|       | BIAS       | 0011 4%                                                                                  |  |  |

|       |            | 0100 6%                                                                                  |  |  |

|       |            | 0101 8%                                                                                  |  |  |

| [3:0] |            | 0110 10%                                                                                 |  |  |

|       |            | 0111 12%                                                                                 |  |  |

|       |            | 1000 14%                                                                                 |  |  |

|       |            | 1001 16%                                                                                 |  |  |

|       |            | 1010 18%                                                                                 |  |  |

|       |            | 1011 20%                                                                                 |  |  |

|       |            | 1100 22%                                                                                 |  |  |

|       |            | 1101 24%                                                                                 |  |  |

#### **MODECN -- Mode Control Register (address 0x12)**

The Parameters in the Mode register allow the configuration of the Operation Mode of the LMP91000.

| Bit   | Name      | Function                                 |  |  |

|-------|-----------|------------------------------------------|--|--|

|       |           | Shorting FET feature                     |  |  |

| 7     | FET_SHORT | 0 Disabled (default)                     |  |  |

|       |           | 1 Enabled                                |  |  |

| [6:3] | RESERVED  |                                          |  |  |

|       |           | Mode of Operation selection              |  |  |

|       |           | 000 Deep Sleep (default)                 |  |  |

|       |           | 001 2-lead ground referred galvanic cell |  |  |

| [2:0] | OP_MODE   | 010 Standby                              |  |  |

|       |           | 011 3-lead amperometric cell             |  |  |

|       |           | 110 Temperature measurement (TIA OFF)    |  |  |

|       |           | 111 Temperature measurement (TIA ON)     |  |  |

When the LMP91000 is in Temperature measurement (TIA ON) mode, the output of the temperature sensor is present at the VOUT pin, while the output of the potentiostat circuit is available at pin C2.

#### **GAS SENSOR INTERFACE**

The LMP91000 supports both 3-lead and 2-lead gas sensors. Most of the toxic gas sensors are amperometric cells with 3 leads (Counter, Worker and Reference). These leads should be connected to the LMP91000 in the potentiostat topology. The 2-lead gas sensor (known as galvanic cell) should be connected as simple buffer either referred to the ground of the system or referred to a reference voltage. The LMP91000 support both connections for 2-lead gas sensor.

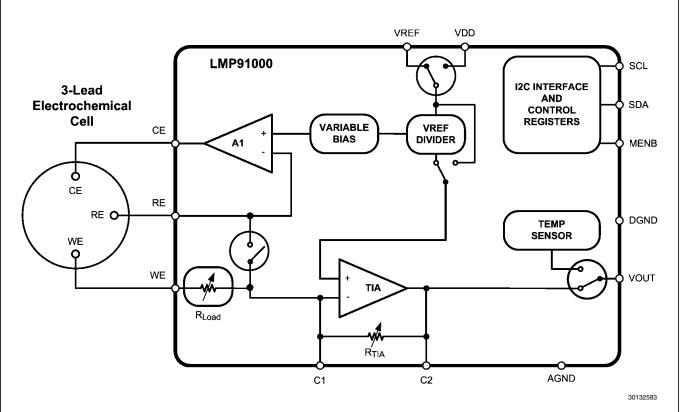

#### 3-lead Amperometric Cell In Potentiostat Configuration

Most of the amperometric cell have 3 leads (Counter, Reference and Working electrodes). The interface of the 3-lead gas sensor to the LMP91000 is straightforward, the leads of the gas sensor need to be connected to the namesake pins of the LMP91000.

The LMP91000 is then configured in 3-lead amperometric cell mode; in this configuration the Control Amplifier (A1) is ON and provides the internal zero voltage and bias in case of biased gas sensor. The transimpedance amplifier (TIA) is ON, it converts the current generated by the gas sensor in a voltage, according to the transimpedance gain:

#### Gain=R<sub>TIA</sub>

If different gains are required, an external resistor can be connected between the pins C1 and C2. In this case the internal feedback resistor should be programmed to "external". The  $\rm R_{Load}$  together with the output capacitance of the gas sensor acts as a low pass filter.

FIGURE 4. 3-Lead Amperometric Cell

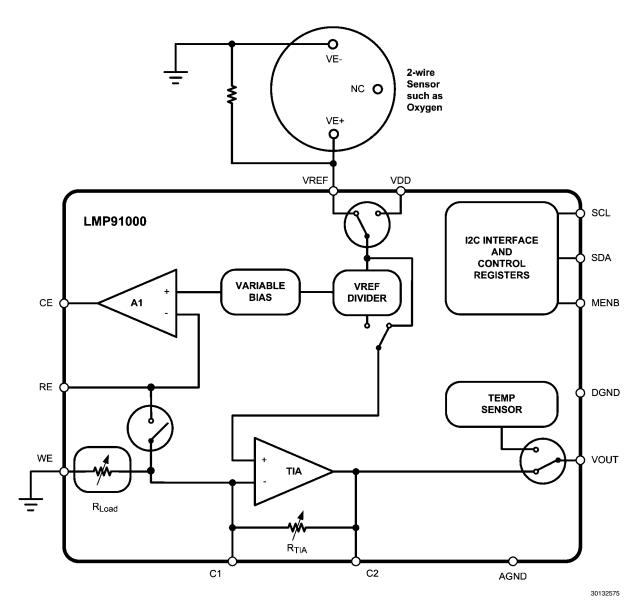

#### 2-lead Galvanic Cell In Ground Referred Configuration

When the LMP91000 is interfaced to a galvanic cell (for instance to an Oxygen gas sensor) referred to the ground of the system, an external resistor needs to be placed in parallel to the gas sensor; the negative electrode of the gas sensor is connected to the ground of the system and the positive electrode to the Vref pin of the LMP91000, the working pin of the LMP91000 is connected to the ground.

The LMP91000 is then configured in 2-lead galvanic cell mode and the Vref bypass feature needs to be enabled. In

this configuration the Control Amplifier (A1) is turned off, and the output of the gas sensor is amplified by the Transimpedance Amplifier (TIA) which is configured as a simple non-inverting amplifier.

The gain of this non inverting amplifier is set according the following formula

$$Gain=1+(R_{TIA}/R_{Load})$$

If different gains are required, an external resistor can be connected between the pins C1 and C2. In this case the internal feedback resistor should be programmed to "external".

FIGURE 5. 2-Lead Galvanic Cell Ground Referred

#### 2-lead Galvanic Cell In Potentiostat Configuration

When the LMP91000 is interfaced to a galvanic cell (for instance to an Oxygen gas sensor) referred to a reference, the Counter and the Reference pin of the LMP91000 are shorted together and connected to negative electrode of the galvanic cell. The positive electrode of the galvanic cell is then connected to the Working pin of the LMP91000.

The LMP91000 is then configured in 3-lead amperometric cell mode (as for amperometric cell). In this configuration the

Control Amplifier (A1) is ON and provides the internal zero voltage. The transimpedance amplifier (TIA) is also ON and it is configured as an inverting amplifier, the gain is set according the following formula:

Gain=

$$-(R_{TIA}/R_{Load})$$

If different gains are required, an external resistor can be connected between the pins C1 and C2. In this case the internal feedback resistor should be programmed to "external".

FIGURE 6. 2-Lead Galvanic Cell In Potentiostat Configuration

## **Application Information**

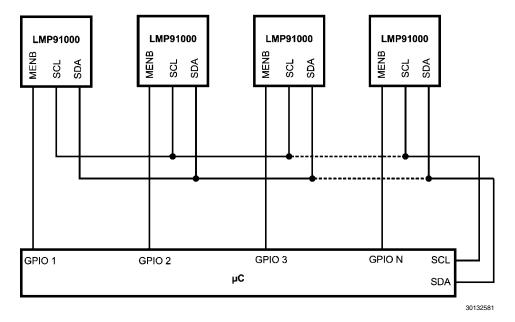

# CONNECTION OF MORE THAN ONE LMP91000 TO THE I2C BUS

The LMP91000 comes out with a unique and fixed I<sup>2</sup>C slave address. It is still possible to connect more than one LMP91000 to an I<sup>2</sup>C bus and select each device using the MENB pin. The MENB simply enables/disables the I<sup>2</sup>C communication of the LMP91000. When the MENB is at logic level low all the I<sup>2</sup>C communication is enabled, it is disabled when MENB is at high logic level.

In a system based on a  $\mu$ controller and more than one LMP91000 connected to the I<sup>2</sup>C bus, the I<sup>2</sup>C lines (SDA and

SCL) are shared, while the MENB of each LMP91000 is connected to a dedicate GPIO port of the  $\mu$ controller.

The  $\mu$ controller starts communication asserting one out of N MENB signals where N is the total number of LMP91000s connected to the I²C bus. Only the enabled device will acknowledge the I²C commands. After finishing communicating with this particular LMP91000, the microcontroller de-asserts the corresponding MENB and repeats the procedure for other LMP91000s. *Figure 7* shows the typical connection when more than one LMP91000 is connected to the I²C bus.

FIGURE 7. More than one LMP91000 on I2C bus

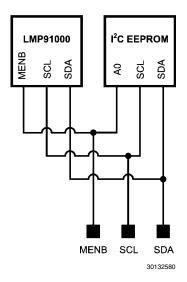

#### **SMART GAS SENSOR ANALOG FRONT END**

The LMP91000 together with an external EEPROM represents the core of a SMART GAS SENSOR AFE. In the EEPROM it is possible to store the information related to the GAS sensor type, calibration and LMP91000's configuration (content of registers 10h, 11h, 12h). At startup the microcontroller reads the EEPROM's content and configures the LMP91000. A typical smart gas sensor AFE is shown in *Figure 8*. The connection of MENB to the hardware address pin A0 of the EEPROM allows the microcontroller to select the LMP91000 and its corresponding EEPROM when more than one smart gas sensor AFE is present on the I<sup>2</sup>C bus. Note: only EEPROM I<sup>2</sup>C addresses with A0=0 should be used in this configuration.

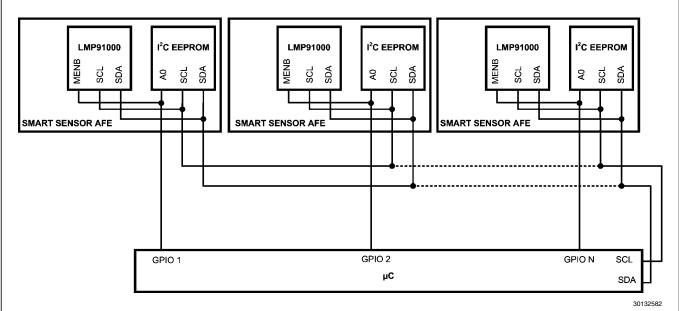

#### SMART GAS SENSOR AFES ON I2C BUS

The connection of Smart gas sensor AFEs on the I²C bus is the natural extension of the previous concepts. Also in this case the microcontroller starts communication asserting 1 out of N MENB signals where N is the total number of smart gas sensor AFE connected to the I²C bus. Only one of the devices (either LMP91000 or its corresponding EEPROM) in the smart gas sensor AFE enabled will acknowledge the I²C commands. When the communication with this particular module ends, the microcontroller de-asserts the corresponding MENB and repeats the procedure for other modules. *Figure 9* shows the typical connection when several smart gas sensor AFEs are connected to the I²C bus.

FIGURE 8. SMART GAS SENSOR AFE

FIGURE 9. SMART GAS SENSOR AFEs on I2C bus

#### **POWER CONSUMPTION**

The LMP91000 is intended for use in portable devices, so the power consumption is as low as possible in order to guarantee a long battery life. The total power consumption for the LMP91000 is below 10µA @ 3.3v average over time, (this excludes any current drawn from any pin). A typical usage of the LMP91000 is in a portable gas detector and its power consumption is summarized in the *Power Consumption Scenario* table. This has the following assumptions:

-Power On only happens a few times over life, so its power consumption can be ignored

- -Deep Sleep mode is not used

- -The system is used about 8 hours a day, and 16 hours a day it is in Standby mode.

- -Temperature Measurement is done about once per minute This results in an average power consumption of approximately 7.95  $\mu A.$  This can potentially be further reduced, by using the Standby mode between gas measurements. It may even be possible, depending on the sensor used, to go into deep sleep for some time between measurements, further reducing the average power consumption.

#### **Power Consumption Scenario**

|                            | Deep Sleep | StandBy | 3-Lead<br>Amperometric<br>Cell | Temperature<br>Measurement<br>TIA OFF | Temperature<br>Measurement<br>TIA ON | Total |

|----------------------------|------------|---------|--------------------------------|---------------------------------------|--------------------------------------|-------|

| Current consumption        |            |         |                                |                                       |                                      |       |

| (μΑ)                       |            |         |                                |                                       |                                      |       |

| typical value              | 0.6        | 6.5     | 10                             | 11.4                                  | 14.9                                 |       |

| Time ON                    |            |         |                                |                                       |                                      |       |

| (%)                        | 0          | 60      | 39                             | 0                                     | 1                                    |       |

| Average                    |            |         |                                |                                       |                                      |       |

| (μΑ)                       | 0          | 3.9     | 3.9                            | 0                                     | 0.15                                 | 7.95  |

| Notes                      |            |         |                                |                                       |                                      |       |

| A1                         | OFF        | ON      | ON                             | ON                                    | ON                                   |       |

| TIA                        | OFF        | OFF     | ON                             | OFF                                   | ON                                   |       |

| TEMP SENSOR                | OFF        | OFF     | OFF                            | ON                                    | ON                                   |       |

| I <sup>2</sup> C interface | ON         | ON      | ON                             | ON                                    | ON                                   |       |

#### **SENSOR TEST PROCEDURE**

The LMP91000 has all the hardware and programmability features to implement some test procedures. The purpose of the test procedure is to:

- a) test proper function of the sensor (status of health)

- b) test proper connection of the sensor to the LMP91000

The test procedure is very easy. The variable bias block is user programmable through the digital interface. A step voltage can be applied by the end user to the positive input of A1. As a consequence a transient current will start flowing into the sensor (to charge its internal capacitance) and it will be detected by the TIA. If the current transient is not detected, either a sensor fault or a connection problem is present. The slope and the aspect of the transient response can also be used to detect sensor aging (for example, a cell that is drying and no longer efficiently conducts the current). After it is verified that the sensor is working properly, the LMP91000 needs to be reset to its original configuration. It is not required to observe the full transient in order to contain the testing time. All the needed information are included in the transient slopes (both edges). Figure 10 shows an example of the test procedure, a Carbon Monoxide sensor is connected to the LMP91000, two pulses are then sequentially applied to the bias voltage:

first step: from 0mV to 40mV second step: from 40mV to -40mV

and finally the bias is set again at 0mV since this is the normal operation condition for this sensor.

30132561

FIGURE 10. TEST PROCEDURE EXAMPLE

# Physical Dimensions inches (millimeters) unless otherwise noted

22

# Notes

For more National Semiconductor product information and proven design tools, visit the following Web sites at: www.national.com

| Pro                            | oducts                       | Design Support               |                                |  |

|--------------------------------|------------------------------|------------------------------|--------------------------------|--|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH® Tools               | www.national.com/webench       |  |

| Audio                          | www.national.com/audio       | App Notes                    | www.national.com/appnotes      |  |

| Clock and Timing               | www.national.com/timing      | Reference Designs            | www.national.com/refdesigns    |  |

| Data Converters                | www.national.com/adc         | Samples                      | www.national.com/samples       |  |

| Interface                      | www.national.com/interface   | Eval Boards                  | www.national.com/evalboards    |  |

| LVDS                           | www.national.com/lvds        | Packaging                    | www.national.com/packaging     |  |

| Power Management               | www.national.com/power       | Green Compliance             | www.national.com/quality/green |  |

| Switching Regulators           | www.national.com/switchers   | Distributors                 | www.national.com/contacts      |  |

| LDOs                           | www.national.com/ldo         | Quality and Reliability      | www.national.com/quality       |  |

| LED Lighting                   | www.national.com/led         | Feedback/Support             | www.national.com/feedback      |  |

| Voltage References             | www.national.com/vref        | Design Made Easy             | www.national.com/easy          |  |

| PowerWise® Solutions           | www.national.com/powerwise   | Applications & Markets       | www.national.com/solutions     |  |

| Serial Digital Interface (SDI) | www.national.com/sdi         | Mil/Aero                     | www.national.com/milaero       |  |

| Temperature Sensors            | www.national.com/tempsensors | SolarMagic™                  | www.national.com/solarmagic    |  |

| PLL/VCO                        | www.national.com/wireless    | PowerWise® Design University | www.national.com/training      |  |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2011 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com

National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com