# JANUARY 2008

### **GENERAL DESCRIPTION**

The TERIDIAN 71M6521DE/FE is a highly integrated SOC with an MPU core, RTC, FLASH and LCD driver. TERIDIAN's patented Single Converter Technology<sup>™</sup> with a 22-bit delta-sigma ADC, four analog inputs, digital temperature compensation, precision voltage reference, battery voltage monitor, and 32-bit computation engine (CE) supports a wide range of residential metering applications with very few low-cost external components. A 32kHz crystal time base for the entire system and internal battery backup support for RAM and RTC further reduce system cost. The IC supports 2-wire, 3-wire and 4-wire single-phase and dual-phase residential metering along with tamper-detection mechanisms.

Maximum design flexibility is provided by multiple UARTs,  $l^2C$ ,  $\mu$ Wire, up to 18 DIO pins and in-system programmable FLASH memory, which can be updated with data or application code in operation.

A complete array of ICE and development tools, programming libraries and reference designs enable rapid development and certification of TOU, AMR and Prepay meters that comply with worldwide electricity metering standards.

### FEATURES

- < 0.4% Wh accuracy over 2000:1 current range and over temperature

- Exceeds IEC62053 / ANSIC12.20 standards

- Voltage reference < 40ppm/°C</li>

- Four sensor inputs—VDD referenced

- Low jitter Wh and VARh pulse test outputs (10kHz maximum)

- Pulse count for pulse outputs

- · Four-quadrant metering

- Tamper detection

Neutral current with CT or shunt

- Line frequency count for RTC

- Digital temperature compensation

- Sag detection for phase A and B

- Independent 32-bit compute engine

- 46-64Hz line frequency range with same calibration

- Phase compensation (±7°)

- · Battery backup for RTC and battery monitor

- Three battery modes w/ wake-up on push-button or timer:

Brownout mode (48µA) LCD mode (5.7µA) Sleep mode (2.9µA)

- Energy display on main power failure

- Wake-up with push-button

- 22-bit delta-sigma ADC

- 8-bit MPU (80515), 1 clock cycle per instruction w/ integrated ICE for MPU debug

- RTC with temperature compensation

- Auto-Calibration

- Hardware watchdog timer, power fail monitor

- LCD driver (up to 152 pixels)

- Up to 18 general purpose I/O pins

- 32kHz time base

- 16KB (6521DE) or 32KB (6521FE) FLASH with security

- 2KB MPU XRAM

- Two UARTs for IR and AMR

- Digital I/O pins compatible with 5V inputs

- 64-pin LQFP or 68-pin QFN package

- Lead-Free packages

DATASHEET

JANUARY 2008

### **Table of Contents**

| GENERAL DESCRIPTION                                     | 1  |

|---------------------------------------------------------|----|

| FEATURES                                                | 1  |

| HARDWARE DESCRIPTION                                    | 9  |

| Hardware Overview                                       | 9  |

| Analog Front End (AFE)                                  | 9  |

| Input Multiplexer                                       | 9  |

| A/D Converter (ADC)                                     | 10 |

| FIR Filter                                              | 10 |

| Voltage References                                      | 10 |

| Temperature Sensor                                      | 11 |

| Battery Monitor                                         | 12 |

| Functional Description                                  | 12 |

| Digital Computation Engine (CE)                         | 12 |

| Meter Equations                                         | 13 |

| Real-Time Monitor                                       | 14 |

| Pulse Generator                                         | 14 |

| CE Functional Overview                                  | 14 |

| 80515 MPU Core                                          | 16 |

| Memory Organization                                     | 16 |

| Special Function Registers (SFRs)                       | 18 |

| Special Function Registers (Generic 80515 SFRs)         | 19 |

| Special Function Registers Specific to the 71M6521DE/FE | 21 |

| Instruction Set                                         | 22 |

| UART                                                    | 22 |

| Timers and Counters                                     | 25 |

| WD Timer (Software Watchdog Timer)                      | 27 |

| Interrupts                                              | 29 |

| On-Chip Resources                                       | 37 |

| Oscillator                                              | 37 |

| PLL and Internal Clocks                                 | 37 |

| Real-Time Clock (RTC)                                   | 37 |

| Temperature Sensor                                      | 37 |

| Physical Memory                                         | 38 |

| Optical Interface                                       | 39 |

| Digital I/O                                             | 39 |

| LCD Drivers                                             | 41 |

| Battery Monitor                                         | 42 |

| EEPROM Interface                                        | 42 |

| Hardware Watchdog Timer                                 | 45 |

### DATASHEET JANUARY 2008

| Program Security                                                       | 45 |

|------------------------------------------------------------------------|----|

| Test Ports                                                             | 46 |

| FUNCTIONAL DESCRIPTION                                                 | 47 |

| Theory of Operation                                                    | 47 |

| System Timing Summary                                                  | 48 |

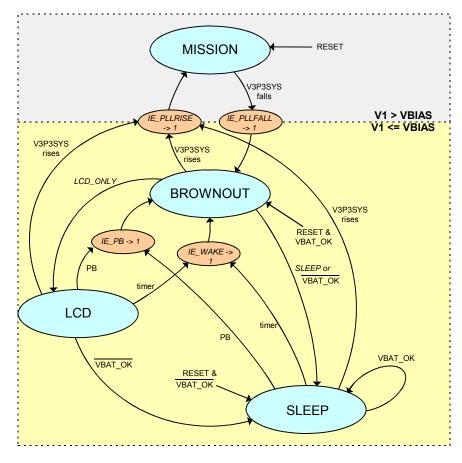

| Battery Modes                                                          | 49 |

| BROWNOUT Mode                                                          | 50 |

| LCD Mode                                                               | 51 |

| SLEEP Mode                                                             | 51 |

| Fault and Reset Behavior                                               | 56 |

| Wake Up Behavior                                                       | 57 |

| Wake on PB                                                             | 57 |

| Wake on Timer                                                          | 57 |

| Data Flow                                                              | 58 |

| CE/MPU Communication                                                   | 58 |

| APPLICATION INFORMATION                                                | 59 |

| Connection of Sensors (CT, Resistive Shunt)                            | 59 |

| Temperature Measurement                                                | 60 |

| Temperature Compensation                                               | 60 |

| Temperature Compensation and Mains Frequency Stabilization for the RTC | 61 |

| Connecting 5V Devices                                                  | 62 |

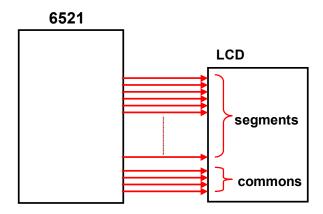

| Connecting LCDs                                                        | 63 |

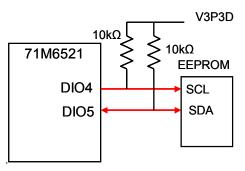

| Connecting I <sup>2</sup> C EEPROMs                                    | 65 |

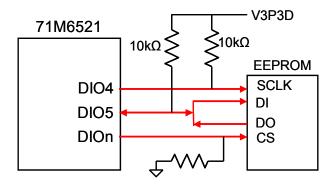

| Connecting Three-Wire EEPROMs                                          | 66 |

| UART0 (TX/RX)                                                          | 66 |

| Optical Interface                                                      | 67 |

| Connecting V1 and Reset Pins                                           | 67 |

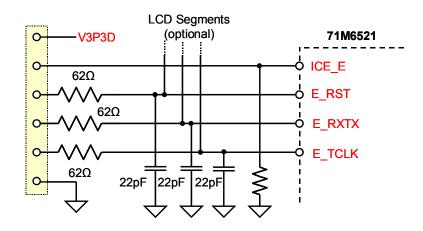

| Connecting the Emulator Port Pins                                      | 68 |

| Crystal Oscillator                                                     | 69 |

| Flash Programming                                                      | 69 |

| MPU Firmware Library                                                   | 69 |

| Meter Calibration                                                      | 69 |

| FIRMWARE INTERFACE                                                     | 70 |

| I/O RAM MAP – In Numerical Order                                       | 70 |

| SFR MAP (SFRs Specific to TERIDIAN 80515) – In Numerical Order         | 71 |

| I/O RAM DESCRIPTION – Alphabetical Order                               | 72 |

| CE Interface Description                                               | 79 |

| CE Program                                                             | 79 |

| Formats                                                                | 79 |

| Constants                                                              | 79 |

| Environment                                                            | 79 |

|                                                                        |    |

### DATASHEET JANUARY 2008

| CE Calculations                                     | 80  |

|-----------------------------------------------------|-----|

| CE STATUS                                           | 80  |

| CE TRANSFER VARIABLES                               | 82  |

| ELECTRICAL SPECIFICATIONS                           |     |

| ABSOLUTE MAXIMUM RATINGS                            | 86  |

| RECOMMENDED EXTERNAL COMPONENTS                     | 87  |

| RECOMMENDED OPERATING CONDITIONS                    | 87  |

| PERFORMANCE SPECIFICATIONS                          |     |

| INPUT LOGIC LEVELS                                  |     |

| OUTPUT LOGIC LEVELS                                 |     |

| POWER-FAULT COMPARATOR                              |     |

| BATTERY MONITOR                                     |     |

| SUPPLY CURRENT                                      |     |

| V3P3D SWITCH                                        |     |

| 2.5V VOLTAGE REGULATOR                              |     |

| LOW POWER VOLTAGE REGULATOR                         |     |

| CRYSTAL OSCILLATOR                                  | 90  |

| VREF, VBIAS                                         | 90  |

| LCD DRIVERS                                         | 90  |

| ADC CONVERTER, V3P3A REFERENCED                     | 91  |

| OPTICAL INTERFACE                                   | 91  |

| TEMPERATURE SENSOR                                  | 91  |

| TIMING SPECIFICATIONS                               | 92  |

| FLASH MEMORY TIMING                                 | 92  |

| EEPROM INTERFACE                                    | 92  |

| RESET and V1                                        | 92  |

| RTC                                                 | 92  |

| TYPICAL PERFORMANCE DATA                            | 93  |

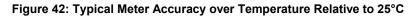

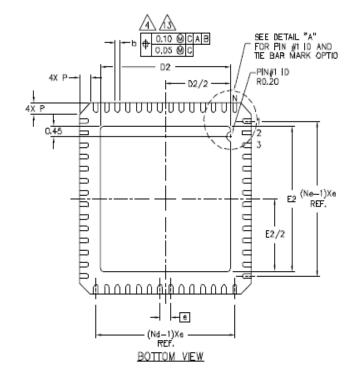

| PACKAGE OUTLINE (LQFP 64)                           | 94  |

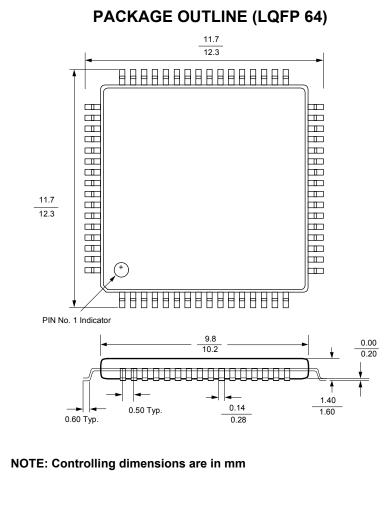

| PACKAGE OUTLINE (QFN 68)                            | 95  |

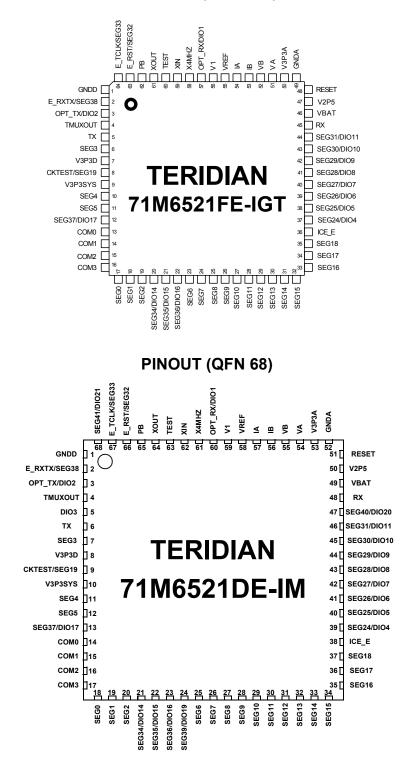

| PINOUT (LQFP-64)                                    | 96  |

| PINOUT (QFN 68)                                     | 96  |

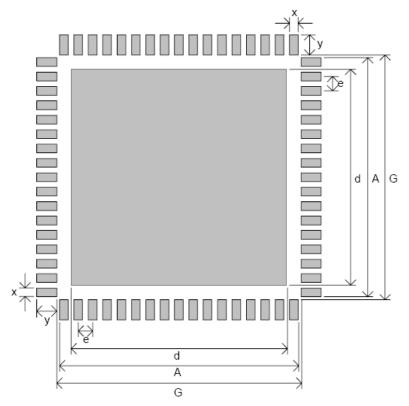

| Recommended PCB Land Pattern for the QFN-68 Package | 97  |

| PIN DESCRIPTIONS                                    |     |

| Power/Ground Pins:                                  |     |

| Analog Pins:                                        |     |

| Digital Pins:                                       |     |

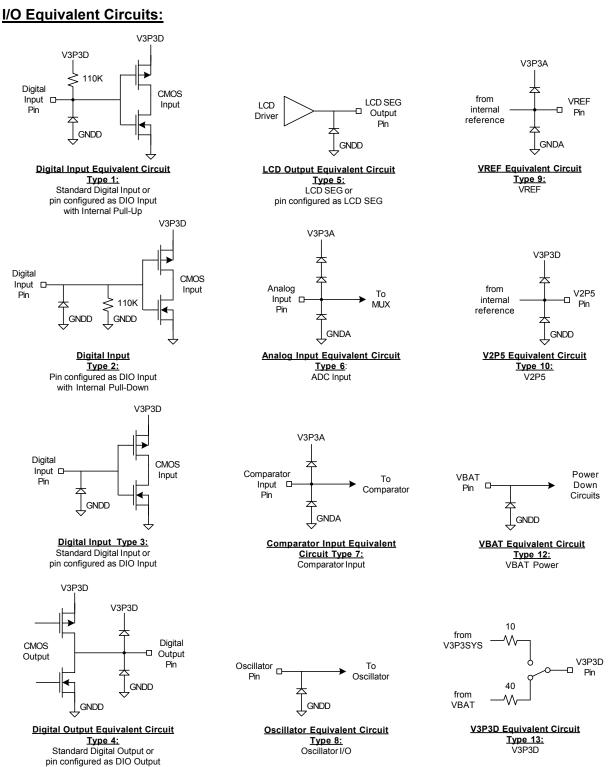

| I/O Equivalent Circuits:                            | 100 |

| ORDERING INFORMATION                                |     |

|                                                     |     |

DATASHEET

JANUARY 2008

### **List of Figures**

| 5                                                                                                |    |

|--------------------------------------------------------------------------------------------------|----|

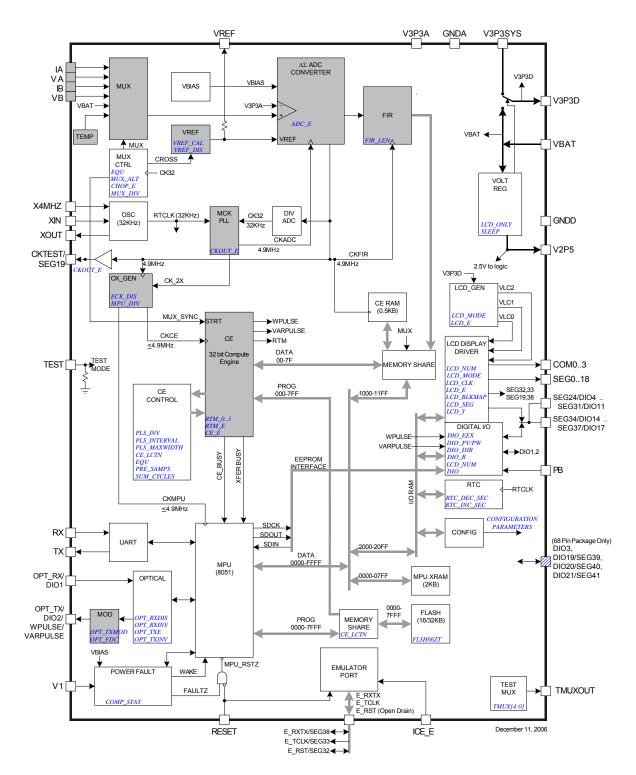

| Figure 1: IC Functional Block Diagram                                                            |    |

| Figure 2: General Topology of a Chopped Amplifier                                                |    |

| Figure 3: AFE Block Diagram                                                                      |    |

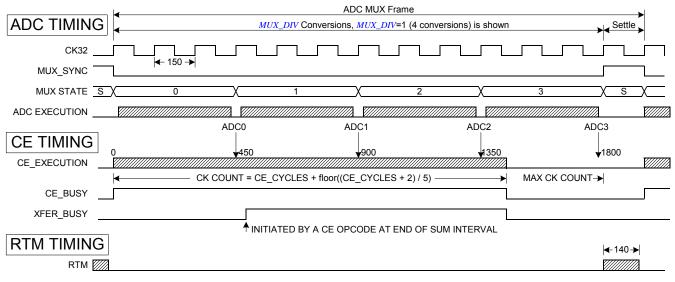

| Figure 4: Samples from Multiplexer Cycle                                                         | 15 |

| Figure 5: Accumulation Interval                                                                  | 15 |

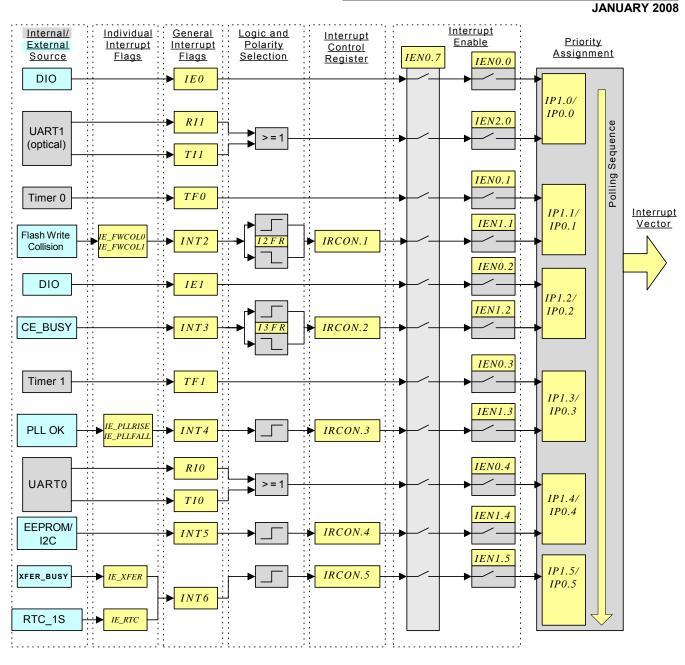

| Figure 6: Interrupt Structure                                                                    |    |

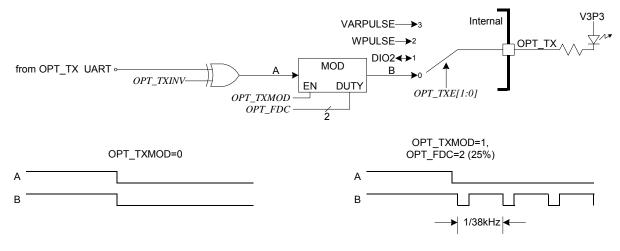

| Figure 7: Optical Interface                                                                      |    |

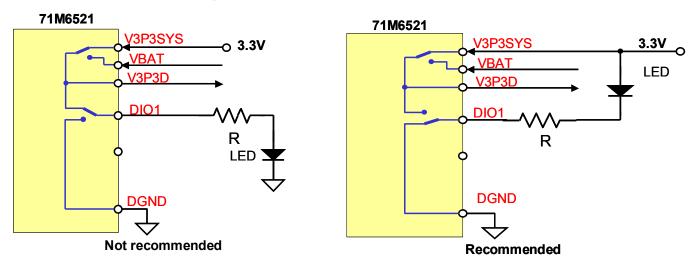

| Figure 8: Connecting an External Load to DIO Pins                                                | 41 |

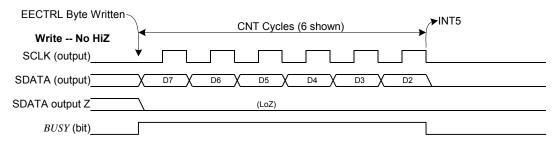

| Figure 9: 3-Wire Interface. Write Command, HiZ=0.                                                | 43 |

| Figure 10: 3-Wire Interface. Write Command, HiZ=1                                                | 44 |

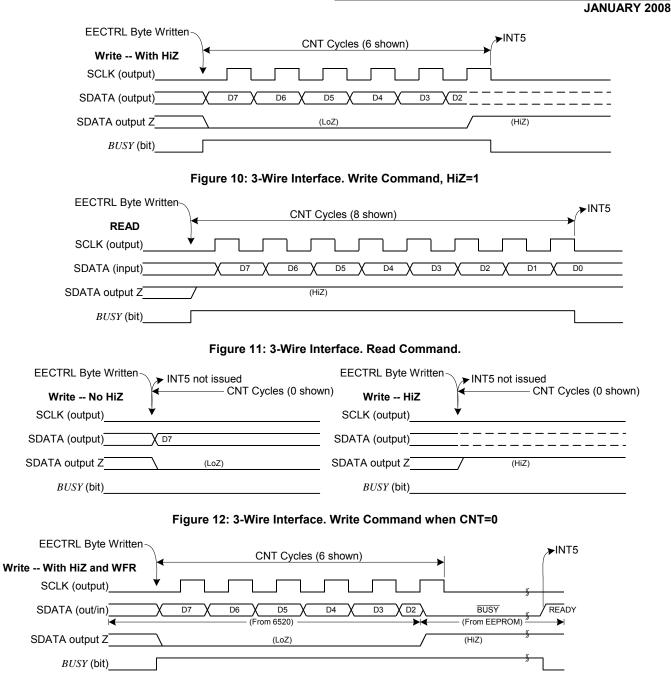

| Figure 11: 3-Wire Interface. Read Command                                                        | 44 |

| Figure 12: 3-Wire Interface. Write Command when CNT=0                                            | 44 |

| Figure 13: 3-Wire Interface. Write Command when HiZ=1 and WFR=1                                  | 44 |

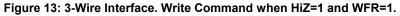

| Figure 14: Functions defined by V1                                                               | 45 |

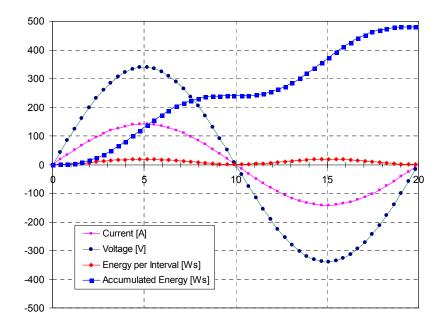

| Figure 15: Voltage. Current, Momentary and Accumulated Energy                                    | 47 |

| Figure 16: Timing Relationship between ADC MUX, Compute Engine, and Serial Transfers.            |    |

| Figure 17: RTM Output Format                                                                     |    |

| Figure 18: Operation Modes State Diagram                                                         |    |

| Figure 19: Functional Blocks in BROWNOUT Mode (inactive blocks grayed out)                       |    |

| Figure 20: Functional Blocks in LCD Mode (inactive blocks grayed out)                            |    |

| Figure 21: Functional Blocks in SLEEP Mode (inactive blocks grayed out)                          |    |

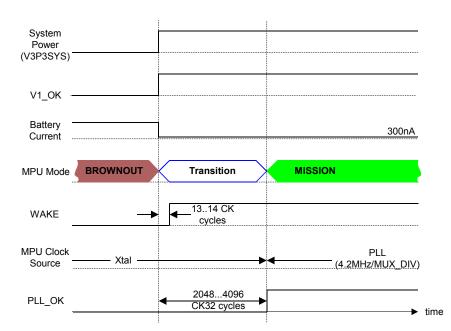

| Figure 22: Transition from BROWNOUT to MISSION Mode when System Power Returns                    |    |

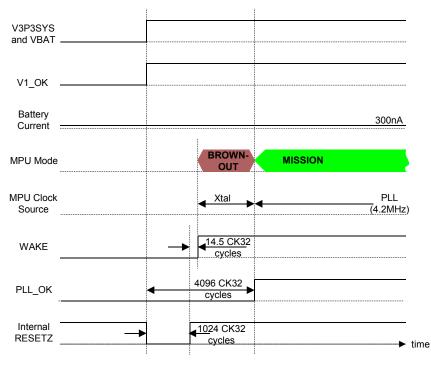

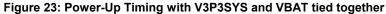

| Figure 23: Power-Up Timing with V3P3SYS and VBAT tied together                                   |    |

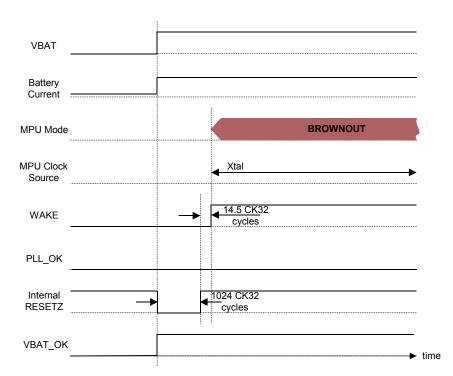

| Figure 24: Power-Up Timing with VBAT only                                                        |    |

| Figure 25: Wake Up Timing                                                                        |    |

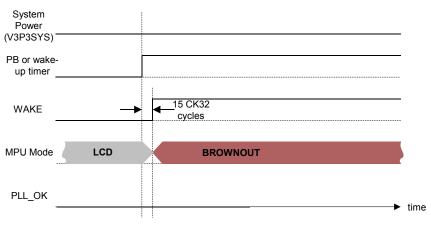

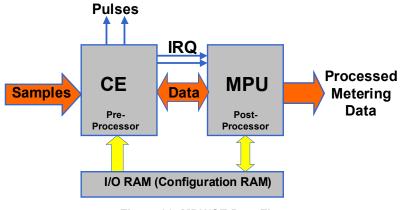

| Figure 26: MPU/CE Data Flow                                                                      |    |

| Figure 27: MPU/CE Communication                                                                  |    |

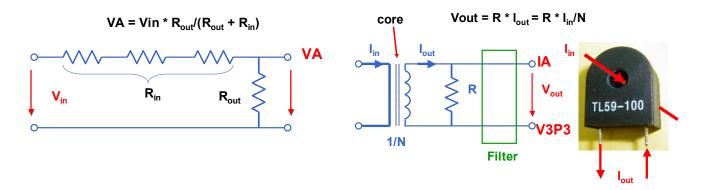

| Figure 28: Resistive Voltage Divider (Left), Current Transformer (Right)                         |    |

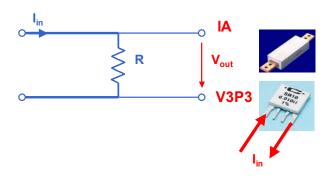

| Figure 29: Resistive Shunt                                                                       |    |

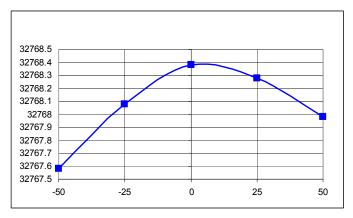

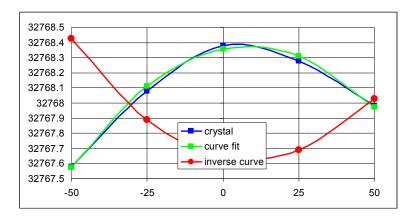

| Figure 30: Crystal Frequency over Temperature                                                    |    |

| Figure 31: Crystal Compensation                                                                  |    |

| Figure 32: Connecting LCDs                                                                       |    |

| Figure 33: I <sup>2</sup> C EEPROM Connection                                                    |    |

| Figure 34: Three-Wire EEPROM Connection                                                          |    |

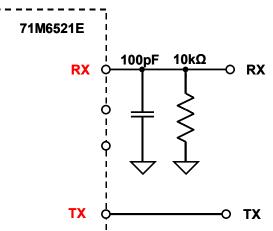

| Figure 35: Connections for the RX Pin                                                            |    |

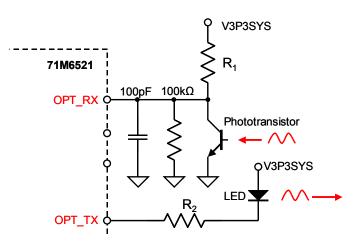

| Figure 36: Connection for Optical Components                                                     | 67 |

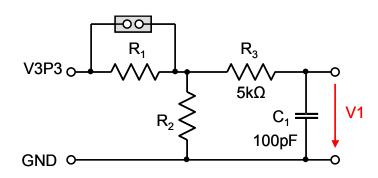

| Figure 37: Voltage Divider for V1                                                                |    |

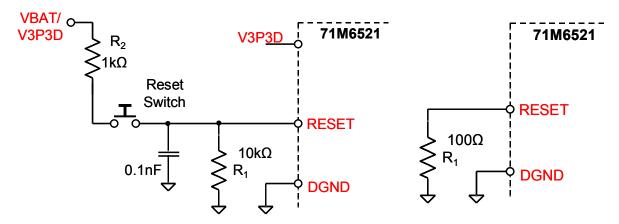

| Figure 38: External Components for the RESET Pin: Push-Button (Left), Production Circuit (Right) |    |

| Figure 39: External Components for the Emulator Interface                                        |    |

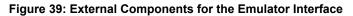

| Figure 40: Wh Accuracy, 0.1A to 200A at 240V/50Hz and Room Temperature                           |    |

|                                                                                                  |    |

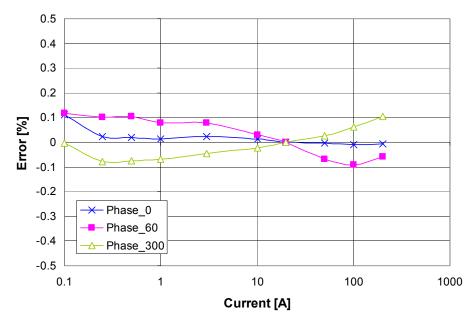

| Figure 41: Meter Accuracy over Harmonics at 240V, 30A                                            |    |

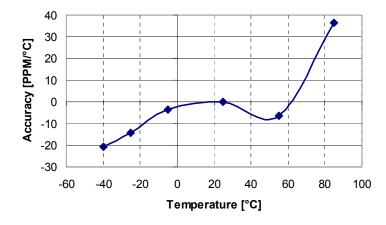

| Figure 42: Typical Meter Accuracy over Temperature Relative to 25°C                              | 94 |

DATASHEET

JANUARY 2008

### **List of Tables**

| Table 1: Inputs Selected in Regular and Alternate Multiplexer Cycles                                                   |    |

|------------------------------------------------------------------------------------------------------------------------|----|

| Table 2: CE DRAM Locations for ADC Results                                                                             |    |

| Table 3: Meter Equations.                                                                                              |    |

| Table 4: Memory Map                                                                                                    |    |

| Table 5: Stretch Memory Cycle Width                                                                                    |    |

| Table 6: Internal Data Memory Map                                                                                      |    |

| Table 7: Special Function Registers Locations                                                                          |    |

| Table 8: Special Function Registers Reset Values                                                                       | 19 |

| Table 9: PSW Register Flags                                                                                            | 20 |

| Table 10: PSW Bit Functions                                                                                            | 20 |

| Table 11: Port Registers                                                                                               | 21 |

| Table 12: Special Function Registers                                                                                   |    |

| Table 13: Baud Rate Generation                                                                                         |    |

| Table 14: UART Modes                                                                                                   | 23 |

| Table 15: The SOCON Register                                                                                           |    |

| Table 16: The S1CON register                                                                                           |    |

| Table 17: The SOCON Bit Functions                                                                                      |    |

| Table 18: The S1CON Bit Functions                                                                                      |    |

| Table 19: The TCON Register                                                                                            |    |

| Table 20: The TCON Register Bit Functions                                                                              |    |

| Table 21: The TMOD Register                                                                                            |    |

| Table 22: TMOD Register Bit Description                                                                                |    |

| Table 23: Timers/Counters Mode Description                                                                             |    |

| Table 24: Timer Modes                                                                                                  |    |

| Table 25: The PCON Register                                                                                            |    |

| Table 26: PCON Register Bit Description.                                                                               |    |

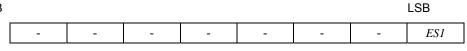

| Table 27: The <i>IENO</i> Register (see also Table 32)                                                                 |    |

| Table 28: The IENO Bit Functions (see also Table 32)         Table 20: The IENO Bit Functions (see also Tables 20/21). |    |

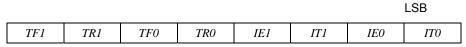

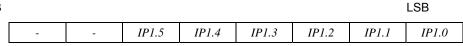

| Table 29: The IEN1 Register (see also Tables 30/31)         Table 30: The IEN1 Bit Functions (see also Tables 30/31)   |    |

|                                                                                                                        |    |

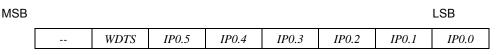

| Table 31: The IP0 Register (see also Table 45)         Table 32: The IP0 bit Functions (see also Table 45)             |    |

| Table 32: The WDTREL Register                                                                                          |    |

| Table 33: The WDTREL Register                                                                                          |    |

| Table 35: The IENO Register                                                                                            |    |

| Table 36: The IENO Bit Functions                                                                                       |    |

| Table 37: The IENI Register                                                                                            |    |

| Table 38: The IEN1 Bit Functions                                                                                       |    |

| Table 39: The IEN2 Register                                                                                            |    |

| Table 40: The IEN2 Bit Functions                                                                                       |    |

| Table 41: The TCON Register                                                                                            |    |

| Table 42: The TCON Bit Functions                                                                                       |    |

| Table 43: The T2CON Bit Functions                                                                                      |    |

| Table 44: The IRCON Register                                                                                           |    |

| Table 45: The IRCON Bit Functions                                                                                      |    |

| Table 45: External MPU Interrupts                                                                                      |    |

|                                                                                                                        |    |

# DATASHEET

JANUARY 2008

| Table 46: Interrupt Enable and Flag Bits    33                                 |

|--------------------------------------------------------------------------------|

| Table 48: Priority Level Groups   34                                           |

| Table 49: The IPO Register                                                     |

| Table 50: The IP1 Register:                                                    |

| Table 51: Priority Levels                                                      |

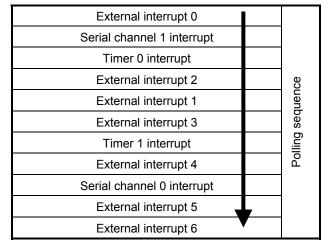

| Table 52: Interrupt Polling Sequence                                           |

| Table 53: Interrupt Vectors                                                    |

| Table 54: Data/Direction Registers and Internal Resources for DIO Pin Groups40 |

| Table 55: DIO_DIR Control Bit                                                  |

| Table 56: Selectable Controls using the DIO_DIR Bits                           |

| Table 57: EECTRL Status Bits                                                   |

| Table 58: EECTRL bits for 3-wire interface                                     |

| Table 59: TMUX[4:0] Selections                                                 |

| Table 60: Available Circuit Functions ("—" means "not active)                  |

| Table 61: Frequency over Temperature                                           |

| Table 62: LCD and DIO Pin Assignment by LCD_NUM for the QFN-68 Package         |

| Table 63: LCD and DIO Pin Assignment by LCD_NUM for the LQFP-64 Package        |

DATASHEET JANUARY 2008

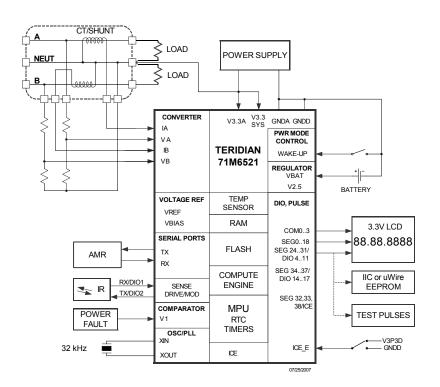

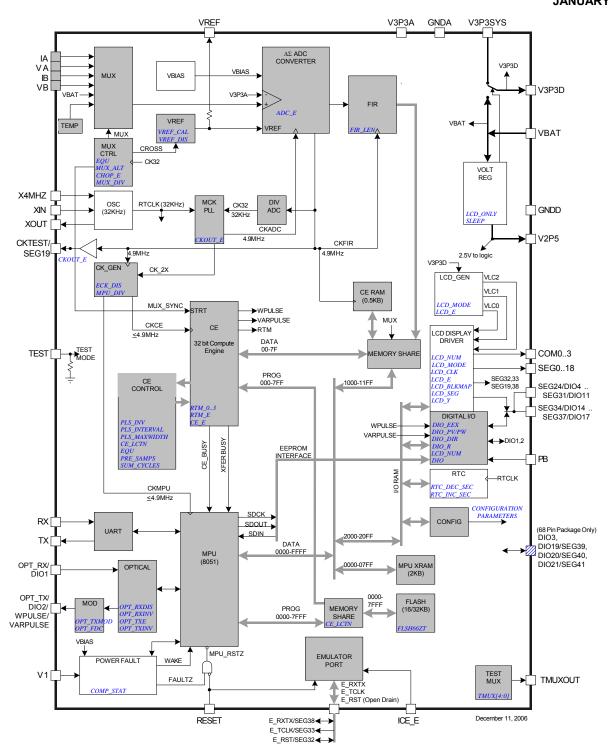

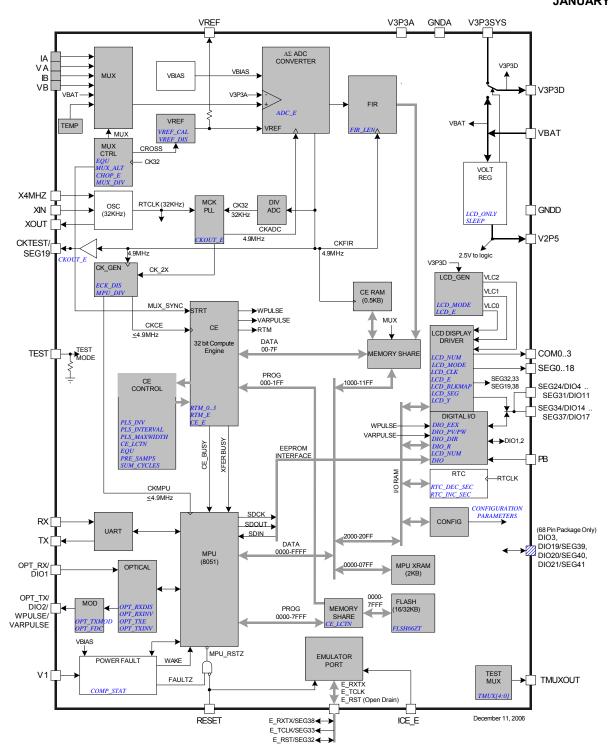

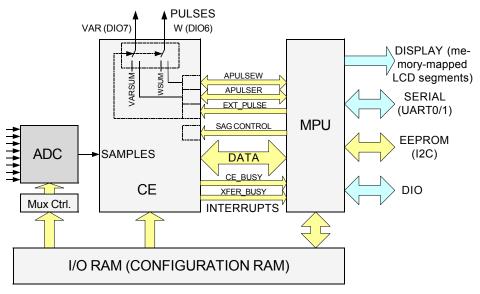

Figure 1: IC Functional Block Diagram

Page: 8 of 101

DATASHEET JANUARY 2008

### HARDWARE DESCRIPTION

### **Hardware Overview**

The TERIDIAN 71M6521DE/FE single-chip energy meter integrates all primary functional blocks required to implement a solidstate electricity meter. Included on chip are an analog front end (AFE), an independent digital computation engine (CE), an 8051-compatible microprocessor (MPU) which executes one instruction per clock cycle (80515), a voltage reference, a temperature sensor, LCD drivers, RAM, Flash memory, a real time clock (RTC), and a variety of I/O pins. Various current sensor technologies are supported including Current Transformers (CT), and Resistive Shunts.

In a typical application, the 32-bit compute engine (CE) of the 71M6521DE/FE sequentially processes the samples from the voltage inputs on pins IA, VA, IB, VB and performs calculations to measure active energy (Wh), reactive energy (VARh),  $A^{2}h$ , and  $V^{2}h$  for four-quadrant metering. These measurements are then accessed by the MPU, processed further and output using the peripheral devices available to the MPU.

In addition to advanced measurement functions, the real time clock function allows the 71M6521DE/FE to record time of use (TOU) metering information for multi-rate applications and to time-stamp tamper events. Measurements can be displayed on 3.3V LCD commonly used in low temperature environments. Flexible mapping of LCD display segments will facilitate integration of existing custom LCD. Design trade-off between number of LCD segments vs. DIO pins can be implemented in software to accommodate various requirements.

In addition to the temperature-trimmed ultra-precision voltage reference, the on-chip digital temperature compensation mechanism includes a temperature sensor and associated controls for correction of unwanted temperature effects on measurement and RTC accuracy, e.g. to meet the requirements of ANSI and IEC standards. Temperature dependent external components such as crystal oscillator, current transformers (CTs), and their corresponding signal conditioning circuits can be characterized and their correction factors can be programmed to produce electricity meters with exceptional accuracy over the industrial temperature range.

One of the two internal UARTs is adapted to support an Infrared LED with internal drive and sense configuration, and can also function as a standard UART. The optical output can be modulated at 38kHz. This flexibility makes it possible to implement AMR meters with an IR interface. A block diagram of the IC is shown in Figure 1. A detailed description of various functional blocks follows.

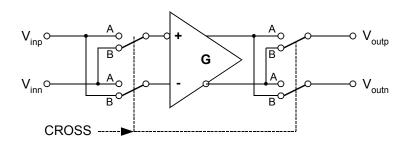

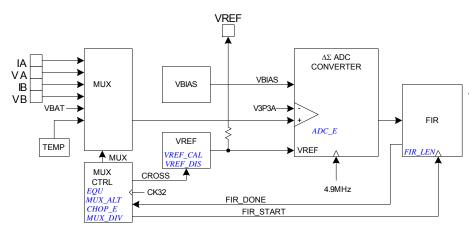

### Analog Front End (AFE)

The AFE of the 71M6521DE/FE is comprised of an input multiplexer, a delta-sigma A/D converter and a voltage reference.

### Input Multiplexer

The input multiplexer supports up to four input signals that are applied to pins IA, VA, IB and VB of the device. Additionally, using the alternate mux selection, it has the ability to select temperature and the battery voltage. The multiplexer can be operated in two modes:

- During a normal multiplexer cycle, the signals from the IA, IB, VA, and VB pins are selected.

- During the alternate multiplexer cycle, the temperature signal (TEMP) and the battery monitor are selected, along with the signal sources shown in Table 1. To prevent unnecessary drainage on the battery, the battery monitor is enabled only with the *BME* bit (0x2020[6]) in the I/O RAM.

The alternate mux cycles are usually performed infrequently (e.g. every second) by the MPU. In order to prevent disruption of the voltage tracking PLL and voltage allpass networks, VA is not replaced in the ALT mux selections. Table 1 details the regular and alternative MUX sequences. Missing samples due to an ALT multiplexer sequence are filled in by the CE.

DATASHEET JANUARY 2008

|         | Reg       | ular MUX | Sequen | се | Α    | LT MUX S | Sequence |      |

|---------|-----------|----------|--------|----|------|----------|----------|------|

|         | Mux State |          |        |    |      | Mux S    | state    |      |

| EQU     | 0         | 1        | 2      | 3  | 0    | 1        | 2        | 3    |

| 0, 1, 2 | IA        | VA       | IB     | VB | TEMP | VA       | IB       | VBAT |

#### Table 1: Inputs Selected in Regular and Alternate Multiplexer Cycles

In a typical application, IA and IB are connected to current transformers that sense the current on each phase of the line voltage. VA and VB are typically connected to voltage sensors through resistor dividers.

The multiplexer control circuit handles the setting of the multiplexer. The function of the control circuit is governed by the I/O RAM registers *MUX\_ALT*, *MUX\_DIV* and *EQU*. *MUX\_DIV* controls the number of samples per cycle. It can request 2, 3, or 4 multiplexer states per cycle. Multiplexer states above 4 are reserved and must not be used. The multiplexer always starts at the beginning of its list and proceeds until *MUX\_DIV* states have been converted.

The *MUX\_ALT* bit requests an alternative multiplexer frame. The bit may be asserted on any MPU cycle and may be subsequently de-asserted on any cycle including the next one. A rising edge on *MUX\_ALT* will cause the multiplexer control circuit to wait until the next multiplexer cycle and implement a single alternate cycle.

The multiplexer control circuit also controls the FIR filter initiation and the chopping of the ADC reference voltage, VREF. The multiplexer control circuit is clocked by CK32, the 32768Hz clock from the PLL block, and launches with each new pass of the CE program.

### A/D Converter (ADC)

A single delta-sigma A/D converter digitizes the voltage and current inputs to the 71M6521DE/FE. The resolution of the ADC is programmable using the *FIR\_LEN* register as shown in the I/O RAM section. ADC resolution can be selected to be 21 bits (*FIR\_LEN=*0), or 22 bits (*FIR\_LEN=*1). Conversion time is two cycles of CK32 with *FIR\_LEN =* 0 and three cycles with *FIR\_LEN =* 1.

In order to provide the maximum resolution, the ADC should be operated with  $FIR\_LEN = 1$ . Accuracy and timing specifications in this data sheet are based on  $FIR\_LEN = 1$ .

Initiation of each ADC conversion is controlled by the multiplexer control circuit as described previously. At the end of each ADC conversion, the FIR filter output data is stored into the CE DRAM location determined by the multiplexer selection.

#### FIR Filter

The finite impulse response filter is an integral part of the ADC and it is optimized for use with the multiplexer. The purpose of the FIR filter is to decimate the ADC output to the desired resolution. At the end of each ADC conversion, the output data is stored into the fixed CE DRAM location determined by the multiplexer selection. FIR data is stored LSB justified, but shifted left by nine bits.

### Voltage References

The device includes an on-chip precision bandgap voltage reference that incorporates auto-zero techniques. The reference is trimmed to minimize errors caused by component mismatch and drift. The result is a voltage output with a predictable temperature coefficient.

The amplifier within the reference is chopper stabilized, i.e. the polarity can be switched by the MPU using the I/O RAM register  $CHOP_E$  (0x2002[5:4]). The two bits in the  $CHOP_E$  register enable the MPU to operate the chopper circuit in regular or inverted operation, or in "toggling" mode. When the chopper circuit is toggled in between multiplexer cycles, DC offsets on the measured signals will automatically be averaged out.

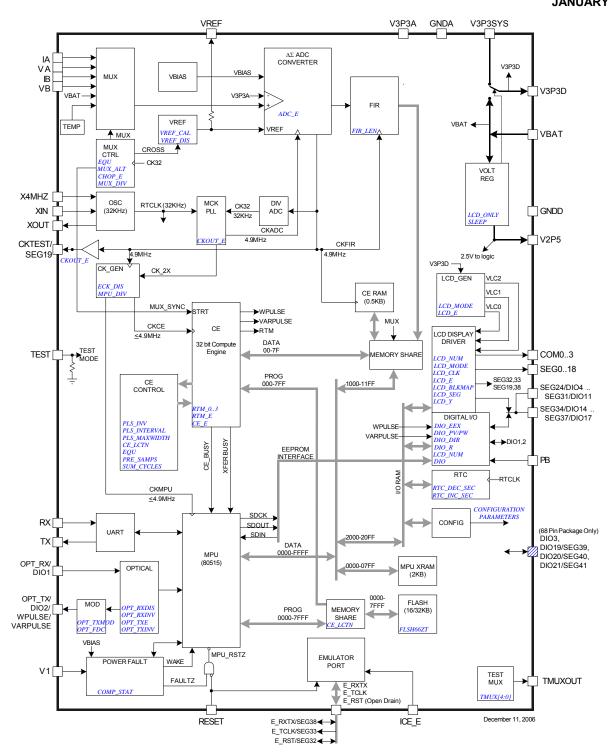

The general topology of a chopped amplifier is given in Figure 2.

DATASHEET JANUARY 2008

#### Figure 2: General Topology of a Chopped Amplifier

It is assumed that an offset voltage Voff appears at the positive amplifier input. With all switches, as controlled by CROSS in the "A" position, the output voltage is:

Voutp – Voutn = G (Vinp + Voff – Vinn) = G (Vinp – Vinn) + G Voff

With all switches set to the "B" position by applying the inverted CROSS signal, the output voltage is:

Voutn – Voutp = G (Vinn – Vinp + Voff) = G (Vinn – Vinp) + G Voff, or

Voutp - Voutn = G (Vinp - Vinn) - G Voff

Thus, when CROSS is toggled, e.g. after each multiplexer cycle, the offset will alternately appear on the output as positive and negative, which results in the offset effectively being eliminated, regardless of its polarity or magnitude.

When CROSS is high, the hookup of the amplifier input devices is reversed. This preserves the overall polarity of that amplifier gain, it inverts its input offset. By alternately reversing the connection, the amplifier's offset is averaged to zero. This removes the most significant long-term drift mechanism in the voltage reference. The *CHOP\_E* bits control the behavior of CROSS. The CROSS signal will reverse the amplifier connection in the voltage reference in order to negate the effects of its offset. On the first CK32 rising edge after the last mux state of its sequence, the mux will wait one additional CK32 cycle before beginning a new frame. At the beginning of this cycle, the value of CROSS will be updated according to the *CHOP\_E* bits. The extra CK32 cycle allows time for the chopped VREF to settle. During this cycle, MUXSYNC is held high. The leading edge of muxsync initiates a pass through the CE program sequence. The beginning of the sequence is the serial readout of the 4 RTM words.

*CHOP\_E* has 3 states: positive, reverse, and chop. In the 'positive' state, CROSS is held low. In the 'reverse' state, CROSS is held high. In the 'chop' state, CROSS is toggled near the end of each Mux Frame, as described above. It is desirable that CROSS take on alternate values at the beginning of each Mux cycle. For this reason, if 'chop' state is selected, CROSS will not toggle at the end of the last Mux cycle in a SUM cycle.

The internal bias voltage VBIAS (typically 1.6V) is used by the ADC when measuring the temperature and battery monitor signals.

### **Temperature Sensor**

The 71M6521DE/FE includes an on-chip temperature sensor implemented as a bandgap reference. It is used to determine the die temperature The MPU may request an alternate multiplexer cycle containing the temperature sensor output by asserting *MUX\_ALT*.

The primary use of the temperature data is to determine the magnitude of compensation required to offset the thermal drift in the system (see section titled "Temperature Compensation").

DATASHEET

### **Battery Monitor**

The battery voltage is measured by the ADC during alternative multiplexer frames if the *BME* (Battery Measure Enable) bit in the I/O RAM is set. While *BME* is set, an on-chip  $45k\Omega$  load resistor is applied to the battery, and a scaled fraction of the battery voltage is applied to the ADC input. After each alternative MUX frame, the result of the ADC conversion is available at CE DRAM address 07. *BME* is ignored and assumed zero when system power is not available (V1 < VBIAS). See the Battery Monitor section of the Electrical Specifications for details regarding the ADC LSB size and the conversion accuracy.

### **Functional Description**

The AFE functions as a data acquisition system, controlled by the MPU. The main signals (IA, VA, IB, VB) are sampled and the ADC counts obtained are stored in CE DRAM where they can be accessed by the CE and, if necessary, by the MPU. Alternate multiplexer cycles are initiated less frequently by the MPU to gather access to the slow temperature and battery signals.

#### Figure 3: AFE Block Diagram

### **Digital Computation Engine (CE)**

The CE, a dedicated 32-bit signal processor, performs the precision computations necessary to accurately measure energy. The CE calculations and processes include:

- Multiplication of each current sample with its associated voltage sample to obtain the energy per sample (when multiplied with the constant sample time).

- Frequency-insensitive delay cancellation on all six channels (to compensate for the delay between samples caused by the multiplexing scheme).

- 90° phase shifter (for VAR calculations).

- Pulse generation.

- Monitoring of the input signal frequency (for frequency and phase information).

- Monitoring of the input signal amplitude (for sag detection).

- Scaling of the processed samples based on calibration coefficients.

The CE program resides in flash memory. Common access to flash memory by CE and MPU is controlled by a memory share circuit. Each CE instruction word is two bytes long. Allocated flash space for the CE program cannot exceed 1024 words (2KB). The CE program counter begins a pass through the CE code each time multiplexer state 0 begins. The code pass ends

JANUARY 2008

DATASH

when a HALT instruction is executed. For proper operation, the code pass must be completed before the multiplexer cycle ends (see System Timing Summary in the Functional Description Section).

The CE program must begin on a 1Kbyte boundary of the flash address. The I/O RAM register *CE\_LCTN[4:0]* defines which 1KB boundary contains the CE code. Thus, the first CE instruction is located at 1024\**CE\_LCTN[4:0]*.

The CE DRAM can be accessed by the FIR filter block, the RTM circuit, the CE, and the MPU. Assigned time slots are reserved for FIR, RTM, and MPU, respectively, to prevent bus contention for CE DRAM data access. Holding registers are used to convert 8-bit wide MPU data to/from 32-bit wide CE DRAM data, and wait states are inserted as needed, depending on the frequency of CKMPU.

The CE DRAM contains 128 32-bit words. The MPU can read and write the CE DRAM as the primary means of data communication between the two processors.

| ADDRESS (HEX) | NAME | DESCRIPTION     |

|---------------|------|-----------------|

| 00            | IA   | Phase A current |

| 01            | VA   | Phase A voltage |

| 02            | IB   | Phase B current |

| 03            | VB   | Phase B voltage |

| 04            | -    | Not used        |

| 05            | -    | Not used        |

| 06            | TEMP | Temperature     |

| 07            | VBAT | Battery Voltage |

Table 2 shows the CE DRAM addresses allocated to analog inputs from the AFE.

#### Table 2: CE DRAM Locations for ADC Results

The CE of the 71M6521DE/FE is aided by support hardware that facilitates implementation of equations, pulse counters, and accumulators. This support hardware is controlled through I/O RAM locations EQU (equation assist),  $DIO_PV$  and  $DIO_PW$  (pulse count assist), and  $PRE_SAMPS$  and  $SUM_CYCLES$  (accumulation assist).  $PRE_SAMPS$  and  $SUM_CYCLES$  support a dual level accumulation scheme where the first accumulator accumulates results from  $PRE_SAMPS$  samples and the second accumulator accumulates up to  $SUM_CYCLES$  of the first accumulator results. The integration time for each energy output is  $PRE_SAMPS * SUM_CYCLES/2520.6$  (with  $MUX_DIV = 1$ ). CE hardware issues the XFER\_BUSY interrupt when the accumulation is complete.

### **Meter Equations**

Compute Engine (CE) firmware and hardware for residential meter configurations implement the equations listed in Table 3. The register EQU (located in the I/O RAM) specifies the equation to be used based on the number of phases used for metering.

| EQU | Description                                                                                    | Watt & VAR  | Formula   |

|-----|------------------------------------------------------------------------------------------------|-------------|-----------|

| LQU |                                                                                                | Element 0   | Element 1 |

| 0   | 1 element, 2W 1 $\phi$ with neutral current sense<br>and tamper detection (VA connected to VB) | VA IA       | VA IB     |

| 1   | 1 element, 3W 1o                                                                               | VA(IA-IB)/2 | N/A       |

| 2   | 2 element, 4W 2∳                                                                               | VA IA       | VB IB     |

Table 3: Meter Equations.

DATASHEET JANUARY 2008

### **Real-Time Monitor**

The CE contains a Real-Time Monitor (RTM), which can be programmed through the UART to monitor four selectable CE DRAM locations at full sample rate. The four monitored locations are serially output to the TMUXOUT pin via the digital output multiplexer at the beginning of each CE code pass. The RTM can be enabled and disabled with *RTM\_EN*. The RTM output is clocked by CKTEST. Each RTM word is clocked out in 35 cycles and contains a leading flag bit. See the Functional Description section for the RTM output format. RTM is low when not in use.

### Pulse Generator

The chip contains two pulse generators that create low-jitter pulses at a rate set by either CE or MPU. The function is distinguished by *EXT\_PULSE* (a CE input variable in CE DRAM):

- If *EXT\_PULSE* = 1, *APULSEW*\**WRATE* and *APULSER*\**WRATE* control the pulse rate (external pulse generation)

- If *EXT\_PULSE* is 0, *APULSEW* is replaced with *WSUM\_X* and *APULSER* is replaced with *VARSUM\_X* (internal pulse generation).

The I/O RAM bits *DIO\_PV* and *DIO\_PW*, as described in the Digital I/O section, can be programmed to route WPULSE to the output pin DIO6 and VARPULSE to the output pin DIO7. Pulses can also be output on OPT\_TX (see *OPT\_TXE[1:0]* for details).

During each CE code pass, the hardware stores exported sign bits in an 8-bit FIFO and outputs them at a specified interval. This permits the CE code to calculate all of the pulse generator outputs at the beginning of its code pass and to rely on hardware to spread them over the MUX frame. The FIFO is reset at the beginning of each MUX frame. *PLS\_INTERVAL* controls the delay to the first pulse update and the interval between subsequent updates. Its LSB is four CK\_FIR cycles, or 4 \* 203ns. If *PLS\_INTERVAL* is zero, the FIFO is deactivated and the pulse outputs are updated immediately. Thus, NINTERVAL is *4\*PLS\_INTERVAL*.

For use with the standard CE code supplied by TERIDIAN, *PLS\_INTERVAL* is set to a fixed value of 81. *PLS\_INTERVAL* is specified so that all of the pulse updates are output <u>before</u> the MUX frame completes.

On-chip hardware provides a maximum pulse width feature:  $PLS_MAXWIDTH[7:0]$  selects a maximum negative pulse width to be 'Nmax' updates per multiplexer cycle according to the formula: Nmax = (2\**PLS\_MAXWIDTH*+1). If *PLS\_MAXWIDTH* = 255, no width checking is performed.

Given that *PLS\_INTERVAL* = 81, the maximum pulse width is determined by:

Maximum Pulse Width = (2 \* *PLS\_MAXWIDTH* +1) \* 81\*4\*203ns = 65.9µs + *PLS\_MAXWIDTH* \* 131.5µs

If the pulse period corresponding to the pulse rate exceeds the desired pulse width, a square wave with 50% duty-cycle is generated.

The CE pulse output polarity is programmable to be either positive or negative. Pulse polarity may be inverted with *PLS\_INV*. When this bit is set, the pulses are active high, rather than the more usual active low.

### **CE Functional Overview**

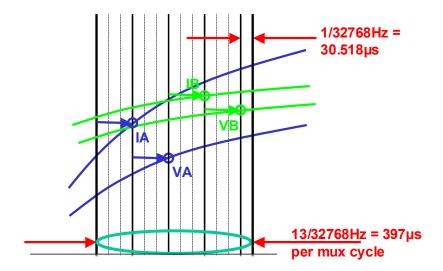

The ADC processes one sample per channel per multiplexer cycle. Figure 4 shows the timing of the samples taken during one multiplexer cycle.

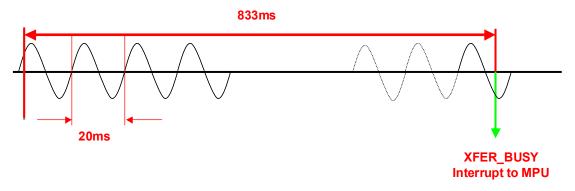

The number of samples processed during one accumulation cycle is controlled by the I/O RAM registers *PRE\_SAMPS* (0x2001[7:6]) and *SUM\_CYCLES* (0x2001[5:0]). The integration time for each energy output is

PRE\_SAMPS \* SUM\_CYCLES / 2520.6, where 2520.6 is the sample rate [Hz]

For example, *PRE\_SAMPS* = 42 and *SUM\_CYCLES* = 50 will establish 2100 samples per accumulation cycle. *PRE\_SAMPS* = 100 and *SUM\_CYCLES* = 21 will result in the exact same accumulation cycle of 2100 samples or 833ms. After an accumulation cycle is completed, the XFER\_BUSY interrupt signals to the MPU that accumulated data are available.

DATASHEET JANUARY 2008

Figure 4: Samples from Multiplexer Cycle

The end of each multiplexer cycle is signaled to the MPU by the CE\_BUSY interrupt. At the end of each multiplexer cycle, status information, such as sag data and the digitized input signal, is available to the MPU.

#### Figure 5: Accumulation Interval

Figure 5 shows the accumulation interval resulting from  $PRE\_SAMPS$  = 42 and  $SUM\_CYCLES$  = 50, consisting of 2100 samples of 397µs each, followed by the XFER\_BUSY interrupt. The sampling in this example is applied to a 50Hz signal.

There is no correlation between the line signal frequency and the choice of *PRE\_SAMPS* or *SUM\_CYCLES* (even though when *SUM\_CYCLES* = 42 one set of *SUM\_CYCLES* happens to sample a period of 16.6ms). Furthermore, sampling does not have to start when the line voltage crosses the zero line, and the length of the accumulation interval need not be an integer multiple of the signal cycles.

It is important to note that the length of the accumulation interval, as determined by  $N_{ACC}$ , the product of *SUM\_CYCLES* and *PRE\_SAMPS*, is not an exact multiple of 1000ms. For example, if *SUM\_CYCLES* = 60, and *PRE\_SAMPS* = 00 (42), the resulting accumulation interval is:

$$\tau = \frac{N_{ACC}}{f_s} = \frac{\frac{60 \cdot 42}{32768Hz}}{\frac{32768Hz}{13}} = \frac{2520}{2520.62Hz} = 999.75ms$$

This means that accurate time measurements should be based on the RTC, not the accumulation interval.

DATASHEET JANUARY 2008

### 80515 MPU Core

The 71M6521DE/FE includes an 80515 MPU (8-bit, 8051-compatible) that processes most instructions in one clock cycle. Using a 5MHz clock results in a processing throughput of 5 MIPS. The 80515 architecture eliminates redundant bus states and implements parallel execution of fetch and execution phases. Normally a machine cycle is aligned with a memory fetch, therefore, most of the 1-byte instructions are performed in a single cycle. This leads to an 8x performance (in average) improvement (in terms of MIPS) over the Intel 8051 device running at the same clock frequency.

Actual processor clocking speed can be adjusted to the total processing demand of the application (metering calculations, AMR management, memory management, LCD driver management and I/O management) using the I/O RAM register *MPU\_DIV[2:0]*.

Typical measurement and metering functions based on the results provided by the internal 32-bit compute engine (CE) are available for the MPU as part of TERIDIAN's standard library. A standard ANSI "C" 80515-application programming interface library is available to help reduce design cycle.

### Memory Organization

The 80515 MPU core incorporates the Harvard architecture with separate code and data spaces.

Memory organization in the 80515 is similar to that of the industry standard 8051. There are three memory areas: Program memory (Flash), external data memory (XRAM), physically consisting of XRAM, CE DRAM, and I/O RAM, and internal data memory (Internal RAM). Table 4 shows the memory map.

| Address<br>(hex)                    | Memory<br>Technology | Memory Type  | Typical Usage                         | Wait States<br>(at 5MHz) | Memory Size<br>(bytes) |

|-------------------------------------|----------------------|--------------|---------------------------------------|--------------------------|------------------------|

| 0000-7FFF<br>0000-3FFF<br>0000-1FFF | Flash Memory         | Non-volatile | MPU Program and non-<br>volatile data | 0                        | 32K<br>16K<br>8K       |

| on 1K<br>boundary                   | Flash Memory         | Non-volatile | CE program                            | 0                        | 2K                     |

| 0000-07FF                           | Static RAM           | Volatile     | MPU data XRAM,                        | 0                        | 2K                     |

| 1000-11FF                           | Static RAM           | Volatile     | CE data                               | 6                        | 512                    |

| 2000-20FF                           | Static RAM           | Volatile     | Configuration RAM<br>I/O RAM          | 0                        | 256                    |

#### Table 4: Memory Map

**Internal and External Data Memory:** Both internal and external data memory are physically located on the 71M6521DE/FE IC. "External" data memory is only external to the 80515 MPU core.

**Program Memory:** The 80515 can theoretically address up to 64KB of program memory space from 0x0000 to 0xFFFF. Program memory is read when the MPU fetches instructions or performs a MOVC operation.

After reset, the MPU starts program execution from location 0x0000. The lower part of the program memory includes reset and interrupt vectors. The interrupt vectors are spaced at 8-byte intervals, starting from 0x0003.

External Data Memory: While the 80515 is capable of addressing up to 64KB of external data memory (0x0000 to 0xFFFF), only the memory ranges shown in Table 4: Memory Map

**contain physical memory.** The 80515 writes into external data memory when the MPU executes a MOVX @Ri,A or MOVX @DPTR,A instruction. The MPU reads external data memory by executing a MOVX A,@Ri or MOVX A,@DPTR instruction (SFR USR2 provides the upper 8 bytes for the MOVX A,@Ri instruction).

**Clock Stretching:** MOVX instructions can access fast or slow external RAM and external peripherals. The three low order bits of the *CKCON* register define the stretch memory cycles. Setting all the *CKCON* stretch bits to one allows access to very slow external RAM or external peripherals.

Table 5 shows how the signals of the External Memory Interface change when stretch values are set from 0 to 7. The widths of the signals are counted in MPU clock cycles. The post-reset state of the CKCON register, which is in bold in the table, performs the MOVX instructions with a stretch value equal to 1.

| CI      | KCON regist | er      | Stretch Value | Read signals width |       | Write sig | nal width |

|---------|-------------|---------|---------------|--------------------|-------|-----------|-----------|

| CKCON.2 | CKCON.1     | CKCON.0 |               | memaddr            | memrd | memaddr   | memwr     |

| 0       | 0           | 0       | 0             | 1                  | 1     | 2         | 1         |

| 0       | 0           | 1       | 1             | 2                  | 2     | 3         | 1         |

| 0       | 1           | 0       | 2             | 3                  | 3     | 4         | 2         |

| 0       | 1           | 1       | 3             | 4                  | 4     | 5         | 3         |

| 1       | 0           | 0       | 4             | 5                  | 5     | 6         | 4         |

| 1       | 0           | 1       | 5             | 6                  | 6     | 7         | 5         |

| 1       | 1           | 0       | 6             | 7                  | 7     | 8         | 6         |

| 1       | 1           | 1       | 7             | 8                  | 8     | 9         | 7         |

#### Table 5: Stretch Memory Cycle Width

There are two types of instructions, differing in whether they provide an eight-bit or sixteen-bit indirect address to the external data RAM.

In the first type (MOVX A,@Ri), the contents of R0 or R1, in the current register bank, provide the eight lower-ordered bits of address. The eight high-ordered bits of address are specified with the *USR2* SFR. This method allows the user paged access (256 pages of 256 bytes each) to all ranges of the external data RAM. In the second type of MOVX instruction (MOVX A,@DPTR), the data pointer generates a sixteen-bit address. This form is faster and more efficient when accessing very large data arrays (up to 64 Kbytes), since no additional instructions are needed to set up the eight high ordered bits of address.

It is possible to mix the two MOVX types. This provides the user with four separate data pointers, two with direct access and two with paged access to the entire 64KB of external memory range.

**Dual Data Pointer:** The Dual Data Pointer accelerates the block moves of data. The standard DPTR is a 16-bit register that is used to address external memory or peripherals. In the 80515 core, the standard data pointer is called DPTR, the second data pointer is called DPTR1. The data pointer select bit chooses the active pointer. The data pointer select bit is located at the LSB of the *DPS* register (*DPS.0*). *DPTR* is selected when *DPS.0* = 0 and *DPTR1* is selected when *DPS.0* = 1.

The user switches between pointers by toggling the LSB of the DPS register. All data pointer-related instructions use the currently selected data pointer for any activity.

#### The second data pointer may not be supported by certain compilers.

**Internal Data Memory:** The Internal data memory provides 256 bytes (0x00 to 0xFF) of data memory. The internal data memory address is always 1 byte wide and can be accessed by either direct or indirect addressing. The Special Function Registers occupy the upper 128 bytes. This SFR area is available only by direct addressing. Indirect addressing accesses the upper 128 bytes of Internal RAM.

DATASHEET JANUARY 2008

**Internal Data Memory:** The lower 128 bytes contain working registers and bit-addressable memory. The lower 32 bytes form four banks of eight registers (R0-R7). Two bits on the program memory status word (PSW) select which bank is in use. The next 16 bytes form a block of bit-addressable memory space at bit addressees 0x00-0x7F. All of the bytes in the lower 128 bytes are accessible through direct or indirect addressing. Table 6 shows the internal data memory map.

| Address | Direct addressing          | Indirect addressing |  |  |

|---------|----------------------------|---------------------|--|--|

| 0xFF    | Special Function Registers | RAM                 |  |  |

| 0x80    | (SFRs)                     | RAW                 |  |  |

| 0x7F    | Bvte-ado                   | Iressable area      |  |  |

| 0x30    |                            |                     |  |  |

| 0x2F    | Bit-addressable area       |                     |  |  |

| 0x20    |                            |                     |  |  |

| 0x1F    | Pogistor                   | hanka P0 P7         |  |  |

| 0x00    | Register                   | banks R0…R7         |  |  |

#### Table 6: Internal Data Memory Map

### Special Function Registers (SFRs)

A map of the Special Function Registers is shown in Table 7.

| Hex\Bin | Bit-address-<br>able | Byte-addressable |         |        |       |        |        |        | Bin/Hex |

|---------|----------------------|------------------|---------|--------|-------|--------|--------|--------|---------|

|         | X000                 | X001             | X010    | X011   | X100  | X101   | X110   | X111   |         |

| F8      | INTBITS              |                  |         |        |       |        |        |        | FF      |

| F0      | В                    |                  |         |        |       |        |        |        | F7      |

| E8      | WDI                  |                  |         |        |       |        |        |        | EF      |

| E0      | Α                    |                  |         |        |       |        |        |        | E7      |

| D8      | WDCON                |                  |         |        |       |        |        |        | DF      |

| D0      | PSW                  |                  |         |        |       |        |        |        | D7      |

| C8      | T2CON                |                  |         |        |       |        |        |        | CF      |

| C0      | IRCON                |                  |         |        |       |        |        |        | C7      |

| B8      | IENI                 | IP1              | SORELH  | SIRELH |       |        |        | USR2   | BF      |

| B0      |                      |                  | FLSHCTL |        |       |        |        | PGADR  | B7      |

| A8      | IENO                 | IP0              | SORELL  |        |       |        |        |        | AF      |

| A0      | P2                   | DIR2             | DIR0    |        |       |        |        |        | A7      |

| 98      | SOCON                | SOBUF            | IEN2    | SICON  | SIBUF | SIRELL | EEDATA | EECTRL | 9F      |

| 90      | P1                   | DIR1             | DPS     |        | ERASE |        |        |        | 97      |

| 88      | TCON                 | TMOD             | TLO     | TL1    | TH0   | TH1    | CKCON  |        | 8F      |

| 80      | PO                   | SP               | DPL     | DPH    | DPL1  | DPH1   | WDTREL | PCON   | 87      |

#### Table 7: Special Function Registers Locations

Only a few addresses are occupied, the others are not implemented. SFRs specific to the 652X are shown in **bold** print. Any read access to unimplemented addresses will return undefined data, while any write access will have no effect. The registers at 0x80, 0x88, 0x90, etc., are bit-addressable, all others are byte-addressable.

DATASHEET JANUARY 2008

### Special Function Registers (Generic 80515 SFRs)

Table 8 shows the location of the SFRs and the value they assume at reset or power-up.

| Name   | Location | Reset value | Description                                        |  |

|--------|----------|-------------|----------------------------------------------------|--|

| P0     | 0x80     | 0xFF        | Port 0                                             |  |

| SP     | 0x81     | 0x07        | Stack Pointer                                      |  |

| DPL    | 0x82     | 0x00        | Data Pointer Low 0                                 |  |

| DPH    | 0x83     | 0x00        | Data Pointer High 0                                |  |

| DPL1   | 0x84     | 0x00        | Data Pointer Low 1                                 |  |

| DPH1   | 0x85     | 0x00        | Data Pointer High 1                                |  |

| WDTREL | 0x86     | 0x00        | Watchdog Timer Reload register                     |  |

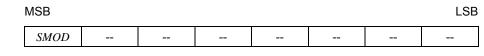

| PCON   | 0x87     | 0x00        | UART Speed Control                                 |  |

| TCON   | 0x88     | 0x00        | Timer/Counter Control                              |  |

| TMOD   | 0x89     | 0x00        | Timer Mode Control                                 |  |

| TLO    | 0x8A     | 0x00        | Timer 0, low byte                                  |  |

| TLI    | 0x8B     | 0x00        | Timer 1, high byte                                 |  |

| TH0    | 0x8C     | 0x00        | Timer 0, low byte                                  |  |

| TH1    | 0x8D     | 0x00        | Timer 1, high byte                                 |  |

| CKCON  | 0x8E     | 0x01        | Clock Control (Stretch=1)                          |  |

| P1     | 0x90     | 0xFF        | Port 1                                             |  |

| DPS    | 0x92     | 0x00        | Data Pointer select Register                       |  |

| SOCON  | 0x98     | 0x00        | Serial Port 0, Control Register                    |  |

| SOBUF  | 0x99     | 0x00        | Serial Port 0, Data Buffer                         |  |

| IEN2   | 0x9A     | 0x00        | Interrupt Enable Register 2                        |  |

| SICON  | 0x9B     | 0x00        | Serial Port 1, Control Register                    |  |

| SIBUF  | 0x9C     | 0x00        | Serial Port 1, Data Buffer                         |  |

| SIRELL | 0x9D     | 0x00        | Serial Port 1, Reload Register, low byte           |  |

| P2     | 0xA0     | 0x00        | Port 2                                             |  |

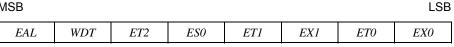

| IEN0   | 0xA8     | 0x00        | Interrupt Enable Register 0                        |  |

| IP0    | 0xA9     | 0x00        | Interrupt Priority Register 0                      |  |

| SORELL | 0xAA     | 0xD9        | Serial Port 0, Reload Register, low byte           |  |

| IENI   | 0xB8     | 0x00        | Interrupt Enable Register 1                        |  |

| IP1    | 0xB9     | 0x00        | Interrupt Priority Register 1                      |  |

| SORELH | 0xBA     | 0x03        | Serial Port 0, Reload Register, high byte          |  |

| SIRELH | 0xBB     | 0x03        | Serial Port 1, Reload Register, high byte          |  |

| USR2   | 0xBF     | 0x00        | User 2 Port, high address byte for MOVX@Ri         |  |

| IRCON  | 0xC0     | 0x00        | Interrupt Request Control Register                 |  |

| T2CON  | 0xC8     | 0x00        | Polarity for INT2 and INT3                         |  |

| PSW    | 0xD0     | 0x00        | Program Status Word                                |  |

| WDCON  | 0xD8     | 0x00        | Baud Rate Control Register (only WDCON.7 bit used) |  |

| Α      | 0xE0     | 0x00        | Accumulator                                        |  |

| В      | 0xF0     | 0x00        | B Register                                         |  |

**Table 8: Special Function Registers Reset Values**

DATASHE **JANUARY 2008**

Accumulator (ACC, A): ACC is the accumulator register. Most instructions use the accumulator to hold the operand. The mnemonics for accumulator-specific instructions refer to accumulator as "A", not ACC.

B Register: The B register is used during multiply and divide instructions. It can also be used as a scratch-pad register to hold temporary data.

Program Status Word (PSW):

| MSB |    |    |     |    |    |   | LSB | ; |

|-----|----|----|-----|----|----|---|-----|---|

| CV  | AC | FO | RS1 | RS | OV | - | Р   | 1 |

Table 9: PSW Register Flags

| Bit     | Symbol | Function            | on                                  |                            |                                 |        |  |

|---------|--------|---------------------|-------------------------------------|----------------------------|---------------------------------|--------|--|

| PSW.7   | CV     | Carry fl            | ag                                  |                            |                                 |        |  |

| PSW.6   | AC     | Auxiliar            | ry Carry flag fo                    | r BCD operations           |                                 |        |  |

| PSW.5   | FO     | Genera              | al purpose Flag                     | g 0 available for user.    |                                 |        |  |

|         |        |                     |                                     |                            | F0 flag in the CE STATUS reg    |        |  |

| PSW.4   | RS1    | Registe<br>register |                                     | control bits. The contents | of RS1 and RS0 select the wor   | king   |  |

|         |        |                     | RS1/RS0                             | Bank selected              | Location                        |        |  |

| DCII/ 2 | DCO    | _                   | 00                                  | Bank 0                     | (0x00 – 0x07)                   |        |  |

| PSW.3   | RSO    |                     | 01                                  | Bank 1                     | (0x08 – 0x0F)                   |        |  |

|         |        |                     | 10                                  | Bank 2                     | (0x10 – 0x17)                   |        |  |

|         |        |                     | 11                                  | Bank 3                     | (0x18 – 0x1F)                   |        |  |

| PSW.2   | OV     | Overflo             | w flag                              |                            |                                 |        |  |

| PSW.1   | -      | User de             | User defined flag                   |                            |                                 |        |  |

| PSW.0   | Р      |                     | lag, affected b<br>ulator, i.e. eve |                            | d / even number of "one" bits i | in the |  |

#### Table 10: PSW Bit Functions

Stack Pointer (SP): The stack pointer is a 1-byte register initialized to 0x07 after reset. This register is incremented before PUSH and CALL instructions, causing the stack to begin at location 0x08.

Data Pointer: The data pointer (DPTR) is 2 bytes wide. The lower part is DPL, and the highest is DPH. It can be loaded as two registers (e.g. MOV DPL,#data8). It is generally used to access external code or data space (e.g. MOVC A,@A+DPTR or MOVX A,@DPTR respectively).

Program Counter: The program counter (PC) is 2 bytes wide initialized to 0x0000 after reset. This register is incremented when fetching operation code or when operating on data from program memory.

### DATASHEET

#### JANUARY 2008

**Port Registers:** The I/O ports are controlled by Special Function Registers *P0*, *P1*, and *P2*. The contents of the SFR can be observed on corresponding pins on the chip. Writing a '1' to any of the ports (see Table 11) causes the corresponding pin to be at high level (V3P3), and writing a '0' causes the corresponding pin to be held at low level (GND). The data direction registers *DIR0*, *DIR1*, and *DIR2* define individual pins as input or output pins (see section Digital I/O for details).

| Register  | SFR<br>Address | R/W | Description                                                                                           |

|-----------|----------------|-----|-------------------------------------------------------------------------------------------------------|

| <i>P0</i> | 0x80           | R/W | Register for port 0 read and write operations (pins DIO4DIO7)                                         |

| DIRO      | 0xA2           | R/W | Data direction register for port 0. Setting a bit to 1 means that the corresponding pin is an output. |

| P1        | 0x90           | R/W | Register for port 1 read and write operations (pins DIO8DIO11, DIO14-DIO15)                           |

| DIR1      | 0x91           | R/W | Data direction register for port 1.                                                                   |

| P2        | 0xA0           | R/W | Register for port 2 read and write operations (pins DIO16DIO17, DIO19DIO21)                           |

| DIR2      | 0xA1           | R/W | Data direction register for port 2.                                                                   |

#### **Table 11: Port Registers**

All DIO ports on the chip are bi-directional. Each of them consists of a Latch (SFR 'P0' to 'P2'), an output driver, and an input buffer, therefore the MPU can output or read data through any of these ports. Even if a DIO pin is configured as an output, the state of the pin can still be read by the MPU, for example when counting pulses issued via DIO pins that are under

CE control.

The technique of reading the status of or generating interrupts based on DIO pins configured as outputs, can be used to implement pulse counting.

### Special Function Registers Specific to the 71M6521DE/FE

Table 12 shows the location and description of the 71M6521DE/FE-specific SFRs.

| Register | Alternative<br>Name | SFR<br>Address | R/W | Description                                                                                                                                                                                                                                                                                                                                                                     |  |

|----------|---------------------|----------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ERASE    | FLSH_ERASE          | 0x94           | W   | This register is used to initiate either the Flash Mass Erase cycle or the Flash Page Erase cycle. Specific patterns are expected for <i>FLSH_ERASE</i> in order to initiate the appropriate Erase cycle (default = 0x00).                                                                                                                                                      |  |

|          |                     |                |     | 0x55 – Initiate Flash Page Erase cycle. Must be preceded by a write to <i>FLSH_PGADR</i> @ SFR 0xB7.                                                                                                                                                                                                                                                                            |  |

|          |                     |                |     | 0xAA – Initiate Flash Mass Erase cycle. Must be preceded by a write to <i>FLSH_MEEN</i> @ SFR 0xB2 and the debug port must be enabled.                                                                                                                                                                                                                                          |  |

|          |                     |                |     | Any other pattern written to FLSH_ERASE will have no effect.                                                                                                                                                                                                                                                                                                                    |  |

| PGADDR   | FLSH_PGADR          | 0xB7           | R/W | Flash Page Erase Address register containing the flash memory page address (page 0 thru 127) that will be erased during the Page Erase cycle (default = 0x00).                                                                                                                                                                                                                  |  |

|          |                     |                |     | Must be re-written for each new Page Erase cycle.                                                                                                                                                                                                                                                                                                                               |  |

| EEDATA   |                     | 0x9E           | R/W | I <sup>2</sup> C EEPROM interface data register                                                                                                                                                                                                                                                                                                                                 |  |

| EECTRL   |                     | 0x9F           | R/W | I <sup>2</sup> C EEPROM interface control register. If the MPU wishes to write a byte of data to EEPROM, it places the data in <i>EEDATA</i> and then writes the 'Transmit' code to <i>EECTRL</i> . The write to <i>EECTRL</i> initiates the transmit sequence. See the EEPROM Interface section for a description of the command and status bits available for <i>EECTRL</i> . |  |

DATASHEET

JANUARY 2008

| FLSHCRL |          | 0xB2 |     | Dit 0 (ELSU, DWE): Program Write Enchlo:                                                                                                                                                                                                                                                                                             |

|---------|----------|------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FLSHCKL |          | UXB2 | R/W | Bit 0 (FLSH_PWE): Program Write Enable:         0 – MOVX commands refer to XRAM Space, normal operation (default).         1 – MOVX @DPTR,A moves A to Program Space (Flash) @         DPTR.         This bit is automatically reset after each byte written to flash. Writes to this bit are inhibited when interrupts are enabled. |

|         |          |      | W   | Bit 1 (FLSH_MEEN): Mass Erase Enable:<br>0 – Mass Erase disabled (default).<br>1 – Mass Erase enabled.<br>Must be re-written for each new Mass Erase cycle.                                                                                                                                                                          |

|         |          |      | R/W | Bit 6 (SECURE):<br>Enables security provisions that prevent external reading of flash<br>memory and CE program RAM. This bit is reset on chip reset and<br>may only be set. Attempts to write zero are ignored.                                                                                                                      |

|         |          |      | R   | Bit 7 (PREBOOT):<br>Indicates that the preboot sequence is active.                                                                                                                                                                                                                                                                   |

| WDI     |          | 0xE8 | R/W | Only byte operations on the whole WDI register<br>should be used when writing. The byte must have all<br>bits set except the bits that are to be cleared.                                                                                                                                                                            |

|         |          |      | R/W | The multi-purpose register <i>WDI</i> contains the following bits:<br><u>Bit 0 (<i>IE_XFER</i>): XFER Interrupt Flag:</u><br>This flag monitors the XFER_BUSY interrupt. It is set by hardware<br>and must be cleared by the interrupt handler                                                                                       |

|         |          |      | W   | Bit 1 (IE_RTC): RTC Interrupt Flag:<br>This flag monitors the RTC_1SEC interrupt. It is set by hardware and<br>must be cleared by the interrupt handler                                                                                                                                                                              |

|         |          |      |     | Bit 7 (WD_RST): WD Timer Reset:<br>Read: Reads the PLL_FALL interrupt flag<br>Write 0: Clears the PLL_FALL interrupt flag<br>Write 1: Resets the watch dog timer                                                                                                                                                                     |

| INTBITS | INT0INT6 | 0xF8 | R   | Interrupt inputs. The MPU may read these bits to see the input to external interrupts INT0, INT1, up to INT6. These bits do not have any memory and are primarily intended for debug use                                                                                                                                             |

#### **Table 12: Special Function Registers**

### **Instruction Set**

All instructions of the generic 8051 microcontroller are supported. A complete list of the instruction set and of the associated op-codes is contained in the 71M6521 Software User's Guide (SUG).

### <u>UART</u>

The 71M6521DE/FE includes a UART (UART0) that can be programmed to communicate with a variety of AMR modules. A second UART (UART1) is connected to the optical port, as described in the optical port description.

DATAS **JANUARY 2008**

The UARTs are dedicated 2-wire serial interfaces, which can communicate with an external host processor at up to 38,400 bits/s (with MPU clock = 1.2288MHz). The operation of each pin is as follows:

**RX**: Serial input data are applied at this pin. Conforming to RS-232 standard, the bytes are input LSB first.

TX: This pin is used to output the serial data. The bytes are output LSB first.

The 71M6521DE/FE has several UART-related registers for the control and buffering of serial data. All UART transfers are programmable for parity enable, parity, 2 stop bits/1 stop bit and XON/XOFF options for variable communication baud rates from 300 to 38400 bps. Table 13 shows how the baud rates are calculated. Table 14 shows the selectable UART operation modes.

|        | Using Timer 1                                              | Using Internal Baud Rate Generator                                      |

|--------|------------------------------------------------------------|-------------------------------------------------------------------------|