### **DUAL P-CHANNEL MATCHED MOSFET PAIR**

© 1998 Advanced Linear Devices, Inc. 415 Tasman Drive, Sunnyvale, California 94089 -1706 Tel: (408) 747-1155 Fax: (408) 747-1286 http://www.aldinc.com

#### **GENERAL DESCRIPTION**

The ALD1102 is a monolithic dual P-channel matched transistor pair intended for a broad range of analog applications. These enhancement-mode transistors are manufactured with Advanced Linear Devices' enhanced ACMOS silicon gate CMOS process.

The ALD1102 offers high input impedance and negative current temperature coefficient. The transistor pair is matched for minimum offset voltage and differential thermal response, and it is designed for switching and amplifying applications in +2V to +12V systems where low input bias current, low input capacitance and fast switching speed are desired. Since these are MOSFET devices, they feature very large (almost infinite) current gain in a low frequency, or near DC operating environment. When used with an ALD1101, a dual CMOS analog switch can be constructed. In addition, the ALD1102 is intended as a building block for differential amplifier input stages, transmission gates, and multiplexer applications.

The ALD1102 is suitable for use in precision applications which require very high current gain, beta, such as current mirrors and current sources. The high input impedance and the high DC current gain of the Field Effect Transistors result in extremely low current loss through the control gate. The DC current gain is limited by the gate input leakage current, which is specified at 50pA at room temperature. For example, DC beta of the device at a drain current of 5mA at 25°C is = 5mA/50pA = 100,000,000.

### **FEATURES**

- · Low threshold voltage of 0.7V

- · Low input capacitance

- Low Vos grades -- 2mV, 5mV, 10mV

- High input impedance -- 10<sup>12</sup>Ω typical

- · Low input and output leakage currents

- Negative current (IDS) temperature coefficient

- Enhancement-mode (normally off)

- DC current gain 10<sup>9</sup>

### **ORDERING INFORMATION**

| Operating Temperature Range* |                                          |                          |  |  |  |  |  |  |  |

|------------------------------|------------------------------------------|--------------------------|--|--|--|--|--|--|--|

| -55°C to +125°C              | 0°C to +70°C                             | 0°C to +70°C             |  |  |  |  |  |  |  |

| 8-Pin<br>CERDIP<br>Package   | 8-Pin<br>Plastic Dip<br>Package          | 8-Pin<br>SOIC<br>Package |  |  |  |  |  |  |  |

| ALD1102 DA                   | ALD1102A PA<br>ALD1102B PA<br>ALD1102 PA | ALD1102 SA               |  |  |  |  |  |  |  |

<sup>\*</sup> Contact factory for industrial temperature range.

### **APPLICATIONS**

- Precision current mirrors

- · Precision current sources

- Analog switches

- Choppers

- Differential amplifier input stage

- · Voltage comparator

- Data converters

- · Sample and Hold

- · Analog inverter

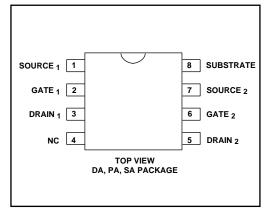

### **PIN CONFIGURATION**

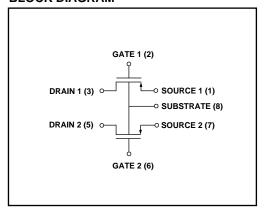

### **BLOCK DIAGRAM**

© 1998 Advanced Linear Devices, Inc. 415 Tasman Drive, Sunnyvale, California 94089 -1706 Tel: (408) 747-1155 Fax: (408) 747-1286 http://www.aldinc.com

## **ABSOLUTE MAXIMUM RATINGS**

| Drain-source voltage, VDS    |                | -13.2V          |

|------------------------------|----------------|-----------------|

| Gate-source voltage, VGS     |                | 13.2V           |

| Power dissipation            |                | 500 mW          |

| Operating temperature range  | PA, SA package | 0°C to +70°C    |

|                              | DA package     | 55°C to +125°C  |

| Storage temperature range —  |                | -65°C to +150°C |

| Lead temperature, 10 seconds | :              | +260°C          |

# **OPERATING ELECTRICAL CHARACTERISTICS**

# $T_A = 25$ °C unless otherwise specified

|                                           |                      | 1102A |      | 1102B    |      | 1102 |          |      | Test |          |          |                                                                      |

|-------------------------------------------|----------------------|-------|------|----------|------|------|----------|------|------|----------|----------|----------------------------------------------------------------------|

| Parameter                                 | Symbol               | Min   | Тур  | Max      | Min  | Тур  | Max      | Min  | Тур  | Max      | Unit     | Conditions                                                           |

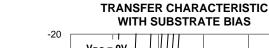

| Gate Threshold<br>Voltage                 | V <sub>T</sub>       | -0.4  | -0.7 | -1.2     | -0.4 | -0.7 | -1.2     | -0.4 | -0.7 | -1.2     | V        | $I_{DS} = -10\mu A V_{GS} = V_{DS}$                                  |

| Offset Voltage<br>VGS1 - VGS2             | V <sub>OS</sub>      |       |      | 2        |      |      | 5        |      |      | 10       | mV       | $I_{DS} = -100\mu A V_{GS} = V_{DS}$                                 |

| Gate Threshold<br>Temperature Drift       | TC <sub>VT</sub>     |       | -1.3 |          |      | -1.3 |          |      | -1.3 |          | mV/°C    |                                                                      |

| On Drain Current                          | IDS (ON)             | -8    | -16  |          | -8   | -16  |          | -8   | -16  |          | mA       | VGS = VDS = -5V                                                      |

| Transconductance                          | G <sub>fs</sub>      | 2     | 4    |          | 2    | 4    |          | 2    | 4    |          | mmho     | $V_{DS} = -5V I_{DS} = -10mA$                                        |

| Mismatch                                  | $\Delta G_fs$        |       | 0.5  |          |      | 0.5  |          |      | 0.5  |          | %        |                                                                      |

| Output<br>Conductance                     | G <sub>OS</sub>      |       | 500  |          |      | 500  |          |      | 500  |          | μmho     | V <sub>DS</sub> = -5V I <sub>DS</sub> = -10mA                        |

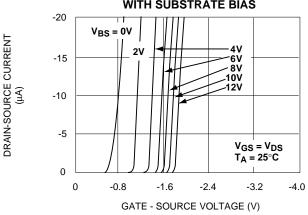

| Drain Source<br>ON Resistance             | RDS(ON)              |       | 180  | 270      |      | 180  | 270      |      | 180  | 270      | Ω        | V <sub>DS</sub> = -0.1V V <sub>GS</sub> = -5V                        |

| Drain Source<br>ON Resistance<br>Mismatch | ΔR <sub>DS(ON)</sub> |       | 0.5  |          |      | 0.5  |          |      | 0.5  |          | %        | V <sub>DS</sub> = -0.1V V <sub>GS</sub> = -5V                        |

| Drain Source<br>Breakdown<br>Voltage      | BV <sub>DSS</sub>    | -12   |      |          | -12  |      |          | -12  |      |          | <b>V</b> | I <sub>DS</sub> = -10μΑ V <sub>GS</sub> =0V                          |

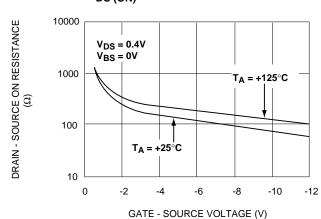

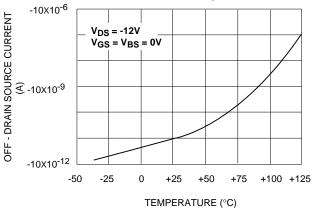

| Off Drain Current                         | IDS(OFF)             |       | 0.1  | 4<br>4   |      | 0.1  | 4<br>4   |      | 0.1  | 4<br>4   | nA<br>μA | V <sub>DS</sub> =-12V V <sub>GS</sub> = 0V<br>T <sub>A</sub> = 125°C |

| Gate Leakage<br>Current                   | I <sub>GSS</sub>     |       | 1    | 50<br>10 |      | 1    | 50<br>10 |      | 1    | 50<br>10 | pA<br>nA | V <sub>DS</sub> =0V V <sub>GS</sub> =-12V<br>T <sub>A</sub> = 125°C  |

| Input<br>Capacitance                      | Ciss                 |       | 6    | 10       |      | 6    | 10       |      | 6    | 10       | pF       |                                                                      |

## TYPICAL PERFORMANCE CHARACTERISITCS

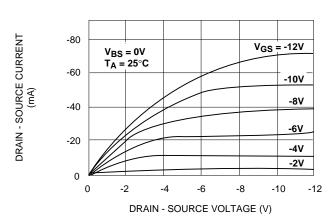

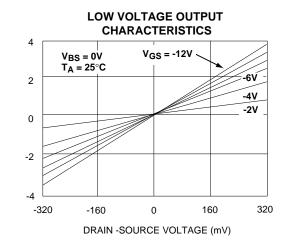

### **OUTPUT CHARACTERISTICS**

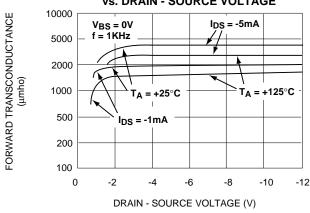

### FORWARD TRANSCONDUCTANCE vs. DRAIN - SOURCE VOLTAGE

# R<sub>DS</sub> (ON) vs. GATE - SOURCE VOLTAGE

# **OFF DRAIN - CURRENT vs. TEMPERATURE**

ALD1102A/ALD1102B ALD1102

**Advanced Linear Devices**

3