January 2007

# LP5952 350mA Dual Rail Linear Regulator

### **General Description**

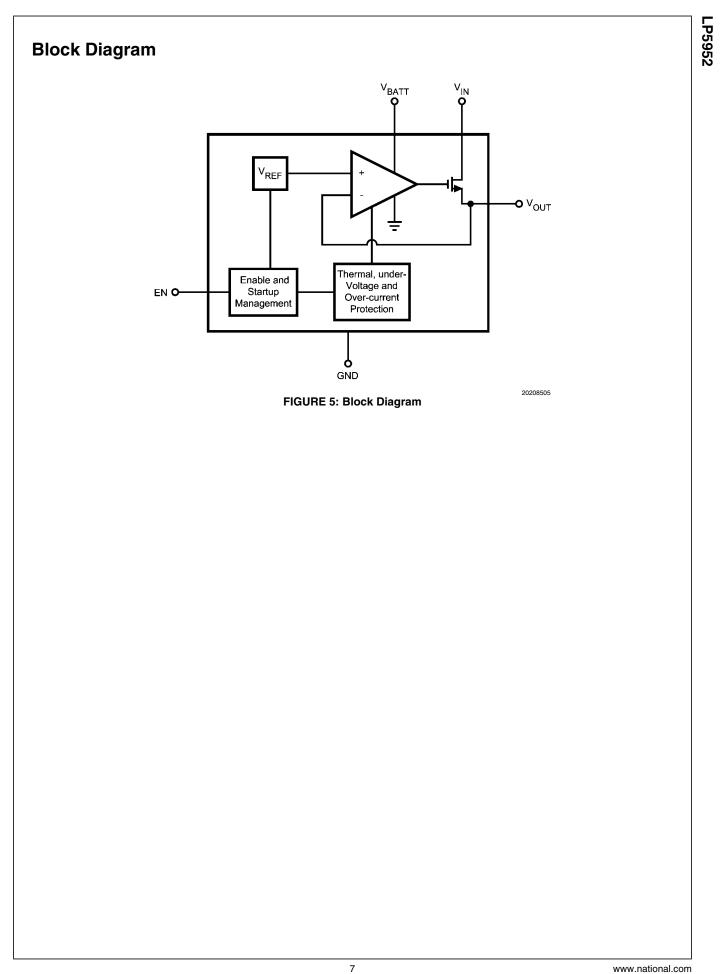

The LP5952 is a Dual Supply Rail Linear Regulator optimized for powering ultra-low voltage circuits from a single Li-lon cell or 3 cell NiMH/NiCd batteries.

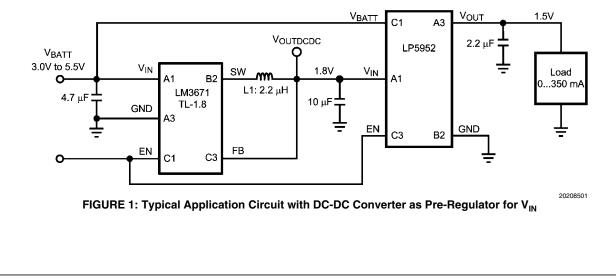

In the typical post regulation application  $\mathsf{V}_{\mathsf{BATT}}$  is directly connected to the battery (range 2.5V...5.5V) and  $\rm V_{IN}$  is supplied by the output voltage of the DC-DC Converter (range 0.7V... 4.5V).

The device offers superior dropout and transient features combined with very low quiescent currents. In shutdown mode (Enable pin pulled low) the device turns off and reduces battery consumption to 0.1µA (typ.).

The LP5952 also features internal protection against overtemperature, over-current and under-voltage conditions.

Performance is specified for a -40°C to 125°C junction temperature range.

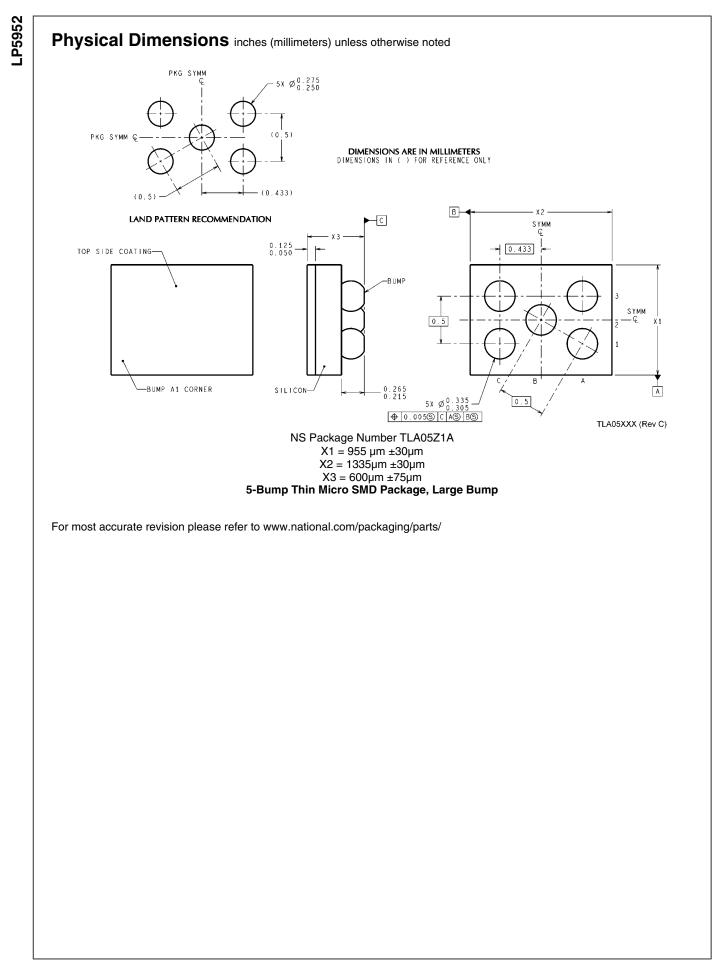

The LP5952 is available in a micro SMD package, lead free.

The device is available in fixed output voltages in the range of 0.5V to 2.0V. For availability, please contact your local NSC sales office.

### Features

- Excellent load transient response: ±15mV typical

- -Excellent line transient response: ±1mV typical

- $0.7V \le V_{IN} \le 4.5V$

- $2.5 \mathrm{V} \leq \mathrm{V}_{\mathrm{BATT}} \leq 5.5 \mathrm{V}$

- $0.5V \le V_{OUT} \le 2.0V$

- For I<sub>LOAD</sub> = 350mA:  $V_{BATT} \ge V_{OUT(NOM)} + 1.5V$  or 2.5V whichever is higher For  $I_{LOAD} = 150$  mA:

- $V_{BATT} \ge V_{OUT(NOM)} + 1.3V$  or 2.5V whichever is higher

- 50µA typical quiescent current from V<sub>BATT</sub>

- 10µA typical quiescent current from V<sub>IN</sub>

- 0.1µA typical guiescent current in shutdown

- Guaranteed 350mA output current

- Noise voltage =  $100\mu V_{BMS}$  typical

- Operates from a single Li-Ion cell or 3 cell NiMH/NiCd batteries

- Only one or two tiny surface-mount external components required depending on application

- Small 5 bump micro SMD package, lead free

- Thermal-overload and short-circuit protection

- -40°C to +125°C junction temperature range

### Applications

- Mobile Phones

- Hand-Held Radios

- Personal Digital Assistants

- Palm-Top PCs

- **Portable Instruments**

- **Battery Powered Devices**

### **Typical Application Circuit**

202085 © 2007 National Semiconductor Corporation

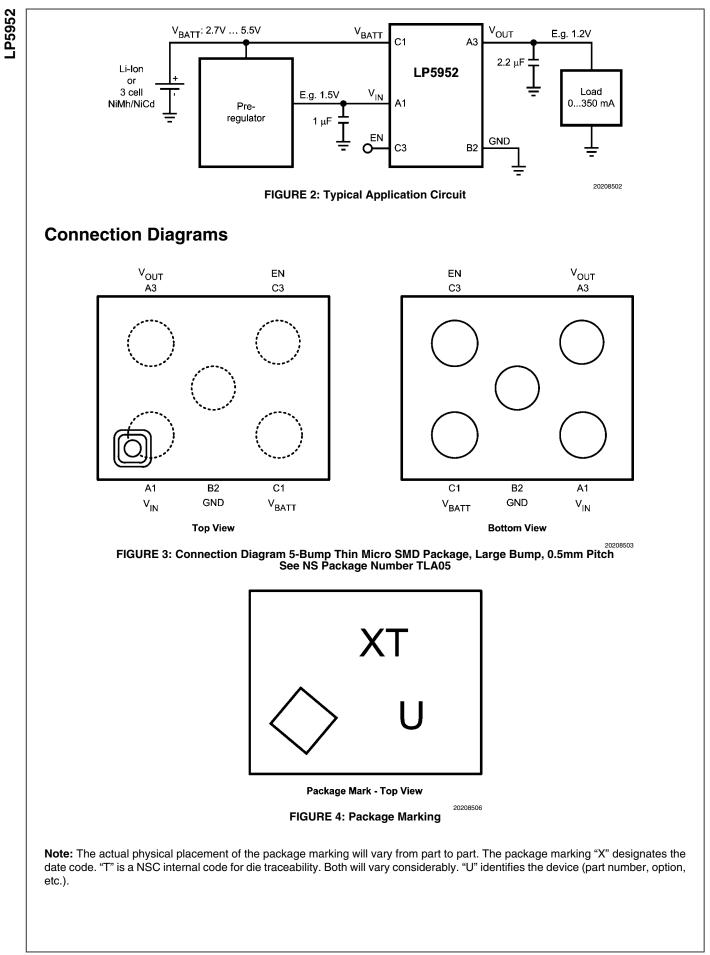

# **Pin Descriptions**

| Pin Number | Pin Name          | Description                                                                                                                                                    |

|------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1         | V <sub>IN</sub>   | Power input voltage; input range: 0.7V to 4.5V, $V_{IN} \le V_{BATT}$                                                                                          |

| A3         | V <sub>OUT</sub>  | Regulated output voltage                                                                                                                                       |

| B2         | GND               | Ground                                                                                                                                                         |

| C1         | V <sub>BATT</sub> | Bias input voltage; input range: 2.5V to 5.5V                                                                                                                  |

| C3         | EN                | Enable pin logic input: low = shutdown, high = active, normal operation. This pin should not be left floating. Tie to $V_{BATT}$ if this function is not used. |

# **Order Information**

| Output Voltage<br>(V) | LP5952 Supplied as 250 Units,<br>Tape and Reel, lead free | LP5952 Supplied as 3000 Units,<br>Tape and Reel, lead free | Flow | Package<br>Marking |

|-----------------------|-----------------------------------------------------------|------------------------------------------------------------|------|--------------------|

| 0.7                   | LP5952TL-0.7                                              | LP5952TLX-0.7                                              | NOPB | 4                  |

| 1.2                   | LP5952TL-1.2                                              | LP5952TLX-1.2                                              | NOPB | 7                  |

| 1.3                   | LP5952TL-1.3                                              | LP5952TLX-1.3                                              | NOPB | U                  |

| 1.4                   | LP5952TL-1.4                                              | LP5952TLX-1.4                                              | NOPB | А                  |

| 1.5                   | LP5952TL-1.5                                              | LP5952TLX-1.5                                              | NOPB | Т                  |

| 1.6                   | LP5952TL-1.6                                              | LP5952TLX-1.6                                              | NOPB | В                  |

| 1.8                   | LP5952TL-1.8                                              | LP5952TLX-1.8                                              | NOPB | 8                  |

| 2.0                   | LP5952TL-2.0                                              | LP5952TLX-2.0                                              | NOPB | 5                  |

### Absolute Maximum Ratings (Notes 2, 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| $V_{IN}$ , $V_{BATT}$ pins: Voltage to GND,                                              |                    |

|------------------------------------------------------------------------------------------|--------------------|

| V <sub>IN</sub> ≤ V <sub>BATT</sub> :                                                    | -0.2V to 6.0V      |

| V <sub>BATT</sub> pin to V <sub>IN</sub> pin:                                            | 0.2V               |

| EN pin: Voltage to GND:                                                                  | -0.2V to 6.0V      |

| Continuous Power Dissipation                                                             |                    |

| (Note 3):                                                                                | Internally Limited |

| Junction Temperature (T <sub>J-MAX</sub> ):                                              | 150°C              |

| Storage Temperature Range:                                                               | -65°C to + 150°C   |

| Package Peak Reflow Temperature<br>(Pb-free, 10-20 sec.)(Note 4):<br>ESD Rating(Note 5): | 260°C              |

| Human Body Model:                                                                        | 2.0kV              |

| Machine Model:                                                                           | 200V               |

### **Operating Ratings**

| Input Voltage Range V <sub>IN</sub>          | 0.7V to 4.5V           |

|----------------------------------------------|------------------------|

| Input Voltage Range V                        | 2.5V to 5.5V           |

| V <sub>EN</sub> Input Voltage                | 0 to V <sub>BATT</sub> |

| Recommended Load Current                     | 0mA to 350mA           |

| Junction Temperature (T <sub>J</sub> ) Range | -40°C to + 125°C       |

| Ambient Temperature (T <sub>A</sub> ) Range  |                        |

| (Note 6)                                     | -40°C to + 85°C        |

### **Thermal Properties**

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ), TLA05 package (Note 7)

95°C/W

## **ESD Caution Notice**

National Semiconductor recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper ESD handling techniques can result in damage.

### Electrical Characteristics (Notes 2, 8, 11)

Typical values and limits appearing in standard typeface are for  $T_A = 25^{\circ}C$ . Limits appearing in **boldface** type apply over the full operating temperature range: -40°C  $\leq T_J \leq$  +125°C. Unless otherwise noted, specifications apply to the typical application circuit with  $V_{IN} = V_{OUT(NOM)} + 1.0V$ ,  $V_{BATT} = V_{OUT(NOM)} + 1.5V$  or 2.5V, whichever is higher,  $I_{OUT} = 1mA$ ,  $C_{VIN} = 1.0\mu$ F,  $C_{OUT} = 2.2\mu$ F,  $V_{EN} = V_{BATT}$ .

| Symbol                               | Parameter                       |                                                           | Тур  | Limit |     | Unite         |

|--------------------------------------|---------------------------------|-----------------------------------------------------------|------|-------|-----|---------------|

|                                      |                                 | Condition                                                 |      | Min   | Max | Units         |

| ΔV <sub>OUT</sub> / V <sub>OUT</sub> | Output Voltage Tolerance        | $V_{IN} = V_{OUT(NOM)} + 0.3V$                            |      | -1.5  | 1.5 | %             |

|                                      |                                 |                                                           |      | -2.0  | 2.0 | %             |

| $\Delta V_{OUT}$ / $\Delta V_{IN}$   | Line Regulation Error           | $V_{IN} = V_{OUT(NOM)} + 0.3V$ to 4.5V, $V_{BATT} = 4.5V$ | 0.3  |       | 1.0 | mV/V          |

| $\Delta V_{OUT}$ / $\Delta V_{BATT}$ | -                               | $V_{BATT} = V_{OUT(NOM)} + 1.5V (\geq 2.5V)$ to 5.5V      | 0.5  |       | 2.2 |               |

| $\Delta V_{OUT}$ / $\Delta mA$       | Load Regulation Error           | I <sub>OUT</sub> = 1mA to 350mA                           | 15   |       | 30  | µV/mA         |

| 1                                    | Output Current                  | $V_{OUT} = 0V, V_{EN} = V_{IN} = V_{BATT} = V_{OUT}$      | 500  | 350   |     | mA            |

| I <sub>SC</sub>                      | (short circuit)                 | <sub>(NOM)</sub> + 1.5V                                   | 500  | 000   |     |               |

|                                      |                                 | I <sub>OUT</sub> = 350mA,                                 | 1.07 |       | 1.5 | v             |

| V <sub>DO_VBATT</sub>                |                                 | $V_{\rm IN} = V_{\rm OUT(NOM)} + 0.3V$                    | 1.07 |       | 1.5 | v             |

| (Note 10)                            | Output Voltage Dropout (Note 9) | I <sub>OUT</sub> = 150mA,                                 | 0.96 |       | 1.3 | v             |

|                                      | Culput Voltage Diopout (Note 3) | $V_{\rm IN} = V_{\rm OUT(NOM)} + 0.3V$                    | 0.90 |       | 1.5 | v             |

| V                                    |                                 | I <sub>OUT</sub> = 350mA,                                 | 88   |       | 200 | mV            |

| V <sub>DO_VIN</sub>                  |                                 | $V_{BATT} = V_{OUT(NOM)} + 1.5V \text{ or } 2.5V$         | 00   |       | 200 |               |

| E <sub>N</sub>                       | Output Noise                    | 10Hz to 100kHz                                            | 100  |       |     | $\mu V_{RMS}$ |

| Symbol | Deveryeter                   | O and little of                  | T   | Limit |     | Linite |

|--------|------------------------------|----------------------------------|-----|-------|-----|--------|

|        | Parameter                    | Condition                        | Тур | Min   | Max | Units  |

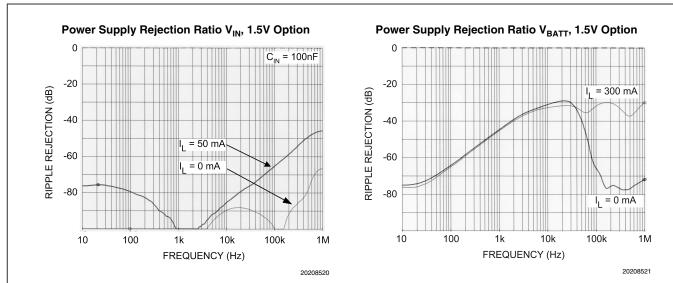

|        |                              | Sine modulated V <sub>BATT</sub> |     |       |     |        |

|        |                              | f = 10Hz                         | 70  |       |     | dB     |

|        | Power Supply Rejection Ratio | f = 100Hz                        | 65  |       |     | dB     |

|        |                              | f = 1kHz                         | 45  |       |     | dB     |

| PSRR   |                              | Sine modulated V <sub>IN</sub>   |     |       |     |        |

|        |                              | f = 10Hz                         | 80  |       |     | dB     |

|        |                              | f = 100Hz                        | 90  |       |     | dB     |

|        |                              | f = 1kHz                         | 95  |       |     | dB     |

|        |                              | f = 10kHz                        | 85  |       |     | dB     |

|        |                              | f = 100 kHz                      | 64  |       |     | dB     |

### **Quiescent Currents**

| Symbol               | Parameter                      | Condition                  | Тур | Limit |     | Units |

|----------------------|--------------------------------|----------------------------|-----|-------|-----|-------|

| Symbol               |                                |                            |     | Min   | Max | Units |

| I <sub>Q_VBATT</sub> | Current into V <sub>BATT</sub> | I <sub>LOAD</sub> = 0350mA | 50  |       | 100 | μA    |

| I <sub>Q_VIN</sub>   | Current into V <sub>IN</sub>   | I <sub>LOAD</sub> = 0      | 11  |       | 28  | μA    |

## **Shutdown Currents**

| Symbol               | Parameter                      | Condition            | Тур | Limit |     | Units |

|----------------------|--------------------------------|----------------------|-----|-------|-----|-------|

| Symbol               | Falameter                      | Condition            |     | Min   | Max | Units |

| I <sub>Q_VBATT</sub> | Current into V <sub>BATT</sub> | V <sub>EN</sub> = 0V | 0.1 |       | 1   | μA    |

| I <sub>Q_VIN</sub>   | Current into V <sub>IN</sub>   | V <sub>EN</sub> = 0V | 0.1 |       | 1   | μA    |

## **Enable Control Characteristics**

| Symbol          | Devementer                                        | Conditions | Тур  | Lir | Units |       |

|-----------------|---------------------------------------------------|------------|------|-----|-------|-------|

|                 | Parameter                                         | Conditions |      | Min | Max   | Units |

| I <sub>EN</sub> | Maximum Input Current at V <sub>EN</sub><br>Input |            | 0.01 |     | 1     | μA    |

| V <sub>IL</sub> | Low Input Threshold (shutdown)                    |            |      |     | 0.4   | V     |

| V <sub>IH</sub> | High Input Threshold (enable)                     |            |      | 1.0 |       | V     |

# **Thermal Protection**

| Symbol             | Parameter                    | Conditions | Тур | Limit |     | Units |

|--------------------|------------------------------|------------|-----|-------|-----|-------|

|                    |                              | Conditions |     | Min   | Max | Units |

| T <sub>SHDN</sub>  | Thermal-Shutdown Temperature |            | 165 |       |     | °C    |

| ΔT <sub>SHDN</sub> | Thermal-Shutdown Hysteresis  |            | 20  |       |     | °C    |

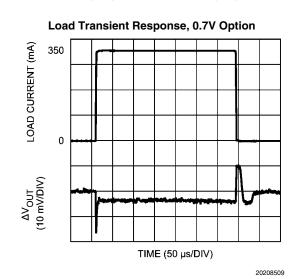

### **Transient Characteristics**

| Symbol               | Barrier                                              | O an dition o                                                                | Turr | Lir |     |       |

|----------------------|------------------------------------------------------|------------------------------------------------------------------------------|------|-----|-----|-------|

|                      | Parameter                                            | Conditions                                                                   | Тур  | Min | Max | Units |

| ΔV <sub>OUT</sub>    | Dynamic Line Transient<br>Response V <sub>IN</sub>   | $V_{IN} = V_{OUT(NOM)} + 0.3V$ to<br>$V_{OUT(NOM)} + 0.9V$ ; tr, tf = 10µs   | ±1   |     |     | mV    |

| ΔV <sub>OUT</sub>    | Dynamic Line Transient<br>Response V <sub>BATT</sub> | $V_{BATT} = V_{OUT(NOM)} + 1.5V$ to<br>$V_{OUT(NOM)} + 2.1V$ ; tr, tf = 10µs | ±15  |     |     | mV    |

| ΔV <sub>OUT</sub>    | Dynamic Load Transient<br>Response                   | Pulsed load 0300mA,<br>di/dt = 300mA/1µs                                     | ±15  |     |     | mV    |

| T <sub>STARTUP</sub> | Startup Time                                         | EN to 0.95 * V <sub>OUT</sub>                                                | 70   |     | 150 | μs    |

### Input and Output Capacitors, Recommended Specification

| Symbol           | Parameter              | Conditions                                                                               | Nom | Limit |     | Units |

|------------------|------------------------|------------------------------------------------------------------------------------------|-----|-------|-----|-------|

|                  |                        | Conditions                                                                               |     | Min   | Max | Units |

| C                | Output Capacitanaa     | Capacitance (Note 12)                                                                    | 2.2 | 1.5   | 10  | μF    |

| C <sub>OUT</sub> | Output Capacitance     | ESR                                                                                      |     | 3     | 300 | mΩ    |

| C <sub>VIN</sub> | Innut Canacitance at V | Capacitance (Note 12), not needed in typ<br>post regulation application,<br>see FIGURE 1 | 1   | 0.47  |     | μF    |

|                  |                        | ESR                                                                                      |     | 3     | 300 | mΩ    |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the component may occur. Operating Ratings are conditions under which operation of the device is guaranteed. Operating Ratings do not imply guaranteed performance limits. For guaranteed performance limits and associated test conditions, see the Electrical Characteristics tables.

Note 2: All voltages are with respect to the potential at the GND pin.

Note 3: Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at  $T_J = 165^{\circ}C$  (typ.) and disengages at  $T_J = 145^{\circ}C$  (typ.).

Note 4: For detailed soldering specifications and information, please refer to National Semiconductor Application Note 1112: Micro SMD Wafer Level Chip Scale Package (AN-1112).

Note 5: The Human body model is a 100pF capacitor discharged through a 1.5kΩ resistor into each pin. The machine model is a 200pF capacitor discharged directly into each pin. (MIL-STD-883 3015.7)

**Note 6:** In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature ( $T_{A-MAX}$ ) is dependent on the maximum operating junction temperature ( $T_{J-MAX-OP} = 125^{\circ}$ C), the maximum power dissipation of the device in the application ( $P_{D-MAX}$ ), and the junction-to ambient thermal resistance of the part/package in the application ( $\theta_{JA}$ ), as given by the following equation:  $T_{A-MAX} = T_{J-MAX-OP} - (\theta_{JA} \times P_{D-MAX})$ .

Note 7: Junction-to-ambient thermal resistance is highly application and board-layout dependent. In applications where high maximum power dissipation exists, special attention must be paid to thermal dissipation issues in board design.

**Note 8:** Min and Max limits are guaranteed by design, test, or statistical analysis. Typical (Typ) numbers are not guaranteed, but do represent the most likely norm. Unless otherwise specified, conditions for Typ specifications are:  $V_{IN} = V_{OUT(NOM)} + 1.0V$ ,  $V_{BATT} = V_{OUT(NOM)} + 1.5V$  or 2.5V, whichever is higher,  $T_A = 25^{\circ}$  C.

Note 9: Dropout voltage is defined as the input to output voltage differential at which the output voltage falls to 100mV below the nominal output voltage.

Note 10: This specification does not apply for output voltages below 1.0V (as  $V_{BATTMIN} = 2.5V$ ).

Note 11:  $V_{\text{OUT}(\text{NOM})}$  is the stated output voltage option

**Note 12:** The capacitor tolerance should be 30% or better over temperature. The full operating conditions for the application should be considered when selecting a suitable capacitor to ensure that the minimum value of capacitance is always met. Recommended capacitor type is X7R. However, dependent on application, X5R, Y5V, and Z5U can also be used. The shown minimum limit represents real minimum capacitance, including all tolerances and must be maintained over temperature and dc bias voltage (See capacitor section in Applications Hints)

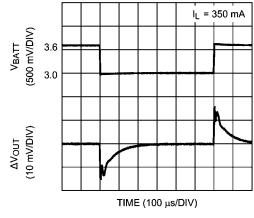

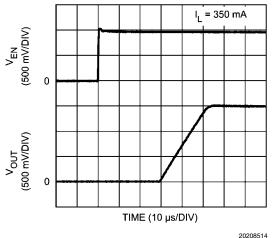

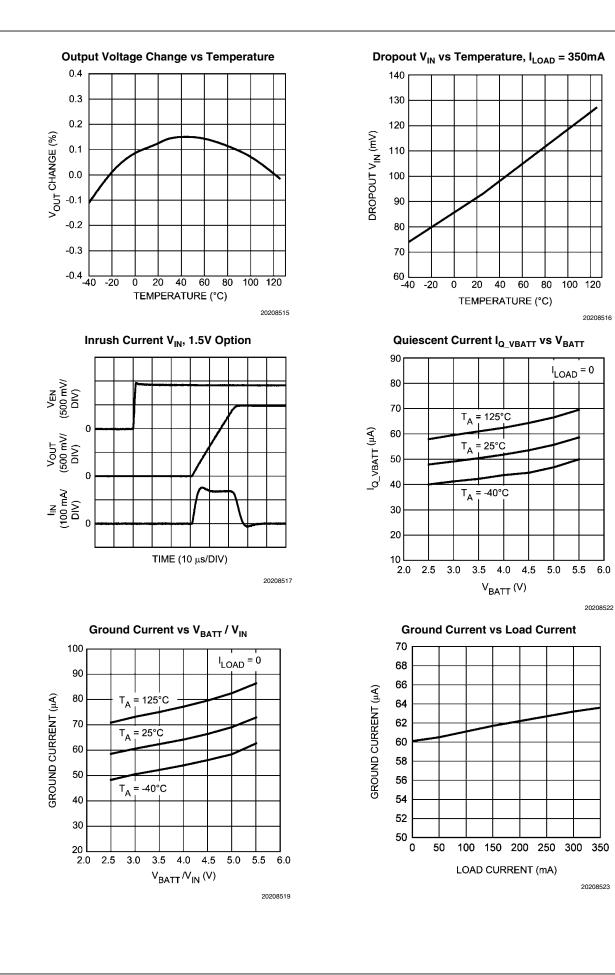

**Typical Performance Characteristics** Unless otherwise specified,  $C_{IN} = 1.0\mu$ F ceramic,  $C_{OUT} = 2.2\mu$ F ceramic,  $V_{IN} = V_{OUT(NOM)} + 1V$ ,  $V_{BATT} = V_{OUT(NOM)} + 1.5V$ ,  $T_A = 25^{\circ}$ C, Enable pin is tied to  $V_{BATT}$ .

Line Transient Response V<sub>IN</sub>, 1.5V Option

TIME (100 µs/DIV)

TIME (10 µs/DIV)

Enable Start-up Time, 0.7V Option

I<sub>L</sub> = 350 mA

20208511

20208513

I<sub>L</sub> = 350 mA

V<sub>BATT</sub> = 3.1V

V<sub>IN</sub> (500 mV/DIV)

ΔVουτ (1 mV/DIV)

V<sub>EN</sub> (500 mV/DIV)

V<sub>OUT</sub> (200 mV/DIV) 0

0

3.1

2.5

Load Transient Response, 1.5V Option

TIME (50 µs/DIV)

20208510

Line Transient Response V<sub>BATT</sub>, 1.5V Option

20208512

### Enable Start-up Time, 1.5V Option

## **Application Hints**

### DUAL RAIL SUPPLY

The LP5952 requires two different supply voltages:

$\bullet V_{\mathsf{IN}},$  the power input voltage, is regulated to the fixed output voltage

$\bullet V_{\text{BATT}},$  the bias input voltage, supplies internal circuitry.

It's important that  $V_{\rm IN}$  does not exceed  $V_{\rm BATT}$  at any time. If the device is used in the typical post regulation application as shown in FIGURE 1, the sequencing of the two power supplies is not an issue as  $V_{\rm BATT}$  supplies both, the DC-DC regulator and the LP5952. The output voltage of the DC-DC regulator will take some time to rise up and supply  $V_{\rm IN}$  of LP5952. In this application  $V_{\rm IN}$  will always ramp up more slowly than  $V_{\rm BATT}.$

In case  $\rm V_{\rm IN}$  is shorted to  $\rm V_{BATT},$  the voltages at the two supply pins will ramp up simultaneously causing no problem.

Only in applications with two independent supplies connected to the LP5952 special care must be taken to guarantee that  $V_{IN}$  is always  $\leq V_{RATT}$ .

#### POWER DISSIPATION AND DEVICE OPERATION

The permissible power dissipation for any package is a measure of the capability of the device to pass heat from the power source, the junctions of the IC, to the ultimate heat sink, the ambient environment. Thus the power dissipation is dependent on the ambient temperature and the thermal resistance across the various interfaces between the die and ambient air.

As stated in the electrical specification section, the allowable power dissipation for the device in a given package can be calculated using the equation:

$$P_{D} = (T_{J(MAX)} - T_{A}) / \theta_{JA}$$

With a  $\theta_{JA} = 95^{\circ}C/W$ , the device in the 5 bump micro SMD package returns a value of 1053mW with a maximum junction temperature of 125°C at T<sub>A</sub> of 25°C or 421mW at T<sub>A</sub> of 85°C. The actual power dissipation across the device can be estimated by the following equation:

$$\mathsf{P}_{\mathsf{D}} = (\mathsf{V}_{\mathsf{IN}} - \mathsf{V}_{\mathsf{OUT}}) * \mathsf{I}_{\mathsf{OUT}}$$

This establishes the relationship between the power dissipation allowed due to thermal consideration, the voltage drop across the device, and the continuous current capability of the device. These two equations should be used to determine the optimum operating conditions for the device in the application. As an example, to keep full load current capability of 350mA for a 1.5V output voltage option at a high ambient temperature of 85°C, V<sub>IN</sub> has to be kept ≤ 2.7V:

$V_{\rm IN} \leq P_{\rm D} \, / \, I_{\rm OUT} + V_{\rm OUT} = 421 \text{mW} \, / \, 350 \text{mA} + 1.5 \text{V} = 2.7 \text{V}.$

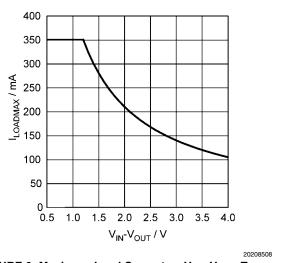

The figure below shows the output current derating due to these considerations:

FIGURE 6: Maximum Load Current vs V<sub>IN</sub> - V<sub>OUT</sub>, T<sub>A</sub> =  $85^{\circ}$ C, V<sub>OUT</sub> = 1.5V,  $\theta_{JA}$  = 95°C/W

The typical contribution of the bias input voltage supply  $V_{\text{BATT}}$  to the power dissipation can be neglected:

$P_{D \text{ VBATT}} = V_{BATT} * I_{QVBATT} = 5.5V * 50\mu A = 0.275mW$  typical.

### **EXTERNAL CAPACITORS**

As is common with most regulators, the LP5952 requires external capacitors to ensure stable operation. The LP5952 is specifically designed for portable applications requiring minimum board space and the smallest size components. These capacitors must be correctly selected for good performance.

### **INPUT CAPACITOR**

If the LP5952 is used stand alone, an input capacitor at V<sub>IN</sub> is required for stability. It is recommended that a 1.0µF capacitor be connected between the LP5952 power voltage input pin V<sub>IN</sub> and ground (this capacitance value may be increased without limit).

This capacitor must be located a distance of not more than 1 cm from the  $V_{\rm IN}$  pin and returned to a clean analogue ground. Any good quality ceramic, tantalum, or film capacitor may be used at the input.

A capacitor at  $V_{BATT}$  is not required if the distance to the supply does not exceed 5cm.

If the device is used in the typical application as post regulator after a DC-DC regulator, no input capacitors are required at all as the capacitors of the DC-DC regulator ( $C_{IN}$  and  $C_{OUT}$ ) are sufficient if both components are mounted close to each other and a proper GND plane is used. If the distance between the output capacitor of the DC-DC regulator and the V<sub>IN</sub> pin of the LP5952 is larger than 5cm, it's recommended to add the mentioned input capacitor at V<sub>IN</sub>.

**Important:** Tantalum capacitors can suffer catastrophic failures due to surge current when connected to a low-impedance source of power (like a battery or a very large capacitor). If a tantalum capacitor is used at the input, it must be guaranteed by the manufacturer to have a surge current rating sufficient for the application.

The ESR (Equivalent Series Resistance) of the input capacitor should be in the range of  $3m\Omega$  to  $300m\Omega$ . The tolerance and temperature coefficient must be considered when selecting the capacitor to ensure the capacitance will remain  $\geq$ 470nF over the entire operating temperature range.

### **OUTPUT CAPACITOR**

The LP5952 is designed specifically to work with very small ceramic output capacitors. A ceramic capacitor (dielectric types X7R, Z5U, or Y5V) in the 2.2µF range (up to 10µF) and with an ESR between 3m $\Omega$  to 300m $\Omega$  is suitable as  $C_{OUT}$  in the LP5952 application circuit.

This capacitor must be located a distance of not more than 1cm from the  $V_{\rm OUT}$  pin and returned to a clean analogue ground.

It is also possible to use tantalum or film capacitors at the device output,  $V_{OUT}$ , but these are not as attractive for reasons of size and cost (see the section Capacitor Characteristics).

#### CAPACITOR CHARACTERISTICS

The LP5952 is designed to work with ceramic capacitors on the output to take advantage of the benefits they offer. For capacitance values in the range of  $1\mu$ F to  $4.7\mu$ F, ceramic capacitors are the smallest, least expensive and have the lowest ESR values, thus making them best for eliminating high frequency noise. The ESR of a typical  $1\mu$ F ceramic capacitor is in the range of  $3m\Omega$  to  $40m\Omega$ , which easily meets the ESR requirement for stability for the LP5952.

For both input and output capacitors, careful interpretation of the capacitor specification is required to ensure correct device operation. The capacitor value can change greatly, depending on the operating conditions and capacitor type.

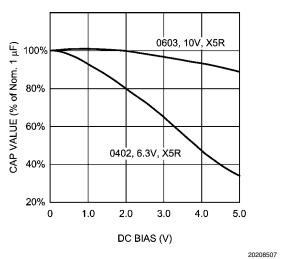

In particular, the output capacitor selection should take account of all the capacitor parameters, to ensure that the specification is met within the application. The capacitance can vary with DC bias conditions as well as temperature and frequency of operation. Capacitor values will also show some decrease over time due to aging. The capacitor parameters are also dependant on the particular case size, with smaller sizes giving poorer performance figures in general. The example shows a typical graph comparing different capacitor case sizes in a Capacitance vs. DC Bias plot. As shown in the graph, increasing the DC Bias condition can result in the capacitance value falling below the minimum value given in the recommended capacitor specifications table (0.47/1.5µF in this case). Note that the graph shows the capacitance out of spec for the 0402 case size capacitor at higher bias voltages. It is therefore recommended that the capacitor manufacturers' specifications for the nominal value capacitor are consulted for all conditions, as some capacitor sizes (e.g. 0402) may not be suitable in the actual application.

FIGURE 7: Graph Showing A Typical Variation In Capacitance vs DC Bias

The ceramic capacitor's capacitance can vary with temperature. The capacitor type X7R, which operates over a temperature range of -55°C to +125°C, will only vary the capacitance to within ±15%. The capacitor type X5R has a similar tolerance over a reduced temperature range of -55°C to +85°C. Many large value ceramic capacitors, larger than 1µF are manufactured with Z5U or Y5V temperature characteristics. Their capacitance can drop by more than 50% as the temperature varies from 25°C to 85°C. Therefore X7R is recommended over Z5U and Y5V in applications where the ambient temperature will change significantly above or below 25°C.

Tantalum capacitors are less desirable than ceramic for use as output capacitors because they are more expensive when comparing equivalent capacitance and voltage ratings in the  $1\mu$ F to  $4.7\mu$ F range.

Another important consideration is that tantalum capacitors have higher ESR values than equivalent size ceramics. This means that while it may be possible to find a tantalum capacitor with an ESR value within the stable range, it would have to be larger in capacitance (which means bigger and more costly) than a ceramic capacitor with the same ESR value. It should also be noted that the ESR of a typical tantalum will increase about 2:1 as the temperature goes from  $25^{\circ}$ C down to - $40^{\circ}$ C, so some guard band must be allowed.

#### **NO-LOAD STABILITY**

The LP5952 will remain stable and in regulation with no external load. This is an important consideration in some circuits, for example CMOS RAM keep-alive applications.

#### **ENABLE OPERATION**

The LP5952 may be switched ON or OFF by a logic input at the Enable pin,  $V_{EN}$ . A logic high at this pin will turn the device on. When the enable pin is low, the regulator output is off and the device typically consumes  $0.1 \mu A$ .

If the application does not require the Enable switching feature, the  $V_{\text{EN}}$  pin should be tied to  $V_{\text{BATT}}$  to keep the regulator output permanently on.

To ensure proper operation, the signal source used to drive the V<sub>EN</sub> input must be able to swing above and below the specified turn-on/off voltage thresholds listed in the Electrical Characteristics section under Enable Control Characteristics, V<sub>IL</sub> and V<sub>IH</sub>.

### FAST TURN ON

Fast turn-on is guaranteed by an optimized architecture allowing a fast ramp of the output voltage to reach the target voltage while the inrush current is controlled low at 120mA typical (for a  $C_{OUT}$  of 2.2µF).

#### SHORT-CIRCUIT PROTECTION

The LP5952 is short circuit protected and in the event of a peak over-current condition, the output current through the NFET pass device will be limited.

If the over-current condition exists for a longer time, the average power dissipation will increase depending on the input to output voltage difference until the thermal shutdown circuitry will turn off the NFET.

Please refer to the section on thermal information for power dissipation calculations.

#### THERMAL-OVERLOAD PROTECTION

Thermal-Overload Protection limits the total power dissipation in the LP5952. When the junction temperature exceeds  $T_J =$ 165°C typ., the shutdown logic is triggered and the NFET is turned off, allowing the device to cool down. After the junction temperature dropped by 20°C (temperature hysteresis) typical, the NFET is activated again. This results in a pulsed output voltage during continuous thermal-overload conditions. The Thermal-Overload Protection is designed to protect the LP5952 in the event of a fault condition. For normal, continuous operation, do not exceed the absolute maximum junction temperature rating of  $T_J = +150^{\circ}C$  (see Absolute Maximum Ratings).

#### **REVERSE CURRENT PATH**

The internal NFET pass device in LP5952 has an inherent parasitic body diode. During normal operation, the input voltage is higher than the output voltage and the parasitic diode is reverse biased. However, if the output is pulled above the input in an application, then current flows from the output to the input as the parasitic diode gets forward biased. The output can be pulled above the input as long as the current in the parasitic diode is limited to 50mA. For currents above this limit an external Schottky diode must be connected from V<sub>OUT</sub> to V<sub>IN</sub> (cathode on V<sub>IN</sub>, anode on V<sub>OUT</sub>).

### **EVALUATION BOARDS**

For availability of evaluation boards please refer to the Product Folder of LP5952 at www.national.com.

For information regarding evaluation boards, please refer to Application Note: AN-1531.

Notes

# Notes

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

#### Copyright© 2007 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Customer Support Center Email: new.feedback@nsc.com Tel: 1-800-272-9959

National Semiconductor Europe Customer Support Center

Fax: +49 (0) 180-530-85-86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +49 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560