# STM1403

3V FIPS-140

## Security Supervisor with Battery Switchover

DATA BRIEFING

#### **FEATURES\***

- STM1403 SUPPORTS FIPS-140 SECURITY LEVEL 3+

- 4 High-Impedance Physical Tamper Inputs

- Over/Under Operating Voltage Detector

- Security Alarm (SAL) on Tamper Detection

- SUPERVISORY FUNCTIONS

- Automatic Battery Switchover

- RST Output (Open Drain)

- Manual (Push-button) Reset Input (MR)

- Power-fail Comparator (PFI/PFO)

- Vccsw (Vcc SWITCH OUTPUT)

- Low When Switched to V<sub>CC</sub>

- High When Switched to V<sub>BAT</sub> (BATT ON Indicator)

- BATTERY LOW VOLTAGE DETECTOR (POWER-UP)

- OPTIONAL V<sub>REF</sub> (1.237V) (Available for STM1403A only)

- LOW BATTERY SUPPLY CURRENT (2.8μA, tvp)

- SECURE LOW PROFILE 16-PIN, 3x3mm, QFN PACKAGE

### Figure 1. Package

QFN16, 3mm x 3mm (Q)

#### **Table 1. Device Options**

|          | STM704<br>Functions <sup>(1)</sup> | Physical<br>Tamper<br>Inputs | Over/Under<br>Voltage<br>Alarms | Over/Under<br>Temperature<br>Alarms | V <sub>REF</sub><br>(1.237V)<br>Option | V <sub>OUT</sub> Status,<br>During<br>Alarm | Vccsw Status,<br>During Alarm |

|----------|------------------------------------|------------------------------|---------------------------------|-------------------------------------|----------------------------------------|---------------------------------------------|-------------------------------|

| STM1403A | ~                                  | <b>&gt;</b>                  | ~                               |                                     | ~                                      | ON                                          | Normal Mode <sup>(2)</sup>    |

| STM1403B | ~                                  | <b>V</b>                     | ~                               |                                     | Note 3                                 | High-Z                                      | High                          |

| STM1403C | ~                                  | <b>V</b>                     | ~                               |                                     | Note 3                                 | Ground                                      | High                          |

Note: 1.  $\overline{SAL}$ ,  $\overline{RST}$ ,  $\overline{PFO}$ , and  $\overline{BLD}$  are Open Drain.

Rev 4.0

1/9

October 2005

For further information contact your local ST sales office.

<sup>2.</sup> Normal Mode: Low when V<sub>OUT</sub> is internally switched to V<sub>CC</sub> and High when V<sub>OUT</sub> is internally switched to battery.

<sup>3.</sup> Pin 9 is the  $V_{REF}$  pin for STM1403A. It is the  $V_{TPU}$  pin for STM1403B/C.

<sup>\*</sup> Contact local ST sales office for the full datasheet.

#### SUMMARY DESCRIPTION

The STM1403 family of security supervisors are a low power family of intrusion (tamper) detection chips targeted at manufacturers of POS terminals and other systems, to enable them to meet physical and/or environmental intrusion monitoring requirements as mandated by various standards, such as Federal Information Processing Standards (FIPS) Pub 140 entitled "Security Requirements for Cryptographic Modules," published by the National Institute of Standards and Technology, U.S. Department of Commerce), EMVCo, ISO, ZKA, and VISA PED. STM1403 supports target levels 3 and lower

The STM1403 includes Automatic Battery Switchover, RST Output (Open Drain), Manual (Push-button) Reset Input (MR), Power-fail Comparator (PFI/PFO), Physical and/or Environmental . Tamper Detect/Security Alarm, and Battery Low Voltage Detect features.

The STM1403A also offers a V<sub>REF</sub> (1.237V) as an option on pin 9. On the STM1403B/C, this pin is V<sub>TPU</sub> (internally switched V<sub>CC</sub> or V<sub>BAT</sub>).

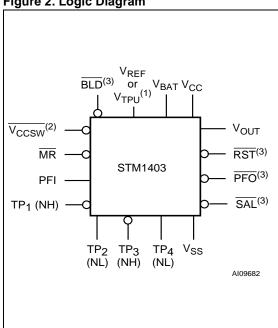

Figure 2. Logic Diagram

Note: 1. V<sub>REF</sub> only for STM1403A; V<sub>TPU</sub> for STM1403B/C.

- 2. Normal Mode: Low when VouT is internally switched to V<sub>CC</sub> and High when V<sub>OUT</sub> is internally switched to battery.

3. SAL, RST, PFO, and BLD are Open Drain.

#### **VOUT Pin Modes**

The STM1403 is available in three versions, corresponding to three modes of the V<sub>OUT</sub> pin (Supply Voltage Out), when the SAL (Security Alarm) is asserted (active-low) upon tamper detection:

**STM1403A.**  $V_{OUT}$  stays ON (at  $V_{CC}$  or  $V_{BAT}$ ) when SAL is driven low (activated).

**STM1403B.**  $V_{OUT}$  is set to High-Z when  $\overline{SAL}$  is driven low (activated).

**STM1403C.**  $V_{OUT}$  is driven to Ground when  $\overline{SAL}$ is activated (may be used when VOUT is connected directly to the V<sub>CC</sub> pin of the external SRAM that holds the cryptographic codes).

All variants (see Table 1., Device Options) are pincompatible and available in a security-friendly, low profile, 16-pin QFN package.

**Table 2. Signal Names**

| Vccsw <sup>(1)</sup>              | V <sub>CC</sub> Switch Output                            |  |  |

|-----------------------------------|----------------------------------------------------------|--|--|

| MR                                | Manual (Push-button) Reset Input                         |  |  |

| PFI                               | Power-fail Input                                         |  |  |

| TP <sub>1</sub> - TP <sub>4</sub> | Independent Physical Tamper<br>Detect Pins 1 through 4   |  |  |

| V <sub>OUT</sub>                  | Supply Voltage Output                                    |  |  |

| RST <sup>(2)</sup>                | Active-low Reset Output                                  |  |  |

| PFO <sup>(2)</sup>                | Power-fail Output                                        |  |  |

| SAL <sup>(2)</sup>                | Security Alarm Output                                    |  |  |

| BLD <sup>(2)</sup>                | Battery Low Voltage Detect                               |  |  |

| V <sub>REF</sub> <sup>(3)</sup>   | 1.237V Reference Voltage                                 |  |  |

| V <sub>TPU</sub> <sup>(3)</sup>   | Tamper Pull-up<br>(V <sub>CC</sub> or V <sub>BAT</sub> ) |  |  |

| V <sub>BAT</sub>                  | Back-up Supply Voltage                                   |  |  |

| V <sub>CC</sub>                   | Supply Voltage                                           |  |  |

| V <sub>SS</sub>                   | Ground                                                   |  |  |

Note: See PIN DESCRIPTIONS, page 9 of the full datasheet for

- 1. Normal Mode: Low when VOLIT is internally switched to V<sub>CC</sub> and High when V<sub>OUT</sub> is internally switched to battery.

SAL, RST, PFO, and BLD are Open Drain.

- 3. V<sub>REF</sub> only for STM1403A; V<sub>TPU</sub> for STM1403B/C.

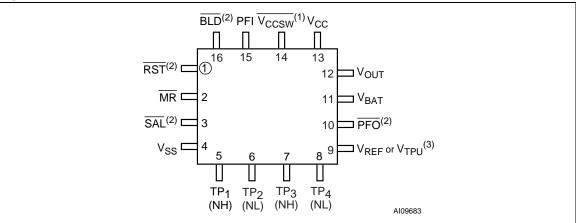

Figure 3. QFN16 Connections

- Note: See PIN DESCRIPTIONS, page 9 of the full datasheet for details.

1. Normal Mode: Low when V<sub>OUT</sub> is internally switched to V<sub>CC</sub> and High when V<sub>OUT</sub> is internally switched to battery.

2. SAL, RST, PFO, and BLD are Open Drain.

3. V<sub>REF</sub> only for STM1403A; V<sub>TPU</sub> for STM1403B/C.

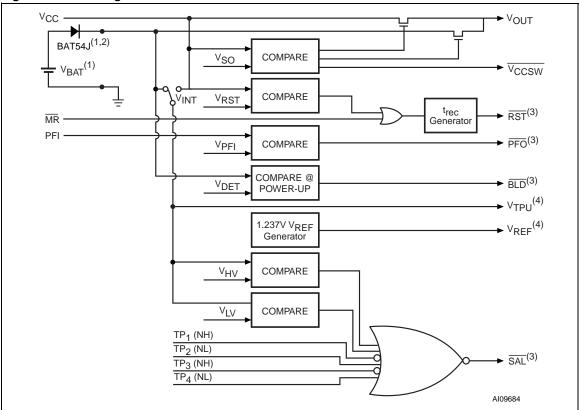

Figure 4. Block Diagram

Note: 1. BAT54J (from STMicroelectronics) recommended.

- 2. Required for battery-reverse charging protection.

- Open Drain

V<sub>REF</sub> only for STM1403; V<sub>TPU</sub> for STM1403B/C.

#### **TAMPER DETECTION**

#### **Physical**

There are four (4) high-impedance physical tamper detect input pins, 2 normally set to High (NH) and 2 normally set to Low (NL). Each input is designed with a glitch immunity. These inputs can be connected externally to several types of actuator devices (e.g., switches, wire mesh). A tamper on any one of the four inputs that causes its state to change will trigger the security alarm (SAL) and drive it to active-low. Once the tamper condition no longer exists, the SAL will return to its normal High state.

$TP_1$  and  $TP_3$  are set Normally to High (NH). They are connected externally through a closed switch or a high-impedance resistor to  $V_{OUT}$  (in the case of STM1403A) or  $V_{TPU}$  (in the case of STM1403B/C), A tamper condition will be detected when the input pin is pulled low. If not used, tie the pin to  $V_{OUT}$  or  $V_{TPU}$ .

$TP_2$  and  $TP_4$  are set Normally to Low (NL). They are connected externally through a high-impedance resistor or a closed switch to  $V_{SS}$ . A tamper condition will be detected when the input pin is pulled high. If not used, tie the pin to  $V_{SS}$ .

#### **Supply Voltage**

The internally switched supply voltage,  $V_{INT}$  (either  $V_{CC}$  input or  $V_{BAT}$  input) is continuously monitored. If  $V_{INT}$  should exceed the over voltage trip point,  $V_{HV}$  (set at 4.2V, typical), or should go below the under voltage trip point,  $V_{LV}$  (set at 2.0v, typical).  $\overline{SAL}$  will be driven active-low. Once the tamper condition no longer exists, the  $\overline{SAL}$  pin will return to its normal High state.

When no tamper condition exists,  $\overline{SAL}$  is normally High.

When a tamper is detected, the SAL is activated (driven low), independent of the part type. V<sub>OUT</sub> can be driven to one of three states, depending on which variant of STM1403 is being used (see Device Options, page 1):

- ON;

- High-Z; or

- Ground (V<sub>SS</sub>).

**Note:** The STM1403 must be initially powered above  $V_{RST}$  to enable the tamper detection alarms. For example, if the battery is on while  $V_{CC}$  = 0V, no alarm condition can be detected until  $V_{CC}$  rises above  $V_{RST}$  (and  $t_{rec}$  expires). From this point on, alarms can be detected either on battery or  $V_{CC}$ . This is done to avoid false alarms when the device goes from no power to its operational state.

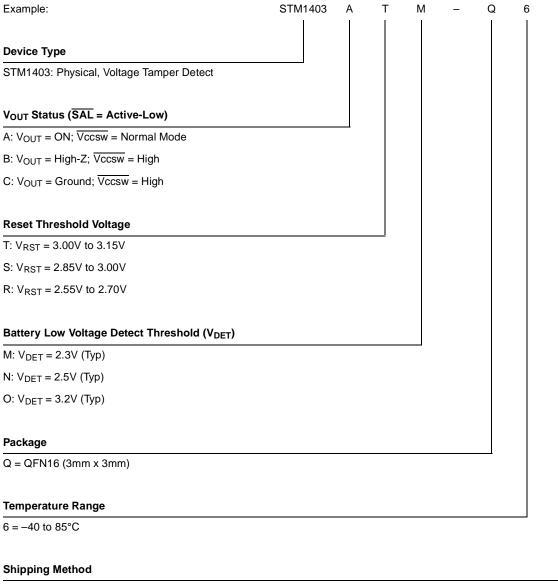

### **PART NUMBERING**

Table 3. Ordering Information Scheme (see Figure 5., page 7 for Marking Information)

F = ECOPACK Package, Tape & Reel

For other options, or for more information on any aspect of this device, please contact the ST Sales Office nearest you.

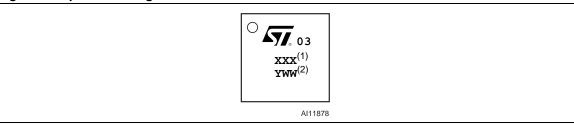

## Figure 5. Topside Marking Information

Note: 1. Options codes:

X = A, B, or C (for  $V_{OUT}$ )

X = T, S, or R (for Reset Threshold)

X = M, N, or O (for Battery Low Voltage Detect Threshold)

2. Traceability Codes

Y = Year

WW = Work Week

## **REVISION HISTORY**

**Table 4. Document Revision History**

| - unio 11 2 0 0 millioni 110 10 10 11 110 10 1 |          |                                                                                                                         |  |  |  |  |

|------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Date                                           | Revision | Description                                                                                                             |  |  |  |  |

| 11-October-04                                  | 1.0      | First Edition                                                                                                           |  |  |  |  |

| 26-Nov-04                                      | 1.1      | Corrected footprint dimensions; update characteristics (Figure 2, 3, 4, 5, 6, 7, 8, 9, 27, 28, 31; Table 1, 2, 3, 6, 7) |  |  |  |  |

| 22-Dec-04                                      | 1.2      | Update characteristics (Figure 5; Table 6, 7, 3)                                                                        |  |  |  |  |

| 03-Feb-05                                      | 1.3      | Update characteristics (Figure 5; Table 6, 7)                                                                           |  |  |  |  |

| 25-Feb-05                                      | 1.4      | Update temperature trip limits (Table 3)                                                                                |  |  |  |  |

| 06-May-05                                      | 2.0      | v2.0 of DB corresponds to v1.5 of DS                                                                                    |  |  |  |  |

| 05-Aug-05                                      | 3.0      | v3.0 of DB corresponds to v2.0 of DS                                                                                    |  |  |  |  |

| 13-Oct-05                                      | 4.0      | v4.0 of DB corresponds to v3.0 of DS; addition of datasheet availability                                                |  |  |  |  |

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics.

All other names are the property of their respective owners

$\ensuremath{\texttt{©}}$  2005 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan

Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

**A77**