September 1998, Rev. F

FN7022

## 100MHz Video Line Driver

# <u>élantec.</u>

The EL2003 and EL2033 are general purpose monolithic unity gain buffers featuring 100MHz, -3dB bandwidth

and 4ns small signal rise time. These buffers are capable of delivering a ±100mA current to a resistive load and are oscillation free into capacitive loads. In addition, the EL2003 and EL2033 have internal output short circuit current limiting which will protect the devices under both a DC fault condition and AC operation with reactive loads. The extremely fast slew rate of 1200V/µs, wide bandwidth, and high output drive make the EL2003 and EL2033 ideal choices for closed loop buffer applications with wide band op amps. These same characteristics and excellent DC performance make the EL2003 and EL2033 excellent choices for open loop applications such as driving coaxial and twisted pair cables.

The EL2003 and EL2033 are constructed using Elantec's proprietary dielectric isolation process that produces PNP and NPN transistors with essentially identical AC and DC characteristics.

#### **Features**

- Differential gain 0.1%

- Differential phase 0.1°

- · 100mA continuous output current guaranteed

- Short circuit protected

- Wide bandwidth 100MHz

- High slew rate 1200V/µs

- High input impedance 2MΩ

- Low quiescent current drain

## **Applications**

- · Co-ax cable driver

- · Flash converter driver

- · Video DAC buffer

- · Op amp booster

# **Ordering Information**

| PART<br>NUMBER | PACKAGE    | TAPE & REEL | PKG. NO. |

|----------------|------------|-------------|----------|

| EL2003CN       | 8-Pin PDIP | -           | MDP0031  |

| EL2003CM       | 20-Pin SOL | -           | MDP0027  |

| EL2033CN       | 8-Pin PDIP | -           | MDP0031  |

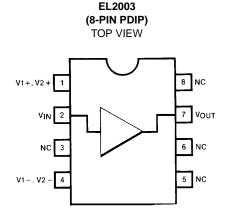

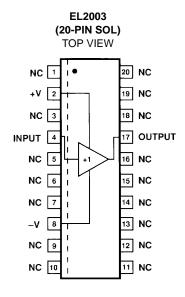

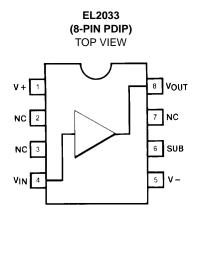

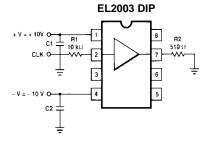

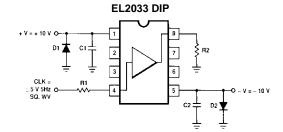

## **Pinouts**

## EL2003, EL2033

## **Absolute Maximum Ratings** (T<sub>A</sub> = 25°C)

| ٧s        | Supply Voltage (V+ - V-)                        | ±18V or 36V                    |

|-----------|-------------------------------------------------|--------------------------------|

| $V_{IN}$  | Input Voltage                                   | $\dots$ ±15V or V <sub>S</sub> |

| If the in | put exceeds the ratings shown (or the supplies) | or if the input to output      |

| voltage   | exceeds ±7.5V then the input current must be I  | imited to ±50 mA. See          |

| the app   | olication hints for more information.           |                                |

|           |                                                 | <b>50</b> A                    |

| liki      | Input Current (See note above)                  | ±50mA                          |

| $I_{IN}$                                                                      | Input Current (See note above) |         |             |         |    |         | ±50mA |         |

|-------------------------------------------------------------------------------|--------------------------------|---------|-------------|---------|----|---------|-------|---------|

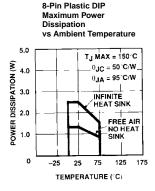

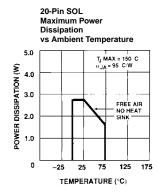

| $P_{D}$                                                                       | Power                          | Dissipa | ation       |         |    |         | . See | Curves  |

| The                                                                           | maximum                        | power   | dissipation | depends | on | package | type, | ambient |

| temperature and heat sinking. See the characteristic curves for more details. |                                |         |             |         |    |         |       |         |

| Output Short Circuit Duration                                               |

|-----------------------------------------------------------------------------|

| A heat sink is required to keep the junction temperature below the absolute |

| maximum when the output is short circuited.                                 |

| $T_A$    | Operating Temperature Range       |

|----------|-----------------------------------|

|          | EL2003C/EL2033C40°C to +85°C      |

| $T_{J}$  | Operating Junction Temperature    |

|          | Metal Can                         |

|          | Plastic                           |

| $T_{ST}$ | Storage Temperature65°C to +150°C |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

# **Electrical Specifications** $V_S = \pm 15V$ , $R_S = 50\Omega$

|                  |                                        | TEST CONDITIONS   |          |                                     | LIMITS |       |     |      |

|------------------|----------------------------------------|-------------------|----------|-------------------------------------|--------|-------|-----|------|

| PARAMETER        | DESCRIPTION                            | V <sub>IN</sub>   | LOAD     | TEMP                                | MIN    | TYP   | MAX | UNIT |

| Vos              | Output Offset Voltage                  | 0                 | ∞        | 25°C                                | -40    | 5     | 40  | mV   |

|                  |                                        |                   |          | T <sub>MIN</sub> , T <sub>MAX</sub> | -50    |       | 50  | mV   |

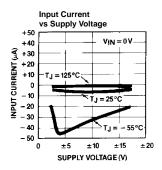

| I <sub>IN</sub>  | Input Current                          | 0                 | ∞        | 25°C, T <sub>MAX</sub>              | -25    | -5    | 25  | μΑ   |

|                  |                                        |                   |          | T <sub>MIN</sub>                    | -50    |       | 50  | μΑ   |

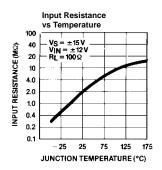

| R <sub>IN</sub>  | Input Resistance                       | ±12V              | 100Ω     | 25°C, T <sub>MAX</sub>              | 0.5    | 2     |     | MΩ   |

|                  |                                        |                   |          | T <sub>MIN</sub>                    | 0.05   |       |     | MΩ   |

| A <sub>V1</sub>  | Voltage Gain                           | ±12V              | 1kΩ      | 25°C                                | 0.98   | 0.99  |     | V/V  |

|                  |                                        |                   |          | T <sub>MIN</sub> , T <sub>MAX</sub> | 0.97   |       |     | V/V  |

| A <sub>V2</sub>  | Voltage Gain                           | ±6V               | 50Ω      | 25°C                                | 0.83   | 0.90  |     | V/V  |

|                  |                                        |                   |          | T <sub>MIN</sub> , T <sub>MAX</sub> | 0.80   |       |     | V/V  |

| A <sub>V3</sub>  | Voltage Gain with V <sub>S</sub> = ±5V | ±3V               | 50Ω      | 25°C                                | 0.82   | 0.89  |     | V/V  |

|                  |                                        |                   |          | T <sub>MIN</sub> , T <sub>MAX</sub> | 0.79   |       |     | V/V  |

| V <sub>01</sub>  | Output Voltage Swing                   | ±14V              | 1kΩ      | 25°C                                | ±13    | ±13.5 |     | V    |

|                  |                                        |                   |          | T <sub>MIN</sub> , T <sub>MAX</sub> | ±12.5  |       |     | V    |

| V <sub>02</sub>  | Output Voltage Swing                   | ±12V              | 100Ω     | 25°C                                | ±10.5  | ±11.3 |     | V    |

|                  |                                        |                   |          | T <sub>MIN</sub> , T <sub>MAX</sub> | ±10    |       |     | V    |

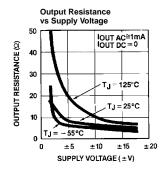

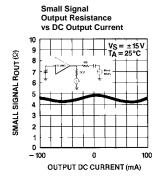

| R <sub>OUT</sub> | Output Resistance                      | ±2V               | 50Ω      | 25°C                                |        | 7     | 10  | Ω    |

|                  |                                        |                   |          | T <sub>MIN</sub> , T <sub>MAX</sub> |        |       | 12  | Ω    |

| lout             | Output Current                         | ±12V              | (Note 1) | 25°C                                | ±105   | ±230  |     | mA   |

|                  |                                        |                   |          | T <sub>MIN</sub> , T <sub>MAX</sub> | ±100   |       |     | mA   |

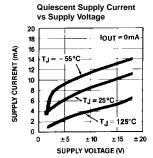

| I <sub>S</sub>   | Supply Current                         | 0                 | ∞        | 25°C, T <sub>MAX</sub>              |        | 10    | 15  | mA   |

|                  |                                        |                   |          | T <sub>MIN</sub>                    |        |       | 20  | mA   |

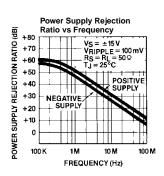

| PSRR             | Supply Rejection (Note 2)              | 0                 | ∞        | 25°C                                | 60     | 80    |     | dB   |

|                  |                                        |                   |          | T <sub>MIN</sub> , T <sub>MAX</sub> | 50     |       |     | dB   |

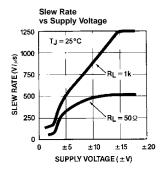

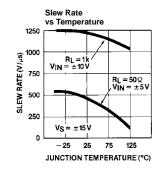

| SR1              | Slew Rate (Note 3)                     | ±10V              | 1kΩ      | 25°C                                | 600    | 1200  |     | V/µs |

| SR2              | Slew Rate (Note 4)                     | ±5V               | 50Ω      | 25°C                                | 200    | 400   |     | V/µs |

| THD              | Distortion @ 1kHz                      | 4V <sub>RMS</sub> | 50Ω      | 25°C                                |        | 0.2   | 1   | %    |

# **Typical Performance Curves**

# Typical Performance Curves (Continued)

4

## Applications Information

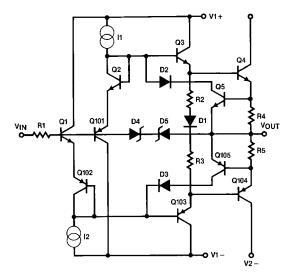

The EL2003 and EL2033 are monolithic buffer amplifiers built with Elantec's proprietary dielectric isolation process that produces NPN and PNP complimentary transistors. The circuits are connection of symmetrical common collector transistors that provide both sink and source current capability independent of output voltage while maintaining constant output and input impedances. The high slew rate and wide bandwidth of the EL2003 and EL2033 make them useful beyond video frequencies.

#### **Power Supplies**

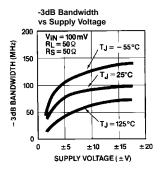

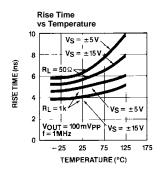

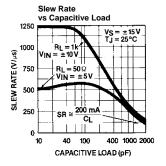

The EL2003 and EL2033 may be operated with single or split supplies as low as  $\pm 2.5 \text{V}$  (5V total) to as high as  $\pm 18 \text{V}$  (36V total). However, the bandwidth, slew rate, and output impedance degrade significantly for supply voltages less than  $\pm 5 \text{V}$  (10V total) as shown in the characteristic curves. It is not necessary to use equal value split supplies, for example -5V and +12V would be excellent for 0V to 1V video signals.

Bypass capacitors from each supply pin to a ground plane are recommended. The EL2003 and EL2033 will not oscillate even with minimal bypassing, however, the supply will ring excessively with inadequate capacitance. To eliminate a supply ringing and the interference it can cause, a 10µF tantalum capacitor with short pins is recommended for both supplies. Inadequate supply bypassing can also result in lower slew rates and longer settling times.

#### Input Range

The input to the EL2003 and EL2033 looks like a high resistance in parallel with a few picofarads in addition to a DC bias current. The input characteristics change very little with output loading, even when the amplifier is in current limit. However, there are clamp diodes from the input to the output that protect the transistor base emitter junctions. These diodes start to conduct at about ±9.5V input to output differential voltage. Of course the input resistance drops dramatically when the diodes start conducting; the diodes are rated at ±50mA.

The input characteristics also change when the input voltage exceeds either supply by 0.5V. This happens because the input transistor's base-collector junctions forward bias. If the input exceeds the supply by LESS than 0.5V and then returns to the normal input range, the output will recover in less than 10ns. However, if the input exceeds the supply by MORE than 0.5V, the recovery time can be hundreds of nanoseconds. For this reason it is recommended that schottky diode clamps from input to supply be used if a fast recovery from large input overloads is required.

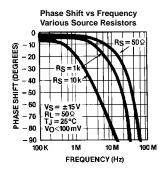

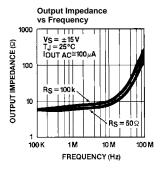

#### Source Impedance

The EL2003 and EL2033 have excellent input-output isolation and are very tolerant of variations in source impedances. Capacitive sources cause no problems at all, resistive sources up to  $100 k\Omega$  present no problems as long as care is used in board layout to minimize output to input coupling. Inductive sources can cause oscillations; a  $1 k\Omega$  resistor in series with the buffer input pin will usually eliminate problems without sacrificing too much speed. An unterminated cable or other resonant source can also cause oscillations. Again, an isolating resistor will eliminate the problem.

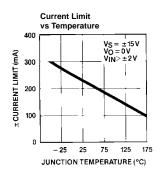

#### **Current Limit**

The EL2003 and EL2033 have internal current limits that protect the output transistors. The current limit goes down with junction temperature rise as shown in the characteristic curves. At a junction temperature of +175°C the current limits are at about 100mA. If the EL2003 or EL2033 output is shorted to ground when operating on ±15V supplies, the power dissipation will be greater than 1.5W. A heat sink is required in order for the EL2003 or EL2033 to survive an indefinite short. Recovery time to come out of current limit is about 250ns.

## Heat Sinking

When operating the EL2003 and EL2033 in elevated ambient temperatures and/or high supply voltages and low impedance loads, the internal power dissipation can force the junction temperature above the maximum rating (150°C for the plastic DIP). Also, an indefinite short of the output to ground will cause excessive power dissipation.

The thermal resistance junction to case is 50°C/W for the plastic DIP. A suitable heat sink will increase the power dissipation capability significantly beyond that of the package alone. Several companies make standard heat sinks for both packages. Aavid and Thermalloy heat sinks have been used successfully.

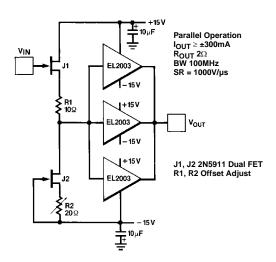

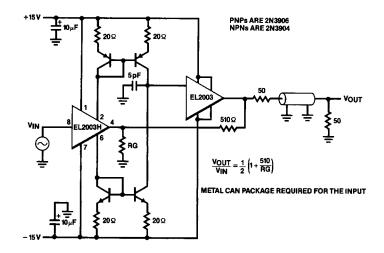

## Parallel Operation

If more than 100mA output is required or if heat management is a problem, several EL2003 or EL2033s may be paralleled together. The result is as though each device was driving only part of the load. For example, if two units are paralleled then a  $50\Omega$  load looks like  $100\Omega$  to each EL2003. Parallel operation results in lower input and output impedances, increased bias current but no increase in offset voltage. An example showing three EL2003s in parallel and also the addition of a FET input buffer stage is shown below. By using a dual FET the circuit complexity is minimal and the performance is excellent. Take care to minimize the stray capacitance at the input of the EL2003s for maximum slew rate and bandwidth.

FET INPUT BUFFER WITH HIGH OUTPUT CURRENTS

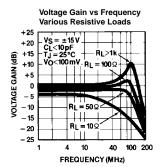

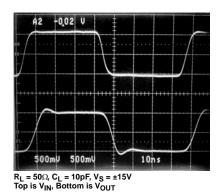

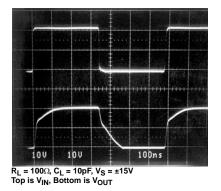

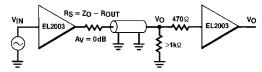

#### Resistive Loads

The DC gain of the EL2003 and EL2033 is the product of the unloaded gain (0.995) and the voltage divider formed by the device output resistance and the load resistance.

$$A_V = 0.995 \times \frac{R_L}{R_L + R_{OUT}}$$

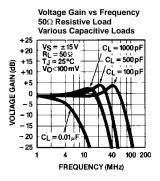

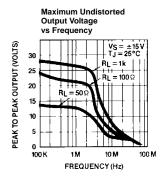

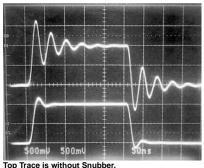

The high frequency response of the EL2003 and EL2033 varies with the value of the load resistance as shown in the characteristic curves. If the 100MHz peaking is undesirable when driving load resistors greater than  $50\Omega$ , an RC snubber circuit can be used from the output to ground. The snubber circuit works by presenting a high frequency load resistance of less than  $50\Omega$  while having no loading effect at low frequencies.

**SMALL SIGNAL RESPONSE**

LARGE SIGNAL RESPONSE

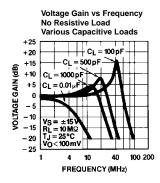

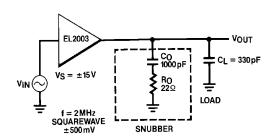

#### Capacitive Loads

The EL2003 and EL2033 are stable driving any type of capacitive load. However, when driving a pure capacitance of less than a thousand picofarads the frequency response has excessive peaking as shown in the characteristic curves. The squarewave response will have large overshoots and will ring for several hundred nanoseconds.

If the peaking and ringing cause system problems they can be eliminated with an RC snubber circuit from the output to ground. The values can be found empirically by observing a squarewave or the frequency response. First just put the resistor alone from output to ground until the desired response is obtained. Of course the gain will be reduced due to R<sub>OUT</sub>. Then put capacitance in series with the resistor to restore the gain at low frequencies. Start with a small capacitor and increase until the response is optimum. Too large a capacitor will roll the gain off prematurely and result in a longer settling time. The figure below shows an example of an EL2003 driving a 330pF load, which is similar to the input of a flash converter.

Bottom Trace is with Snubber Circuit.

#### **DRIVING A PURE CAPACITANCE**

#### **Inductive Loads**

The EL2003 and EL2033 can drive small motors, solenoids, LDTs and other inductive loads. Foldback current limiting is NOT used in the EL2003 or EL2033 and current limiting into an inductive load does NOT in and of itself cause spikes or kickbacks. However, if the EL2003 or EL2033 is in current limit and the input voltage is changing quickly (i.e., a squarewave) the inductive load can kick the output beyond the supply voltage. Motors are also able to generate kickbacks when the EL2003 or EL2033 is in current limit.

To prevent damage to the EL2003 and EL2033 when the output kicks beyond the supplies it is recommended that catch diodes be placed from each supply to the output.

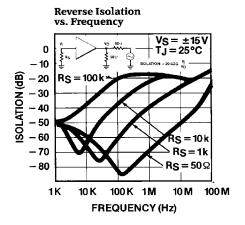

#### Reverse Isolation

The EL2003 and EL2033 have excellent output to input isolation over a wide frequency range. This characteristic is very important when the buffer is used to drive signals between different equipment over cables. Often the cable is not perfect or the termination is improper and reflections occur that act like a signal source at the output of the buffer. Worst case the cable is connected to a source instead of where it is supposed to go. In both situations the buffer must keep these signals from its input. The following curve shows the reverse isolation of the EL2003 and EL2033 verses frequency for various source resistors.

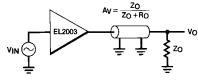

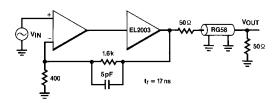

#### **Driving Cables**

There are at least three ways to use the EL2003 and EL2033 to drive cables, as shown in the adjacent figure. The most obvious is to directly connect the cable to the output of the buffer. This results in a gain determined by the output resistance of the EL2003 or EL2033 and the characteristic impedance of the cable, assuming it is properly terminated. For RG-58 into  $50\Omega$  the gain is about -1dB, exclusive of cable losses. For optimum response and minimum reflections it is important for the cable to be properly terminated.

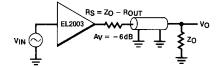

Double termination of a cable is the cleanest way to drive it since reflections are absorbed on both ends of the cable. The cable source resistor is equal to the characteristic impedance of the cable less the output resistance of the EL2003 and EL2033. The gain is -6dB exclusive of the cable attenuation.

Back matching is the last and most interesting way to drive a cable. The cable source resistor is again the characteristic impedance less the output resistance of the EL2003 and EL2033; the termination resistance is now much greater than the cable impedance. The gain is 0dB and DC levels waste no power.

An additional EL2003 or EL2033 make a good receiver at the terminating end. Because an unterminated cable looks like a resonant circuit, the receiving EL2003 or EL2033 should have an isolating resistor in series with its input to prevent oscillations when the cable is not connected to the driver. Of course if the cable is always connected to the back match, no resistor is necessary.

WARNING: ONE END OF A CABLE MUST BE PROPERLY TERMINATED. If neither end is terminated in the cable characteristic impedance, the cable will have standing waves that appear as resonances in the frequency response. The resonant frequencies are a function of the cable length and even relatively short cables can cause problems at frequencies as low as 1MHz. Longer cables should be terminated on both ends.

**DIRECT DRIVE**

**DOUBLE MATCHED**

**BACK MATCHED**

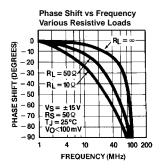

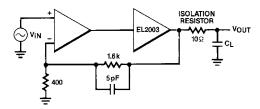

#### **Op Amp Booster**

The EL2003 or EL2033 can boost the output drive of almost any monolithic op amp. Because the phase shift in the EL2003 and EL2033 is low at the op amp's unity gain frequency, no additional compensation is required. By following an op amp with an EL2003 or EL2033, the buffered op amp can drive cables and other low impedance loads directly. Even decompensated high speed op amps can take advantage of the EL2003's or EL2033's 100mA drive.

**OP AMP BOOSTER**

Driving capacitive loads with any closed loop amplifier creates special problems. The open loop output impedance works into the load capacitance to generate phase lag which can make the loop unstable. The output impedance of the EL2003 or EL2033 is less than  $10\Omega$  from DC to about 10MHz, but a capacitive load of 1000pF will generate about  $45^\circ$  phase shift at 10MHz and make high speed op amps unstable. Obviously more capacitance will cause the same problem but at lower frequencies, and slower op amps as well would become unstable.

The easiest way to drive capacitive loads is to isolate them from the feedback with a series resistor. Ten to twenty ohms is usually enough but the final value depends on the op amp used and the range of load capacitance.

$10\Omega$  is enough isolation and speed is determined by the isolation resistor and capacitive load time constant.

#### OP AMP BOOSTER WITH CAPACITIVE LOAD

| CL      | t <sub>R</sub> | os  |

|---------|----------------|-----|

| 10pF    | 17ns           | 10% |

| 470pF   | 20ns           | 50% |

| 0.001µF | 30ns           | 35% |

| 0.005µF | 80ns           | 0   |

| 0.01μF  | 220ns          | 0   |

| 0.05μF  | 1.1µs          | 0   |

| 0.1µF   | 2.2µs          | 0   |

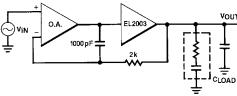

If the system requirements will not tolerate the isolation resistor, then additional high frequency feedback from the op amp output (the buffer input) and an isolating resistor from the buffer output is required. This requires that the op amp be unity gain stable.

This works with any unity gain stable OA. Snubber Circuit (51 $\Omega$  470pF) is optional.

# COMPLEX FEEDBACK WITH THE BUFFER TO DRIVE CAPACITIVE LOADS

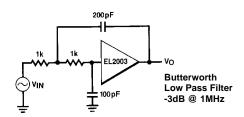

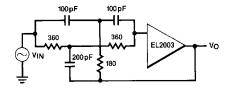

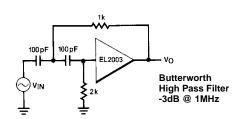

# **Typical Applications**

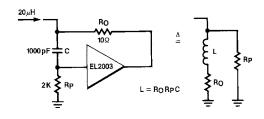

#### **HIGH Q NOTCH FILTER**

#### SIMULATED INDUCTOR

TURBO AMPLIFIER, BW = 30MHZ FOR GAINS FROM 1 TO 5

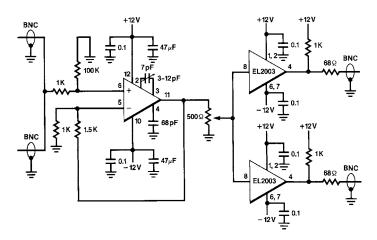

## Video Distribution Amplifier

In this broadcast quality circuit, the EL2006 FET input amplifier provides a very high input impedance so that it may be used with a wide variety of signal sources including video DACs, CCD cameras, video switches or  $75\Omega$  cables. The EL2006 provides a voltage gain of 2.5 while the

potentiometer allows the overall gain to be adjusted to drive the standard signal levels into the back matched  $75\Omega$  cables. Back matching prevents multiple reflections in the event that the remote end of the cable is not properly terminated. The 1k pull up resistors reduce the differential gain error from 0.15% to less than 0.1%.

**VIDEO DISTRIBUTION AMPLIFIER**

## **Burn-In Circuits**

# Simplified Schematic

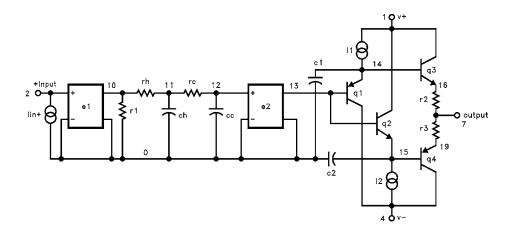

### EL2003 Macromodel

```

* Connections:

+input

+Vsupply

-Vsupply

output

.subckt M2003

* Input Stage

e1 10 0 2 0 1.0

r1 10 0 1K

rh 10 11 150

ch 11 0 10pF

rc 11 12 100

cc 12 0 3pF

e2 13 0 12 0 1.0

* Output Stage

q1 4 13 14 qp

q2 1 13 15 qn

q3 1 14 16 qn

q4 4 15 19 qp

r2 16 7 5

r3 19 7 5

c1 14 0 3pF

c2 15 0 3pF

i1 1 14 3mA

i2 15 4 3mA

* Bias Current

iin+ 2 0 5uA

* Models

.model gn npn(is=5e-15 bf=150 rb=350 ptf=45 cjc=2pF tf=0.3nS)

.model qp pnp(is=5e-15 bf=150 rb=350 ptf=45 cjc=2pF tf=0.3nS)

.ends

```

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com