**April 1999**

## **LF442**

# **Dual Low Power JFET Input Operational Amplifier**

## **General Description**

The LF442 dual low power operational amplifiers provide many of the same AC characteristics as the industry standard LM1458 while greatly improving the DC characteristics of the LM1458. The amplifiers have the same bandwidth, slew rate, and gain (10 k $\Omega$  load) as the LM1458 and only draw one tenth the supply current of the LM1458. In addition the well matched high voltage JFET input devices of the LF442 reduce the input bias and offset currents by a factor of 10,000 over the LM1458. A combination of careful layout design and internal trimming guarantees very low input offset voltage and voltage drift. The LF442 also has a very low equivalent input noise voltage for a low power amplifier.

The LF442 is pin compatible with the LM1458 allowing an immediate 10 times reduction in power drain in many applications. The LF442 should be used where low power dissipation and good electrical characteristics are the major considerations

#### **Features**

- 1/10 supply current of a LM1458: 400 µA (max)

- Low input bias current: 50 pA (max)

- Low input offset voltage: 1 mV (max)

- Low input offset voltage drift: 10 µV/°C (max)

- High gain bandwidth: 1 MHz

- High slew rate: 1 V/µs

- Low noise voltage for low power: 35 nV/√Hz

- Low input noise current:  $0.01 \text{ pA}/\sqrt{\text{Hz}}$

- High input impedance:  $10^{12}\Omega$

- High gain  $V_O = \pm 10V$ ,  $R_L = 10k$ : 50k (min)

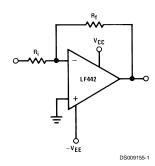

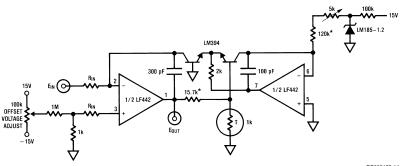

# **Typical Connection**

# **Ordering Information**

#### LF442XYZ

- X indicates electrical grade

- Y indicates temperature range "M" for military

- "C" for commercial

- **Z** indicates package type "H" or "N"

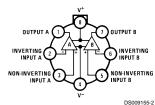

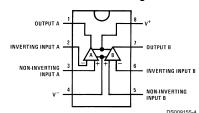

## **Connection Diagrams**

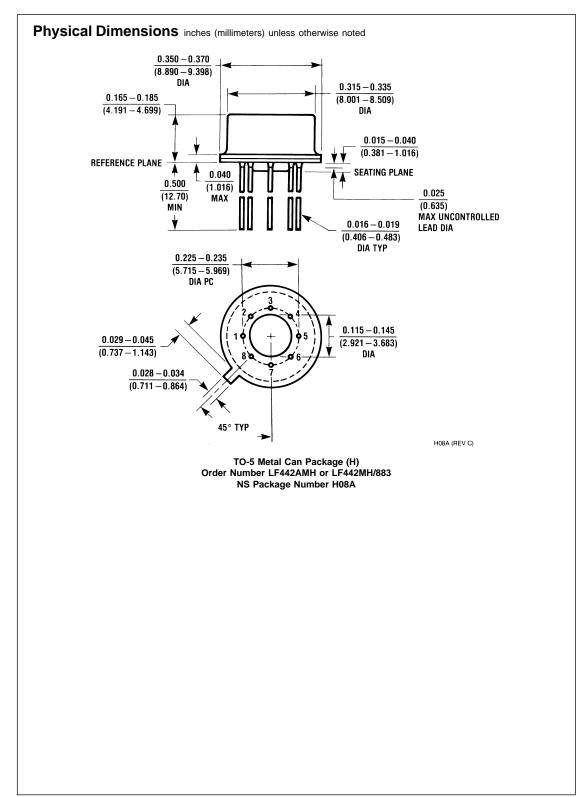

#### Metal Can Package

Pin 4 connected to case

Top View Order Number LF442AMH or LF442MH or LF442MH/883 See NS Package Number H08A

#### **Dual-In-Line Package**

Top View

Order Number LF442ACN or LF442CN

See NS Package Number N08E

BI-FET II™ is a trademark of National Semiconductor Corporation

© 1999 National Semiconductor Corporation

DS009155

# **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| 3V  |

|-----|

| V   |

| δV  |

|     |

| uou |

|     |

Duration (Note 3)

H Package N Package T<sub>i</sub> max 150°C 115°C

|                                                                            | H Package                   | N Package                   |

|----------------------------------------------------------------------------|-----------------------------|-----------------------------|

| $\theta_{JA}$ (Typical)<br>(Note 4)<br>(Note 5)<br>$\theta_{JC}$ (Typical) | 65°C/W<br>165°C/W<br>21°C/W | 114°C/W<br>152°C/W          |

| Operating Temperature                                                      | (Note 5)                    | (Note 5)                    |

| Range<br>Storage                                                           | –65°C≤T <sub>A</sub> ≤150°C | –65°C≤T <sub>A</sub> ≤150°C |

| Temperature Range<br>Lead Temperature                                      | 260°C                       | 260°C                       |

Lead Temperature 260°C

(Soldering, 10 sec.)

ESD Tolerance Rating to be determined

# DC Electrical Characteristics (Note 7)

| Symbol                   | Parameter                          | Conditions                                                               |                        | LF442A |                  |     | LF442 |                  |     | Units |

|--------------------------|------------------------------------|--------------------------------------------------------------------------|------------------------|--------|------------------|-----|-------|------------------|-----|-------|

|                          |                                    |                                                                          |                        | Min    | Тур              | Max | Min   | Тур              | Max |       |

| Vos                      | Input Offset Voltage               | $R_S = 10 \text{ k}\Omega, T_A = 25^{\circ}\text{C}$                     |                        |        | 0.5              | 1.0 |       | 1.0              | 5.0 | mV    |

|                          |                                    | Over Temperature                                                         |                        |        |                  |     |       |                  | 7.5 | mV    |

| $\Delta V_{OS}/\Delta T$ | Average TC of Input Offset Voltage | $R_S = 10 \text{ k}\Omega$                                               |                        |        | 7                | 10  |       | 7                |     | μV/°C |

| Ios                      | Input Offset Current               | V <sub>S</sub> = ±15V                                                    | T <sub>i</sub> = 25°C  |        | 5                | 25  |       | 5                | 50  | pА    |

|                          |                                    | (Notes 7, 8)                                                             | $T_j = 70^{\circ}C$    |        |                  | 1.5 |       |                  | 1.5 | nA    |

|                          |                                    |                                                                          | T <sub>j</sub> = 125°C |        |                  | 10  |       |                  |     | nA    |

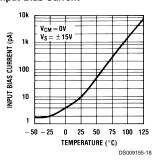

| I <sub>B</sub>           | Input Bias Current                 | V <sub>S</sub> = ±15V                                                    | T <sub>j</sub> = 25°C  |        | 10               | 50  |       | 10               | 100 | pА    |

|                          |                                    | (Notes 7, 8)                                                             | T <sub>i</sub> = 70°C  |        |                  | 3   |       |                  | 3   | nA    |

|                          |                                    |                                                                          | T <sub>i</sub> = 125°C |        |                  | 20  |       |                  |     | nA    |

| R <sub>IN</sub>          | Input Resistance                   | T <sub>i</sub> = 25°C                                                    |                        |        | 10 <sup>12</sup> |     |       | 10 <sup>12</sup> |     | Ω     |

| A <sub>VOL</sub>         | Large Signal Voltage               | $V_S = \pm 15V, V_O = \pm 10V,$                                          |                        | 50     | 200              |     | 25    | 200              |     | V/mV  |

|                          | Gain                               | $R_L = 10 \text{ k}\Omega, T_A = 25^{\circ}\text{C}$<br>Over Temperature |                        |        |                  |     |       |                  |     |       |

|                          |                                    |                                                                          |                        | 25     | 200              |     | 15    | 200              |     | V/mV  |

| Vo                       | Output Voltage Swing               | $V_{S} = \pm 15V, R_{L} = 10 \text{ k}\Omega$                            |                        | ±12    | ±13              |     | ±12   | ±13              |     | V     |

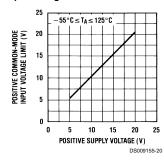

| V <sub>CM</sub>          | Input Common-Mode                  |                                                                          |                        | ±16    | +18              |     | ±11   | +14              |     | V     |

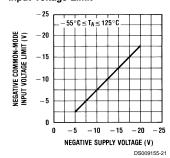

|                          | Voltage Range                      |                                                                          |                        |        | -17              |     |       | -12              |     | V     |

| CMRR                     | Common-Mode                        | $R_S \le 10 \text{ k}\Omega$                                             |                        | 80     | 100              |     | 70    | 95               |     | dB    |

|                          | Rejection Ratio                    |                                                                          |                        |        |                  |     |       |                  |     |       |

| PSRR                     | Supply Voltage                     | (Note 9)                                                                 |                        | 80     | 100              |     | 70    | 90               |     | dB    |

|                          | Rejection Ratio                    |                                                                          |                        |        |                  |     |       |                  |     |       |

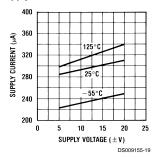

| Is                       | Supply Current                     |                                                                          |                        |        | 300              | 400 |       | 400              | 500 | μA    |

# **AC Electrical Characteristics** (Note 7)

| Symbol         | Parameter              | Conditions                                   | LF442A |      |     | LF442 |      |     | Units  |

|----------------|------------------------|----------------------------------------------|--------|------|-----|-------|------|-----|--------|

|                |                        |                                              | Min    | Тур  | Max | Min   | Тур  | Max |        |

|                | Amplifier to Amplifier | T <sub>A</sub> = 25°C, f = 1 Hz-20 kHz       |        | -120 |     |       | -120 |     | dB     |

|                | Coupling               | (Input Referred)                             |        |      |     |       |      |     |        |

| SR             | Slew Rate              | V <sub>S</sub> = ±15V, T <sub>A</sub> = 25°C | 0.8    | 1    |     | 0.6   | 1    |     | V/µs   |

| GBW            | Gain-Bandwidth Product | V <sub>S</sub> = ±15V, T <sub>A</sub> = 25°C | 0.8    | 1    |     | 0.6   | 1    |     | MHz    |

| e <sub>n</sub> | Equivalent Input Noise | $T_A = 25^{\circ}C, R_S = 100\Omega,$        |        | 35   |     |       | 35   |     | nV/√Hz |

|                | Voltage                | f = 1 kHz                                    |        |      |     |       |      |     |        |

| i <sub>n</sub> | Equivalent Input Noise | T <sub>A</sub> = 25°C, f = 1 kHz             |        | 0.01 |     |       | 0.01 |     | pA/√Hz |

|                | Current                |                                              |        |      |     |       |      |     | F      |

## AC Electrical Characteristics (Note 7) (Continued)

Note 1: "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits.

Note 2: Unless otherwise specified the absolute maximum negative input voltage is equal to the negative power supply voltage.

Note 3: Any of the amplifier outputs can be shorted to ground indefinitely, however, more than one should not be simultaneously shorted as the maximum junction temperature will be exceeded.

Note 4: The value given is in 400 linear feet/min air flow.

Note 5: The value given is in static air.

Note 6: These devices are available in both the commercial temperature range 0°C  $\leq$   $T_A \leq$  70°C and the military temperature range -55°C  $\leq$   $T_A \leq$  125°C. The temperature range is designated by the position just before the package type in the device number. A "C" indicates the commercial temperature range and an "M" indicates the military temperature range. The military temperature range is available in "H" package only.

Note 7: Unless otherwise specified, the specifications apply over the full temperature range and for  $V_S = \pm 20V$  for the LF442A and for  $V_S = \pm 15V$  for the LF442.  $V_{OS}$ ,  $I_B$ , and  $I_{OS}$  are measured at  $V_{CM} = 0$ .

**Note 8:** The input bias currents are junction leakage currents which approximately double for every 10°C increase in the junction temperature,  $T_j$ . Due to limited production test time, the input bias currents measured are correlated to junction temperature. In normal operation the junction temperature rises above the ambient temperature as a result of internal power dissipation,  $P_D$ .  $T_j = T_A + \theta_{jA}P_D$  where  $\theta_{jA}$  is the thermal resistance from junction to ambient. Use of a heat sink is recommended if input bias current is to be kept to a minimum.

Note 9: Supply voltage rejection ratio is measured for both supply magnitudes increasing or decreasing simultaneously in accordance with common practice from ±15V to ±5V for the LF442 and ±20V to ±5V for the LF442A.

Note 10: Refer to RETS442X for LF442MH military specifications.

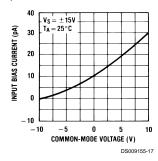

# **Typical Performance Characteristics**

#### Input Bias Current

## Input Bias Current

#### **Supply Current**

#### Positive Common-Mode Input Voltage Limit

#### Negative Common-Mode Input Voltage Limit

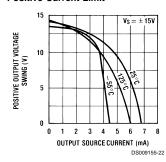

#### Positive Current Limit

# **Typical Performance Characteristics** (Continued)

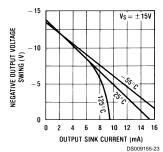

#### **Negative Current Limit**

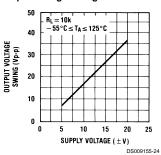

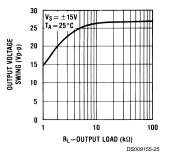

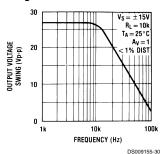

## Output Voltage Swing

#### **Output Voltage Swing**

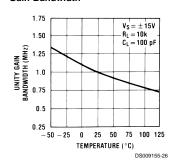

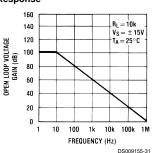

#### **Gain Bandwidth**

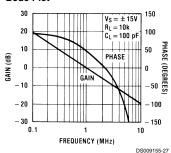

#### **Bode Plot**

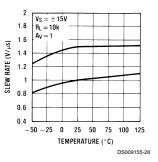

Slew Rate

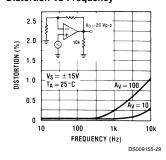

## Distortion vs Frequency

Undistorted Output Voltage Swing

Open Loop Frequency Response

#### **Typical Performance Characteristics** (Continued) Common-Mode Rejection **Power Supply Rejection Equivalent Input Noise** Ratio Ratio Voltage 160 120 POWER SUPPLY REJECTION RATIO (dB) EQUIVALENT INPUT NOISE VOLTAGE (nV/ JHz) 100 50 80 SUPPLY $\begin{aligned} V_S &= \pm 15V \\ R_L &= 10k \\ T_A &= 25^{\circ}C \end{aligned}$ 60 60 40 CMRR = 20 LOG VCM VOLTAGE GAIN - SUPPLY + OPEN LOOP 20 VOLTAGE GAIN 0 L 10 10 100 1k 10k 100k 1M 100 1k 10k 100k 100 1k FREQUENCY (Hz) FREQUENCY (Hz) FREQUENCY (Hz) DS009155-34 Open Loop Voltage Gain **Output Impedance Inverter Settling Time** OPEN LOOP VOLTAGE GAIN (V/V) OUTPUT VOLTAGE SWING FROM OV (V) OUTPUT IMPEDANCE $(\Omega)$ - 55°C 100k $T_A = 25 \,^{\circ} C$ -10100 10k 100k SUPPLY VOLTAGE ( $\pm$ V) FREQUENCY (Hz) SETTLING TIME $(\mu s)$ DS009155-35 DS009155-36 **Pulse Response** $R_L = 10 \text{ k}\Omega$ , $C_L = 10 \text{ pF}$ **Small Signal Inverting Small Signal Non-Inverting** OUTPUT VOLTAGE SWING (50 mV/DIV) OUTPUT VOLTAGE SWING (50 mV/DIV) DS009155-7 ${\rm TIME}\,(0.5\,\mu{\rm s/DIV})$ DS009155-8

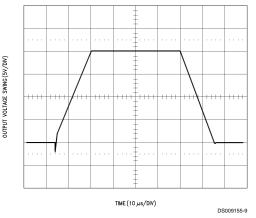

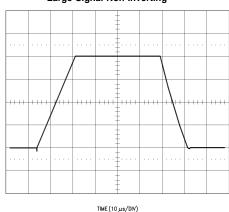

## **Pulse Response** $R_L = 10 \text{ k}\Omega$ , $C_L = 10 \text{ pF}$ (Continued)

#### Large Signal Non-Inverting

VOLTAGE SWING (5V/DIV)

OUTPUT

DS009155-10

# **Application Hints**

This device is a dual low power op amp with internally trimmed input offset voltages and JFET input devices (BI-FET II). These JFETs have large reverse breakdown voltages from gate to source and drain eliminating the need for clamps across the inputs. Therefore, large differential input voltages can easily be accommodated without a large increase in input current. The maximum differential input voltage is independent of the supply voltages. However, neither of the input voltages should be allowed to exceed the negative supply as this will cause large currents to flow which can result in a destroyed unit.

Exceeding the negative common-mode limit on either input will force the output to a high state, potentially causing a reversal of phase to the output. Exceeding the negative common-mode limit on both inputs will force the amplifier output to a high state. In neither case does a latch occur since raising the input back within the common-mode range again puts the input stage and thus the amplifier in a normal operating mode.

Exceeding the positive common-mode limit on a single input will not change the phase of the output; however, if both inputs exceed the limit, the output of the amplifier will be forced to a high state.

The amplifiers will operate with a common-mode input voltage equal to the positive supply; however, the gain bandwidth and slew rate may be decreased in this condition. When the negative common-mode voltage swings to within 3V of the negative supply, an increase in input offset voltage may occur.

Each amplifier is individually biased to allow normal circuit operation with power supplies of ±3.0V. Supply voltages less than these may degrade the common-mode rejection and restrict the output voltage swing.

The amplifiers will drive a 10 k $\Omega$  load resistance to  $\pm$  10V over the full temperature range.

Precautions should be taken to ensure that the power supply for the integrated circuit never becomes reversed in polarity or that the unit is not inadvertently installed backwards in a socket as an unlimited current surge through the resulting forward diode within the IC could cause fusing of the internal conductors and result in a destroyed unit.

As with most amplifiers, care should be taken with lead dress, component placement and supply decoupling in order to ensure stability. For example, resistors from the output to an input should be placed with the body close to the input to minimize "pick-up" and maximize the frequency of the feedback pole by minimizing the capacitance from the input to ground.

A feedback pole is created when the feedback around any amplifier is resistive. The parallel resistance and capacitance from the input of the device (usually the inverting input) to AC ground set the frequency of the pole. In many instances the frequency of this pole is much greater than the expected 3 dB frequency of the closed loop gain and consequenty there is negligible effect on stability margin. However, if the feedback pole is less than approximately 6 times the expected 3 dB frequency a lead capacitor should be placed from the output to the input of the op amp. The value of the added capacitor should be such that the RC time constant of this capacitor and the resistance it parallels is greater than or equal to the original feedback pole time constant.

# **Typical Applications**

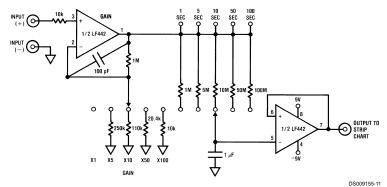

#### **Battery Powered Strip Chart Preamplifier**

TIME CONSTANT

Runs from 9v batteries (±9V supplies)

Fully settable gain and time constant

Battery powered supply allows direct plug-in interface to strip chart recorder without common-mode problems

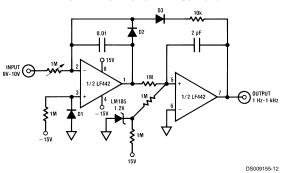

#### "No FET" Low Power $V \rightarrow F$ Converter

Trim 1M pot for 1 kHz full-scale output 15 mW power drain No integrator reset FET required Mount D1 and D2 in close proximity 1% linearity to 1 kHz

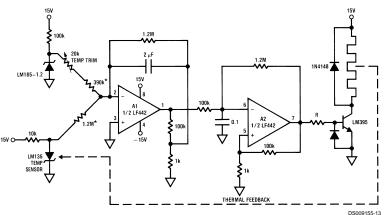

# Typical Applications (Continued)

## High Efficiency Crystal Oven Controller

- T<sub>control</sub>= 75°C

- A1's output represents the amplified difference between the LM335 temperature sensor and the crystal oven's temperature

- A2, a free running duty cycle modulator, drives the LM395 to complete a servo loop

- Switched mode operation yields high efficiency

- 1% metal film resistor

#### **Conventional Log Amplifier**

$$E_{OUT} = -\left[\log 10\left(\frac{E_{IN}}{R_{III}}\right) + 5\right]$$

$R_T$  = Tel Labs type Q81 Trim 5k for 10  $\mu$ A through the 5k–120k combination

\*1% film resistor

# Unconventional Log Amplifier | SEALE FACTOR | SCALE FACTOR | SCAL

Q1, Q2, Q3 are included on LM389 amplifier chip which is temperature-stabilized by the LM389 and Q2-Q3, which act as a heater-sensor pair. Q1, the logging transistor, is thus immune to ambient temperature variation and requires no temperature compensation at all.

9 www.national.com

DS009155-15

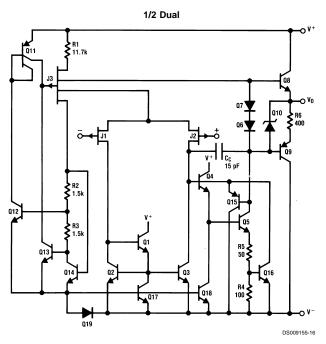

# **Detailed Schematic**

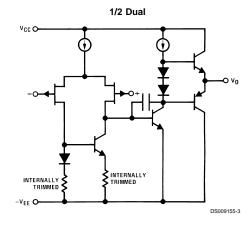

# **Simplified Schematic**

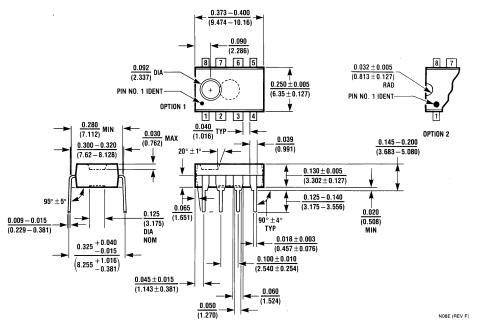

# Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

Molded Dual-In-Line Package (N)

Order Number LF442ACN or LF442CN

NS Package Number N08E

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor

Corporation

Tel: 1-800-272-9959 Fax: 1-800-737-7018 Email: support@nsc.com

www.national.com

National Semiconductor Europe

Europe

Fax: +49 (0) 1 80-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 1 80-530 85 85

English Tel: +49 (0) 1 80-532 78 32

Français Tel: +49 (0) 1 80-532 93 58

Italiano Tel: +49 (0) 1 80-534 16 80

National Semiconductor Asia Pacific Customer Response Group Tel: 65-2544466 Fax: 65-2504466 Email: sea.support@nsc.com National Semiconductor Japan Ltd. Tel: 81-3-5639-7560 Fax: 81-3-5639-7507

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.