# **TSC 80251**

# **Programmer's Guide**

**REV C – 1999**

TEMIC Semiconductors reserves the right to make changes in the specifications contained in this document in order to improve design or performance and to supply the best possible products. TEMIC also assumes no responsibility for the use of any circuits described herein, conveys no license under any patents or other rights, and makes no representations that the circuits are free from patent infringement. Applications for any integrated circuits contained in this publication are for illustration purposes only and TEMIC makes no representation or warranty that such applications will be suitable for the use specified without further testing or modification. Reproduction of any portion hereof without the prior written consent of TEMIC is prohibited.

#### On line information

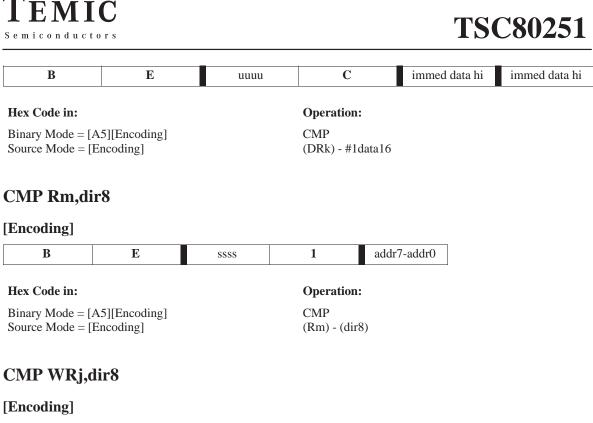

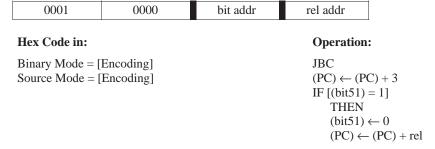

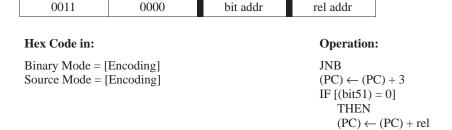

World Wide Web: http://www.temic-semi.com

## **Factory Technical Support**

Email: c251@temic-semi.com

#### **Publisher**

MHS S.A. La Chantrerie – Route de Gachet, BP 70602 44306 NANTES Cedex 03 France

Phone: 33 2 40 18 18 18 Fax: +33 2 40 18 19 60

Copyright TEMIC Semiconductors 1997.

Copyright INTEL Corporation 1994.

Portions reprinted by permission of INTEL Corporation.

## **Table of Contents**

| Conventions                                                                                                                                                                                               | • • • • • • • • • • • • • • • • • • • • |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| Chapter 1: Introduction                                                                                                                                                                                   | 1.1                                     |

| 1.1. Extended 8-bit Microcontroller                                                                                                                                                                       | 1.1                                     |

| 1.2. TSC80251 Derivatives                                                                                                                                                                                 | 1.1                                     |

| 1.3. TSC80251 Documentation                                                                                                                                                                               | 1.3                                     |

| Chapter 2: Architectural Overview                                                                                                                                                                         | 2.1                                     |

| 2.1. Microcontroller Architecture                                                                                                                                                                         | 2.1                                     |

| 2.2. Microcontroller Core 2.2.1. CPU 2.2.2. Clock and Reset Unit 2.2.3. Interrupt Handler                                                                                                                 | 2.2                                     |

| Chapter 3: Address Spaces                                                                                                                                                                                 | 3.1                                     |

| 3.1. C251 Architecture Address Spaces                                                                                                                                                                     | 3.1<br>3.2                              |

| 3.3. C51 Architecture mapping to C251 Architecture Address Spaces                                                                                                                                         | 3.2                                     |

| 3.4. TSC80251 Register File 3.4.1. Byte, Word and Dword Registers 3.4.2. Dedicated Registers 3.4.2.1. Accumulator and B Register 3.4.2.2. Extended Data Pointer, DPX 3.4.2.3. Extended Stack Pointer, SPX | 3.5<br>3.6<br>3.7<br>3.7                |

| 3.5. Special Function Registers (SFRs)                                                                                                                                                                    | 3.9                                     |

| Chapter 4: Programming                                                                                                                                                                                    | 4.1                                     |

| 4.1. Source Mode or Binary Mode Opcodes                                                                                                                                                                   |                                         |

| 4.2. Programming Features of the C251 Architecture                                                                                                                                                        | 4.2                                     |

# **TSC80251**

| 4.2.1. Data Types                                                  |          |

|--------------------------------------------------------------------|----------|

| 4.2.1.1. Order of Byte Storage for Words and Double Words          |          |

| 4.2.2. Register Notations                                          |          |

| 4.2.3. Address Notations                                           |          |

| 4.2.4. Addressing Modes                                            | 4.4      |

| 4.3. Program Status Words                                          | 4.4      |

| 4.4. Data Instructions                                             |          |

| 4.4.1. Data Addressing Modes                                       |          |

| 4.4.1.1. Addressable Registers                                     |          |

| 4.4.1.1. Addressable Registers 4.4.1.2. Immediate Addressing       |          |

| 4.4.1.3. Direct Addressing                                         |          |

| 4.4.1.4. Indirect Addressing                                       |          |

| 4.4.1.5. Displacement Addressing                                   |          |

| 4.4.2. Arithmetic Instructions                                     |          |

| 4.4.3. Logical Instructions                                        |          |

| 4.4.4. Data Transfer Instructions                                  |          |

| T.T.T. Data Halistet Historicolis                                  |          |

| 4.5. Bit Instructions                                              | 4.10     |

| 4.5.1. Bit Addressing                                              |          |

|                                                                    |          |

| 4.6. Control Instructions                                          |          |

| 4.6.1. Addressing Modes for Control Instructions                   |          |

| 4.6.2. Conditional Jumps                                           |          |

| 4.6.3. Unconditional Jumps                                         |          |

| 4.6.4. Calls and Returns                                           |          |

| 4.6.5. Interrupt Processing                                        |          |

| 4.6.6. Minimum Fixed Interrupt Time                                |          |

| 4.6.7. Variable Interrupt Parameters                               |          |

| 4.6.7.1. Response Time Variables                                   |          |

| 4.6.7.2. Computation of Worst Case Latency with Variables          |          |

| 4.6.8. Latency Calculations                                        |          |

| 4.6.9. Blocking Conditions                                         |          |

| 4.6.10. Interrupt Vector Cycle                                     |          |

| 4.6.11. ISRs in Process                                            | 4.18     |

| Chapter 5: Instruction Set                                         |          |

|                                                                    |          |

| 5.1. Instruction Set Summary                                       |          |

| 5.1.1. Notation for Instruction Operands                           |          |

|                                                                    |          |

| 5.2. Opcode Map and SupPorting Tables                              | 5.18     |

| 5.3. Instruction Set Summary                                       | 5.24     |

| 5.3.1. Execution Times for Instructions that Access the Ports SFRs | 5.24     |

| 5.4. Instruction Descriptions                                      | 5.36     |

|                                                                    |          |

| Glossary glo                                                       | ossary.1 |

# List of figures

| Chapter 2: Architectural Overview                                                 | 2.1  |

|-----------------------------------------------------------------------------------|------|

| Figure 2.1. TSC80251 Product Block Diagram                                        | 2.3  |

| Chapter 3: Address Spaces                                                         | 3.1  |

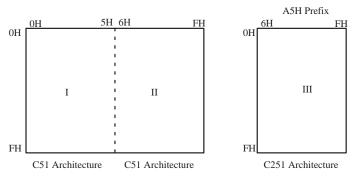

| Figure 3.1. Address Spaces for TSC80251 Microcontrollers                          | 3.1  |

| Figure 3.2. Address Spaces for the C51 Architecture                               | 3.2  |

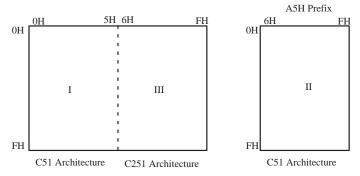

| Figure 3.3. Mappings C51 Architecture to C251 Architecture Address Spaces         | 3.4  |

| Figure 3.4. TSC80251 Memory Space                                                 | 3.4  |

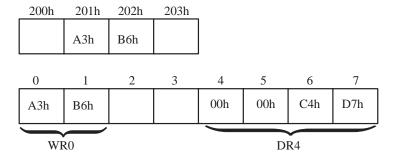

| Figure 3.5. Register File in Byte, Word, and Dword Register Views                 | 3.5  |

| Figure 3.6. Register File Locations 0-7                                           | 3.6  |

| Figure 3.7. Dedicated Registers in the Register File and their Corresponding SFRs | 3.8  |

| Chapter 4: Programming                                                            | 4.1  |

| Figure 4.1. Binary Mode Opcode Map                                                | 4.2  |

| Figure 4.2. Source Mode Opcode Map                                                | 4.2  |

| Figure 4.3. Word and Double-word Storage in Big Endian Form                       | 4.3  |

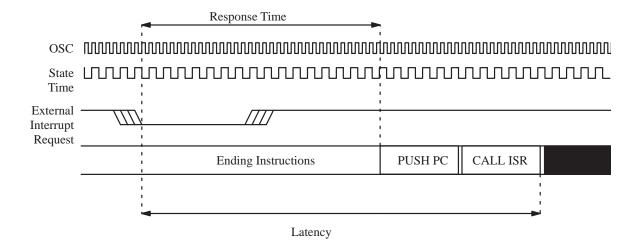

| Figure 4.4. Interrupt Process                                                     | 4.14 |

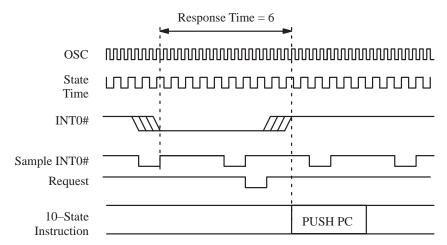

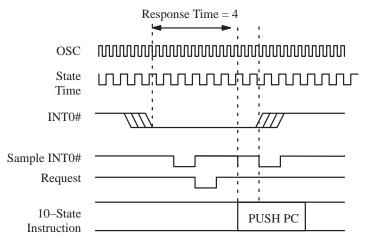

| Figure 4.5. Response Time Example                                                 | 4.15 |

| Figure 4.6. Response Time Example                                                 | 4.16 |

| Figure 4.7. Program Status Word register (PSW)                                    | 4.19 |

| Figure 4.8 Program Status Word 1 register (PSW1)                                  | 4.20 |

## List of tables

| Chapter 3: Address Spaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3.1                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| Table 3.1. Address Mappings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3.4<br>3.6                                                                      |

| Chapter 4: Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4.1                                                                             |

| Table 4.1. Examples of Opcodes in Binary and Source Modes Table 4.2. Data Types Table 4.3. Notation for Byte Registers, Word Registers, and Dword Registers Table 4.4. The Efffects of Instructions on the PSW and PSW1 Flags Table 4.5. Addressing Modes for Data Instruction in the C51 Architecture Table 4.6. Addressing Modes for Data Instruction in the C251 Architecture Table 4.7. Bit-addressable Locations Table 4.8. Two Samples of Bits Addressing Table 4.9. Addressing Modes for Bit Instructions Table 4.10. Addressing Modes for Control Instructions Table 4.11. Compare-conditional Jump Instructions Table 4.12. Interrupt Latency Variables Table 4.13. Actual vs. Predicted Latency Calculations | 4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.10<br>4.11<br>4.12<br>4.12<br>4.14<br>4.15 |

| Chapter 5: Instruction Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5.1                                                                             |

| Table 5.1. Minimum Number of States per Instruction for given Average Sizes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                 |

| Table 5.2. Notation for Direct Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                 |

| Table 5.3. Notation for Immediate Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                 |

| Table 5.5. Notation for Destination in Control Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                 |

| Table 5.6. Notation for Register Operands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                 |

| Table 5.7. Summary of Add and Subtract Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                 |

| Table 5.8. Summary of Increment and Decrement Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5.4<br>5.5                                                                      |

| Table 5.8. Summary of Increment and Decrement Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5.4<br>5.5<br>5.5                                                               |

| Table 5.8. Summary of Increment and Decrement Instructions Table 5.9. Summary of Compare Instructions Table 5.10. Summary of Logical Instructions (1/2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.4<br>5.5<br>5.5<br>5.5                                                        |

| Table 5.8. Summary of Increment and Decrement Instructions Table 5.9. Summary of Compare Instructions Table 5.10. Summary of Logical Instructions (1/2) Table 5.11. Summary of Logical Instructions (2/2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5.4<br>5.5<br>5.5<br>5.6<br>5.7                                                 |

| Table 5.8. Summary of Increment and Decrement Instructions Table 5.9. Summary of Compare Instructions Table 5.10. Summary of Logical Instructions (1/2) Table 5.11. Summary of Logical Instructions (2/2) Table 5.12. Summary of Multiply, Divide and Decimal-adjust Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5.4<br>5.5<br>5.5<br>5.6<br>5.7<br>5.8                                          |

| Table 5.8. Summary of Increment and Decrement Instructions Table 5.9. Summary of Compare Instructions Table 5.10. Summary of Logical Instructions (1/2) Table 5.11. Summary of Logical Instructions (2/2) Table 5.12. Summary of Multiply, Divide and Decimal-adjust Instructions Table 5.13. Summary of Move Instructions (1/3)                                                                                                                                                                                                                                                                                                                                                                                       | 5.4<br>5.5<br>5.5<br>5.6<br>5.7<br>5.8<br>5.8                                   |

| Table 5.8. Summary of Increment and Decrement Instructions Table 5.9. Summary of Compare Instructions Table 5.10. Summary of Logical Instructions (1/2) Table 5.11. Summary of Logical Instructions (2/2) Table 5.12. Summary of Multiply, Divide and Decimal-adjust Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5.4<br>5.5<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10                           |

| Table 5.8. Summary of Increment and Decrement Instructions  Table 5.9. Summary of Compare Instructions  Table 5.10. Summary of Logical Instructions (1/2)  Table 5.11. Summary of Logical Instructions (2/2)  Table 5.12. Summary of Multiply, Divide and Decimal-adjust Instructions  Table 5.13. Summary of Move Instructions (1/3)  Table 5.14. Summary of Move Instructions (2/3)  Table 5.15. Summary of Move Instructions (3/3)  Table 5.16. Summary of Bit Instructions                                                                                                                                                                                                                                         | 5.4<br>5.5<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.10                   |

| Table 5.8. Summary of Increment and Decrement Instructions Table 5.9. Summary of Compare Instructions Table 5.10. Summary of Logical Instructions (1/2) Table 5.11. Summary of Logical Instructions (2/2) Table 5.12. Summary of Multiply, Divide and Decimal-adjust Instructions Table 5.13. Summary of Move Instructions (1/3) Table 5.14. Summary of Move Instructions (2/3) Table 5.15. Summary of Move Instructions (3/3) Table 5.16. Summary of Bit Instructions Table 5.17. Summary of Exchange, Push and Pop Instructions                                                                                                                                                                                      | 5.4<br>5.5<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.12                   |

| Table 5.8. Summary of Increment and Decrement Instructions Table 5.9. Summary of Compare Instructions Table 5.10. Summary of Logical Instructions (1/2) Table 5.11. Summary of Logical Instructions (2/2) Table 5.12. Summary of Multiply, Divide and Decimal-adjust Instructions Table 5.13. Summary of Move Instructions (1/3) Table 5.14. Summary of Move Instructions (2/3) Table 5.15. Summary of Move Instructions (3/3) Table 5.16. Summary of Bit Instructions Table 5.17. Summary of Exchange, Push and Pop Instructions Table 5.18. Summary of Conditional Jump Instructions (1/2)                                                                                                                           | 5.4<br>5.5<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.12<br>5.13           |

| Table 5.8. Summary of Increment and Decrement Instructions Table 5.9. Summary of Compare Instructions Table 5.10. Summary of Logical Instructions (1/2) Table 5.11. Summary of Logical Instructions (2/2) Table 5.12. Summary of Multiply, Divide and Decimal-adjust Instructions Table 5.13. Summary of Move Instructions (1/3) Table 5.14. Summary of Move Instructions (2/3) Table 5.15. Summary of Move Instructions (3/3) Table 5.16. Summary of Bit Instructions Table 5.17. Summary of Exchange, Push and Pop Instructions                                                                                                                                                                                      | 5.4<br>5.5<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.10<br>5.12<br>5.13   |

# **TSC80251**

| Table 5.21. | Summary of Call and Return Instructions                     | 5.17 |

|-------------|-------------------------------------------------------------|------|

| Table 5.22. | Instructions for 80C51 Microcontrollers                     | 5.18 |

| Table 5.23. | New Instructions for the C251 Architecture                  | 5.19 |

| Table 5.24. | Data Instructions                                           | 5.20 |

| Table 5.25. | High Nibble, Byte 0 of Data Instructions                    | 5.20 |

| Table 5.26. | Bit Instructions                                            | 5.21 |

| Table 5.27. | Byte 1 (High Nibble) for Bit Instructions                   | 5.21 |

| Table 5.28. | PUSH/POP Instructions                                       | 5.21 |

| Table 5.29. | Control Instructions                                        | 5.22 |

| Table 5.30. | Displacement/Extended MOVs Instructions                     | 5.22 |

| Table 5.31. | INC/DEC Instructions                                        | 5.23 |

| Table 5.32. | Encoding for INC/DEC Instructions                           | 5.23 |

| Table 5.33. | Shifts Instructions                                         | 5.23 |

| Table 5.34. | State Times to Access the Port SFRs                         | 5.25 |

| Table 5.35. | Summary of Add and Subtract Instructions                    | 5.27 |

| Table 5.36. | Summary of Compare Instructions                             | 5.28 |

| Table 5.37. | Summary of Increment and Decrement Instructions             | 5.29 |

| Table 5.38. | Summary of Multiply, Divide and Decimal-adjust Instructions | 5.29 |

| Table 5.39. | Summary of Logical Instructions                             | 5.30 |

|             | Summary of Logical Instructions (Cont'd)                    |      |

| Table 5.41. | Summary of Move Instructions                                | 5.31 |

| Table 5.42. | Summary of Exchange, Push and Pop Instructions              | 5.34 |

| Table 5.43. | Summary of Bit Instructions                                 | 5.35 |

| Table 5 44  | Flag Symbols                                                | 5 36 |

## **Conventions**

The following notations and terminology are used in this manual. The Glossary defines all terms with special meanings.

# The pound symbol (#) has either of two meanings, depending on the context.

When used with a signal name, the symbol means that the signal is active low. When used in an instruction, the symbol prefixes an immediate value

in immediate addressing mode.

italics Italics identify variables and introduce new terminology. The context in

which italics are used distinguishes between two possible meanings.

Variables in registers and signal names are commonly represented by x and y, where x represents the first variable and y represents the second variable. For example, in register Px.y, x represents the variable that identifies the specific port, and y represents the register bit variable [7:0]. Variables must be replaced with the correct values when configuring or programming

registers or identifying signals.

**XXXX** Uppercase X (no italics) represents an unknown value or a "don't care" state

or condition. The value may be either binary or hexadecimal, depending on the context. For example, 2XAFh (hex) indicates that bits 11:8 are unknown; 10XXb in binary context indicates that the two Least Significant Bits are

unknown.

**Assert and Deassert** The terms Assert and Deassert refer to the act of making a signal active

(enabled) and inactive (disabled), respectively. The active polarity (high/low) is defined by the signal name. Active—low signals are designated by a pound symbol (#) suffix; active—high signals have no suffix. To assert RD# is to drive it low; to assert ALE is to drive it high; to deassert RD# is

to drive it high; to deassert ALE is to drive it low.

**Instructions** Instruction mnemonics are shown in upper case to avoid confusion. You may

use either upper case or lower case.

**Logic 0 (Low)** An input voltage level equal to or less than the maximum value of  $V_{IL}$  or an

output voltage level equal to or less than the maximum value of V<sub>OL</sub>. See

Product Datasheet for values.

**Logic 1 (High)** An input voltage level equal to or greater than the minimum value of V<sub>IH</sub> or

an output voltage level equal to or greater than the minimum value of V<sub>OH</sub>.

See Product Datasheet for values.

**Numbers** Hexadecimal numbers are represented by a string of hexadecimal digits

followed by the letter h. Decimal and binary numbers are represented by their customary notations: i.e. 255 is a decimal number and 1111 1111 is a binary number. In most cases of binary numbers, the letter b is added for

clarity.

**Register Bits** Bit locations are indexed by 7:0 for byte registers, 15:0 for word registers,

and 31:0 for double word (dword) registers. Bit 0 is the least significant bit

## **TSC80251**

and 7, 15 or 31 are the most significant bits. An individual bit is represented by the register name, followed by a period and the bit number. For example, PCON.4 is bit 4 of the Power Control register. In some discussions, bit names are used. For example, the name of PCON.4 is POF, the Power Off flag.

**Register Names** Register names are shown in upper case. For example, PCON is the Power

Control register. If a register name contains a lowercase character, it represents more than one register. For example, CCAPMx (x = 0, 1, 2, 3, 4)

represents the five registers: CCAPM0 through CCAPM4.

**Reserved Bits** Some registers contain reserved bits. These bits are not used in this device

but they may be used in future implementations. Pay attention to the

recommendations when manipulating theses bits.

**Set and Clear** The terms Set and Clear refer to the value of a bit or the act of giving it a

value. If a bit is Set, its value is "1"; setting a bit gives it a "1" value. If a bit

is Clear, its value is "0"; clearing a bit gives it a "0" value.

## Introduction

### 1.1. 8/16-bit microcontroller

In the world of 8/16-bit microcontrollers, the C51 Architecture has become an industry standard for embedded applications. For over 15 years, TEMIC has been a leading provider of this microcontroller family. This unsurpassed experience is the driving force as TEMIC takes this proven family to the next level of performance: the TSC80251 family!

This new C251 Architecture at its lowest performance level (binary mode), is binary code compatible with the 80C51 microcontrollers, hence, attaining an increase in performance has never been easier.

Due to a 3-stage pipeline, the CPU-performance is increased by a factor 5, using existing C51 code without modifications.

Using the new C251 instruction set, which you will find in this document (See Chapter 5), the performance will increase up to 15 times at the same clock rate. This performance enhancement is based on the 16-bit instruction bus, allowing for more powerful instructions and additional internal instruction bus, 8-bit and 16-bit data busses.

The 24-bit address bus will allow to access up to 16 Mbytes in a single linear memory space. Please see each individual TSC80251 Product Design Guide for the effective addressable memory range.

Programming flexibility and C-code efficiency are both increased through a Register-based Architecture, the 64-Kbyte extended stack space combining with the new instruction set.

C251 C-compilers are some of the most efficient available (nearly no overhead), coupled with the final codesize which could be a factor of 3 down when compared with the C51 C-compilers.

All technical information in this document about core features are related to the core revision A and core revision D.

### 1.2. TSC80251 Derivatives

TEMIC is developing a full family of application specific TSC80251 derivatives. Please see the Design Guide of each product for further information.

These products are designed to help you getting high-performance products to market faster.

Due to the high instruction throughput, the TSC80251 derivatives are focussing on all high-end 8-bit to 16-bit applications.

TSC80251 derivatives are also used in mid-range and lower-end microcontroller applications, where a very low operation frequency is needed, without decreasing the level of CPU-power.

This feature is ideal for today portable applications and EMC sensitive systems.

## **TSC80251**

Typical applications for this family are:

- Automotive:

- Airbag

- ABS

- Gearbox

- Climate control

- Car radio

- Car navigation

- Communication:

- Cordless phones

- Cellular phones

- High speed modems

- High-end feature phones

- ISDN phones

- Line cards

- Network termination

- Computer:

- High-end monitors

- DVD–ROM

- Magtape card & smart card readers

- Barcodes readers

- Computer telephony

- Force feedback joysticks

- Industrial:

- Process monitoring control & readouts

- Air conditioning systems

- Automation

TEMIC's TSC80251 derivatives are designed around the C251 core, using standard peripherals dedicated to a targetted range of applications.

Here is a selection of peripheral blocks:

- Serial interfaces:

- UART (Universal Asynchronous Receiver Transmitter)

- I2C (Inter–Integrated Circuit)

- SPI (Serial Protocol Interface)

- μWire (Synchronous Serial Interface)

- Special Functions:

- PCA: Programmable Counter Array (5 × 16-bit modules)

- High-speed output

- Compare/Capture I/O

- 8-bit Pulse Width Modulator (PWM)

- ADC (Analog to Digital Converter)

- Smart sensor interfaces with PMU (Pulse Measurement Unit)

- Control functions:

- Watchdog Timer

- Timers/Counters

- Power monitoring and management

- Interrupt handler

- Memories:

- RAM

- ROM

- EPROM/OTPROM

Most of TEMIC's TSC80251 derivatives are available as ROMless, OTPROM, EPROM and Mask ROM version. For any special request, refer to TEMIC sales representative.

## 1.3. TSC80251 Documentation

The following documentation and starter tools are available to allow the full evaluation of the TEMIC's TSC80251 derivatives:

- "TSC80251 Programmer's Guide"

- Contains all information for the programmer (Architecture, Instruction Set, Programming).

- "TSC80251 Design Guide"

- Contains all product specific data and a summary of available application notes.

- Application Notes

- "TSC80251 Product Starter Kit"

- This kit enables the product to be evaluated by the designer.

- Its contents is

- C-Compiler (limited to 2 Kbytes of code)

- Assembler

- Linker

- Product Simulator

- TSC80251 Product Evaluation Board with ROM–Monitor

- EPROM and ROMless samples of the available derivatives

- Please visit our WWW for updated versions in ZIP format.

- World Wide Web

- Please contact our WWW for possible updated information at http://www.temic-semi.com

- Technical support: C251@temic-semi.com

## **Architectural Overview**

### 2.1. Microcontroller Architecture

The TSC80251 family of 8/16-bit microcontrollers is a high performance upgrade of the widely used 80C51 microcontrollers. It extends features and performance while maintaining binary code compatibility, so the impact on existing hardware and software is minimal.

#### The C251 Architecture core contains:

- 24-bit linear addressing and up to 16 Mbytes of memory

- a register file based CPU with registers accessible as bytes, words, and double words

- a page mode for accelerating external instruction fetches

- an instruction pipeline

- an enriched instruction set, including 16-bit arithmetic and logic instructions

- a 64–Kbyte extended stack space

- a minimum instruction–execution time of two clocks (vs. 12 clocks for 80C51 microcontrollers)

- binary-code compatibility with 80C51 microcontrollers

#### Several benefits are derived from these features:

- preservation of code written for 80C51 microcontrollers

- a significant increase in core execution speed in comparison with 80C51 microcontrollers at the same clock rate

- support for larger programs and more data

- increased efficiency for code written in C language

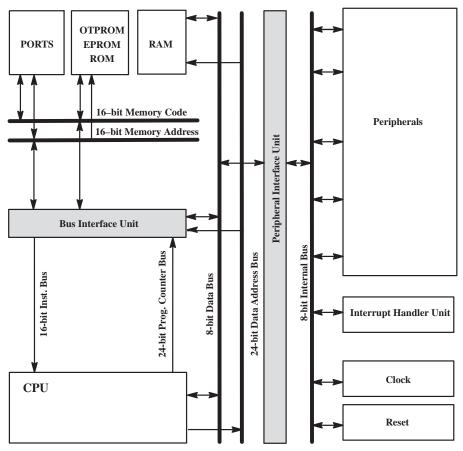

Figure 2.1. is a functional block diagram of TSC80251 microcontrollers. The core, which is common to all TSC80251 microcontrollers, is described in the next paragraph. Each derivative in the family has its own on–chip peripherals, I/O Ports, external bus, size of on–chip RAM, type and size of on–chip ROM.

Figure 2.1. TSC80251 Product Block Diagram

## 2.2. Microcontroller Core

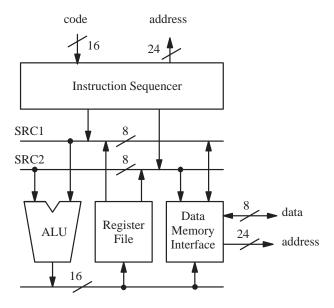

The TSC80251 microcontroller core contains the CPU, the clock and reset unit, the interrupt handler, the bus interface and the peripheral interface (See Figure 2.1.). The CPU contains the instruction sequencer, ALU, register file and data memory interface (See Figure 2.2.).

### 2.2.1. CPU

The TSC80251 fetches instructions from on–chip code memory two bytes at a time or from external memory one byte at a time. The instructions are sent over the 16–bit instruction bus to the CPU. You can configure the TSC80251 to operate in page mode for accelerated instruction fetches from external memory. In page mode, if an instruction fetch is to the same 256–byte "page" as the previous fetch, the fetch requires one state (two clocks) rather than two states (four clocks). For information regarding the page or non–page mode selection, see Product Design Guide.

The TSC80251 register file has 40 registers, which can be accessed as bytes (8–bit data), words (16–bit data) and double words (32–bit data). As in the C51 Architecture, registers 0-7 consist of four banks of eight registers each, where the active bank is selected by the Program Status Word (PSW) for fast context switches (See "Programming" chapter).

The TSC80251 CPU is a pipeline machine. When the pipeline is full and code is executing from on—chip code memory, an instruction can be completed every state time. When the pipeline is full and code is executing from external memory (with no wait states and no extension of the ALE signal) an instruction can be completed every two state times.

Figure 2.2. Central Processor Unit Block Diagram

#### 2.2.2. Clock and Reset Unit

The timing source for the TSC80251 microcontroller can be an external oscillator or an internal oscillator with an external crystal/resonator. The basic unit of time in TSC80251 is the state time (or state), which is two oscillator periods. The state time is divided into phase P1 and phase P2 (See Figure 2.3.).

Figure 2.3. Clocking Definitions

The TSC80251 peripherals operate on a peripheral cycle, which is six state times (this peripheral cycle is not a characteristic of the C251 Architecture). A one–clock interval in a peripheral cycle is denoted by its state and phase (SxPy). For simplicity purpose, XTAL1 signal has been used in this figure. In fact this is the prescaler output that drives the core. The clock prescaler being a software programmable device, the effective core clock can be dynamically adapted to the application speed and power consumption needs.

The reset unit places the TSC80251 into a known state. A chip reset is initiated by asserting the RST pin or allowing the Watchdog Timer to time out when the TSC80251 has one.

## 2.2.3. Interrupt Handler Unit

The Interrupt Handler Unit can receive interrupt requests from many sources: internal peripheral sources, external sources and TRAP instruction. When the interrupt handler grants an interrupt request, the CPU discontinues the normal flow of instructions and branches to a routine that services the source that requested the interrupt. You can enable or disable the interrupts individually (except for TRAP and NMI which cannot be disabled) and you can chose among one to four priority levels for each interrupt.

## **Address Spaces**

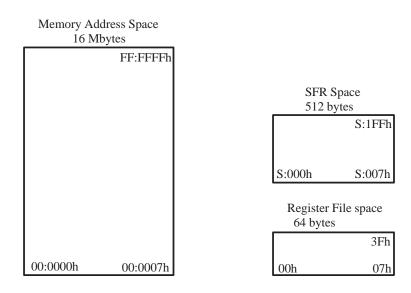

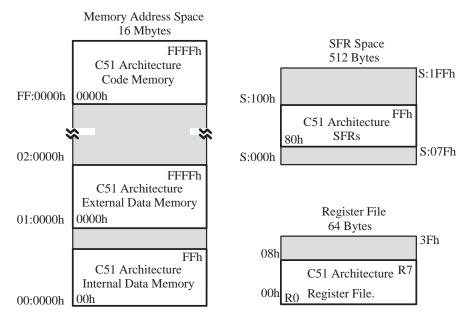

TSC80251 microcontrollers have three address spaces: a memory space, a Special Function Register (SFR) space and a register file. This chapter describes these address spaces as they apply to all TSC80251 microcontrollers. It also discusses the compatibility of the C251 Architecture and the C51 Architecture in terms of their address spaces.

## 3.1. C251 Architecture Address Spaces

Figure 3.1. shows the three address spaces: i.e. memory space, SFR space and register file for TSC80251 microcontrollers. The address spaces are depicted as being 8-byte wide with addresses increasing from left to right and from bottom to top (See Figure 3.1.).

Figure 3.1. Address Spaces for TSC80251 Microcontrollers

It is convenient to view the unsegmented, 16–Mbyte memory space as consisting of 256 64–Kbyte regions, numbered 00: to FF:.

#### Note:

The memory space in the C251 Architecture is unsegmented. The 64– Kbyte "region" 00:, 01:, ..., FF: are introduced only as a convenience for discussions. Addressing in the C251 Architecture is linear; there are no segment registers.

TSC80251 microcontrollers can have up to 64–Kbytes of on–chip code memory in region FF:. On–chip data RAM begins at location 00:0000h. The first 32 bytes (00:0000h-00:001Fh) provide storage for a part of the register file. The sizes of the on–chip code memory and on–chip RAM depend on the particular device.

The register file has its own address space (See Figure 3.1.). The 64 locations in the register file are numbered decimally from 0 to 63. Locations 0-7 represent one of four, switchable register banks, each having 8 registers. The 32 bytes required for these banks occupy locations 00:0000h-00:001Fh in the memory space. Register file locations 8-63 do not appear in the memory space and are new hardware resources of the C251 Architecture.

The SFR space can accommodate up to 512 8-bit Special Function Registers with addresses S:000h-S:1FFh. Some of these locations may be unimplemented in a particular device. In the C251 Architecture, the prefix "S:" is used with SFR addresses to distinguish them from the memory space addresses 00:0000h-00:01FFh.

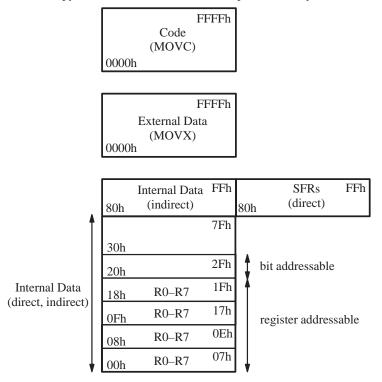

## 3.2. C51 Architecture Address Spaces

Figure 3.2. shows the address spaces of the C51 Architecture. Internal data memory locations 00h-7Fh can be addressed directly, indirectly by register addressing mode and bit addressing mode for data locations 20h–2Fh. Internal data locations 80h-FFh can only be addressed indirectly. Directly addressing these locations accesses the SFRs. The 64–Kbyte code memory has a separate memory space. Data in the code memory can be accessed only with the MOVC instruction. Similarly, the 64–Kbyte external data memory can be accessed only with the MOVX instruction.

The register file (registers R0-R7) comprises four, switchable register banks, each having 8 registers. The 32 bytes required for the four banks occupy locations 00h-1Fh in the on–chip data memory.

Figure 3.2. Address Spaces for the C51 Architecture

## 3.3. C51 Architecture mapping to C251 Architecture Address Spaces

The 64–Kbyte code memory for 80C51 microcontrollers maps into region FF: of the memory space for TSC80251 microcontrollers. Assemblers for TSC80251 microcontrollers assemble code for 80C51 microcontrollers into region FF:, and data accesses to code memory (MOVC) are directed to this region. The assembler also maps the interrupt vectors to region FF:. This mapping is transparent to the user; code executes just as with a 80C51 micro without modification.

|       | 2 1  | A 1 1     | T .             |

|-------|------|-----------|-----------------|

| Table | 3 I  | Address   | <b>Mappings</b> |

| IUDIC | O.I. | 11uul Coo | Manhamen        |

| M T           | C51 Architecture |             |                     | C251 Architecture |

|---------------|------------------|-------------|---------------------|-------------------|

| Memory Type   | Size             | Location    | Data Addressing     | Location          |

| Code          | 64 Kbytes        | 0000h-FFFFh | Indirect using MOVC | FF:0000h-FF:FFFFh |

| External Data | 64 Kbytes        | 0000h-FFFFh | Indirect using MOVX | 01:0000h-01:FFFFh |

|               | 128 bytes        | 00h-7Fh     | Direct, Indirect    | 00:0000h-00:007Fh |

| Internal Data | 128 bytes        | 80h-FFh     | Indirect            | 00:0080h-00:00FFh |

| SFRs          | 128 bytes        | S:80h-S:FFh | Direct              | S:0080h-S:0FFh    |

| Register      | 8 bytes          | R0-R7       | Register            | 00:0000h-00:001Fh |

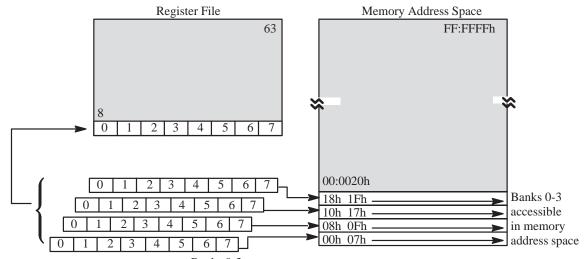

The 64–Kbyte external data memory for 80C51 microcontrollers is mapped into the memory region specified by bits 16–23 of the data pointer DPX, i.e., DPXL, which is accessible as register file location 57 and also as SFR at S:084h. The reset value of DPXL is 01h, which maps the external memory to region 01: as shown in Figure 3.3. You can change this mapping by writing a different value to DPXL. A mapping of the C51 Architecture external data memory into any 64–Kbyte memory region in the C251 Architecture provides complete runtime compatibility because the lower 16 address bits are identical in both architectures.

The 256 bytes of on-chip data memory for 80C51 microcontrollers (00h-FFh) are mapped to addresses 00:0000h-00:00FFh to ensure complete runtime compatibility. In the C51 Architecture, the lower 128 bytes (00h-7Fh) are directly and indirectly addressable; however the upper 128 bytes are accessible by indirect addressing only. In the C251 Architecture, all locations in region 00: are accessible by direct, indirect, and displacement addressing.

The 128-byte SFR space for 80C51 microcontrollers is mapped into the 512-byte SFR space of the C251 Architecture starting at address S:080h, as shown in Figure 3.3. This provides complete compatibility with direct addressing of 80C51 microcontroller SFRs (including bit addressing). The SFR addresses are unchanged in the new Architecture. In the C251 Architecture, SFRs, A, B, DPL, DPH and SP, as well as the new DPXL and SPH, reside in the register file for high performance. However, to maintain compatibility, they are also mapped into the SFR space at the same addresses as in the C51 Architecture.

Figure 3.3. Mappings C51 Architecture to C251 Architecture Address Spaces

Figure 3.4. TSC80251 Memory Space

## 3.4. TSC80251 Register File

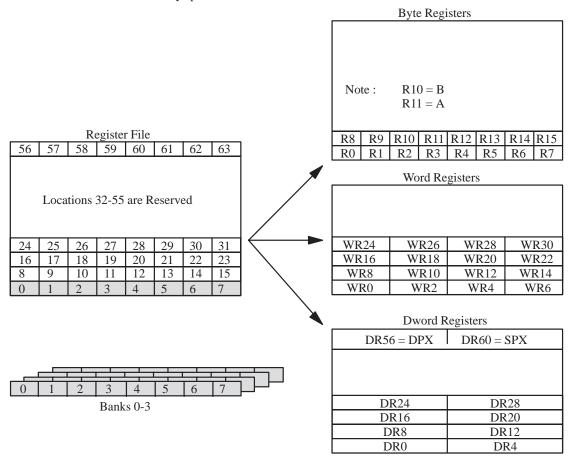

The TSC80251 register file consists of 40 byte locations: 0-31 and 56-63, as shown in Figure 3.5. These locations are accessible as bits, bytes, words and dwords. Several locations are dedicated to special registers; the others are general–purpose registers.

Register file locations 0-7 actually consist of four switchable banks of eight registers each, as illustrated in Figure 3.6. The four banks are implemented as the first 32 bytes of on—chip RAM and are always accessible as locations 00:0000h-00:001Fh in the memory address space. Only one of the four banks is accessible via the register file at a given time. The accessible, or "active", bank is selected by bits RS1 and RS0 in the PSW register, as shown in Table 3.2. This bank selection can be used for fast context switches.

Register file locations 8-31 and 56-63 are always accessible. These locations are implemented as registers in the CPU. Register file locations 32-55 are reserved and cannot be accessed.

| Danila | A JJ D        | PSW Sele | ection Bits |

|--------|---------------|----------|-------------|

| Bank   | Address Range | RS1      | RS0         |

| Bank 0 | 00h-07h       | 0        | 0           |

| Bank 1 | 08h-0Fh       | 0        | 1           |

| Bank 2 | 10h-17h       | 1        | 0           |

| Bank 3 | 18h-1Fh       | 1        | 1           |

**Table 3.2. Register Bank Selection**

## 3.4.1. Byte, Word and Dword Registers

Depending on its location in the register file, a register is addressable as a byte, a word, or a dword, as shown in the right side of Figure 3.5. A register is named for its lowest numbered byte location. For instance:

- R4 is the byte register consisting of location 4.

- WR4 is the word register consisting of registers 4 and 5.

- DR4 is the dword register consisting of registers 4, 5, 6, and 7.

Locations R0-R15 are addressable as bytes, words or dwords. Locations 16-31 are addressable only as words or dwords. Locations 56-63 are addressable only as dwords. Registers are addressed only by the names shown in Figure 3.5., except for the 32 registers that comprise the four banks of registers R0-R7, which can also be accessed as locations 00:0000h-00:001Fh in the memory space.

Figure 3.5. Register File in Byte, Word, and Dword Register Views

PSW bits RS1:0 select one bank to be accessed via the register file.

Banks 0-3

Figure 3.6. Register File Locations 0-7

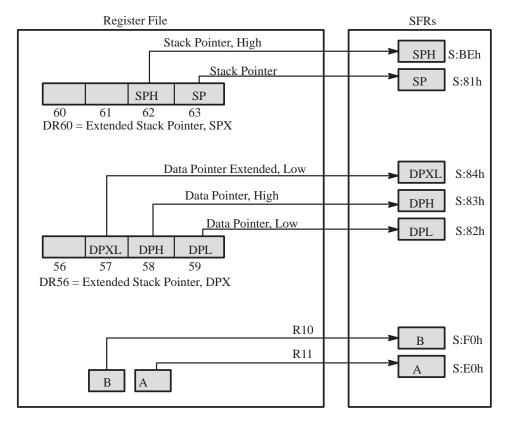

## 3.4.2. Dedicated Registers

The register file has four dedicated registers:

- R10 is the B-register.

- R11 is the accumulator (A).

- DR56 is the extended data pointer, DPX.

- DR60 is the extended stack pointer, SPX.

These registers are located in the register file; however, R10, R11 and some bytes of DR56 and DR60 are also accessible as SFRs. The bytes of DPX and SPX can be accessed in the register file only by addressing the dword registers. The dedicated registers in the register file and their corresponding SFRs are illustrated in Figure 3.7. and listed in Table 3.3.

Table 3.3. Dedicated Registers in the Register File and their Corresponding SFRs

| Register File                    |           |                    |          |      | SFRs     |          |         |

|----------------------------------|-----------|--------------------|----------|------|----------|----------|---------|

|                                  | Nam       | e                  | Mnemonic | Reg. | Location | Mnemonic | Address |

| Stack Pointer                    |           | _                  | -        |      | 60       | _        | _       |

| (SPX)                            |           | _                  | -        |      | 61       | _        | _       |

|                                  | Stack Poi | nter, High         | SPH      | DR60 | 62       | SPH      | S:BEh   |

| Stack Pointer, Low               |           | SP                 |          | 63   | SP       | S:81h    |         |

| Data Pointer –                   |           | -                  |          | 56   | _        | -        |         |

| (DPX) Data Pointer, Extended Low |           | DPXL               |          | 57   | DPXL     | S:84h    |         |

|                                  | DPTR      | Data Pointer, High | DPH      | DR56 | 58       | DPH      | S:83h   |

|                                  |           | Data Pointer, Low  | DPL      |      | 59       | DPL      | S:82h   |

| Accumulator (A Register)         |           | A                  | R11      | 11   | A        | S:E0h    |         |

| B Register                       |           | В                  | R10      | 10   | В        | S:F0h    |         |

#### 3.4.2.1. Accumulator and B Register

The 8-bit accumulator (A) is byte register R11, which is also accessible in the SFR space as A at S:0E0h (See Figure 3.7.). The B register, used in multiplies and divides, is register R10, which is also accessible in the SFR space as B at S:0F0h. Accessing A or B as a register is one state faster than accessing them as SFRs.

Instructions in the C51 Architecture use the accumulator as the primary register for data moves and calculations. however, in the C251 Architecture, any of registers R1-R15 can serve for these tasks. As a result, the accumulator does not play the central role that it has in 80C51 microcontrollers.

#### 3.4.2.2. Extended Data Pointer, DPX

Dword register DR56 is the extended data pointer, DPX (See Figure 3.7.). The lower three bytes of DPX (DPL, DPH and DPXL) are accessible as SFRs. DPL and DPH comprise the 16-bit data pointer DPTR. While instructions in the C51 Architecture always use DPTR as the data pointer, instructions in the C251 Architecture can use any word or dword register as a data pointer.

DPXL, the byte in location 57, specifies the region of memory (00:-FF:) that maps into the 64–Kbyte external data memory space in the C51 Architecture. In other words, the MOVX instruction addresses the region specified by DPXL when it moves data to and from external memory. The reset value of DPXL is 01h.

### 3.4.2.3. Extended Stack Pointer, SPX

Dword register DR60 is the stack pointer, SPX (See Figure 3.7.). The byte at (location 63) is the 8-bit stack pointer, SP, in the C51 Architecture. The byte at location 62 is the stack pointer high, SPH. The two bytes allow the stack to extend to the top of memory region 00:. SP and SPH can be accessed as SFRs.

Two instructions, PUSH and POP directly address the stack pointer. Subroutine calls (ACALL, ECALL, LCALL) and returns (ERET, RET, RETI) also use the stack pointer. To preserve the stack, do not use DR60 as a general–purpose register.

Figure 3.7. Dedicated Registers in the Register File and their Corresponding SFRs

## 3.5. Special Function Registers (SFRs)

The Special Function Registers (SFRs) reside in their associated on—chip peripherals or in the core. SFR addresses are preceded by "S:" to differentiate them from addresses in the memory space. Unoccupied locations in the SFR space are unimplemented, i.e., no register exists. If an unimplemented SFR location is read, it returns an unspecified value.

#### Note:

SFRs may be accessed only as bytes; they may not be accessed as words or dwords.

Table 3.4. Core SFRs

| Mnemonic | Name                              | Address |

|----------|-----------------------------------|---------|

| A*       | Accumulator                       | S:E0h   |

| B *      | B register                        | S:F0h   |

| PW       | Program Status Word               | S:D0h   |

| PSW1     | Program Status Word 1             | S:D1h   |

| SP       | Stack Pointer - LSB of SPX        | S:81h   |

| SPH *    | Stack Pointer high - MSB of SPX   | S:BEh   |

| DPTR *   | Data Pointer (2 bytes)            | _       |

| DPL *    | Low Byte of DPTR                  | S:82h   |

| DPH *    | high Byte of DPTR                 | S:83h   |

| DPXL *   | Data Pointer, Extended Low        | S:84h   |

| IE0      | Interrupt Enable Control 0        | S:A8h   |

| IE1      | Interrupt Enable Control 1        | S:B1h   |

| IPL0     | Interrupt Priority Control Low 0  | S:B8h   |

| IPL1     | Interrupt Priority Control Low 1  | S:B3h   |

| IPH0     | Interrupt Priority Control High 0 | S:B7h   |

| IPH1     | Interrupt Priority Control High 1 | S:B2h   |

#### Note

<sup>\*</sup>These SFRs can also be accessed by their corresponding registers in the register file (See Table 3.3.

## **Programming**

The instruction set for the C251 Architecture is a superset of the instruction set for the C51 Architecture. This chapter describes the addressing modes and summarizes the instruction set, which is divided into data instructions, bit instructions, and control instructions. (Chapter 5, "Instruction Set Reference" contains an opcode map and the detailed description of each instruction.)

#### **Notes:**

- The instruction execution times given in Chapter 5 are for code executing from on-chip code memory and for data that is read from and written to on-chip RAM. Execution times are increased by executing code from external memory, accessing peripheral SFRs, accessing data in external memory, using a wait state, or extending the ALE pulse.

- For some instructions, accessing the port SFRs, Px (x = 0, 1, 2, 3) increases the execution time. These cases are noted individually in the tables in Chapter 5.

## 4.1. Source Mode or Binary Mode Opcodes

Source mode and Binary mode refer to the two ways of assigning opcodes to the instruction set of the C251 Architecture. Depending on the application, one mode or the other may produce more efficient code. The mode is established during device reset based on the value of the SRC bit in configuration byte CONFIGO. For information regarding the configuration bytes, see the Product Design Guide.

Binary mode and source mode refer to two ways of assigning opcodes to the instruction set for the C251 Architecture. One of these modes must be selected when the chip is configured. Depending on the application, binary mode or source mode may produce more efficient code. This section describes the binary and source modes and provides some guidelines for selecting the mode for your application.

The C251 Architecture has two types of instructions:

- Instructions that originate in the C51 Architecture

- Instructions that are unique to the C251 Architecture

Figure 4.1. shows the opcode map for the binary mode. Area I and area II make up the opcode map for the instructions that are unique to the C251 Architecture. Note that some of these opcodes are reserved for future instructions. The opcode values for areas II and III are identical (06H–FFH). To distinguish between the two areas in binary mode, the opcodes in area III are given the prefix A5H (the A5H instruction is not implemented in the native C51 Architecture). The area III opcodes are thus A506H–A5FFH.

Figure 4.2. shows the opcode map for source mode. Areas II and III have switched places (compare with Figure 4.1.). In source mode, opcodes for instructions in area II require the A5F escape prefix while opcodes for instructions in area III (C251 Architecture) do not.

To illustrate the difference between the binary-mode and source-mode opcodes, Table 4.1. shows the opcode assignments for three sample instructions.

Table 4.1. Examples of Opcodes in Binary and Source Modes

| Instruction | Opcode      |             |

|-------------|-------------|-------------|

|             | Binary Mode | Source Mode |

| DEC A       | 14H         | 14CH        |

| SUBB A, R4  | 9CH         | A59CH       |

| SUB R4, R4  | A59CH       | 9CH         |

### 4.1.1. Selecting Binary Mode or Source Mode

If you have code that was written for a C51 microcontroller and you want to run it unmodified on a C251 microcontroller, choose binary mode. You can use the object code without reassembling the source code. You can also assemble the source code with an assembler for the C251 Architecture and have it produce object code that is binary—compatible with C51 microcontrollers. The remainder of this section discusses the selection of binary mode or source mode for code that may contain instructions from both architectures.

An instruction with a prefixed opcode requires one more byte for code storage, and if an additional fetch is required for the extra byte, the execution time is increased by one state. This means that using fewer prefixed opcodes produces more efficient code.

If a program uses only instructions from the C51 Architecture, the binary–mode code is more efficient because it uses no prefixes. On the other hand, if a program uses many more new instructions than instructions from the C51 Architecture, source mode is likely to produce more efficient code. For a program where the choice is not clear, the better mode can be found by experimenting with a simulator.

Figure 4.1. Binary Mode Opcode Map

Figure 4.2. Source Mode Opcode Map

## 4.2. Programming Features of the C251 Architecture

The instruction set for TSC80251 microcontrollers provides the user with new instructions that exploit the features of the C251 Architecture while maintaining compatibility with the instruction set for 80C51 microcontrollers. Many of the new instructions can operate on either 8-bit (byte), 16-bit (word) or 32-bit (dword) operands (In comparison with 8-bit and 16-bit operands, 32-bit operands are accessed with fewer addressing modes.). This capability increases the ease and efficiency of programming TSC80251 microcontrollers in a high-level language such as C.

The instruction set is divided into "Data Instructions", "Bit Instructions" and "Control Instructions". Data instructions process 8-bit, 16-bit and 32-bit data; bit instructions manipulate bits; and control instructions manage program flow.

## 4.2.1. Data Types

Table 4.2. lists the data types that are addressed by the instruction set. Words or dwords (double words) can be stored in memory starting at any byte address; alignment on two–byte or four–byte boundaries is not required. Words and dwords are stored in memory and the register file in big endian form.

Table 4.2. Data Types

| Data Type           | Number of Bits |

|---------------------|----------------|

| Bit                 | 1              |

| Byte                | 8              |

| Word                | 16             |

| Dword (Double Word) | 32             |

### 4.2.1.1. Order of Byte Storage for Words and Double Words

TSC80251 microcontrollers store words (2 bytes) and double words (4 bytes) in memory and in the register file in big endian form. In memory storage, the most significant byte (MSB) of the word or double word is stored in the memory byte specified in the instruction; the remaining bytes are stored at higher addresses, with the least significant byte (LSB) at the highest address. Words and double words can be stored in memory starting at any byte address. In the register file, the MSB is stored in the lowest byte of the register specified in the instruction. The code fragment in Figure 4.3. illustrates the storage of words and double words in big endian form.

## 4.2.2. Register Notations

In register–addressing instructions, specific indices denote the registers that can be used in that instruction. For example, the instruction ADD A,Rn uses "Rn" to denote any one of R0, R1, ..., R7; i.e., the range of n is 0-7. The instruction ADD Rm,#data uses "Rm" to denote R0, R1, ..., R15; i.e., the range of m is 0-15. Table 4.3. summarizes the notation used for the register indices. When an instruction contains two registers of the same type (e.g., MOV Rmd,Rms) the first index "d" denotes "destination" and the second index "s" denotes "source".

#### 4.2.3. Address Notations

In the C251 Architecture, memory addresses include a region number (00:, 01:, ..., FF:). SFR addresses have a prefix "S:" (S:000h-S:1FFh). The distinction between memory addresses and SFR addresses is necessary, because memory locations 00:0000h-00:01FFh and SFR locations S:000h-S:1FFh can both be directly addressed in an instruction.

Contents of register file and memory after execution: MOV WR0, #A3B6h

MOV 00:0201h, WR0 MOV DR4, #0000C4D7h

Figure 4.3. Word and Double-word Storage in Big Endian Form

| Table 4.3 | . Notation       | for Byte | Registers.  | Word Registers. | and Dword Registers    |

|-----------|------------------|----------|-------------|-----------------|------------------------|

| IUDIC III | · I I O COLCIOII | LIUI DYC | TICE INCOLU | TOTAL TECTION   | alla D Wol a legistels |

| Register Type | Register<br>Symbol | Destination<br>Register | Source<br>Register | Register Range                  |

|---------------|--------------------|-------------------------|--------------------|---------------------------------|

|               | Ri                 | _                       | _                  | R0, R1                          |

| Byte          | Rn                 | _                       | _                  | R0-R7                           |

| 2,00          | Rm                 | Rmd                     | Rms                | R0-R15                          |

| Word          | WRj                | WRjd                    | WRjs               | WR0, WR2, WR4,, WR30            |

| Dword         | DRk                | DRkd                    | DRks               | DR0, DR4, DR8,, DR28,DR56, DR60 |

Instructions in the C51 Architecture use 80h-FFh as addresses for both memory locations and SFRs, because memory locations are addressed only indirectly and SFR locations are addressed only directly. For compatibility, software tools for TSC80251 controllers recognize this notation for instructions in the C51 Architecture. No change is necessary in any code written for 80C51 microcontrollers.

For new instructions in the C251 Architecture, the memory region prefixes (00:, 01:, ..., FF:) and the SFR prefix (S:) are required. Also, software tools for the C251 Architecture permit 00: to be used for memory addresses 00h-FFh and permit the prefix S: to be used for SFR addresses in instructions in the C51 Architecture.

## 4.2.4. Addressing Modes

The C251 Architecture supports the following addressing modes:

- Register addressing

- The instruction specifies the register that contains the operand.

- Immediate addressing

- The instruction contains the operand.

- Direct addressing

- The instruction contains the operand address.

- Indirect addressing

- The instruction specifies the register that contains the operand address.

- Displacement addressing

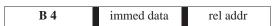

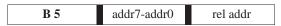

- The instruction specifies a register and an offset. The operand address is the sum of the register contents (the base address) and the offset.

- Relative addressing

- The instruction contains the signed offset from the next instruction to the target address (the address for transfer of control, e.g., the jump address).

- Bit addressing

- The instruction contains the bit address.

## 4.3. Program Status Words

The Program Status Word (PSW) register and the Program Status Word 1 (PSW1) register contain four types of bits (See Figure 4.7. and Figure 4.8.):

- CY, AC, OV, N and Z are flags set by hardware to indicate the result of an operation.

- The P bit indicates the parity of the accumulator.

- Bits RS0 and RS1 are programmed by software to select the active register bank for registers R0-R7.

- F0 and UD are available to the user as general—purpose flags.

The PSW and PSW1 registers are read/write registers; however, the parity bit in the PSW is not affected by a write. Individual bits can be addressed with the bit instructions ("Bit Instructions"). The PSW and PSW1 bits are used implicitly in the conditional jump instructions ("Conditional Jumps").

The PSW register is identical to the PSW register in 80C51 microcontrollers. The PSW1 register exists only in TSC80251 microcontrollers. Bits CY, AC, RS0, RS1, and OV in PSW1 are identical to the corresponding bits in PSW, i.e., the same bit can be accessed in either register. Table 4.4. lists the instructions that affect the CY, AC, OV, N and Z bits.

Table 4.4. The Efffects of Instructions on the PSW and PSW1 Flags

| Instruction | Instruction                               |   | Flags Affected (1) |        |   |   |  |

|-------------|-------------------------------------------|---|--------------------|--------|---|---|--|

| Type        |                                           |   | ov                 | AC (2) | N | Z |  |

|             | ADD, ADDC, SUB, CMP                       | X | X                  | X      | X | X |  |

|             | INC, DEC                                  |   |                    |        | X | X |  |

| Arithmetic  | MUL, DIV (3)                              | 0 | X                  |        | X | X |  |

|             | DA                                        | X |                    |        | X | X |  |

|             | ANL, ORL, XRL, CLR A, CPL A, RL, RR, SWAP |   |                    |        | X | X |  |

| Logical     | RLC, RRC, SRL, SLL, SRA (4)               | X |                    |        | X | X |  |

| Program     | CJNE                                      | X |                    |        | X | X |  |

| Control     | DJNE                                      |   |                    |        | X | X |  |

#### Notes:

## 4.4. Data Instructions

Data instructions consist of arithmetic, logical, and data-transfer instructions for 8-bit, 16-bit and 32-bit data. This section describes the data addressing modes and the set of data instructions.

## 4.4.1. Data Addressing Modes

This section describes the data addressing modes, which are summarized in two tables: Table 4.6. for the instructions that are native to the C51 Architecture and Table 4.6. for the data instructions unique to the C251 Architecture.

#### Notes:

- References to registers R0-R7, WR0-WR6, DR0 and DR4 always refer to the register bank that is currently selected

by the PSW and PSW1 registers. Registers in all banks (active and inactive) can be accessed as memory locations

in the range 00h-1Fh.

- Instructions from the C51 Architecture access external memory through the region of memory specified by byte DPXL in the extended data pointer register, DPX (DR56). Following reset, DPXL contains 01h, which maps the external memory to region 01:. You can specify a different region by writing to DR56 or the DPXL SFR.

#### 4.4.1.1. Addressable Registers

Both Architectures address registers directly.

- C251 Architecture

- In the register addressing mode, the operand(s) in a data instruction are in byte registers (R0-R15), word registers (WR0, WR2, ..., WR30) or dword registers (DR0, DR4, ..., DR28, DR56, DR60).

- C51 Architecture Instructions address registers R0-R7 only.

<sup>1.</sup> X =the flag can be affected by the instruction. 0 =the flag is cleared by the instruction.

<sup>2.</sup> The AC flag is affected only by operations on 8-bit operands.

<sup>3.</sup> If the divisor is zero, the OV flag is set, and the other bits are meaningless.

<sup>4.</sup> For SRL, SLL and SRA instructions, the last bit shifted out is stored in the CY bit.

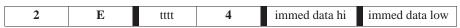

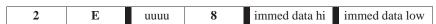

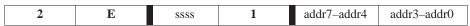

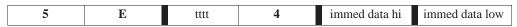

#### 4.4.1.2. Immediate Addressing

#### • C251 Architecture

In the immediate addressing mode, the instruction contains the data operand itself. Byte operations use 8-bit immediate data (#data16), word operations use 16-bit immediate data (#data16). Dword operations use 16-bit immediate data in the lower word and either zeros in the upper word (denoted by #0data16) or ones in the upper word (denoted by #1data16). MOV instructions that place 16-bit immediate data into a dword register (DRk), place the data either into the upper word while leaving the lower word unchanged, or into the lower word with a sign extension or a zero extension.

The increment and decrement instructions contain immediate data (#short = 1, 2, or 4), which specifies the amount of the increment/decrement.

C51 Architecture Instructions use only 8-bit immediate data (#data).

#### 4.4.1.3. Direct Addressing

#### • C251 Architecture

In the direct addressing mode, the instruction contains the address of the data operand. The 8-bit direct mode addresses on-chip RAM (dir8 = 00:0000h-00:007Fh) as both bytes and words, and addresses the SFRs (dir8 = S:080h-S:1FFh) as bytes only. The 16-bit direct mode addresses both bytes and words in memory (dir16 = 00:0000h-00:FFFFh).

C51 Architecture

The 8-bit direct mode addresses 256 bytes of on-chip RAM (dir8 = 00h-7Fh) as bytes only and the SFRs (dir8 = 80h-FFh) as bytes only.

| Mode      | Address Range of<br>Operand | Assembly<br>Language<br>Reference | Comments                                                                    |

|-----------|-----------------------------|-----------------------------------|-----------------------------------------------------------------------------|

| Register  | 00h-1Fh                     | R0-R7 (Bank<br>selected by PSW)   |                                                                             |