# SH7201<sub>Group</sub>

Hardware Manual

Renesas 32-Bit RISC Microcomputer SuperH<sup>TM</sup> RISC engine Family / SH7200 Series R5S72011

Jardware Manua

Rev.2.00 Revision Date: Sep. 07, 2007

RenesasTechnology www.renesas.com

#### Notes regarding these materials

- This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document.

- 2. Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

- 3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

- 4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas products listed in this document, please confirm the latest product information with a Renesas sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas such as that disclosed through our website. (http://www.renesas.com)

- 5. Renesas has used reasonable care in compiling the information included in this document, but Renesas assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document.

- 6. When using or otherwise relying on the information in this document, you should evaluate the information in light of the total system before deciding about the applicability of such information to the intended application. Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Renesas products.

- 7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which require especially high quality and reliability such as safety systems, or equipment or systems for transportation and traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication transmission. If you are considering the use of our products for such purposes, please contact a Renesas sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

- 8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below:

- (1) artificial life support devices or systems

- (2) surgical implantations

- (3) healthcare intervention (e.g., excision, administration of medication, etc.)

- (4) any other purposes that pose a direct threat to human life

- Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers who elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas Technology Corp., its affiliated companies and their officers, directors, and employees against any and all damages arising out of such applications.

- 9. You should use the products described herein within the range specified by Renesas, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or damages arising out of the use of Renesas products beyond such specified ranges.

- 10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 11. In case Renesas products listed in this document are detached from the products to which the Renesas products are attached or affixed, the risk of accident such as swallowing by infants and small children is very high. You should implement safety measures so that Renesas products may not be easily detached from your products. Renesas shall have no liability for damages arising out of such detachment.

- 12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written approval from Renesas.

- 13. Please contact a Renesas sales office if you have any questions regarding the information contained in this document, Renesas semiconductor products, or if you have any other inquiries.

### **General Precautions on Handling of Product**

#### 1. Treatment of NC Pins

Note: Do not connect anything to the NC pins.

The NC (not connected) pins are either not connected to any of the internal circuitry or are used as test pins or to reduce noise. If something is connected to the NC pins, the operation of the LSI is not guaranteed.

#### 2. Treatment of Unused Input Pins

Note: Fix all unused input pins to high or low level.

Generally, the input pins of CMOS products are high-impedance input pins. If unused pins are in their open states, intermediate levels are induced by noise in the vicinity, a pass-through current flows internally, and a malfunction may occur.

3. Processing before Initialization

Note: When power is first supplied, the product's state is undefined.

The states of internal circuits are undefined until full power is supplied throughout the chip and a low level is input on the reset pin. During the period where the states are undefined, the register settings and the output state of each pin are also undefined. Design your system so that it does not malfunction because of processing while it is in this undefined state. For those products that have a reset function, reset the LSI immediately after the power supply has been turned on.

4. Processing when the Power Supply Voltage is beyond the Operating Voltage Specification\* When the power supply voltage exceeds the operating voltage specification, erroneous operation may occur. To prevent this, design your system so that it does not malfunction. For example, the system should be reset after the power supply voltage is changed to a value within the operating voltage specification.

Note: \* The voltage must be within the range up to the absolute maximum rating. The LSI may be permanently damaged if the absolute maximum rating is exceeded.

5. Prohibition of Access to Undefined or Reserved Addresses

Note: Access to undefined or reserved addresses is prohibited.

The undefined or reserved addresses may be used to expand functions, or test registers may have been be allocated to these addresses. Do not access these registers; the system's operation is not guaranteed if they are accessed.

6. Reading from/Writing to Reserved Bit of Each Register

Treat the reserved bit of a register used in each module as follows except in cases where the specifications for values which are read from or written to the bit are provided in the description.

The bit is always read as 0. The write value should be 0 or one, which has been read immediately before writing.

Writing the value, which has been read immediately before writing, has the advantage of preventing the bit from being affected on its extended function when the function is assigned.

# Configuration of This Manual

This manual comprises the following items:

- 1. General Precautions on Handling of Product

- 2. Configuration of This Manual

- 3. Preface

- 4. Contents

- 5. Overview

- 6. Description of Functional Modules

- CPU and System-Control Modules

- On-Chip Peripheral Modules

The configuration of the functional description of each module differs according to the module. However, the generic style includes the following items:

- i) Feature

- ii) Input/Output Pin

- iii) Register Description

- iv) Operation

- v) Usage Note

When designing an application system that includes this LSI, take notes into account. Each section includes notes in relation to the descriptions given, and usage notes are given, as required, as the final part of each section.

- 7. List of Registers

- 8. Electrical Characteristics

- 9. Appendix

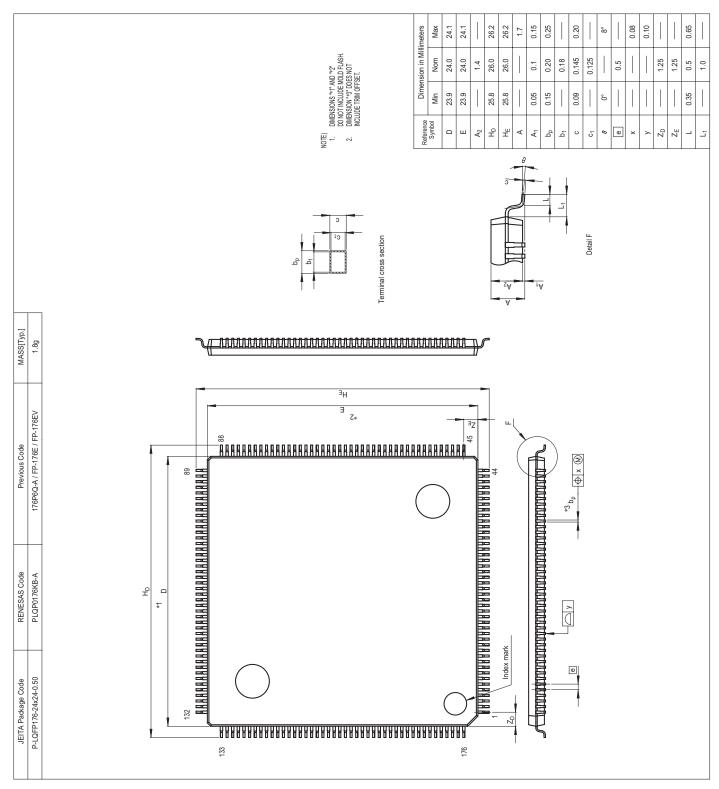

- Product Type, Package Dimensions, etc.

- 10. Main Revisions and Additions in this Edition (only for revised versions)

The list of revisions is a summary of points that have been revised or added to earlier versions. This does not include all of the revised contents. For details, see the actual locations in this manual.

11. Index

## **Preface**

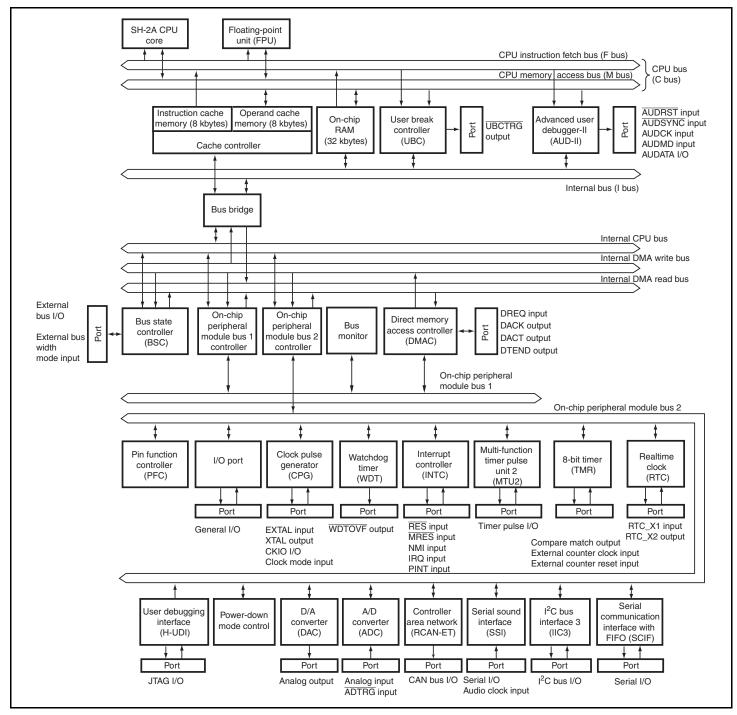

This LSI is an RISC (Reduced Instruction Set Computer) microcomputer that includes a Renesas Technology-original RISC CPU as its core, and the peripheral functions required to configure a system.

Target Users: This manual was written for users who will be using this LSI in the design of application systems. Target users are expected to understand the fundamentals of electrical circuits, logical circuits, and microcomputers.

Objective: This manual was written to explain the hardware functions and electrical characteristics of this LSI to the target users.

#### Notes on reading this manual:

- In order to understand the overall functions of the chip

Read the manual according to the contents. This manual can be roughly categorized into parts

on the CPU, system control functions, peripheral functions and electrical characteristics.

- In order to understand the details of the CPU's functions Read the SH-2A, SH2A-FPU Software Manual.

- In order to understand the details of a register when its name is known

Read the index that is the final part of the manual to find the page number of the entry on the register. The addresses, bits, and initial values of the registers are summarized in section 28, List of Registers.

#### Description of Numbers and Symbols

Aspects of the notations for register names, bit names, numbers, and symbolic names in this manual are explained below.

#### (1) Overall notation

In descriptions involving the names of bits and bit fields within this manual, the modules and registers to which the bits belong may be clarified by giving the names in the forms "module name". "register name". "bit name" or "register name". "bit name".

#### (2) Register notation

The style "register name"\_"instance number" is used in cases where there is more than one instance of the same function or similar functions.

[Example] CMCSR\_0: Indicates the CMCSR register for the compare-match timer of channel 0.

#### (3) Number notation

Binary numbers are given as B'nnnn (B' may be omitted if the number is obviously binary), hexadecimal numbers are given as H'nnnn or 0xnnnn, and decimal numbers are given as nnnn.

[Examples] Binary: B'11 or 11

Hexadecimal: H'EFA0 or 0xEFA0

Decimal: 1234

#### (4) Notation for active-low

An overbar on the name indicates that a signal or pin is active-low. [Example] WDTOVF

Note: The bit names and sentences in the above figure are examples and do not refer to specific data in this manual.

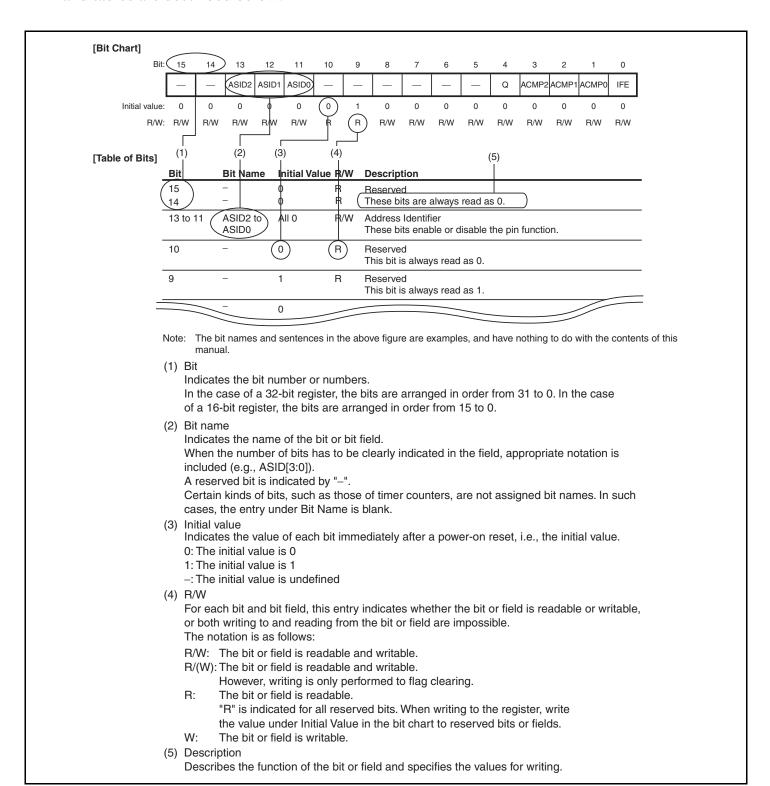

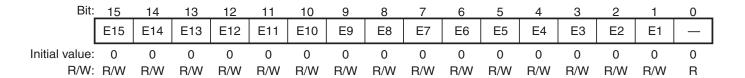

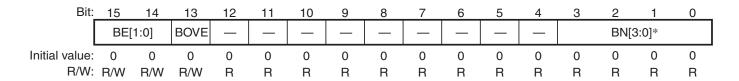

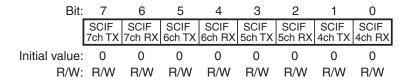

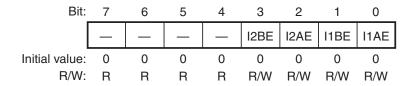

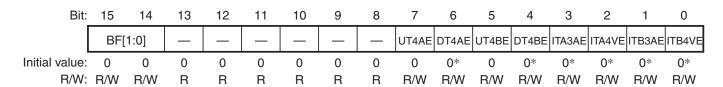

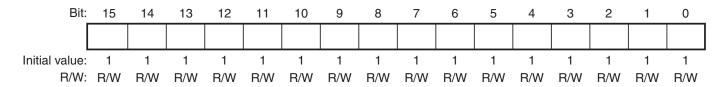

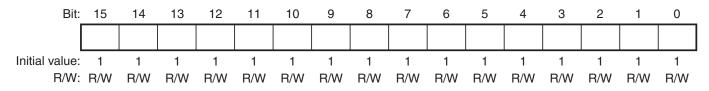

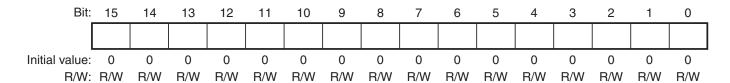

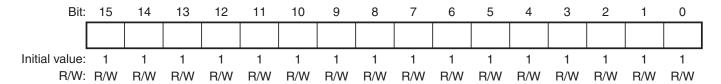

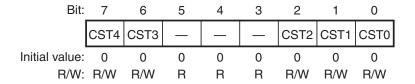

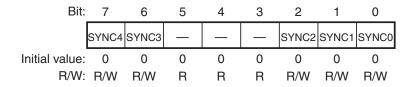

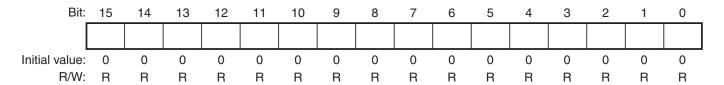

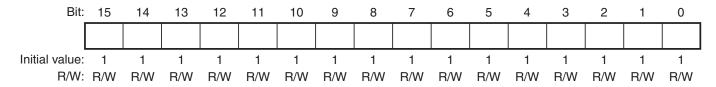

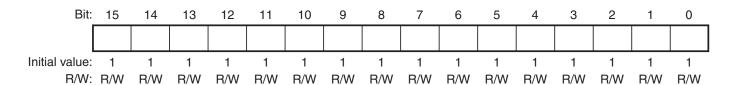

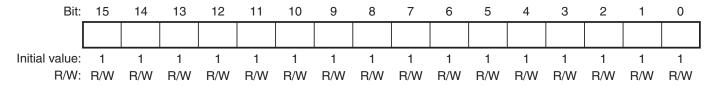

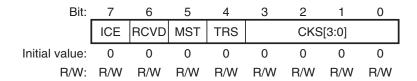

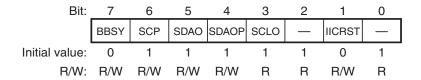

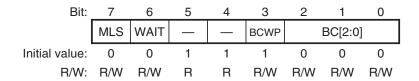

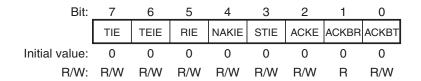

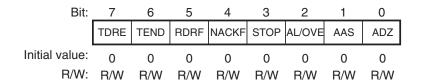

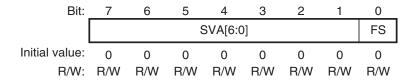

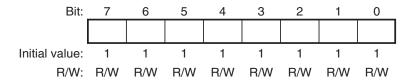

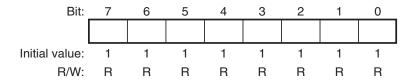

#### Description of Registers

Each register description includes a bit chart, illustrating the arrangement of bits, and a table of bits, describing the meanings of the bit settings. The standard format and notation for bit charts and tables are described below.

All trademarks and registered trademarks are the property of their respective owners.

# Contents

| Section | on 1    | Overview                              | 1  |

|---------|---------|---------------------------------------|----|

| 1.1     | SH720   | 1 Group Features                      | 1  |

| 1.2     | Produc  | t Lineup                              | 8  |

|         |         | Diagram                               |    |

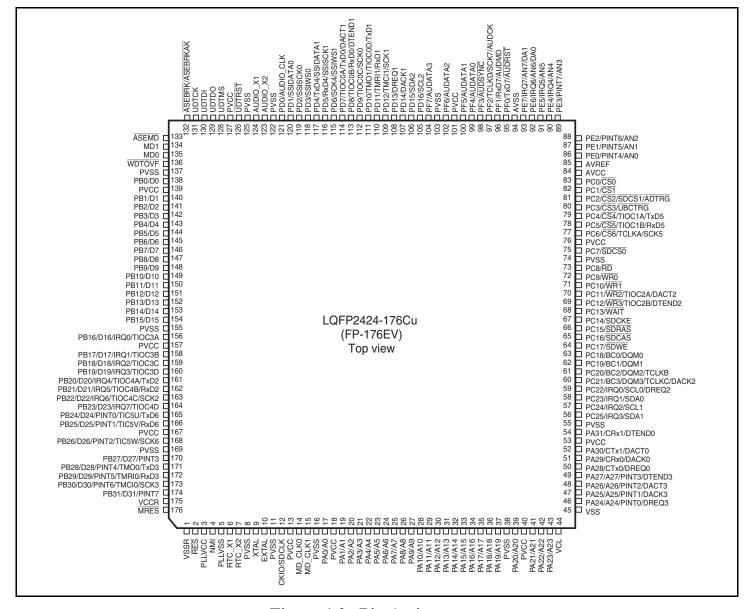

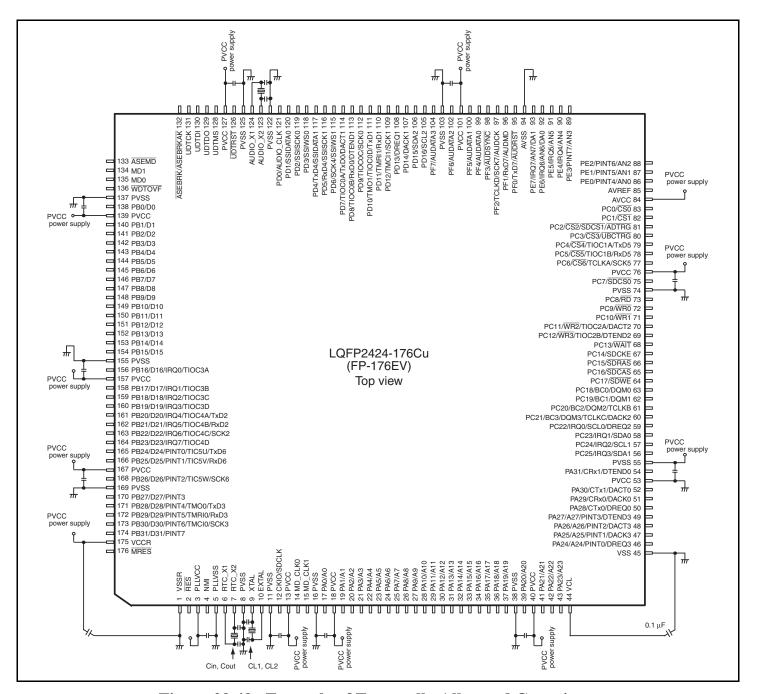

| 1.4     | Pin Ass | signments                             | 10 |

|         |         | nctions                               |    |

|         |         |                                       |    |

|         |         | CPU                                   |    |

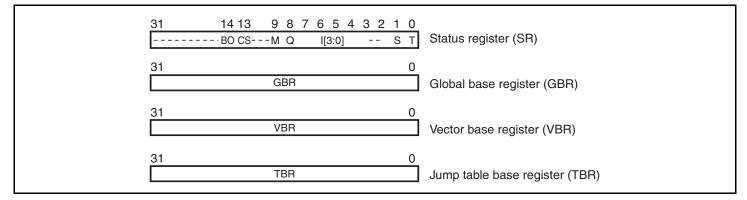

| 2.1     | Registe | er Configuration                      |    |

|         | 2.1.1   | General Registers                     |    |

|         | 2.1.2   | Control Registers                     | 20 |

|         | 2.1.3   | System Registers                      | 22 |

|         | 2.1.4   | Register Banks                        | 23 |

|         | 2.1.5   | Initial Values of Registers           | 23 |

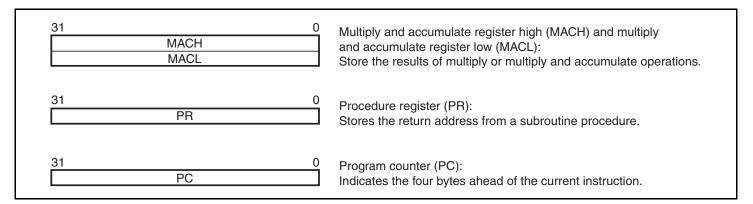

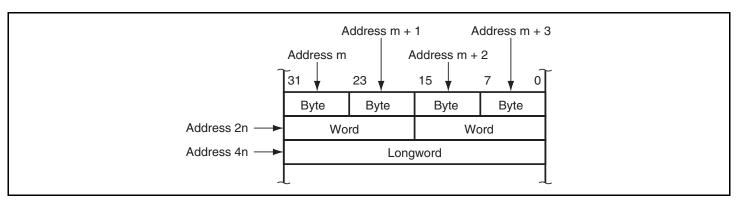

| 2.2     | Data Fo | ormats                                | 24 |

|         | 2.2.1   | Data Format in Registers              | 24 |

|         | 2.2.2   | Data Formats in Memory                | 24 |

|         | 2.2.3   | Immediate Data Format                 | 25 |

| 2.3     | Instruc | tion Features                         | 26 |

|         | 2.3.1   | RISC-Type Instruction Set             | 26 |

|         | 2.3.2   | Addressing Modes                      |    |

|         | 2.3.3   | Instruction Format                    |    |

| 2.4     | Instruc | tion Set                              |    |

|         | 2.4.1   | Instruction Set by Classification     | 38 |

|         | 2.4.2   | Data Transfer Instructions            |    |

|         | 2.4.3   | Arithmetic Operation Instructions     | 48 |

|         | 2.4.4   | Logic Operation Instructions          |    |

|         | 2.4.5   | Shift Instructions                    |    |

|         | 2.4.6   | Branch Instructions                   |    |

|         | 2.4.7   | System Control Instructions           |    |

|         | 2.4.8   | Floating Point Operation Instructions |    |

|         | 2.4.9   | FPU-Related CPU Instructions          |    |

|         | 2.4.10  | Bit Manipulation Instructions         |    |

|         |         | sing States                           |    |

|         |         | $\sigma$                              |    |

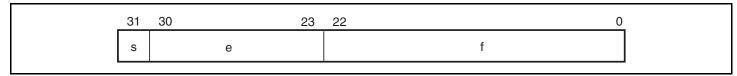

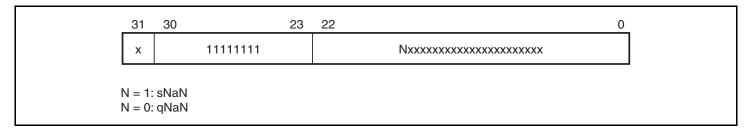

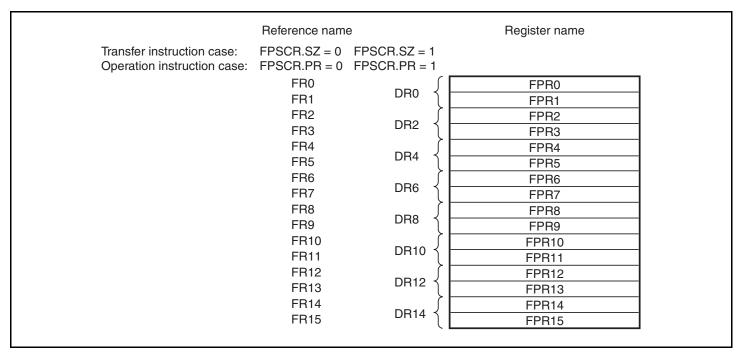

| Sec          | tion 3 | Floating-Point Unit (FPU)                      | 63 |

|--------------|--------|------------------------------------------------|----|

| 3.1          |        | res                                            |    |

| 3.2          | Data I | Formats                                        | 63 |

|              | 3.2.1  | Floating-Point Format                          | 63 |

|              | 3.2.2  | Non-Numbers (NaN)                              | 65 |

|              | 3.2.3  | Denormalized Numbers                           | 66 |

| 3.3          | Regist | ter Descriptions                               | 67 |

|              | 3.3.1  | Floating-Point Registers                       | 67 |

|              | 3.3.2  | Floating-Point Status/Control Register (FPSCR) | 68 |

|              | 3.3.3  | Floating-Point Communication Register (FPUL)   | 69 |

| 3.4          | Round  | ding                                           | 70 |

| 3.5          | Floati | ng-Point Exceptions                            | 71 |

|              | 3.5.1  | FPU Exception Sources                          | 71 |

|              | 3.5.2  | FPU Exception Handling                         | 71 |

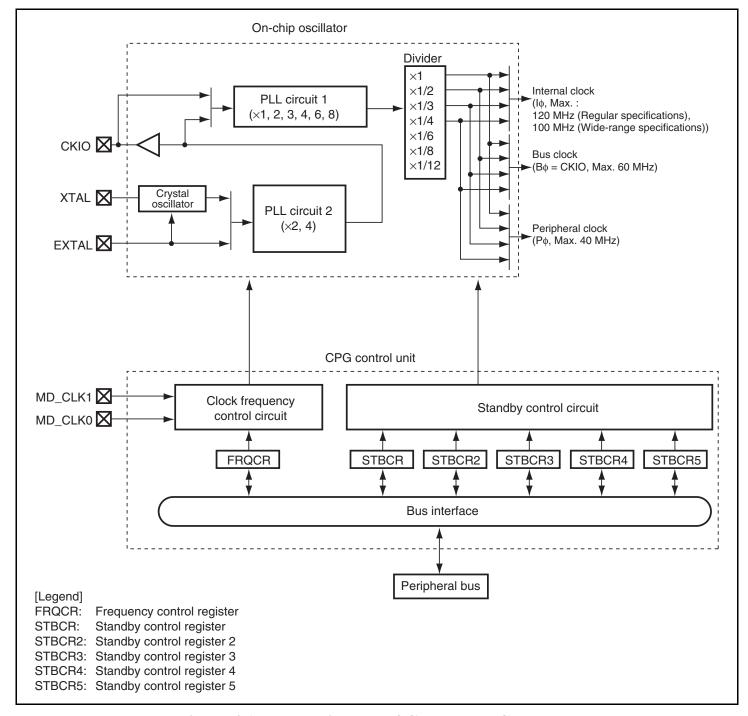

| Sec          | tion 4 | Clock Pulse Generator (CPG)                    | 73 |

| 4.1          |        | res                                            |    |

| 4.2          |        | Output Pins                                    |    |

| 4.3          |        | Operating Modes                                |    |

| 4.4          |        | ter Descriptions                               |    |

|              | 4.4.1  | Frequency Control Register (FRQCR)             |    |

|              | 4.4.2  | CKIO Control Register (CKIOCR)                 |    |

| 4.5          | Chang  | ging the Frequency                             |    |

|              | 4.5.1  | Changing the Multiplication Rate               |    |

|              | 4.5.2  | Changing the Division Ratio                    |    |

| 4.6          | Notes  | on Board Design                                |    |

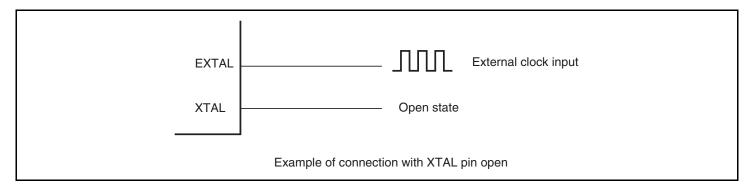

|              | 4.6.1  | Note on Inputting External Clock               |    |

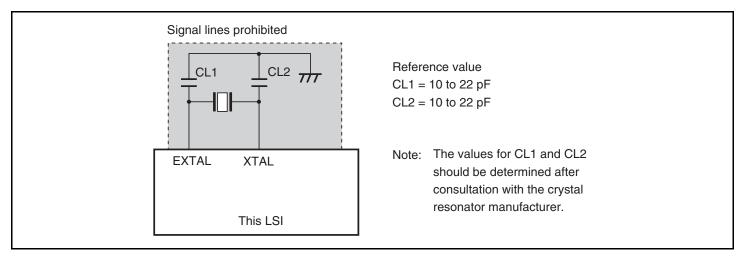

|              | 4.6.2  | Note on Using Crystal Resonator                |    |

|              | 4.6.3  | Note on Resonator                              |    |

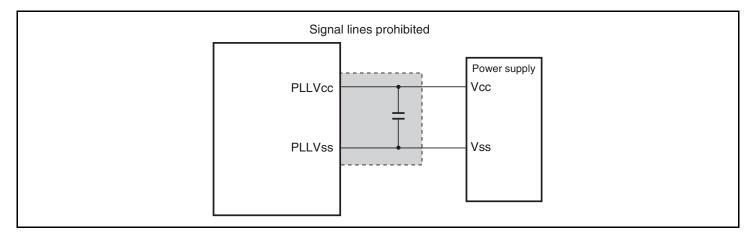

|              | 4.6.4  | Note on Using a PLL Oscillation Circuit        |    |

|              | 4.6.5  | Note on Changing the Multiplication Rate       |    |

| Sect         | tion 5 | Exception Handling                             | 91 |

| 5.1          |        | view                                           |    |

|              | 5.1.1  | Types of Exception Handling and Priority       |    |

|              | 5.1.2  | Exception Handling Operations                  |    |

|              | 5.1.2  | Exception Handling Vector Table                |    |

| 5.2          |        | S                                              |    |

| - · <b>-</b> |        | Input/Output Pins                              |    |

|       | 5.2.2   | Types of Reset                                                               | 97   |

|-------|---------|------------------------------------------------------------------------------|------|

|       | 5.2.3   | Power-On Reset                                                               | 98   |

|       | 5.2.4   | Manual Reset                                                                 | 100  |

| 5.3   | Addres  | s Errors                                                                     | 101  |

|       | 5.3.1   | Address Error Sources                                                        | 101  |

|       | 5.3.2   | Address Error Exception Handling                                             | 102  |

| 5.4   | Bus Er  | ror                                                                          | 102  |

|       | 5.4.1   | Bus Error Generation Source                                                  | 102  |

|       | 5.4.2   | Bus Error Exception Handling                                                 | 102  |

| 5.5   | Registe | er Bank Errors                                                               | 103  |

|       | 5.5.1   | Register Bank Error Sources                                                  | 103  |

|       | 5.5.2   | Register Bank Error Exception Handling                                       | 103  |

| 5.6   | Interru | pts                                                                          | 104  |

|       | 5.6.1   | Interrupt Sources                                                            | 104  |

|       | 5.6.2   | Interrupt Priority Level                                                     | 105  |

|       | 5.6.3   | Interrupt Exception Handling                                                 | 106  |

| 5.7   | Except  | ions Triggered by Instructions                                               | 107  |

|       | 5.7.1   | Types of Exceptions Triggered by Instructions                                | 107  |

|       | 5.7.2   | Trap Instructions                                                            | 108  |

|       | 5.7.3   | Slot Illegal Instructions                                                    | 108  |

|       | 5.7.4   | General Illegal Instructions.                                                | 108  |

|       | 5.7.5   | Integer Division Instructions                                                | 109  |

|       | 5.7.6   | Floating-point Operation Instruction                                         | 109  |

| 5.8   | When I  | Exception Sources Are Not Accepted                                           | 110  |

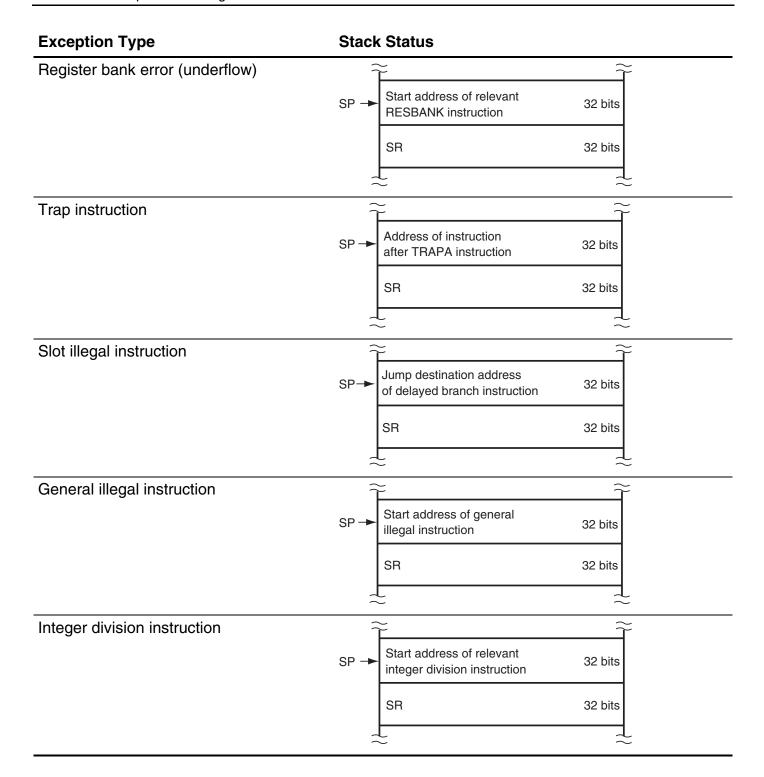

| 5.9   | Stack S | Status after Exception Handling Ends                                         | 111  |

| 5.10  | _       | Notes                                                                        |      |

|       | 5.10.1  | Value of Stack Pointer (SP)                                                  | 113  |

|       | 5.10.2  | Value of Vector Base Register (VBR)                                          | 113  |

|       | 5.10.3  | Address Errors Caused by Stacking of Address Error Exception Handling        | 113  |

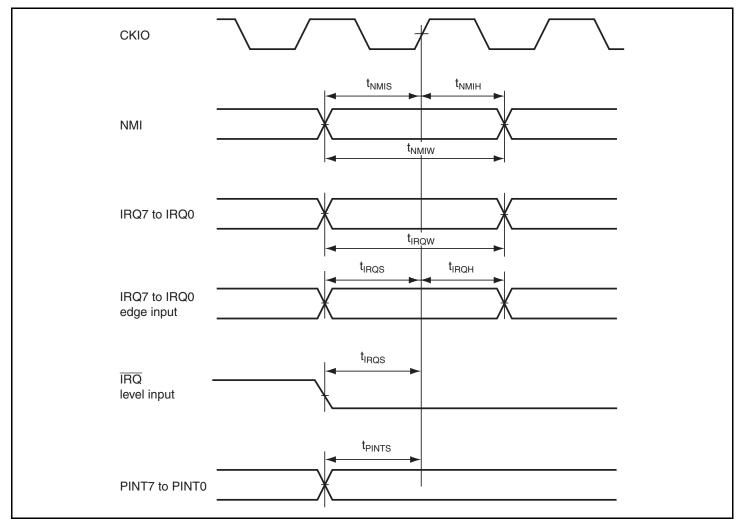

| Secti | ion 6   | Interrupt Controller (INTC)                                                  | .115 |

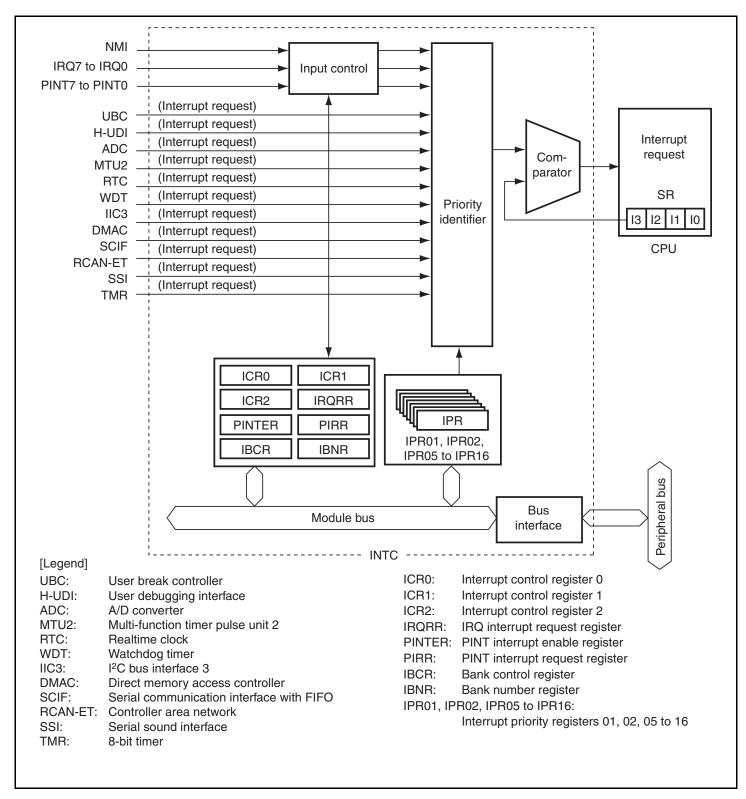

| 6.1   | Feature | es                                                                           | 115  |

| 6.2   | Input/C | Output Pins                                                                  | 117  |

| 6.3   | Registe | er Descriptions                                                              | 117  |

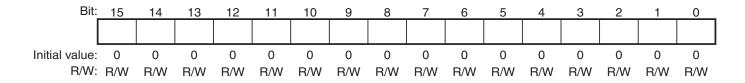

|       | 6.3.1   | Interrupt Priority Registers 01, 02, 05 to 16 (IPR01, IPR02, IPR05 to IPR16) | 119  |

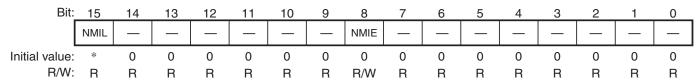

|       | 6.3.2   | Interrupt Control Register 0 (ICR0)                                          | 121  |

|       | 6.3.3   | Interrupt Control Register 1 (ICR1)                                          | 122  |

|       | 6.3.4   | Interrupt Control Register 2 (ICR2)                                          | 123  |

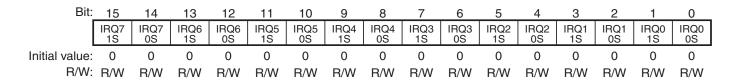

|       | 6.3.5   | IRQ Interrupt Request Register (IRQRR)                                       | 123  |

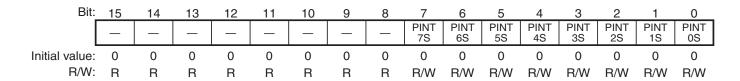

|       | 6.3.6   | PINT Interrupt Enable Register (PINTER)                                      | 125  |

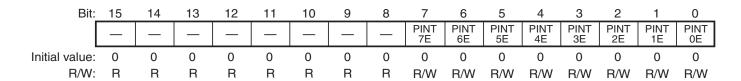

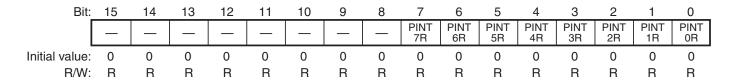

|      | 6.3.7   | PINT Interrupt Request Register (PIRR)                | 126 |

|------|---------|-------------------------------------------------------|-----|

|      | 6.3.8   | Bank Control Register (IBCR)                          | 127 |

|      | 6.3.9   | Bank Number Register (IBNR)                           | 128 |

|      | 6.3.10  | DMA Transfer Request Enable Register 0 (DREQER0)      | 129 |

|      | 6.3.11  | DMA Transfer Request Enable Register 1 (DREQER1)      | 130 |

|      | 6.3.12  | DMA Transfer Request Enable Register 2 (DREQER2)      | 131 |

|      | 6.3.13  | DMA Transfer Request Enable Register 3 (DREQER3)      | 132 |

| 6.4  | Interru | pt Sources                                            | 133 |

|      | 6.4.1   | NMI Interrupt                                         | 133 |

|      | 6.4.2   | User Break Interrupt                                  | 133 |

|      | 6.4.3   | H-UDI Interrupt                                       | 133 |

|      | 6.4.4   | IRQ Interrupts                                        | 134 |

|      | 6.4.5   | PINT Interrupts                                       | 135 |

|      | 6.4.6   | On-Chip Peripheral Module Interrupts                  | 135 |

| 6.5  | Interru | pt Exception Handling Vector Table and Priority       | 136 |

| 6.6  | Operat  | ion                                                   | 146 |

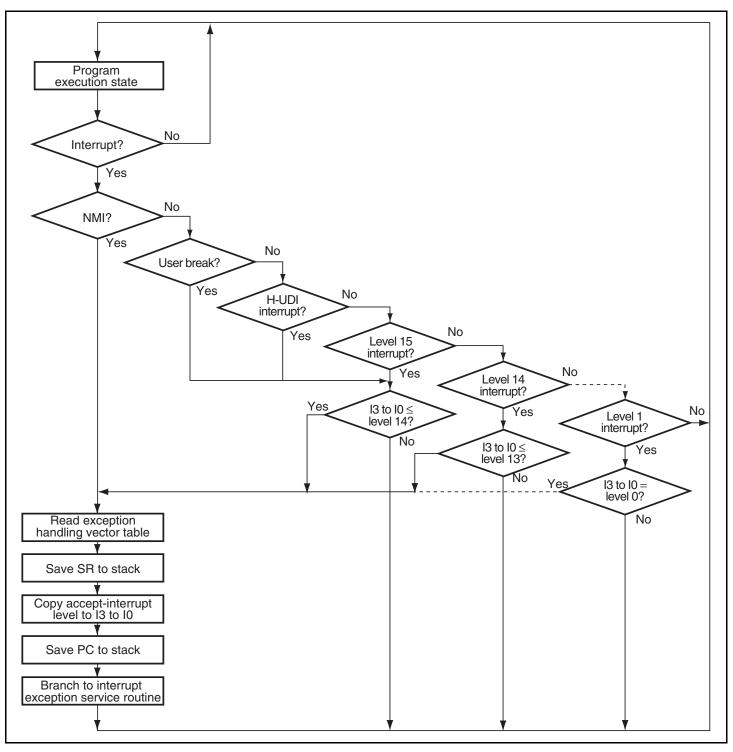

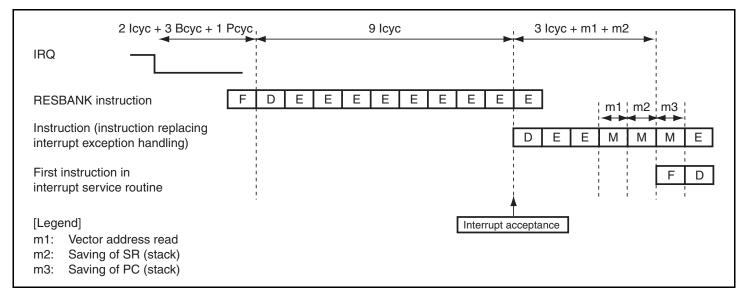

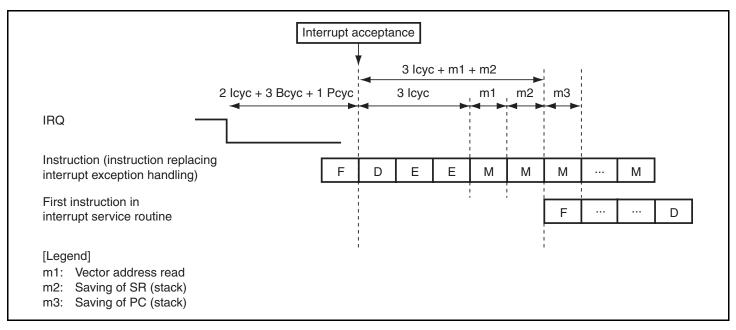

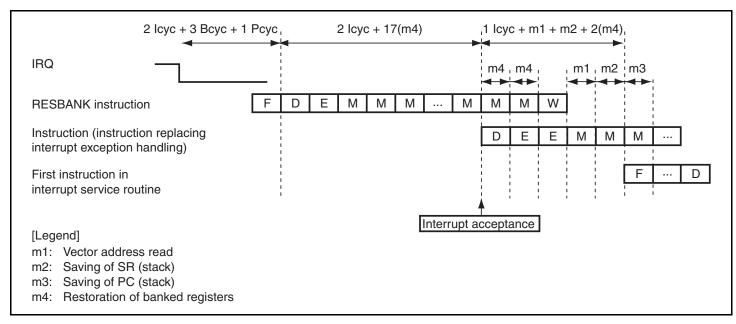

|      | 6.6.1   | Interrupt Operation Sequence                          | 146 |

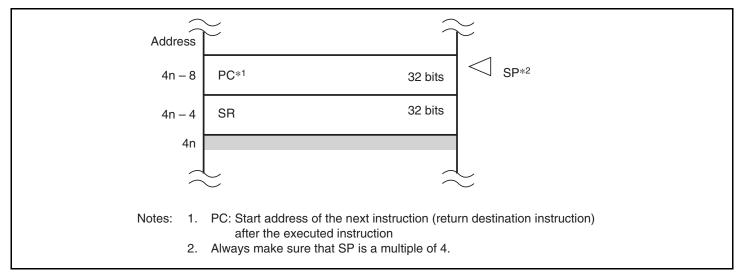

|      | 6.6.2   | Stack after Interrupt Exception Handling              | 148 |

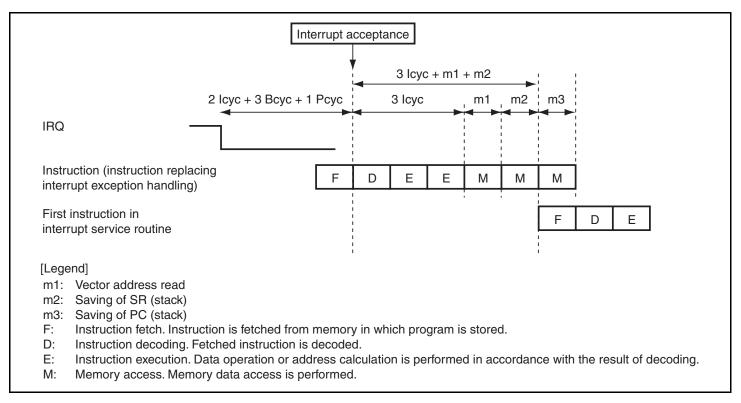

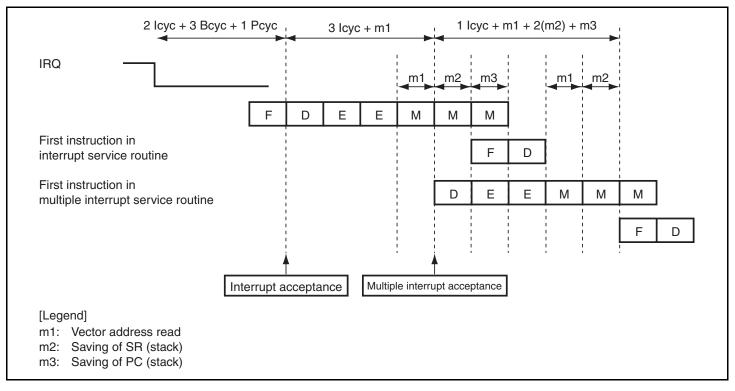

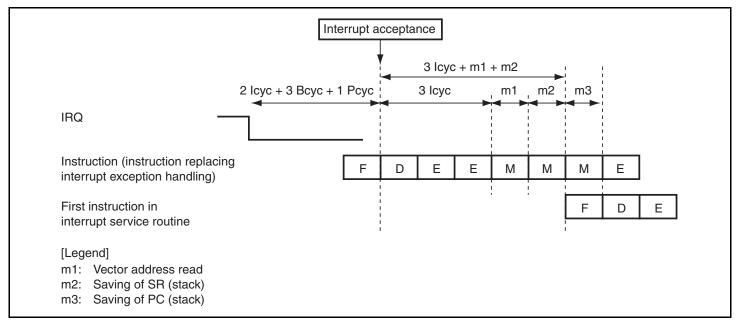

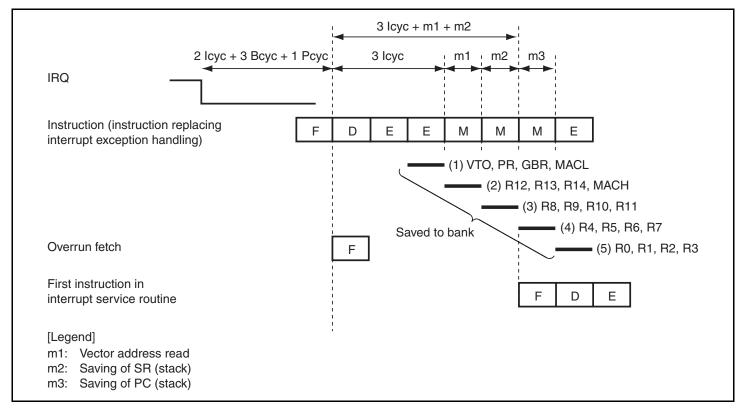

| 6.7  | Interru | pt Response Time                                      | 149 |

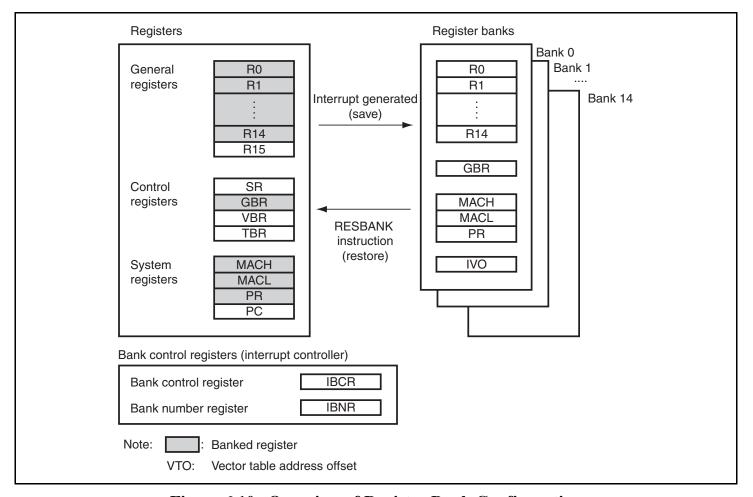

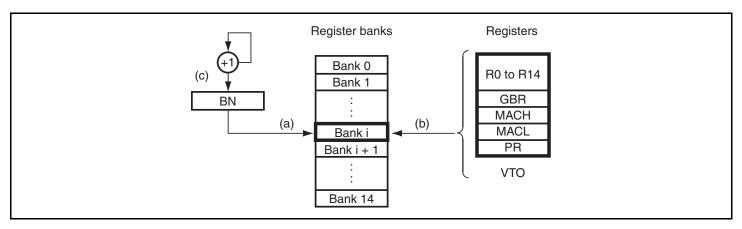

| 6.8  | Registe | er Banks                                              | 154 |

|      | 6.8.1   | Register Banks and Bank Control Registers             | 155 |

|      | 6.8.2   | Bank Save and Restore Operations                      | 155 |

|      | 6.8.3   | Save and Restore Operations after Saving to All Banks | 157 |

|      | 6.8.4   | Register Bank Exception                               | 158 |

|      | 6.8.5   | Register Bank Error Exception Handling                | 158 |

| 6.9  | Data T  | ransfer with Interrupt Request Signals                | 159 |

|      | 6.9.1   | Handling Interrupt Request Signals as Sources for     |     |

|      |         | CPU Interrupt but not DMAC Activation                 | 159 |

|      | 6.9.2   | Handling Interrupt Request Signals as Sources for     |     |

|      |         | DMAC Activation but not CPU Interrupt                 | 159 |

| 6.10 | Usage   | Note                                                  | 160 |

|      | 6.10.1  | Timing to Clear an Interrupt Source                   | 160 |

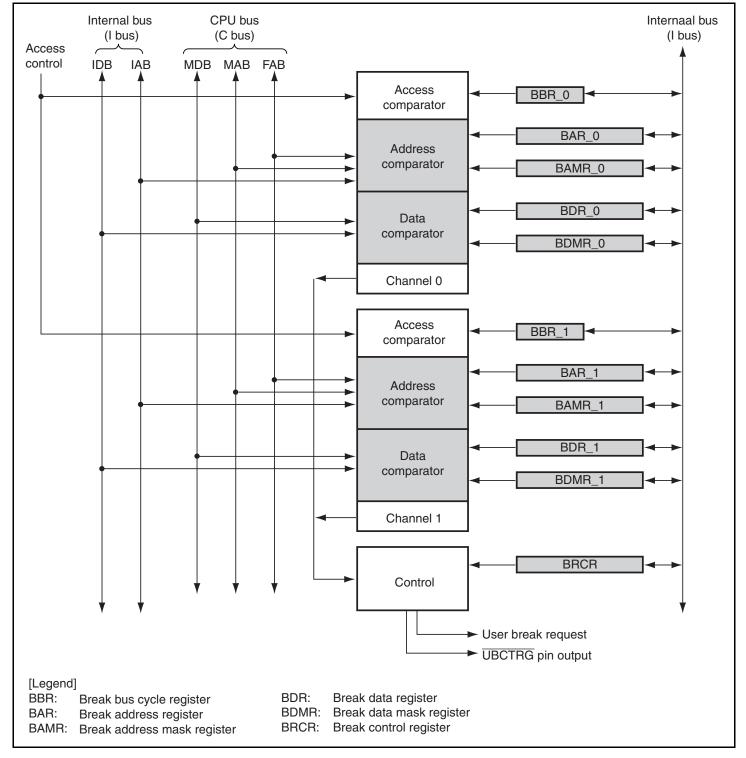

| Sect | ion 7   | User Break Controller (UBC)                           | 161 |

| 7.1  | Feature | es                                                    | 161 |

| 7.2  | Input/C | Output Pin                                            | 163 |

| 7.3  | -       | er Descriptions                                       |     |

|      | 7.3.1   | Break Address Register (BAR)                          |     |

|      | 7.3.2   | Break Address Mask Register (BAMR)                    |     |

|      | 7.3.3   | Break Data Register (BDR)                             |     |

|      | 7.3.4   | Break Data Mask Register (BDMR)                              | 167 |

|------|---------|--------------------------------------------------------------|-----|

|      | 7.3.5   | Break Bus Cycle Register (BBR)                               | 168 |

|      | 7.3.6   | Break Control Register (BRCR)                                | 170 |

| 7.4  | Operat  | ion                                                          | 173 |

|      | 7.4.1   | Flow of the User Break Operation                             | 173 |

|      | 7.4.2   | Break on Instruction Fetch Cycle                             | 174 |

|      | 7.4.3   | Break on Data Access Cycle                                   | 175 |

|      | 7.4.4   | Value of Saved Program Counter                               | 176 |

|      | 7.4.5   | Usage Examples                                               | 177 |

| 7.5  | Usage   | Notes                                                        | 180 |

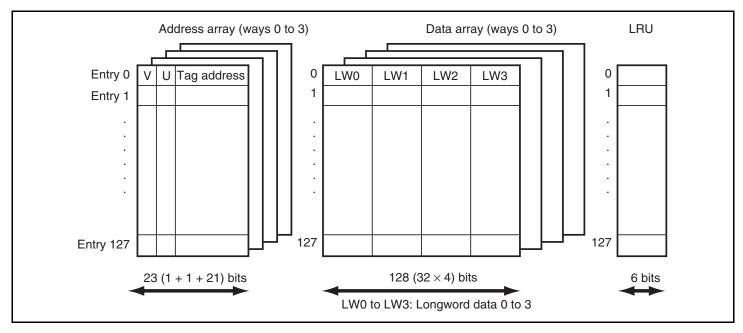

| Sect | tion 8  | Cache                                                        | 183 |

| 8.1  | Feature | es                                                           | 183 |

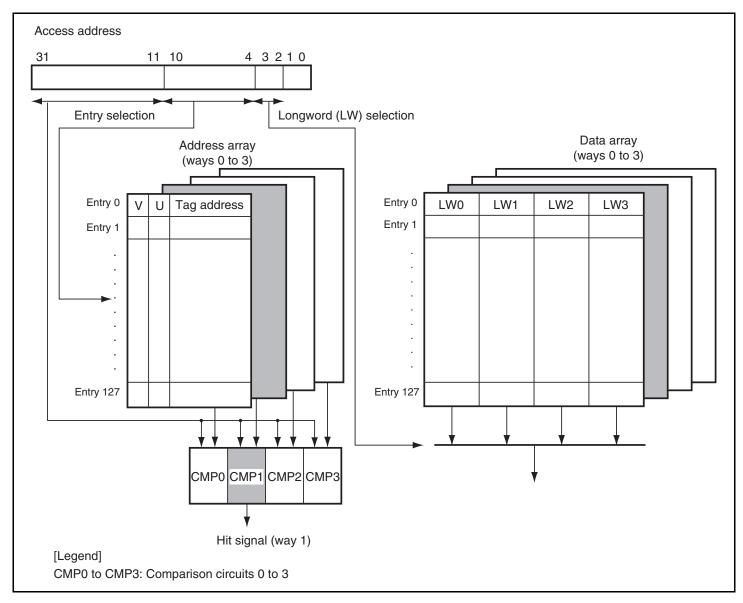

|      | 8.1.1   | Cache Structure                                              | 183 |

| 8.2  | Registe | er Descriptions                                              | 186 |

|      | 8.2.1   | Cache Control Register 1 (CCR1)                              | 186 |

|      | 8.2.2   | Cache Control Register 2 (CCR2)                              | 188 |

| 8.3  | Operat  | ion                                                          | 191 |

|      | 8.3.1   | Searching Cache                                              | 191 |

|      | 8.3.2   | Read Access                                                  | 193 |

|      | 8.3.3   | Prefetch Operation (Only for Operand Cache)                  | 193 |

|      | 8.3.4   | Write Operation (Only for Operand Cache)                     | 193 |

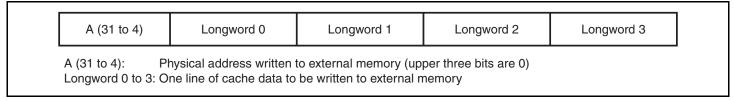

|      | 8.3.5   | Write-Back Buffer (Only for Operand Cache)                   | 194 |

|      | 8.3.6   | Coherency of Cache and External Memory                       | 196 |

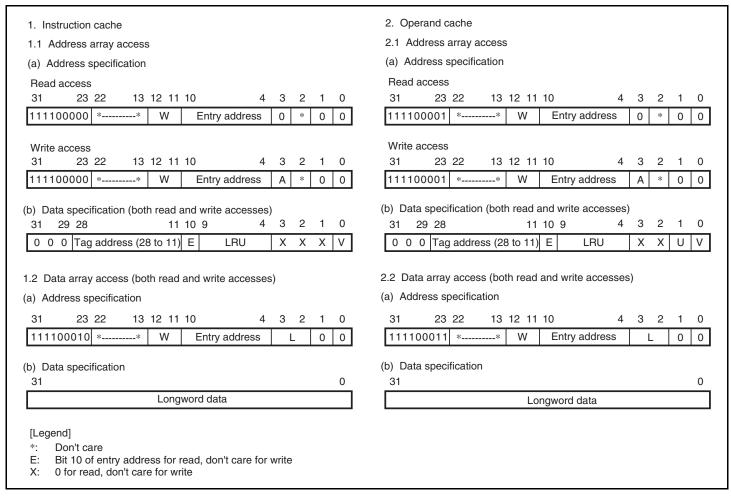

| 8.4  | Memor   | ry-Mapped Cache                                              | 196 |

|      | 8.4.1   | Address Array                                                | 196 |

|      | 8.4.2   | Data Array                                                   | 197 |

|      | 8.4.3   | Usage Examples                                               | 199 |

|      | 8.4.4   | Notes                                                        | 200 |

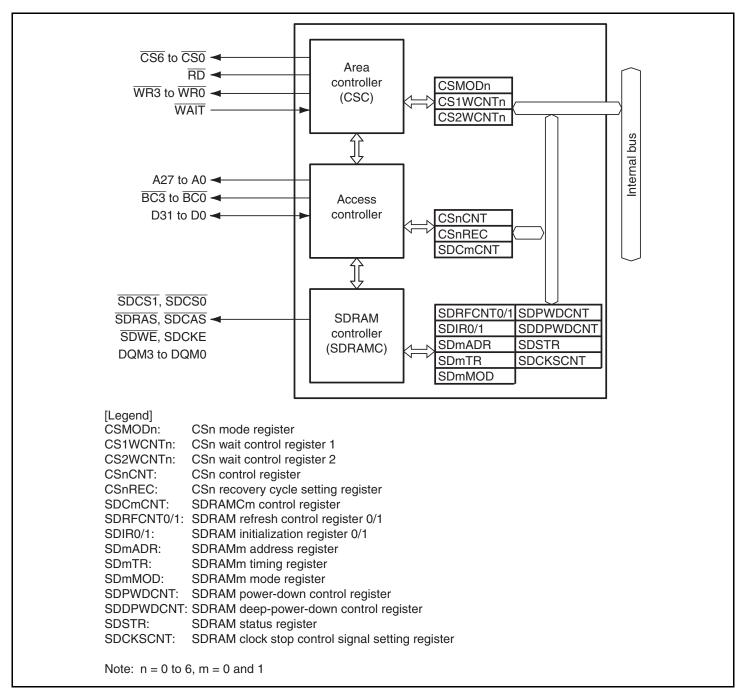

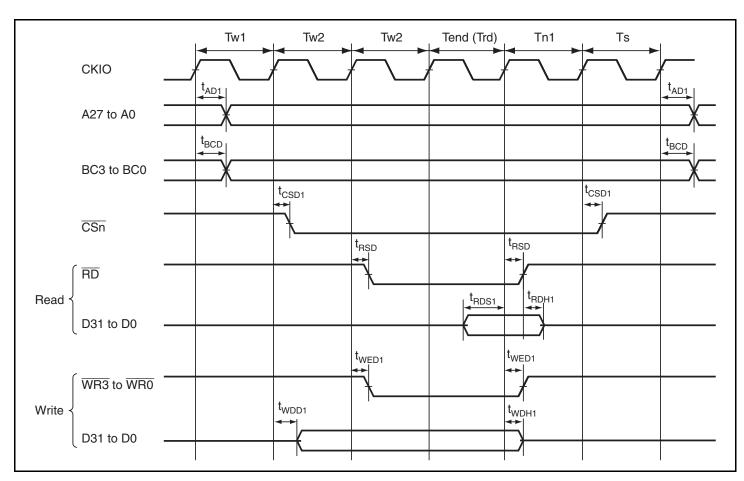

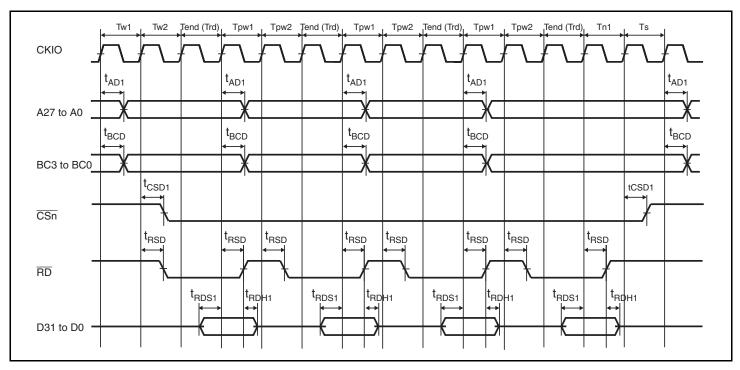

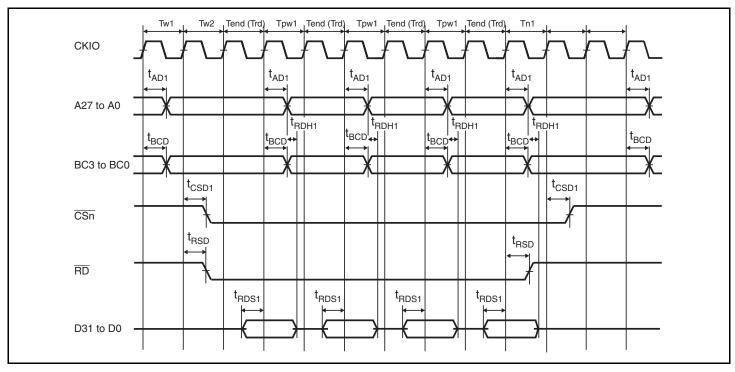

| Sect | tion 9  | Bus State Controller (BSC)                                   | 201 |

| 9.1  | Feature | es                                                           | 201 |

| 9.2  | Input/C | Output Pins                                                  | 203 |

| 9.3  | Area C  | Overview                                                     | 205 |

|      | 9.3.1   | Address Map                                                  | 205 |

|      | 9.3.2   | Data Bus Width and Pin Function Setting for Individual Areas | 206 |

| 9.4  | Registe | er Descriptions                                              | 207 |

|      | 9.4.1   | CSn Control Register (CSnCNT) (n = 0 to 6)                   | 209 |

|      | 9.4.2   | CSn Recovery Cycle Setting Register (CSnREC) (n = 0 to 6)    | 211 |

|      | 9.4.3   | SDRAMCm Control Register (SDCmCNT) (m = 0, 1)                | 213 |

|      | 9.4.4   | CSn Mode Register (CSMODn) (n = 0 to 6)                          | 214 |

|------|---------|------------------------------------------------------------------|-----|

|      | 9.4.5   | CSn Wait Control Register 1 (CS1WCNTn) (n = 0 to 6)              | 217 |

|      | 9.4.6   | CSn Wait Control Register 2 (CS2WCNTn) (n = 0 to 6)              | 219 |

|      | 9.4.7   | SDRAM Refresh Control Register 0 (SDRFCNT0)                      | 222 |

|      | 9.4.8   | SDRAM Refresh Control Register 1 (SDRFCNT1)                      | 223 |

|      | 9.4.9   | SDRAM Initialization Register 0 (SDIR0)                          | 225 |

|      | 9.4.10  | SDRAM Initialization Register 1 (SDIR1)                          | 227 |

|      | 9.4.11  | SDRAM Power-Down Control Register (SDPWDCNT)                     | 228 |

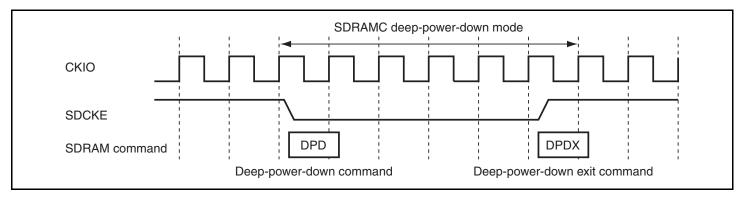

|      | 9.4.12  | SDRAM Deep-Power-Down Control Register (SDDPWDCNT)               | 229 |

|      | 9.4.13  | SDRAMm Address Register (SDmADR) (m = 0, 1)                      | 230 |

|      | 9.4.14  | SDRAMm Timing Register (SDmTR) (m = 0, 1)                        | 231 |

|      | 9.4.15  | SDRAMm Mode Register (SDmMOD) (m = 0, 1)                         | 233 |

|      | 9.4.16  | SDRAM Status Register (SDSTR)                                    | 234 |

|      | 9.4.17  | SDRAM Clock Stop Control Signal Setting Register (SDCKSCNT)      | 236 |

|      | 9.4.18  | AC Characteristics Switching Register (ACSWR)                    |     |

| 9.5  | Operat  | ion                                                              | 238 |

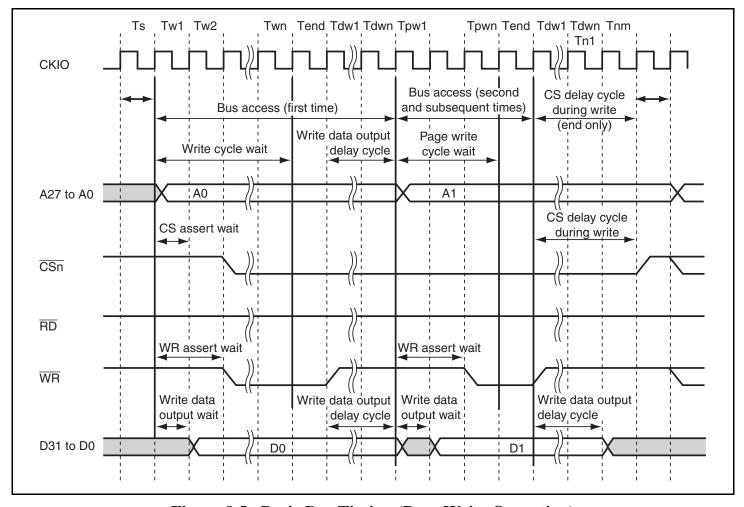

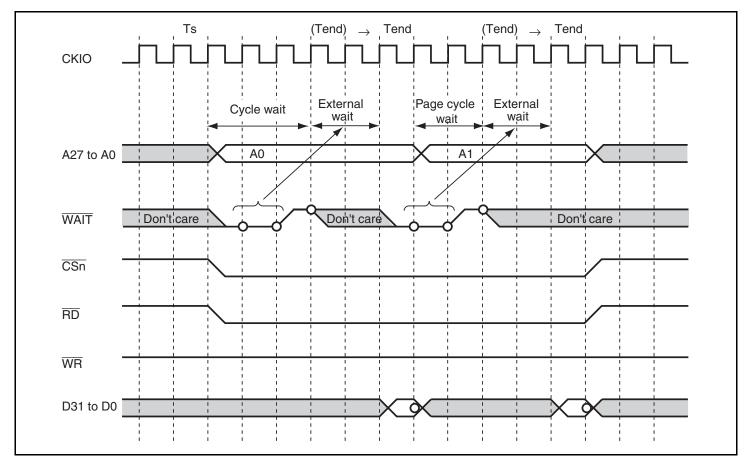

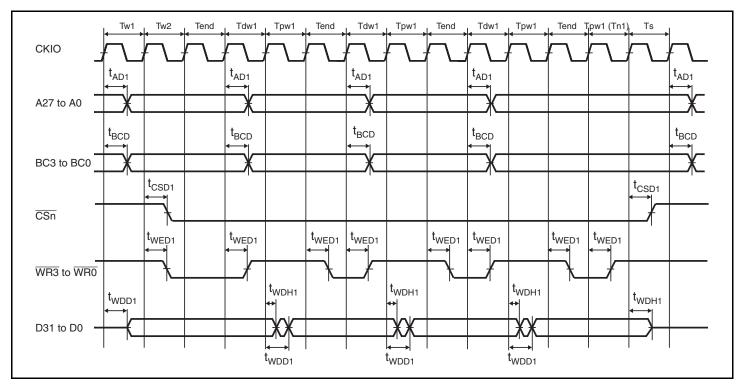

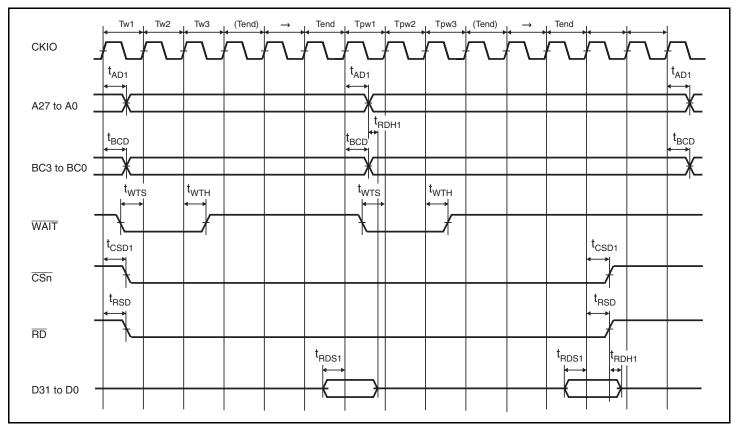

|      | 9.5.1   | CSC Interface                                                    | 238 |

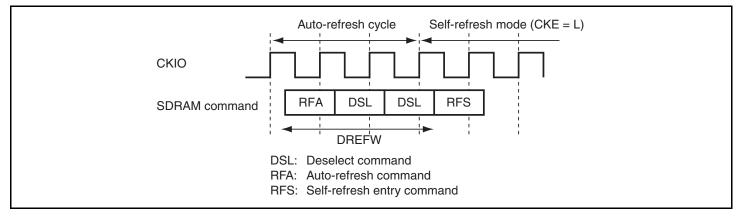

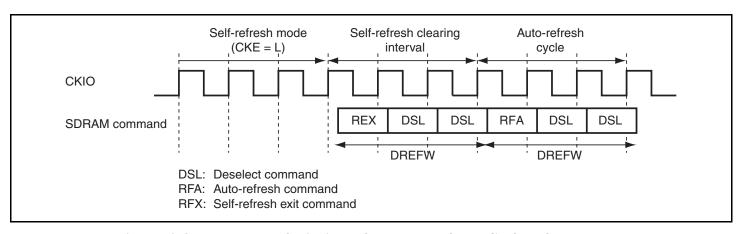

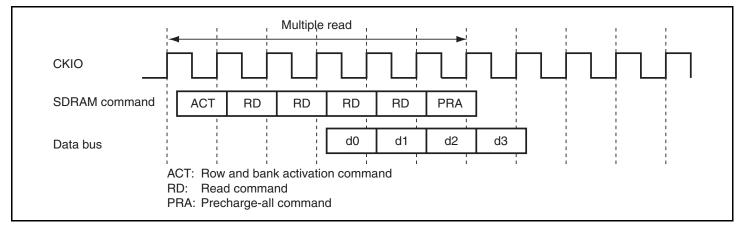

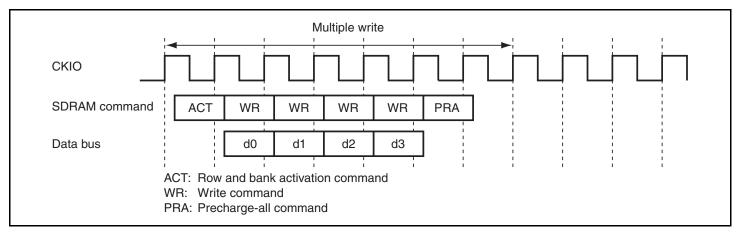

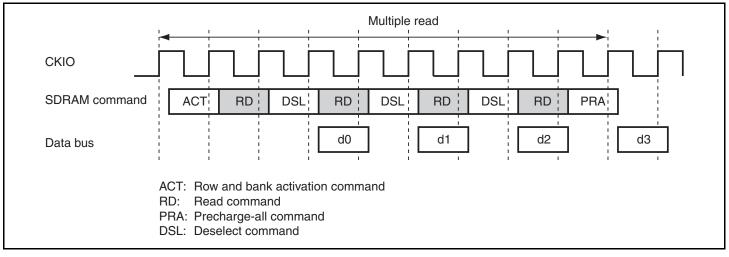

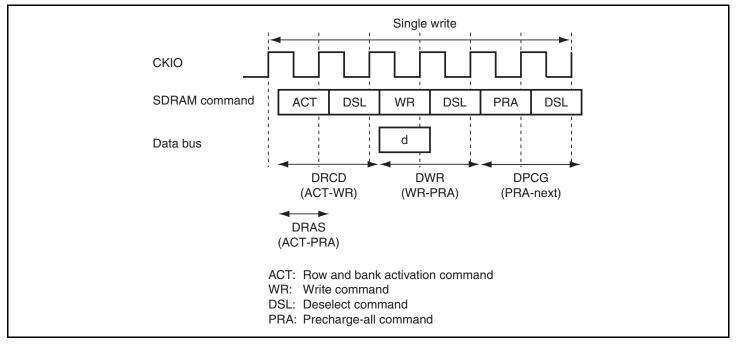

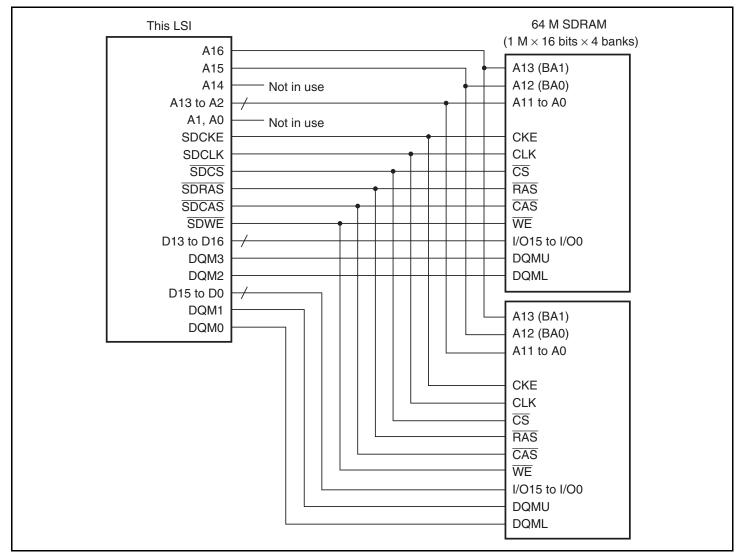

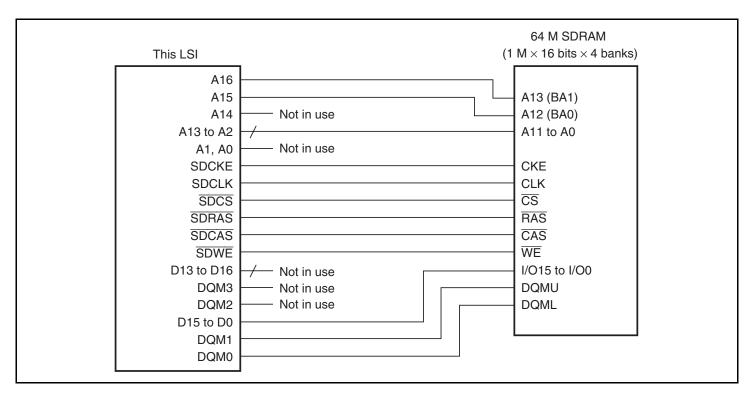

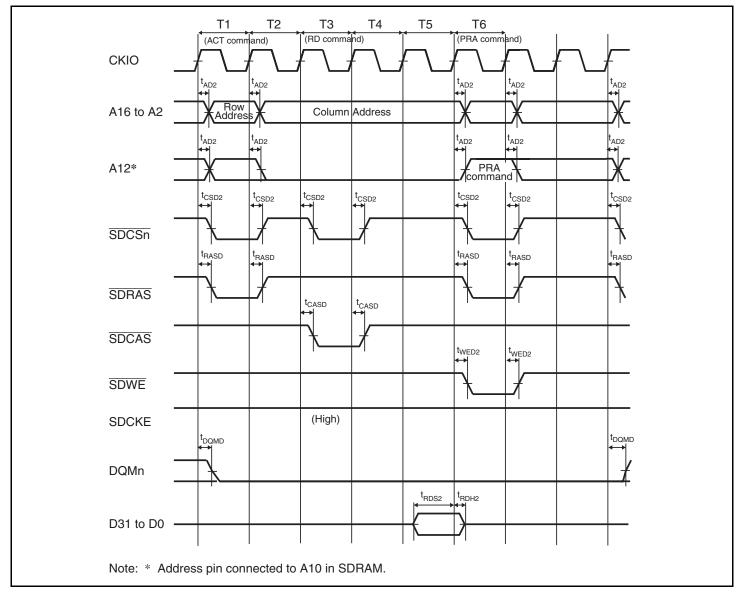

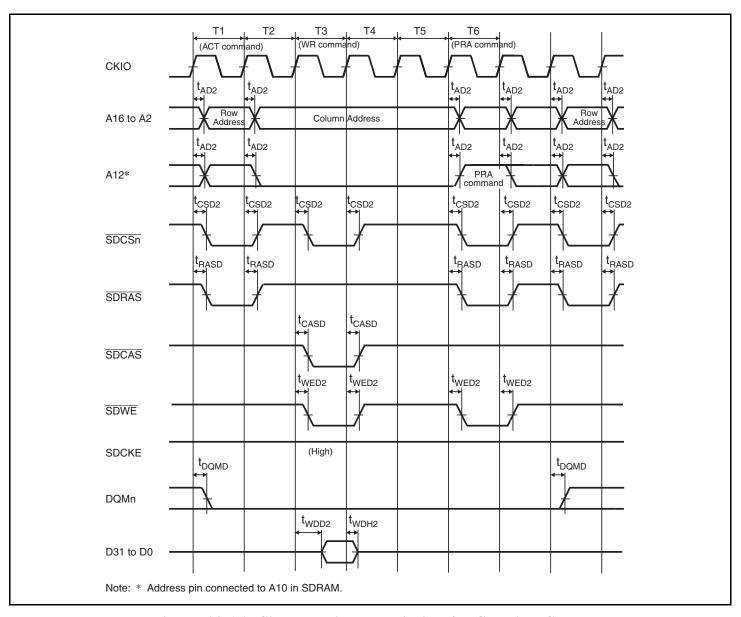

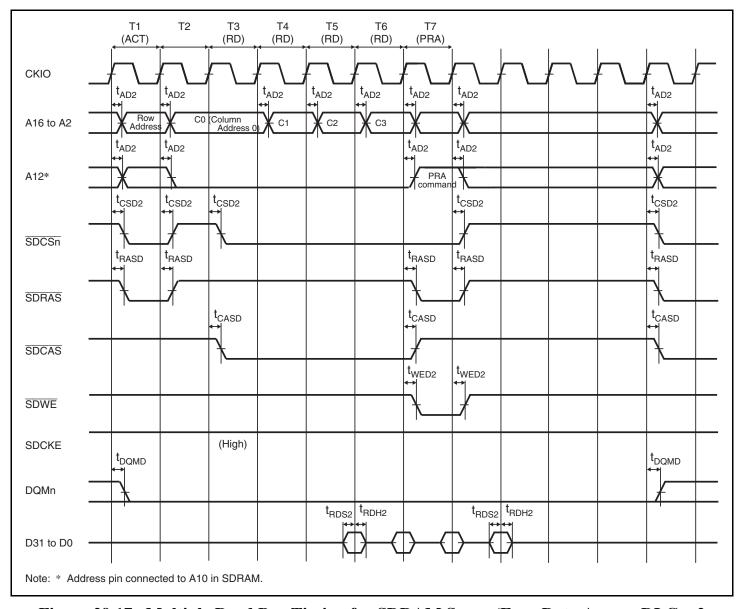

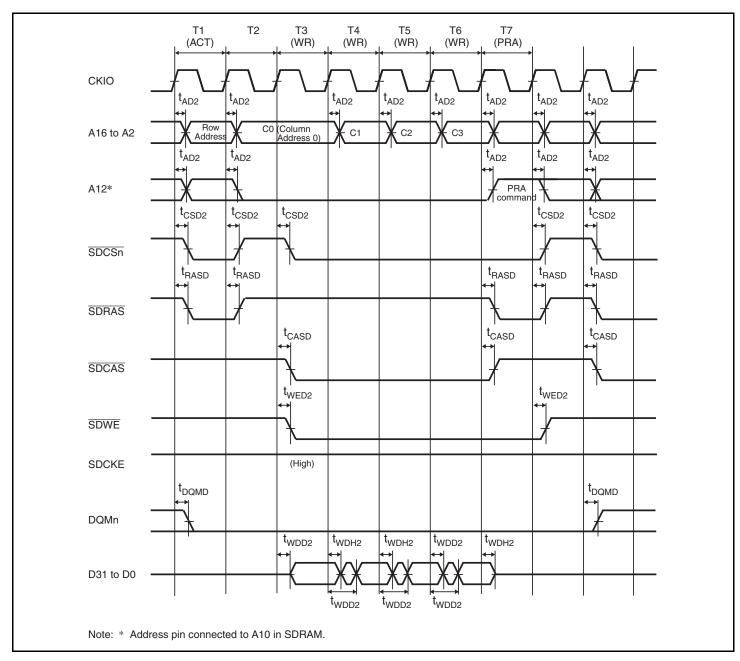

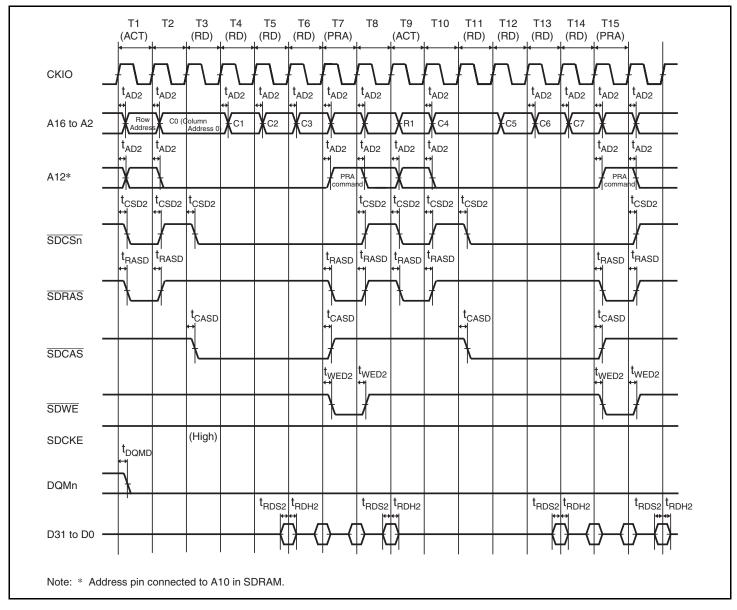

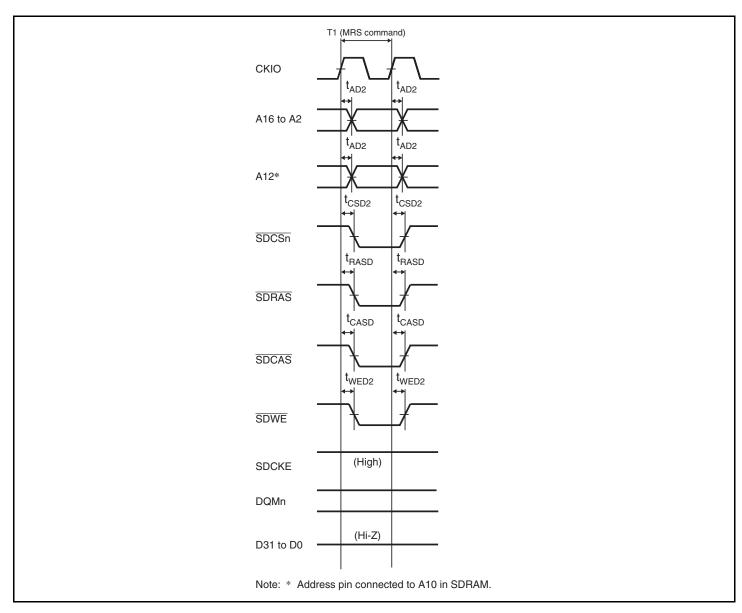

|      | 9.5.2   | SDRAM Interface                                                  | 248 |

| 9.6  | Usage   | Note                                                             | 285 |

|      | 9.6.1   | Note on Power-on Reset Exception Handling and                    |     |

|      |         | Deep Standby Mode Cancellation                                   | 285 |

|      | 9.6.2   | Write Buffer                                                     | 285 |

|      | 9.6.3   | Note on Transition to Software Standby Mode or Deep Standby Mode | 285 |

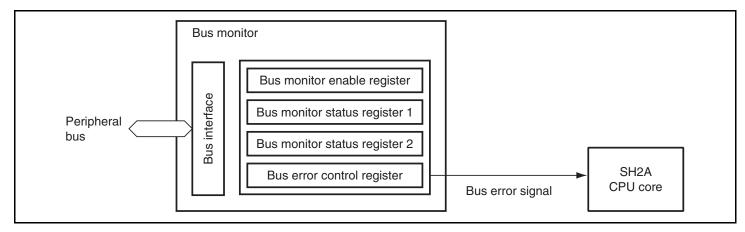

| Sect | ion 10  | Bus Monitor                                                      | 287 |

| 10.1 | Registe | er Descriptions                                                  | 287 |

|      |         | Bus Monitor Enable Register (SYCBEEN)                            |     |

|      | 10.1.2  | Bus Monitor Status Register 1 (SYCBESTS1)                        | 289 |

|      | 10.1.3  | Bus Monitor Status Register 2 (SYCBESTS2)                        | 291 |

|      | 10.1.4  | Bus Error Control Register (SYCBESW)                             | 294 |

| 10.2 |         | onitor Function                                                  |     |

|      | 10.2.1  | Operation when a Bus Error is Detected                           | 295 |

|      | 10.2.2  | Illegal Address Access Detection Function                        |     |

|      | 10.2.3  | Bus Timeout Detection Function                                   |     |

|      |         | Combinations of Masters and Bus Errors                           |     |

| 10.3 |         | Note                                                             |     |

|      | •       | Operation when the CPU is Not Notified of a Bus Error            |     |

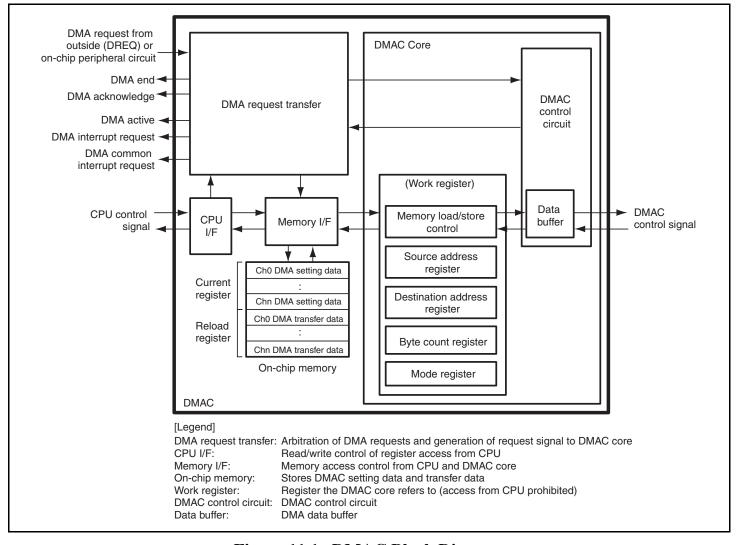

| Sect | ion 11 Direct Memory Access Controller (DMAC)               | 301 |

|------|-------------------------------------------------------------|-----|

| 11.1 | Features                                                    |     |

| 11.2 | Input/Output Pins                                           | 303 |

| 11.3 | Register Descriptions                                       | 304 |

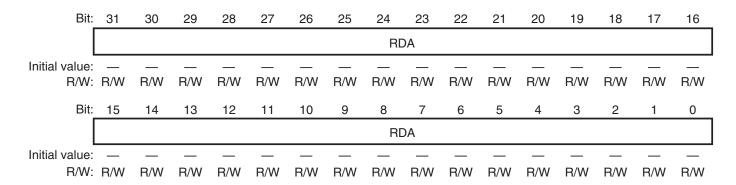

|      | 11.3.1 DMA Current Source Address Register (DMCSADR)        | 308 |

|      | 11.3.2 DMA Current Destination Address Register (DMCDADR)   | 309 |

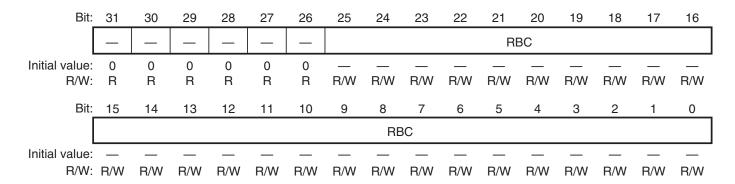

|      | 11.3.3 DMA Current Byte Count Register (DMCBCT)             | 310 |

|      | 11.3.4 DMA Reload Source Address Register (DMRSADR)         | 311 |

|      | 11.3.5 DMA Reload Destination Address Register (DMRDADR)    |     |

|      | 11.3.6 DMA Reload Byte Count Register (DMRBCT)              | 313 |

|      | 11.3.7 DMA Mode Register (DMMOD)                            | 314 |

|      | 11.3.8 DMA Control Register A (DMCNTA)                      | 320 |

|      | 11.3.9 DMA Control Register B (DMCNTB)                      | 328 |

|      | 11.3.10 DMA Activation Control Register (DMSCNT)            | 334 |

|      | 11.3.11 DMA Interrupt Control Register (DMICNT)             | 335 |

|      | 11.3.12 DMA Common Interrupt Control Register (DMICNTA)     | 336 |

|      | 11.3.13 DMA Interrupt Status Register (DMISTS)              | 337 |

|      | 11.3.14 DMA Transfer End Detection Register (DMEDET)        | 338 |

|      | 11.3.15 DMA Arbitration Status Register (DMASTS)            | 340 |

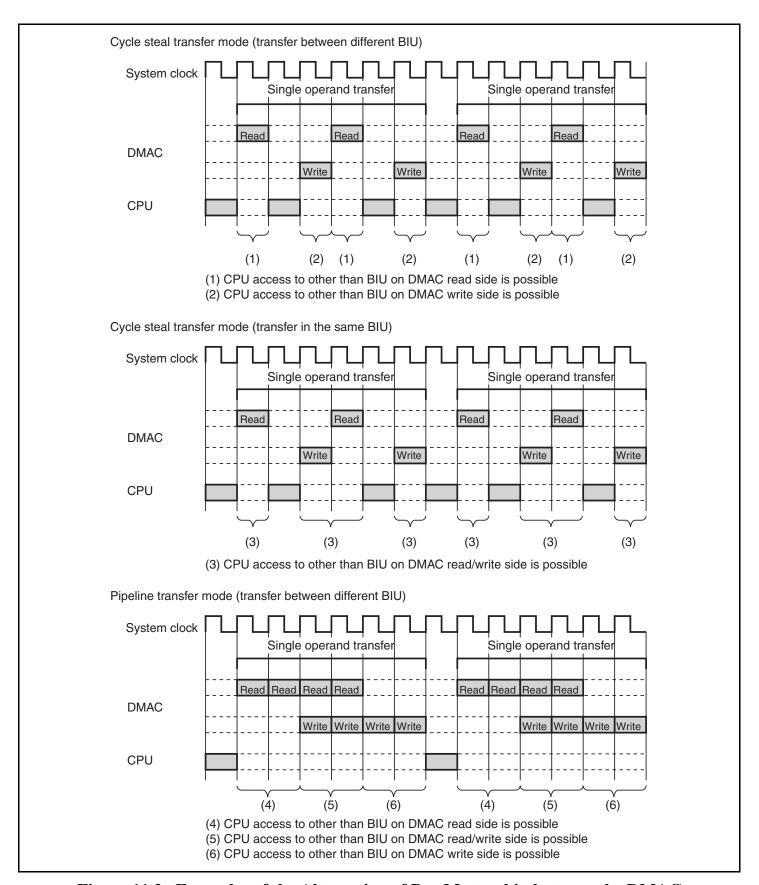

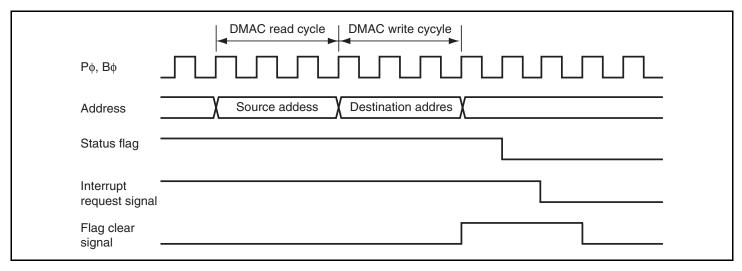

| 11.4 | Operation                                                   | 342 |

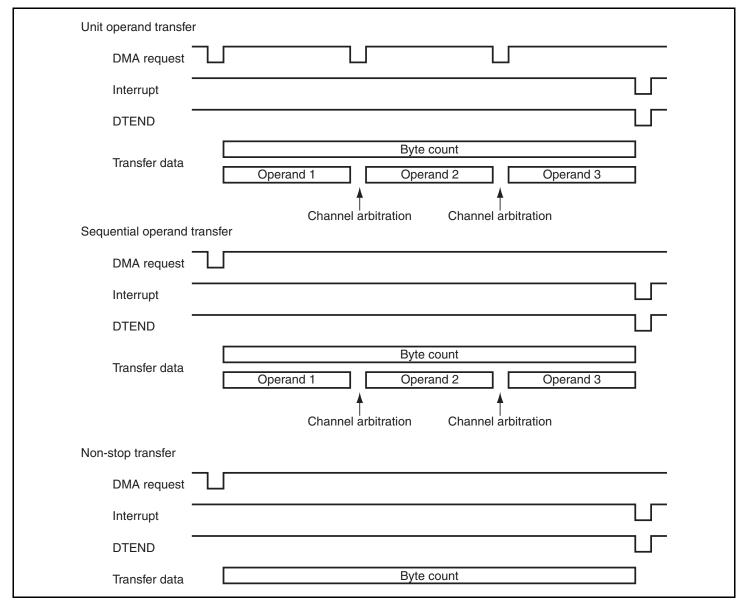

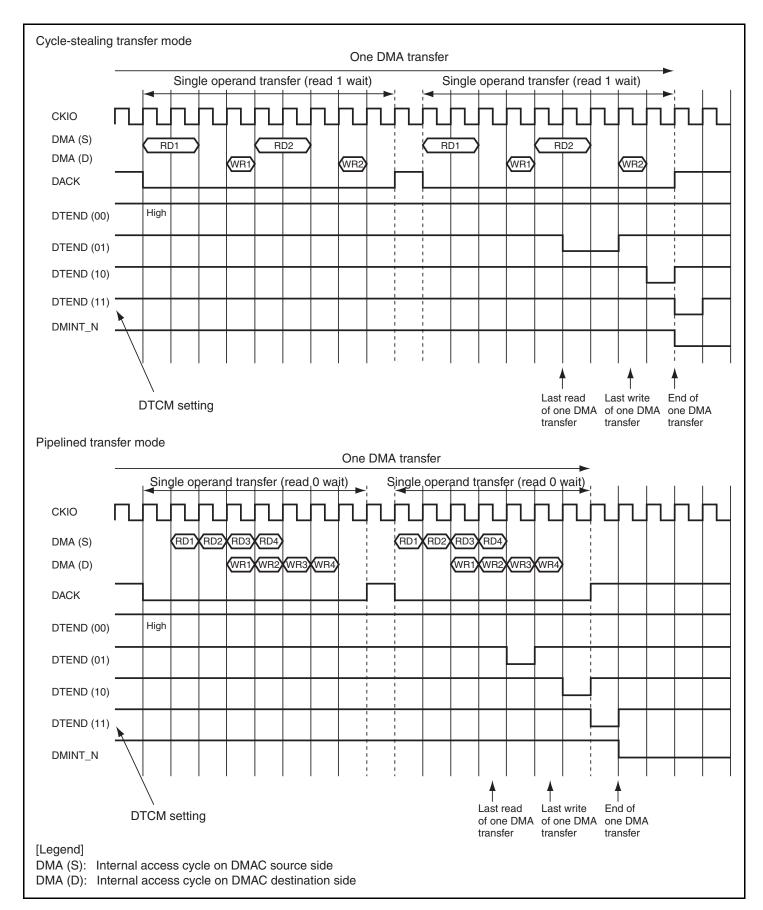

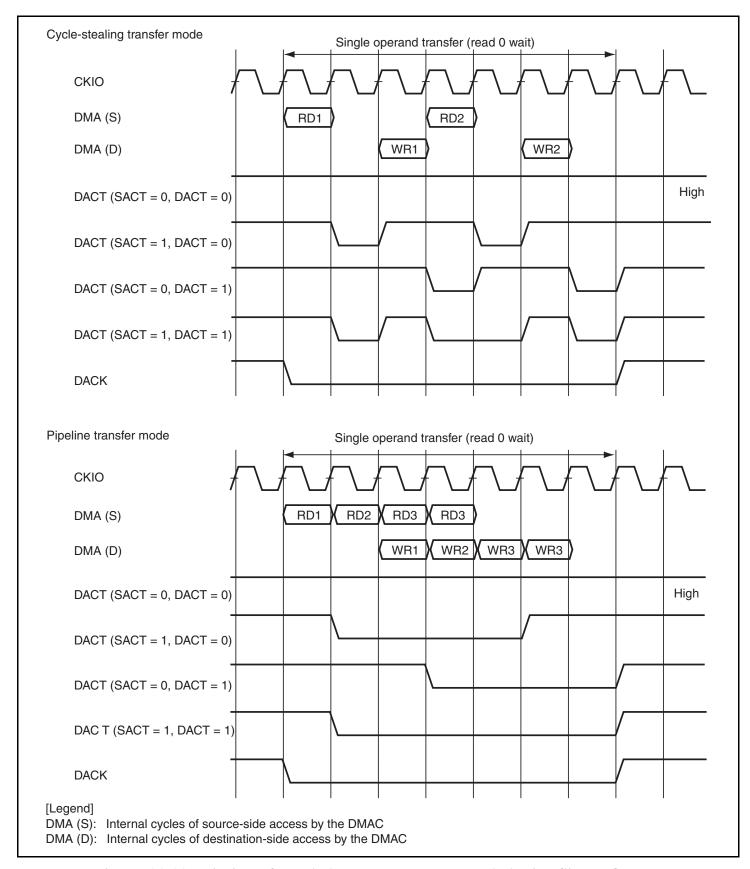

|      | 11.4.1 DMA Transfer Mode                                    | 342 |

|      | 11.4.2 DMA Transfer Condition                               | 344 |

|      | 11.4.3 DMA Activation                                       | 348 |

| 11.5 | Completion of DMA Transfer and Interrupts                   |     |

|      | 11.5.1 Completion of DMA Transfer                           | 349 |

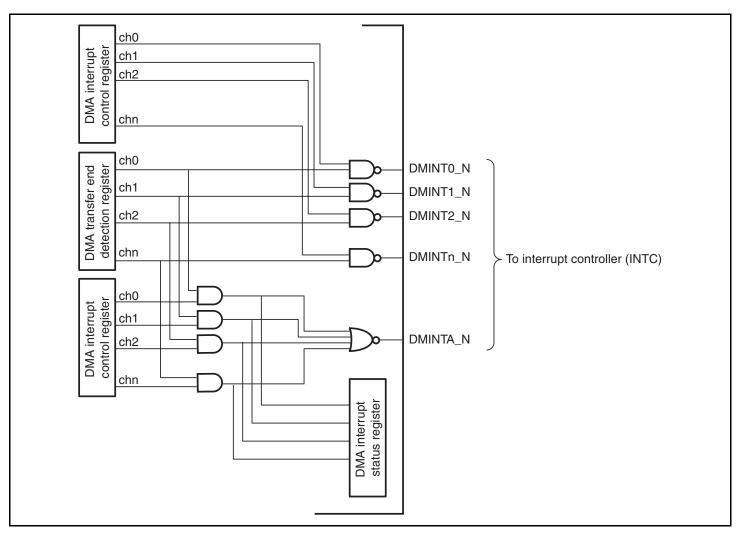

|      | 11.5.2 DMA Interrupt Requests                               | 350 |

|      | 11.5.3 DMA End Signal Output                                | 352 |

| 11.6 | Suspending, Restarting, and Stopping of DMA Transfer        | 354 |

|      | 11.6.1 Suspending and Restarting DMA Transfer               | 354 |

|      | 11.6.2 Stopping DMA Transfer on Any Channel                 | 354 |

| 11.7 | DMA Requests                                                | 355 |

|      | 11.7.1 Sources of DMA Requests                              | 355 |

|      | 11.7.2 Synchronous Circuits for DMA Request Signals         | 355 |

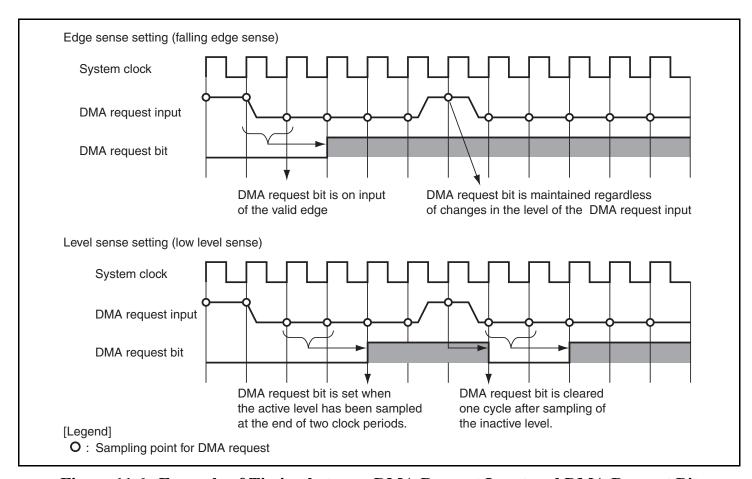

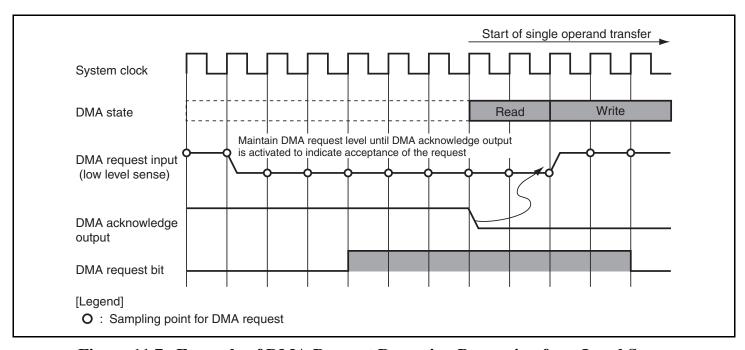

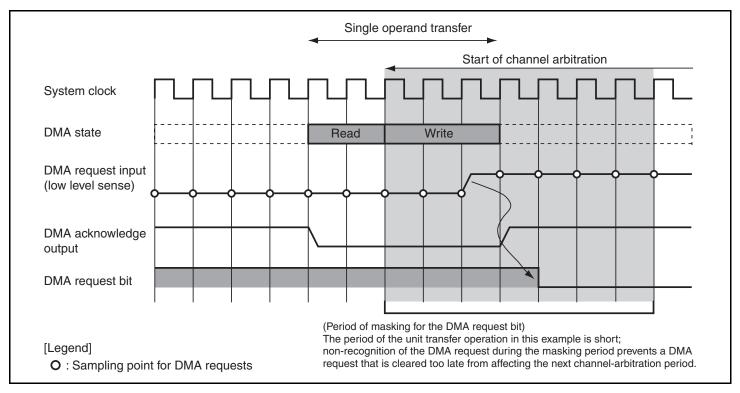

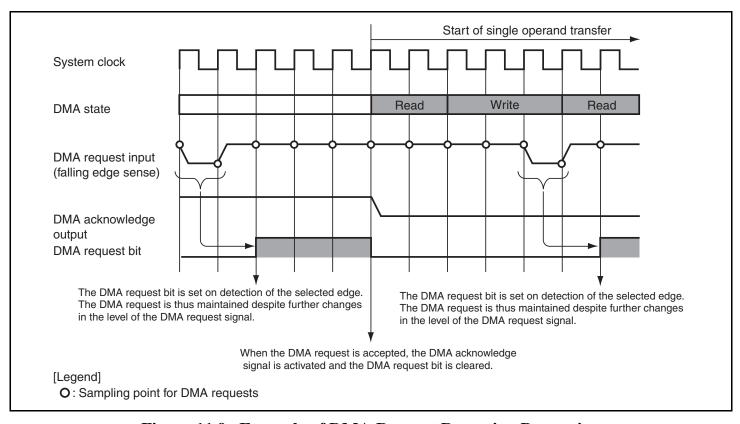

|      | 11.7.3 Sense Mode for DMA Requests                          | 356 |

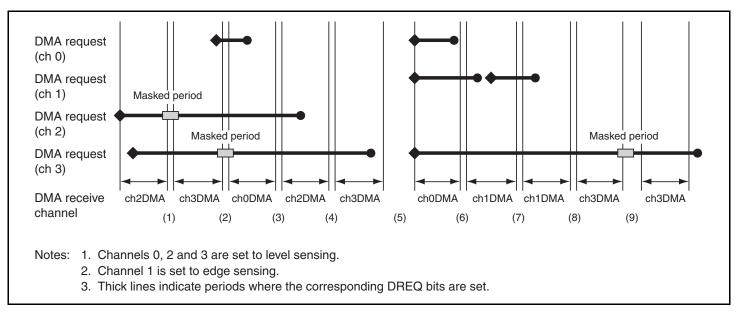

| 11.8 | Determining DMA Channel Priority                            | 359 |

|      | 11.8.1 Channel Priority Order                               | 359 |

|      | 11.8.2 Operation during Multiple DMA Requests               | 359 |

|      | 11.8.3 Output of the DMA Acknowledge and DNA Active Signals | 360 |

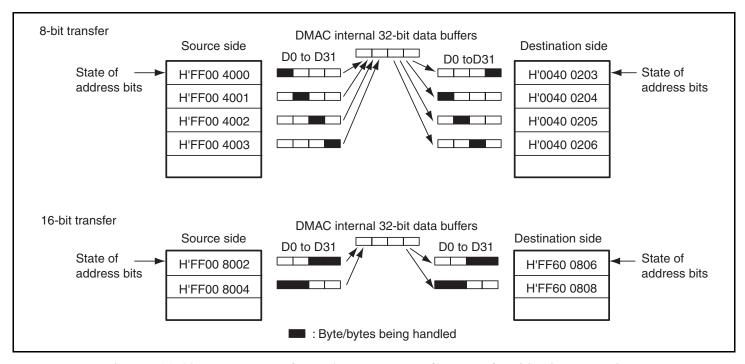

| 11.9 | Units of Transfer and Positioning of Bytes for Transfer     | 362 |

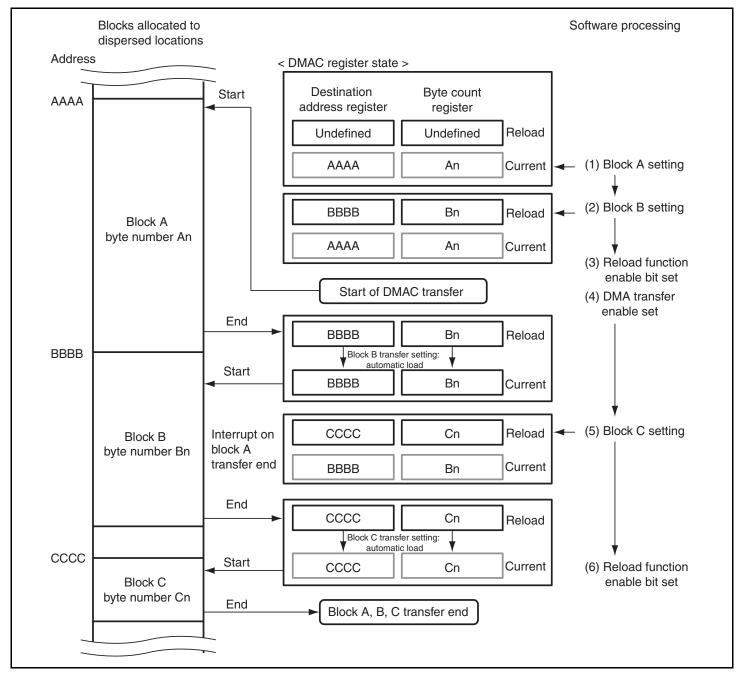

| 11.10 | Reload   | Function                                                     | 363 |

|-------|----------|--------------------------------------------------------------|-----|

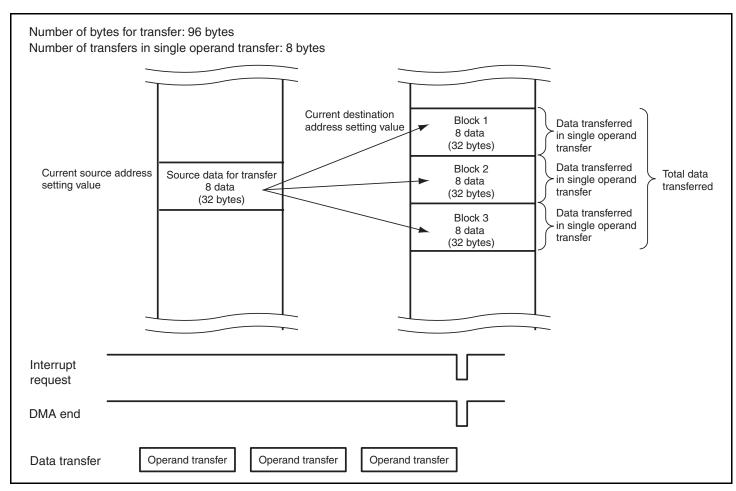

| 11.11 | Rotate I | Function                                                     | 365 |

| 11.12 | Transfe  | r Speed                                                      | 366 |

| 11.13 | Usage N  | Note                                                         | 367 |

|       | 11.13.1  | Note on Making a Transition To Software Standby              |     |

|       |          | Mode or Deep Standby Mode                                    | 367 |

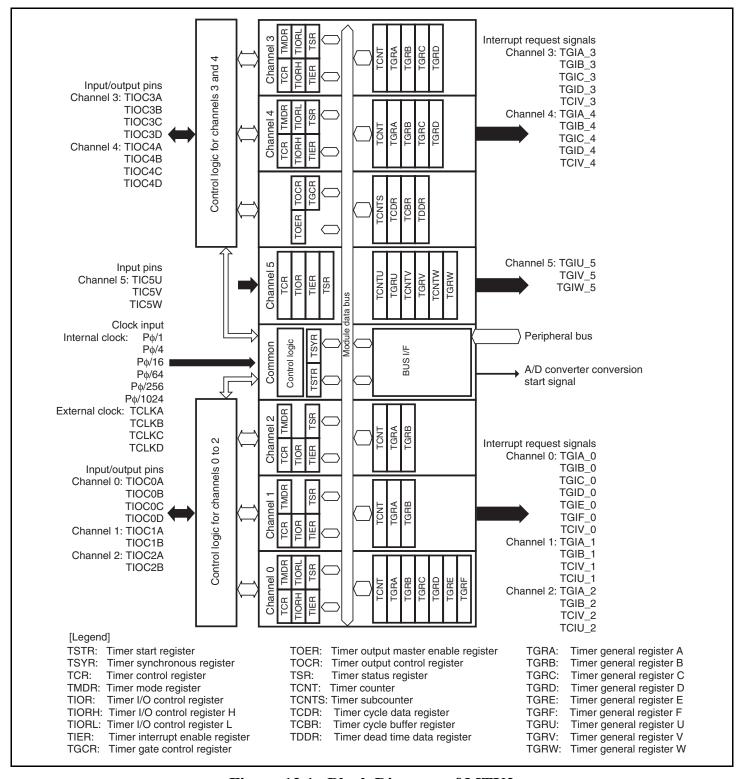

| Secti | on 12    | Multi-Function Timer Pulse Unit 2 (MTU2)                     | 369 |

| 12.1  | Feature  | s                                                            | 369 |

| 12.2  | Input/O  | utput Pins                                                   | 375 |

| 12.3  | Registe  | r Descriptions                                               | 376 |

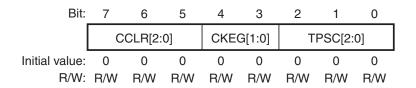

|       | 12.3.1   | Timer Control Register (TCR)                                 | 382 |

|       | 12.3.2   | Timer Mode Register (TMDR)                                   | 386 |

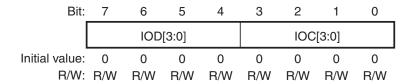

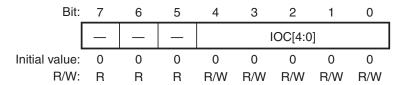

|       | 12.3.3   | Timer I/O Control Register (TIOR)                            | 389 |

|       | 12.3.4   | Timer Compare Match Clear Register (TCNTCMPCLR)              | 408 |

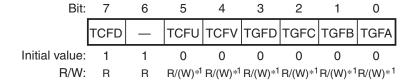

|       | 12.3.5   | Timer Interrupt Enable Register (TIER)                       | 409 |

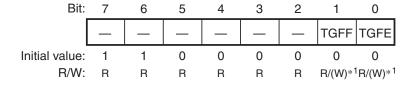

|       | 12.3.6   | Timer Status Register (TSR)                                  | 414 |

|       | 12.3.7   | Timer Buffer Operation Transfer Mode Register (TBTM)         | 421 |

|       | 12.3.8   | Timer Input Capture Control Register (TICCR)                 | 422 |

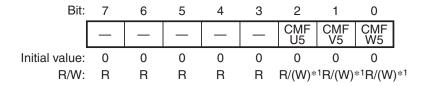

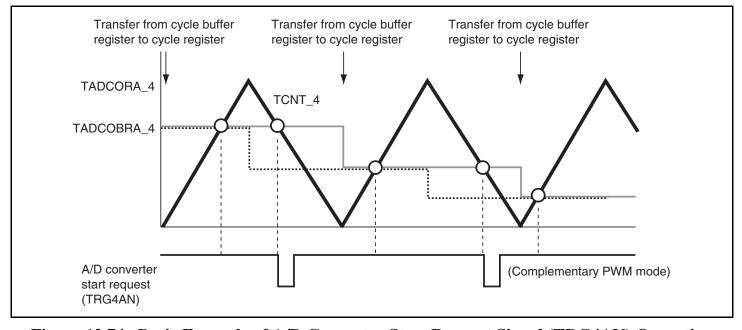

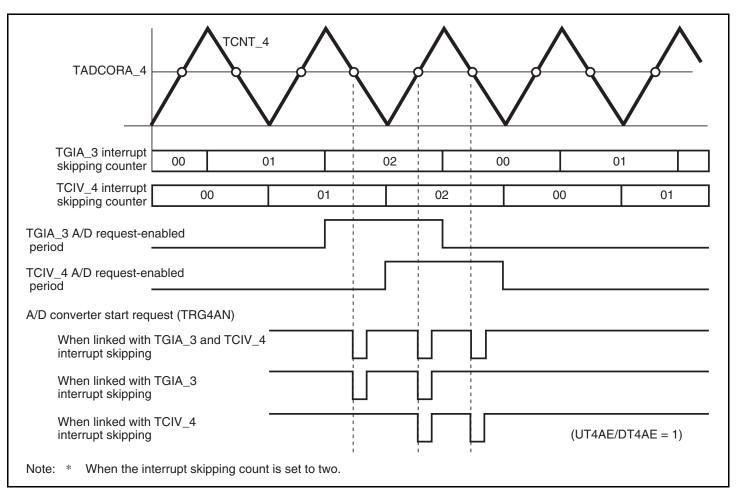

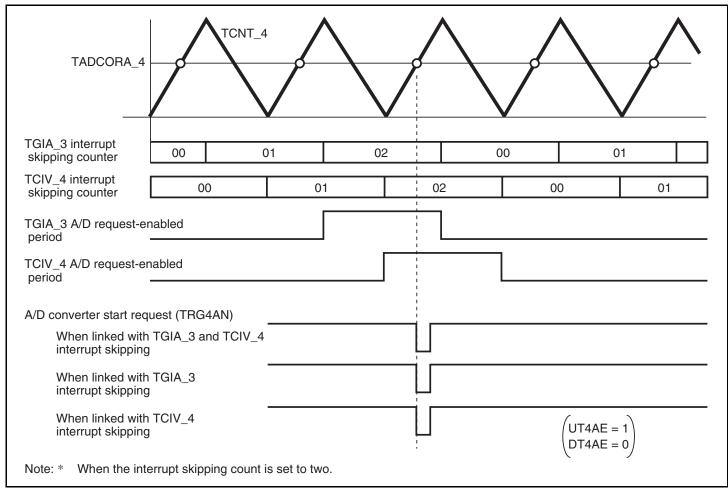

|       | 12.3.9   | Timer A/D Converter Start Request Control Register (TADCR)   | 423 |

|       | 12.3.10  | Timer A/D Converter Start Request Cycle Set Registers        |     |

|       |          | (TADCORA_4 and TADCORB_4)                                    | 426 |

|       | 12.3.11  | Timer A/D Converter Start Request Cycle Set Buffer Registers |     |

|       |          | (TADCOBRA_4 and TADCOBRB_4)                                  | 427 |

|       | 12.3.12  | Timer Counter (TCNT)                                         | 427 |

|       | 12.3.13  | Timer General Register (TGR)                                 | 428 |

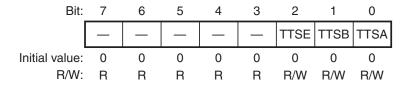

|       |          | Timer Start Register (TSTR)                                  |     |

|       | 12.3.15  | Timer Synchronous Register (TSYR)                            | 431 |

|       | 12.3.16  | Timer Counter Synchronous Start Register (TCSYSTR)           | 433 |

|       |          | Timer Read/Write Enable Register (TRWER)                     |     |

|       | 12.3.18  | Timer Output Master Enable Register (TOER)                   | 436 |

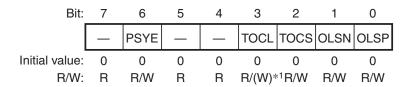

|       | 12.3.19  | Timer Output Control Register 1 (TOCR1)                      | 437 |

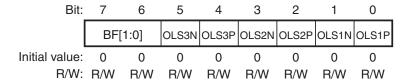

|       |          | Timer Output Control Register 2 (TOCR2)                      |     |

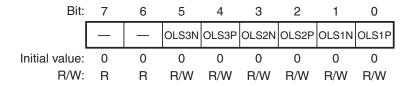

|       | 12.3.21  | Timer Output Level Buffer Register (TOLBR)                   | 443 |

|       |          | Timer Gate Control Register (TGCR)                           |     |

|       | 12.3.23  | Timer Subcounter (TCNTS)                                     | 446 |

|       |          | Timer Dead Time Data Register (TDDR)                         |     |

|       |          | Timer Cycle Data Register (TCDR)                             |     |

|       |          | Timer Cycle Buffer Register (TCBR)                           |     |

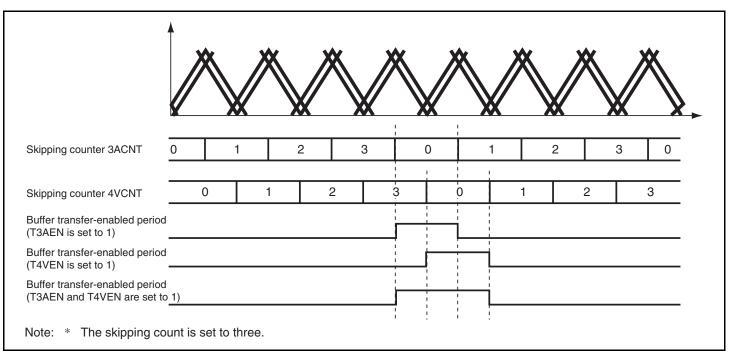

|       |          | Timer Interrupt Skipping Set Register (TITCR)                |     |

|       |          |                                                              |     |

|      | 12.3.28 | 3 Timer Interrupt Skipping Counter (TITCNT)                            | 450 |

|------|---------|------------------------------------------------------------------------|-----|

|      | 12.3.29 | Timer Buffer Transfer Set Register (TBTER)                             | 451 |

|      | 12.3.30 | Timer Dead Time Enable Register (TDER)                                 | 453 |

|      | 12.3.31 | Timer Waveform Control Register (TWCR)                                 | 454 |

|      | 12.3.32 | 2 Bus Master Interface                                                 | 455 |

| 12.4 | Operati | ion                                                                    | 456 |

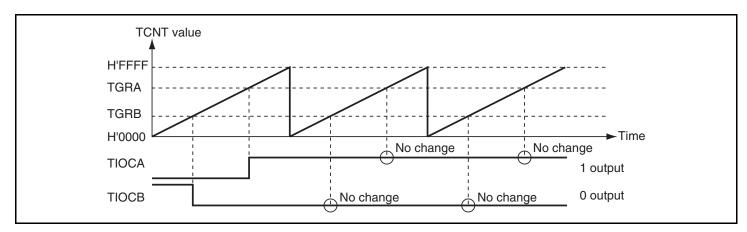

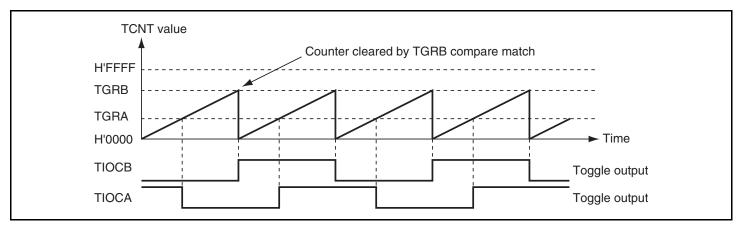

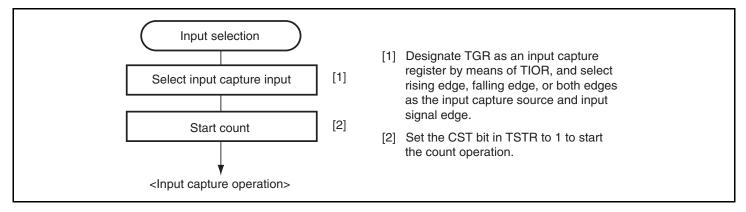

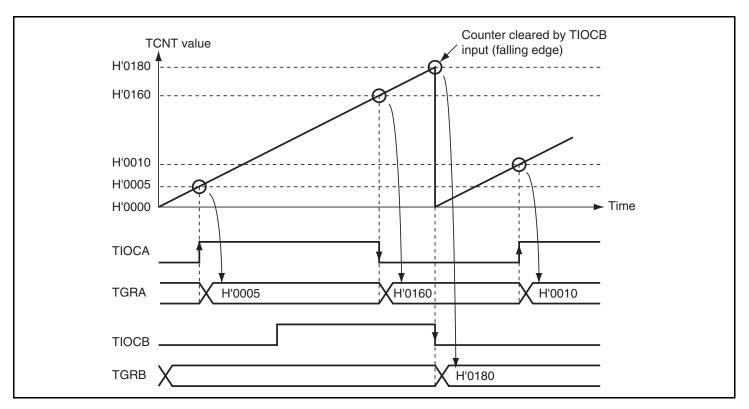

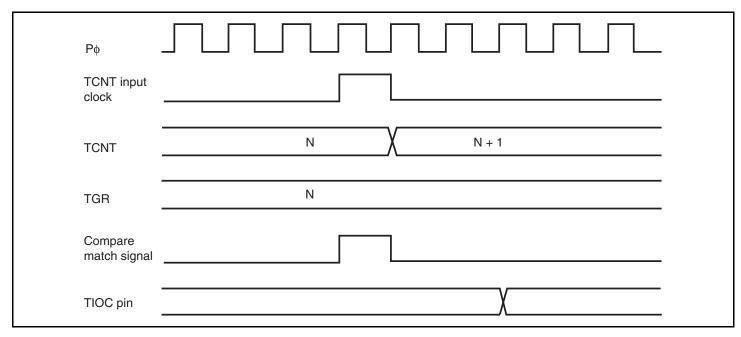

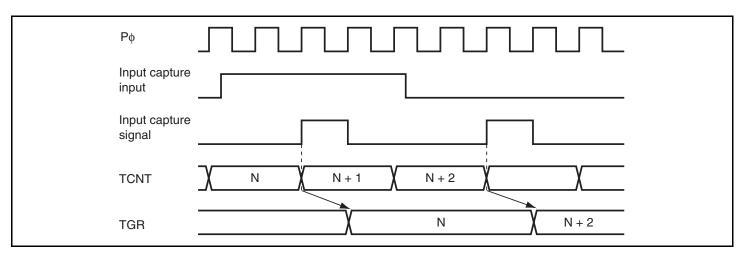

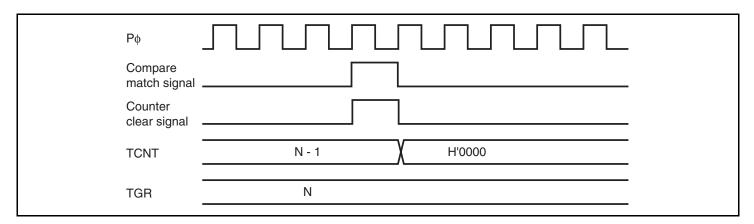

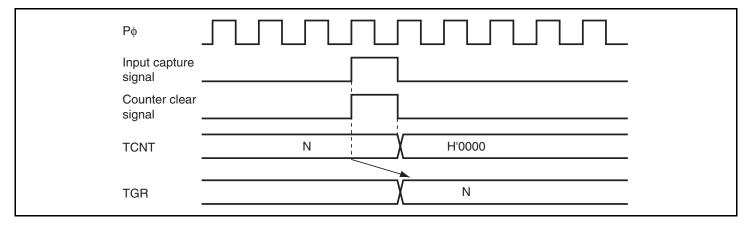

|      | 12.4.1  | Basic Functions                                                        | 456 |

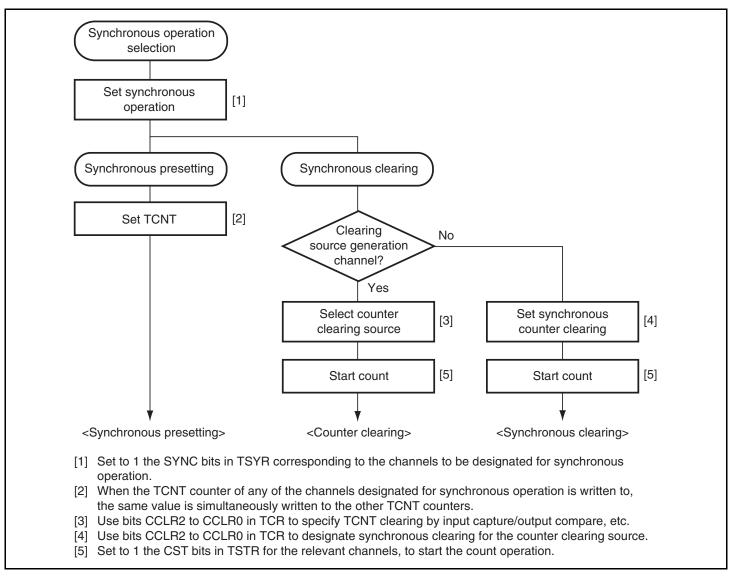

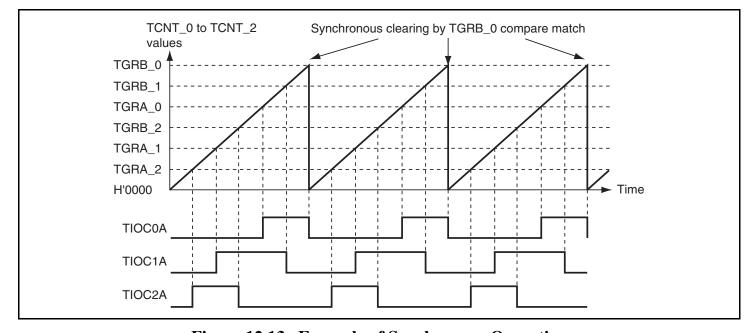

|      | 12.4.2  | Synchronous Operation                                                  | 462 |

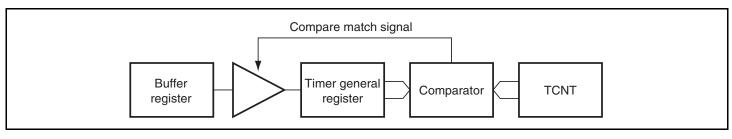

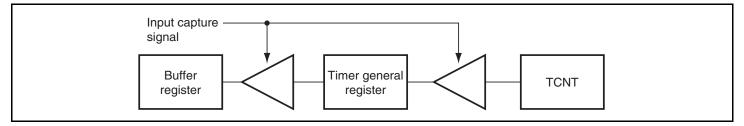

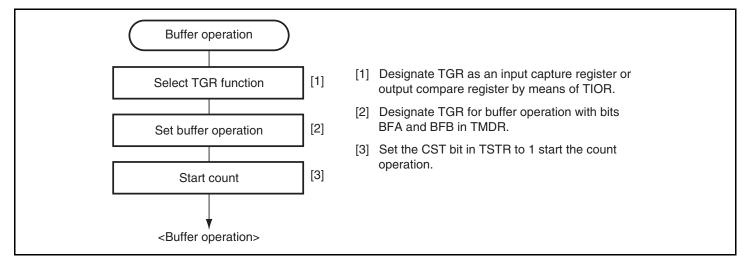

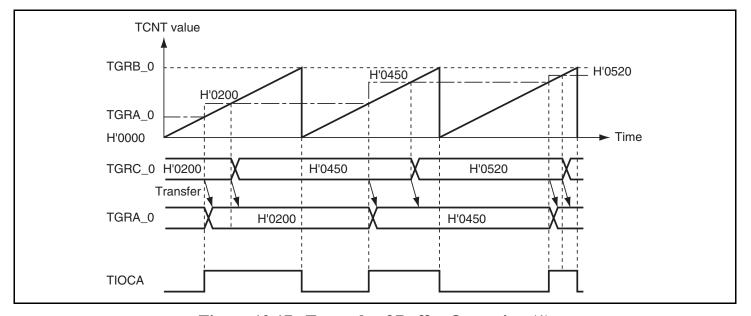

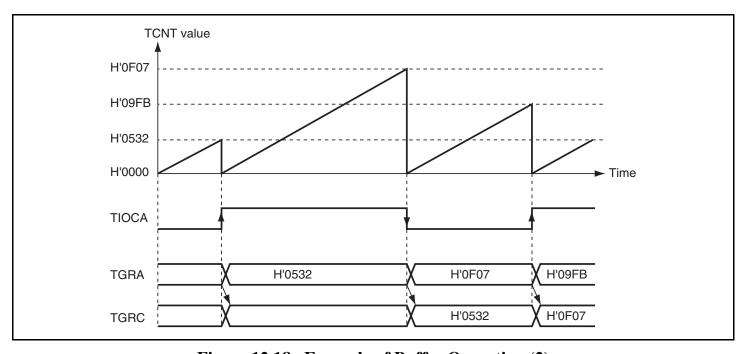

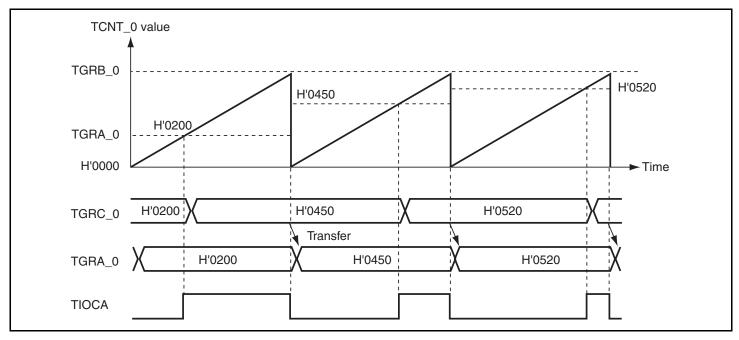

|      | 12.4.3  | Buffer Operation                                                       | 464 |

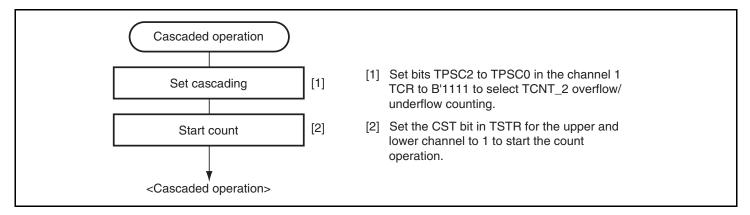

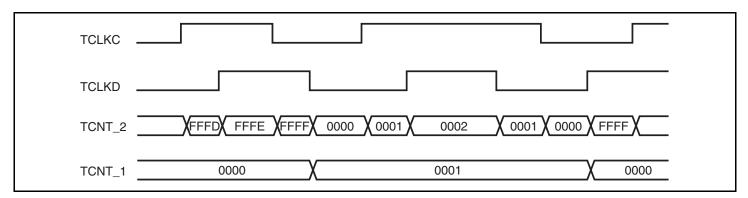

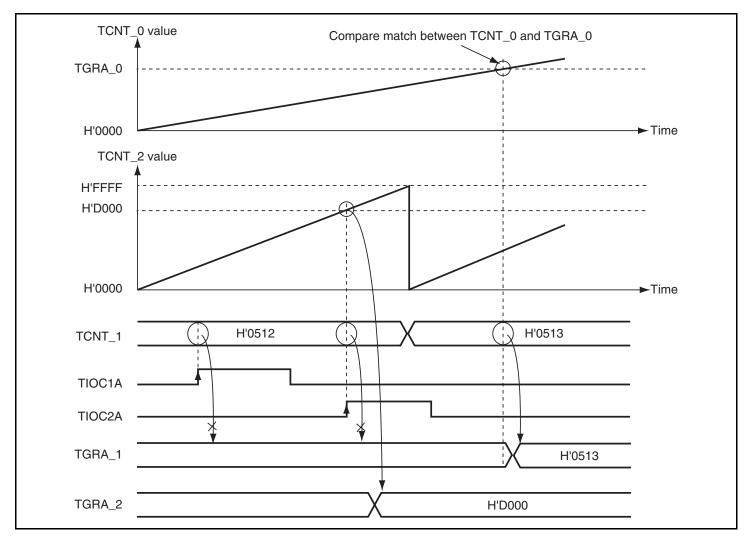

|      | 12.4.4  | Cascaded Operation                                                     | 469 |

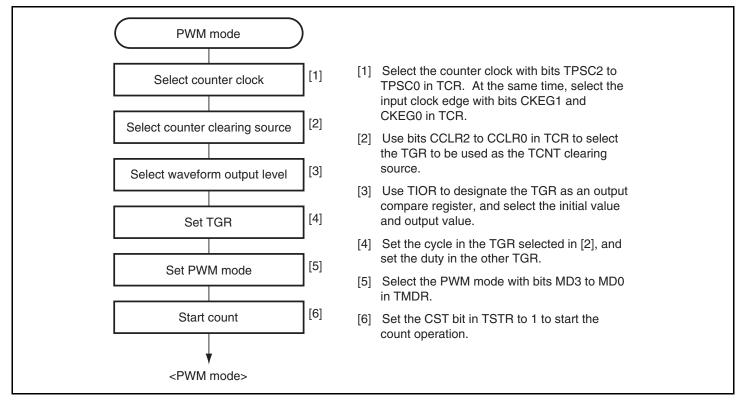

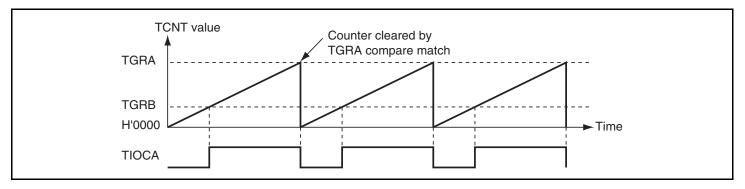

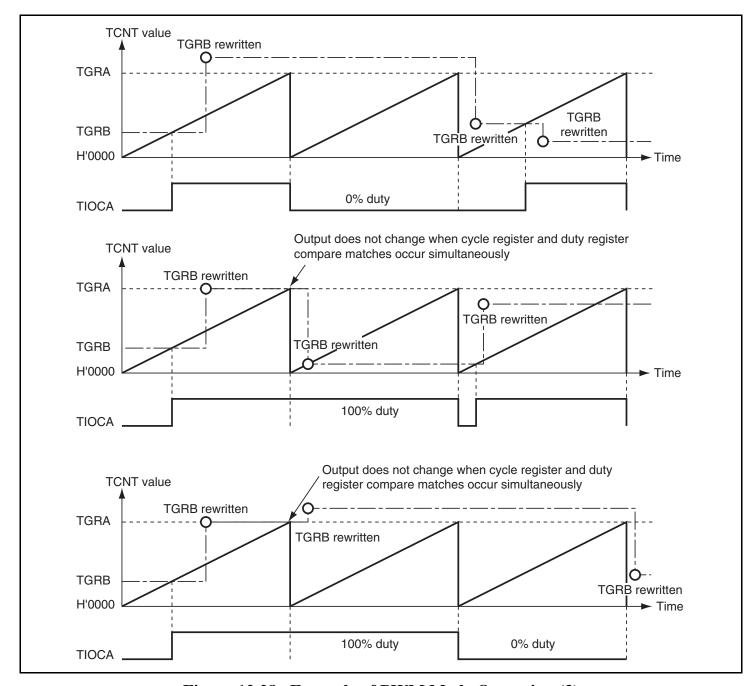

|      | 12.4.5  | PWM Modes                                                              | 474 |

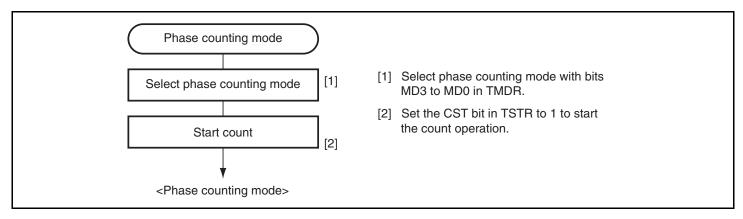

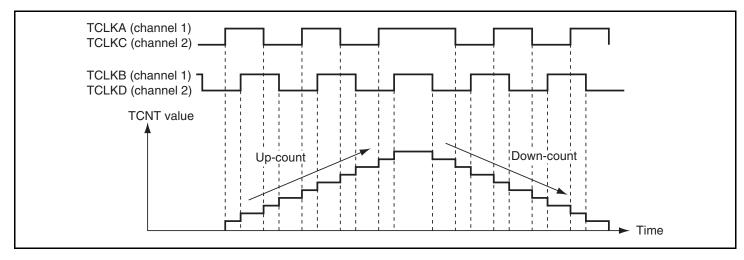

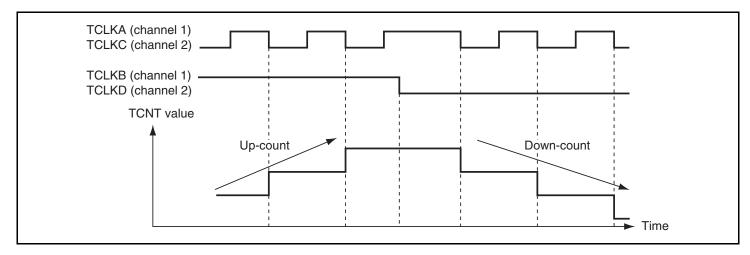

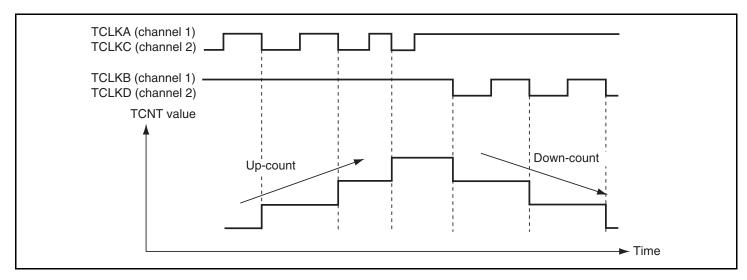

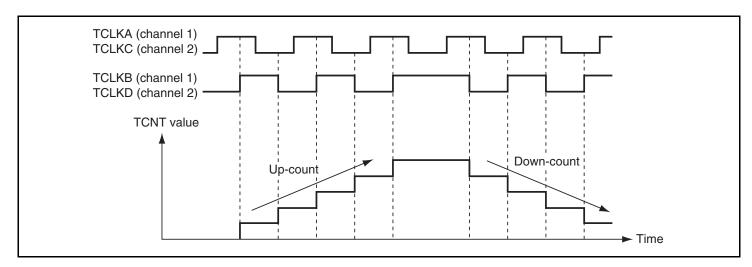

|      | 12.4.6  | Phase Counting Mode                                                    | 479 |

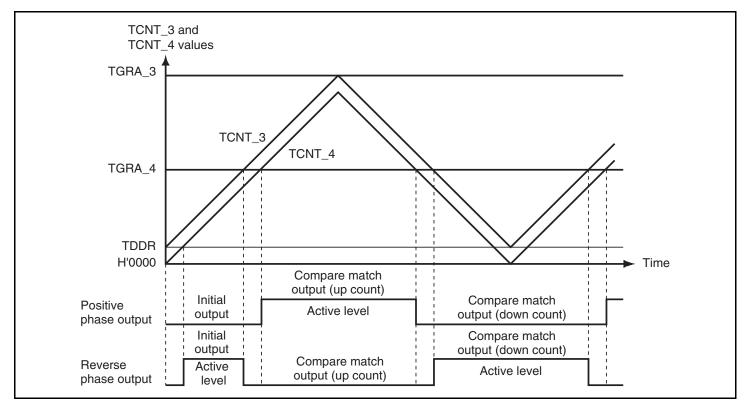

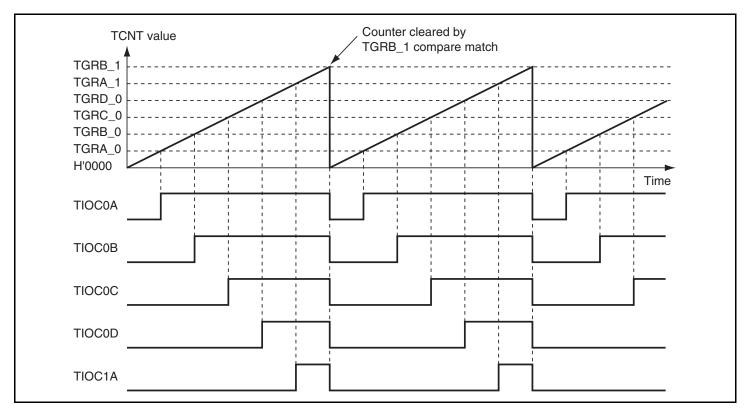

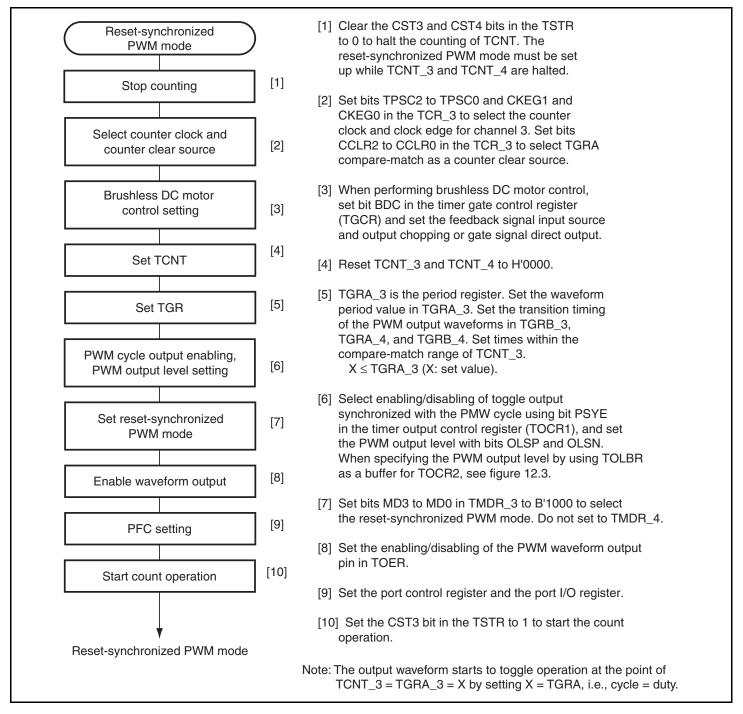

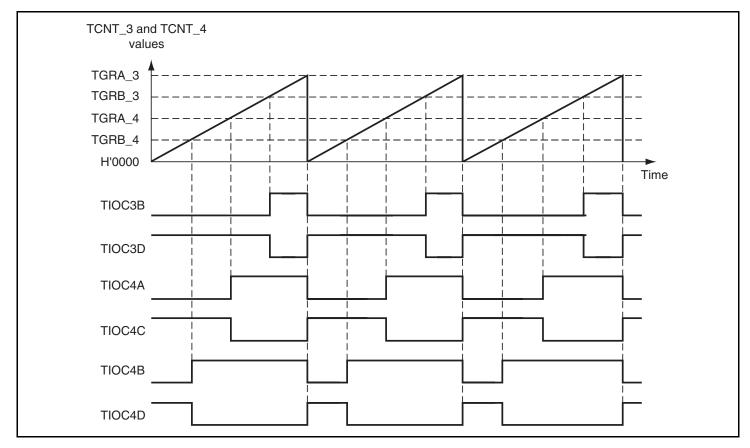

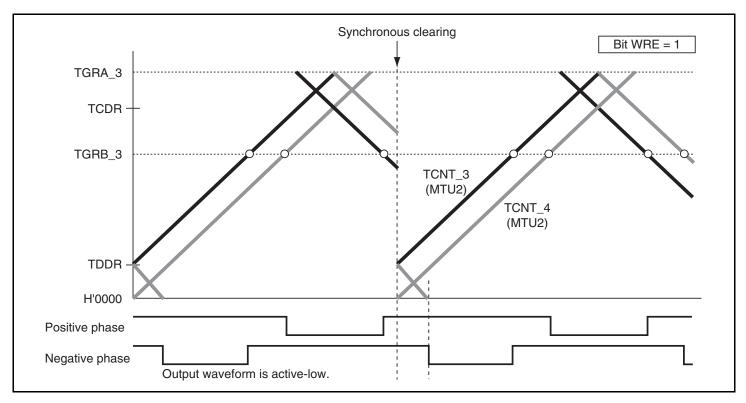

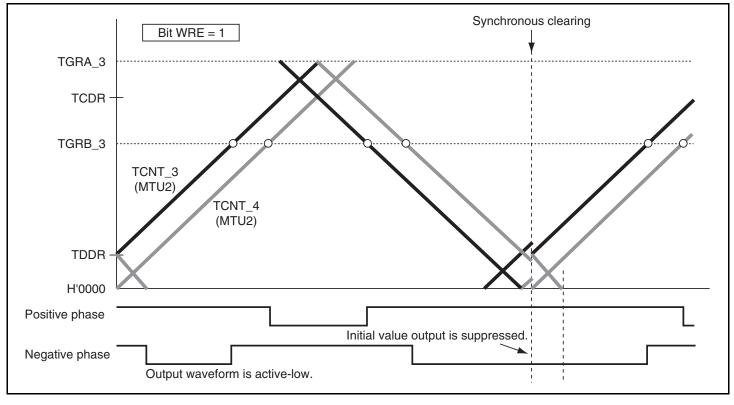

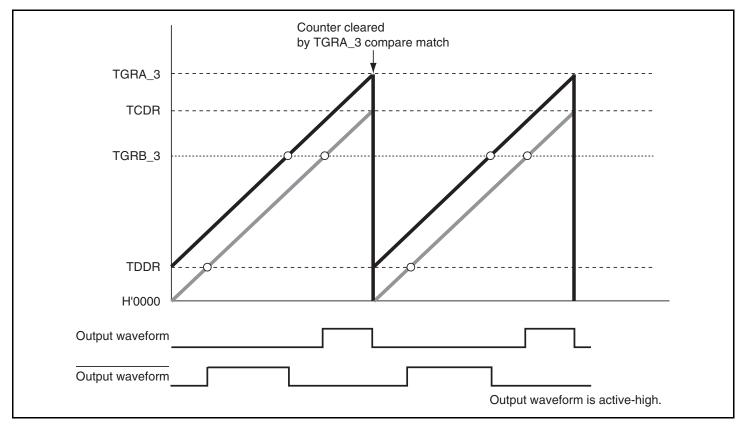

|      | 12.4.7  | Reset-Synchronized PWM Mode                                            | 486 |

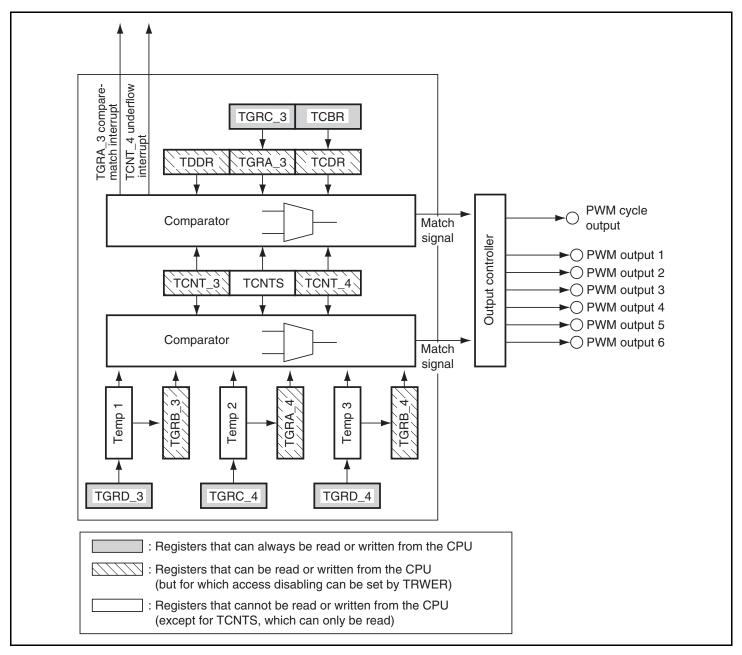

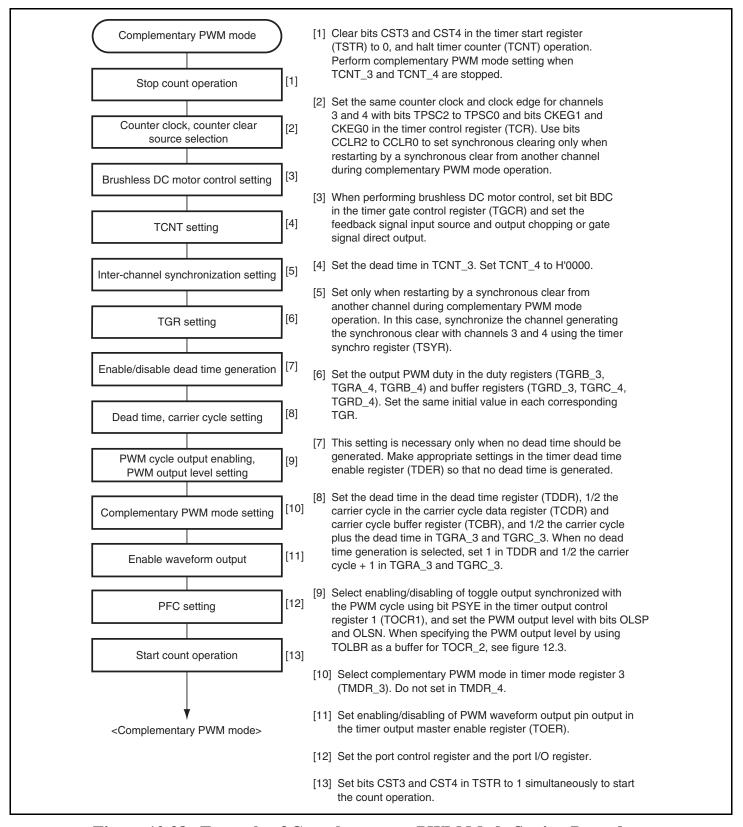

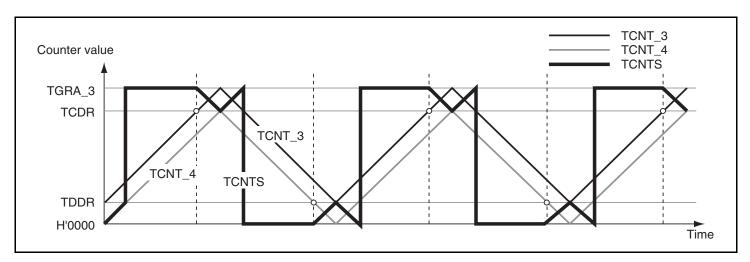

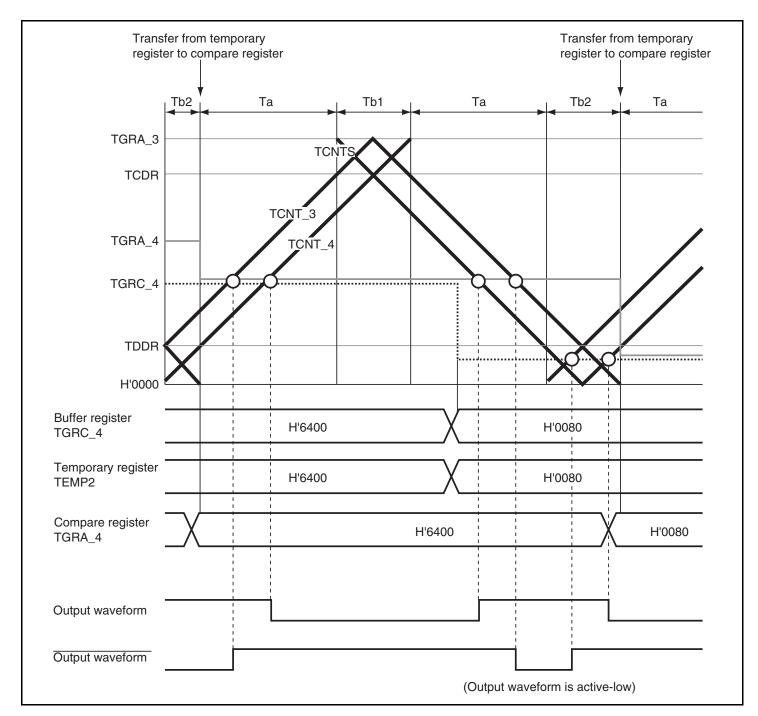

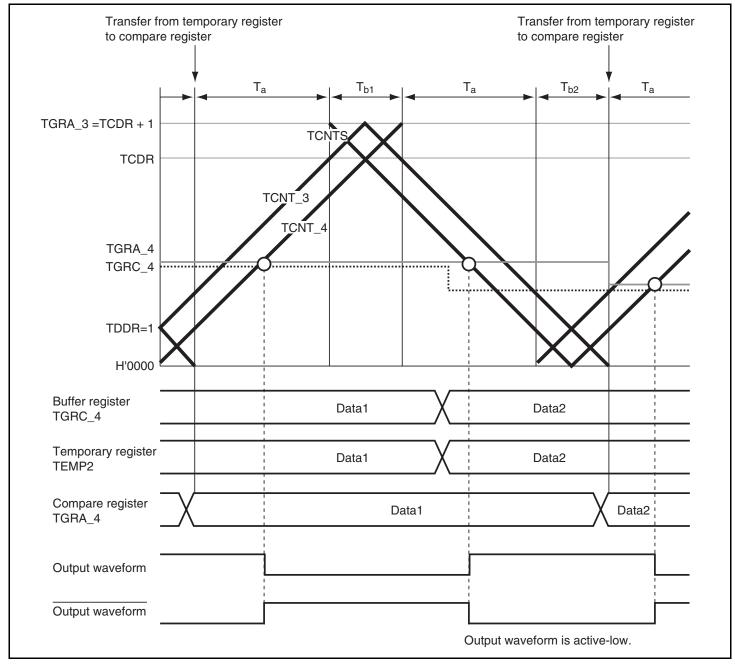

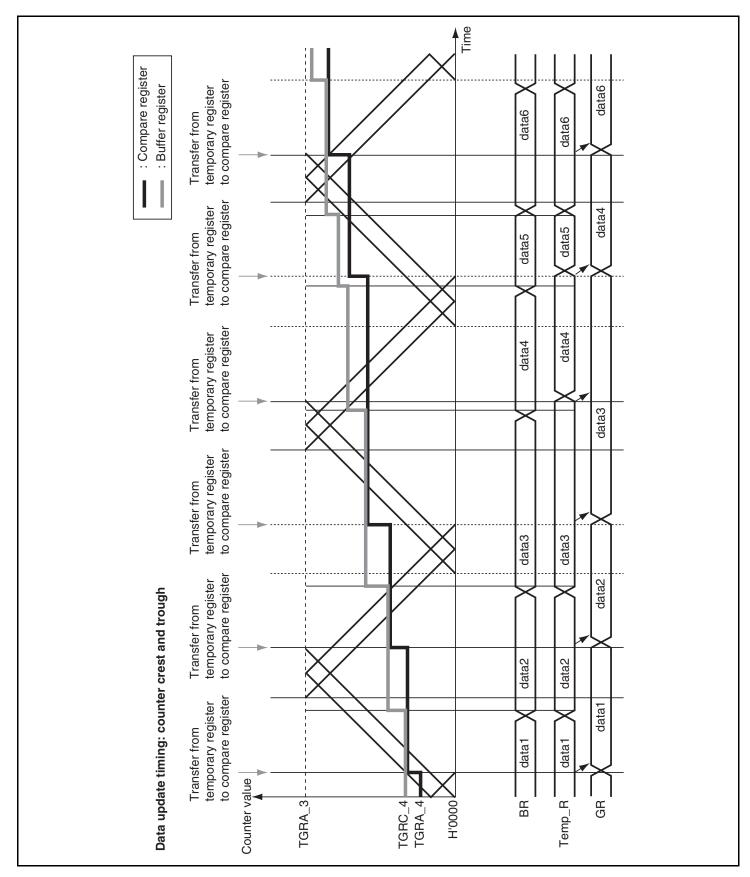

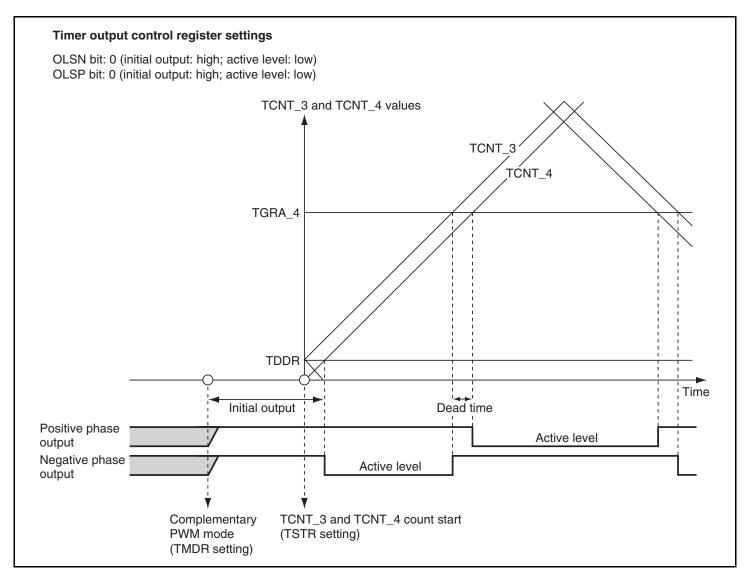

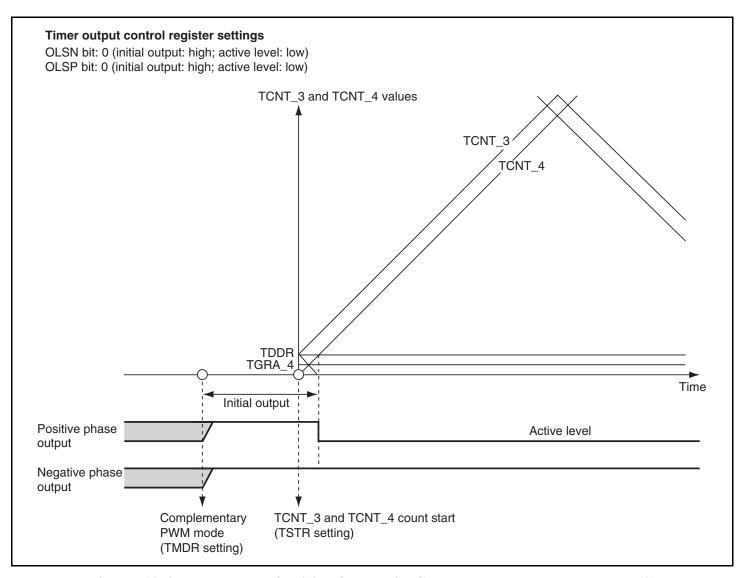

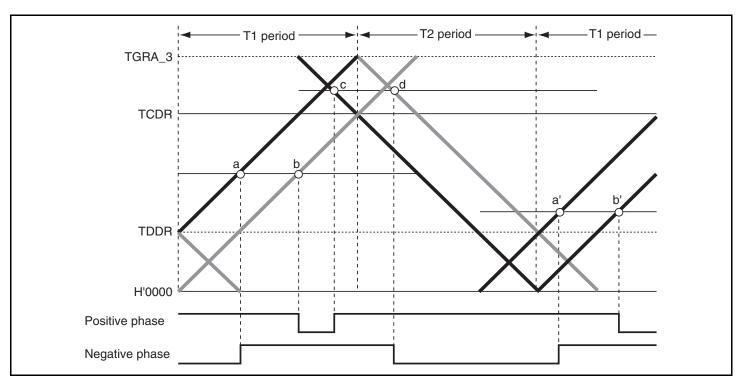

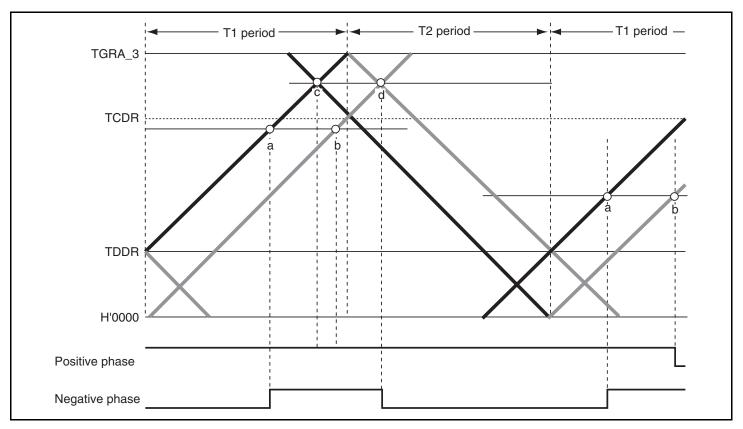

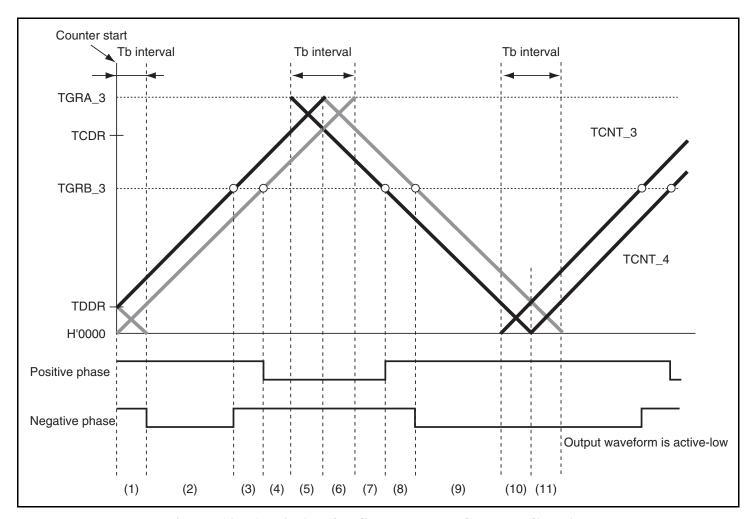

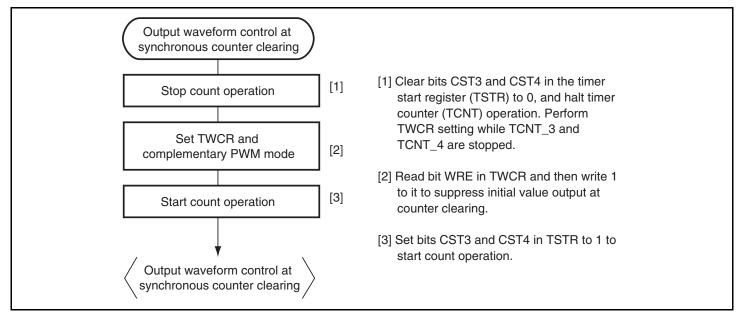

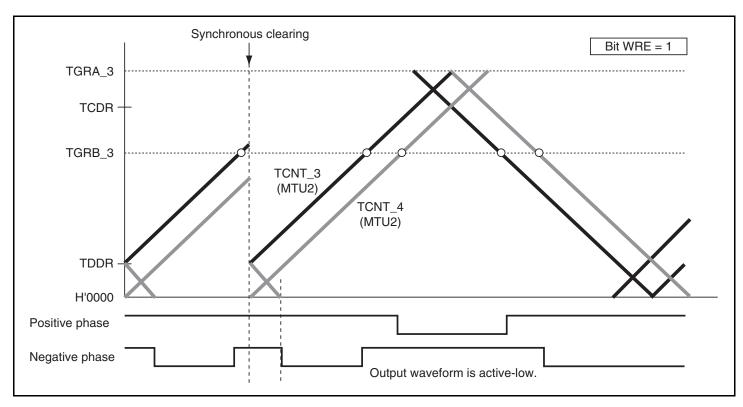

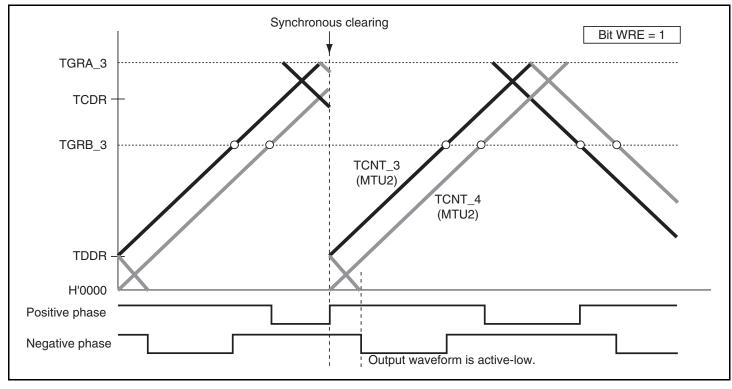

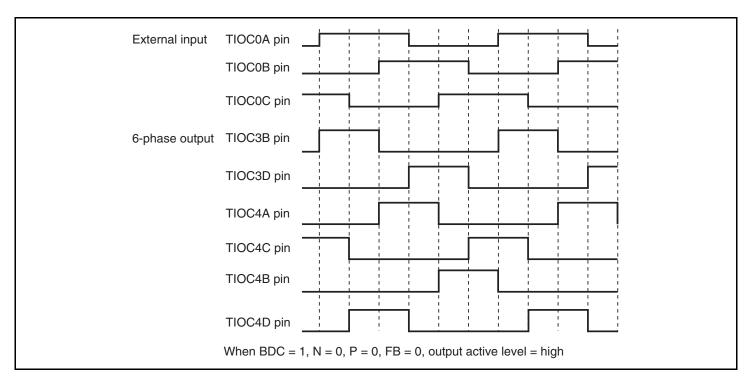

|      | 12.4.8  | Complementary PWM Mode                                                 | 489 |

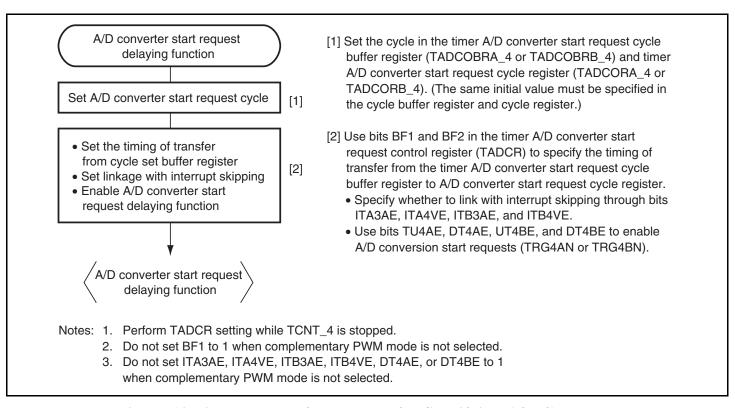

|      | 12.4.9  | A/D Converter Start Request Delaying Function                          | 525 |

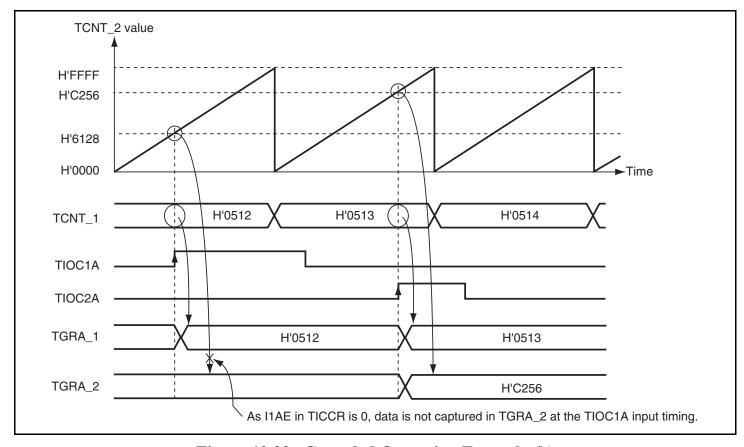

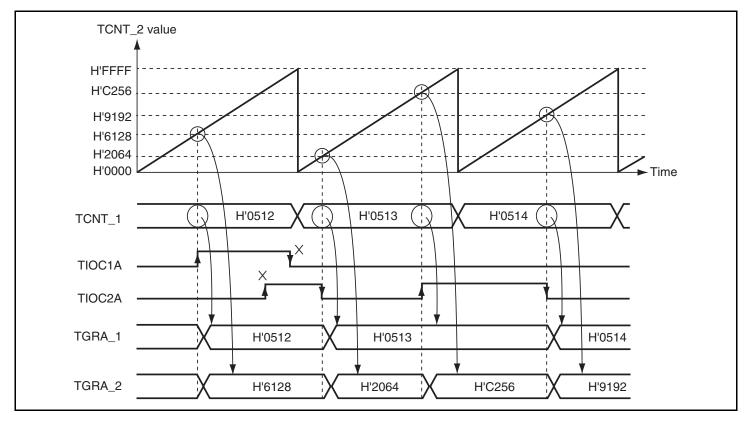

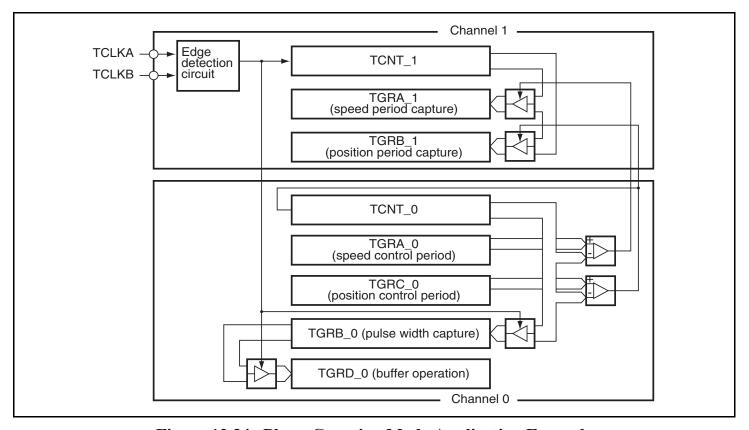

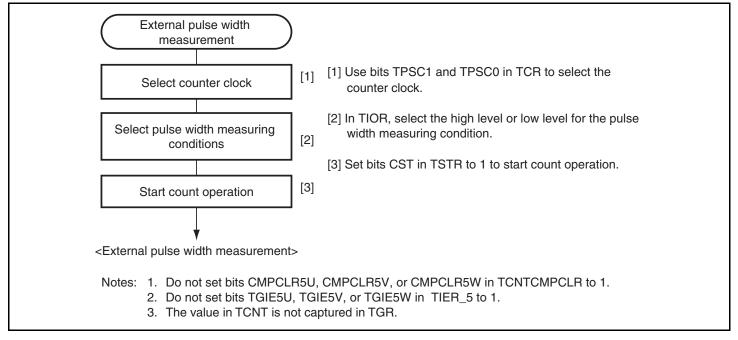

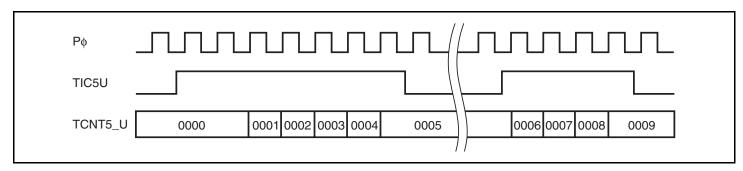

|      | 12.4.10 | External Pulse Width Measurement                                       | 529 |

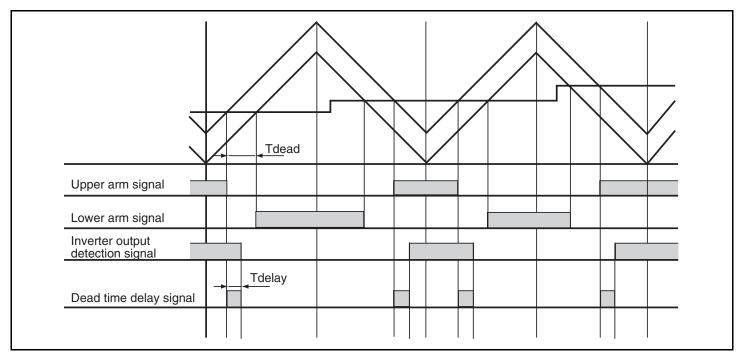

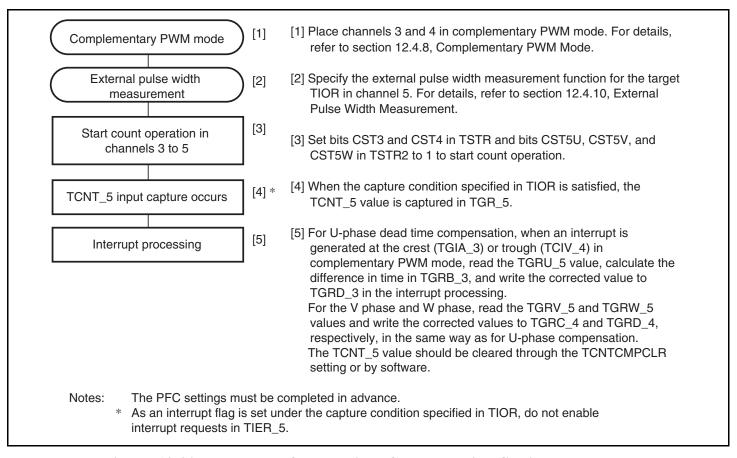

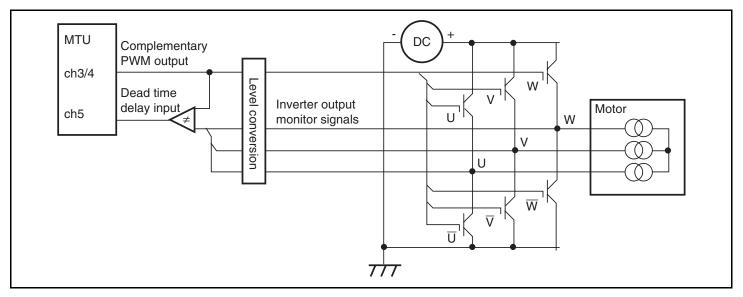

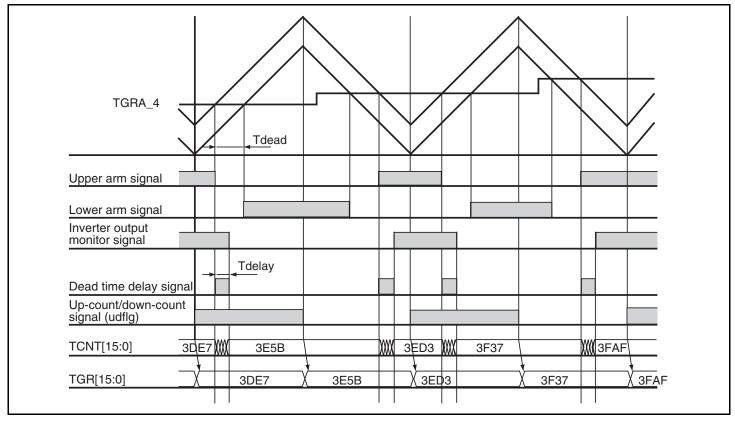

|      | 12.4.11 | Dead Time Compensation                                                 | 530 |

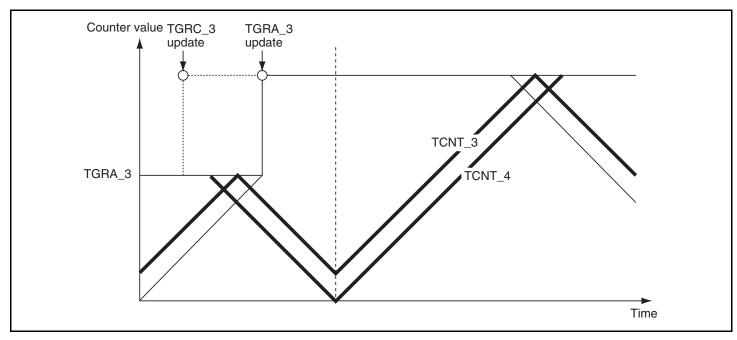

|      | 12.4.12 | 2 TCNT Capture at Crest and/or Trough in Complementary PWM Operation   | 532 |

| 12.5 | Interru | pt Sources                                                             | 533 |

|      |         | Interrupt Sources and Priorities                                       |     |

|      | 12.5.2  | DMAC Activation.                                                       | 535 |

|      |         | A/D Converter Activation                                               |     |

| 12.6 | -       | ion Timing                                                             |     |

|      |         | Input/Output Timing                                                    |     |

|      |         | Interrupt Signal Timing                                                |     |

| 12.7 | Usage   | Notes                                                                  |     |

|      | 12.7.1  | Module Standby Mode Setting                                            | 548 |

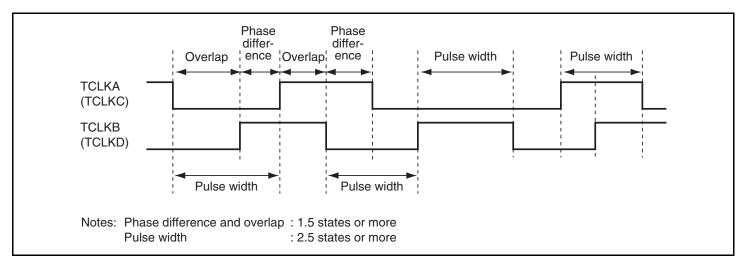

|      | 12.7.2  | Input Clock Restrictions                                               |     |

|      | 12.7.3  | Caution on Period Setting                                              |     |

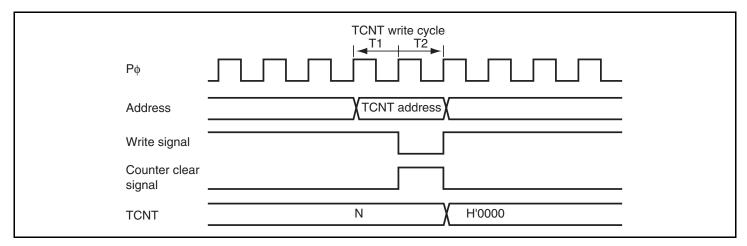

|      | 12.7.4  | Contention between TCNT Write and Clear Operations                     |     |

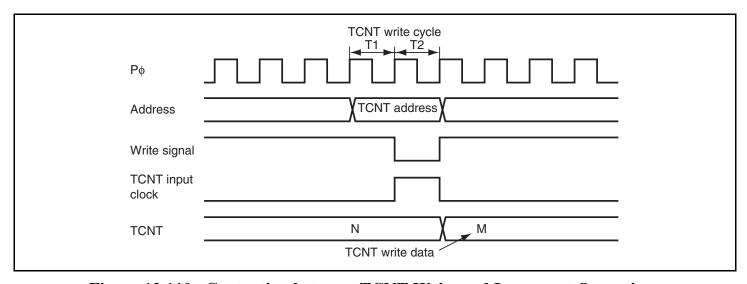

|      | 12.7.5  | Contention between TCNT Write and Increment Operations                 |     |

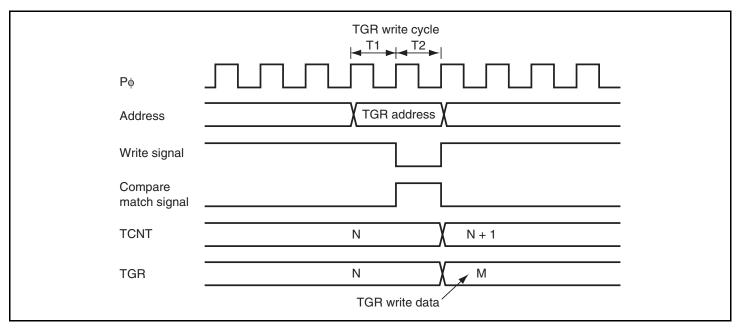

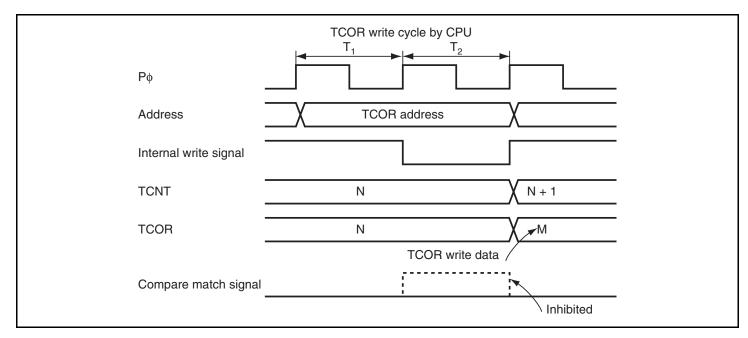

|      | 12.7.6  | Contention between TGR Write and Compare Match                         |     |

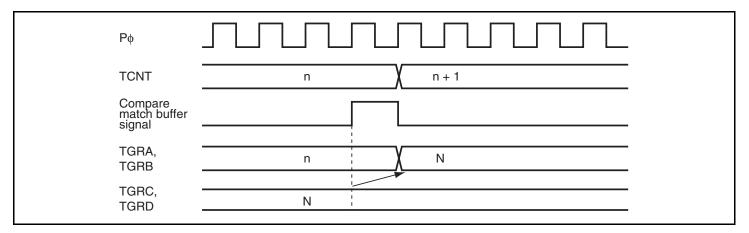

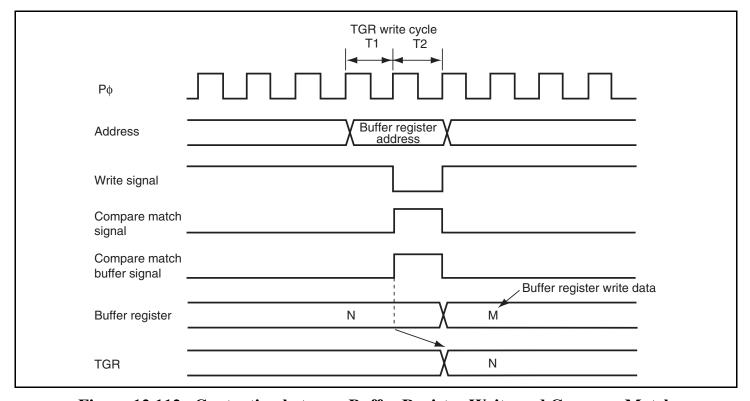

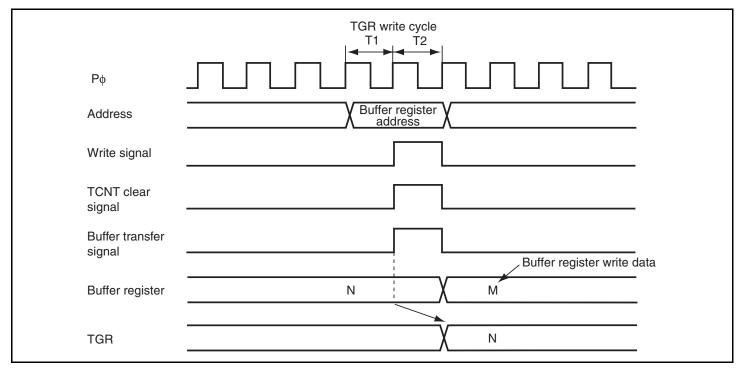

|      | 12.7.7  | Contention between Buffer Register Write and Compare Match             |     |

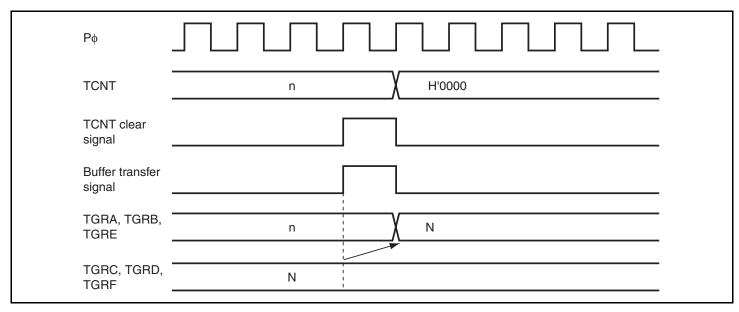

|      | 12.7.8  | Contention between Buffer Register Write and TCNT Clear                |     |

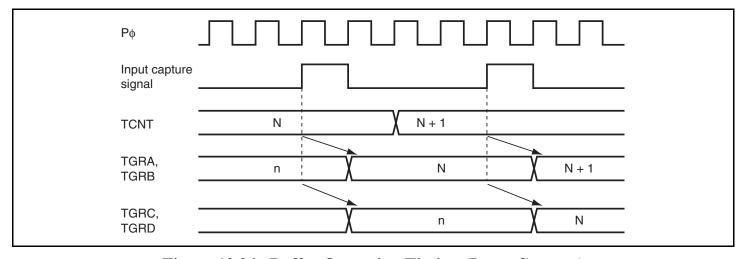

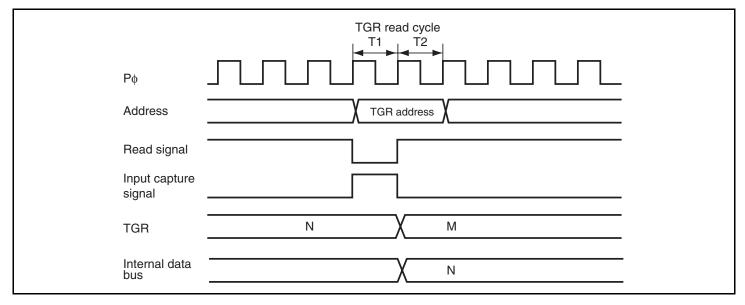

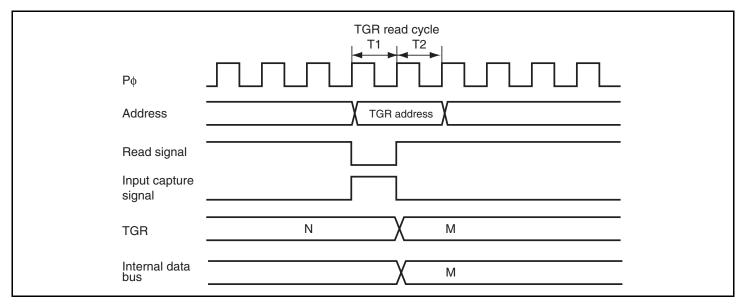

|      | 12.7.9  | Contention between TGR Read and Input Capture                          |     |

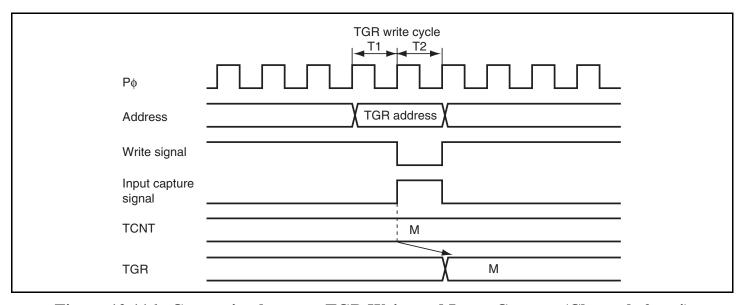

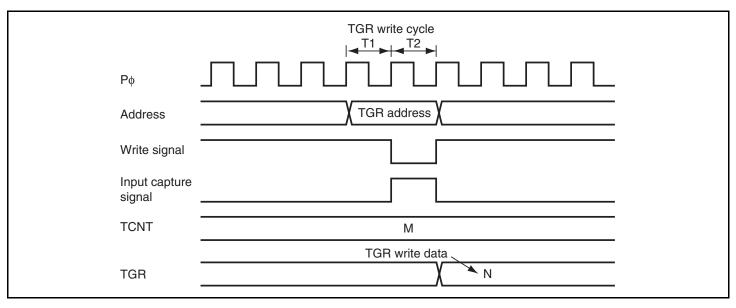

|      |         | Contention between TGR Write and Input Capture                         |     |

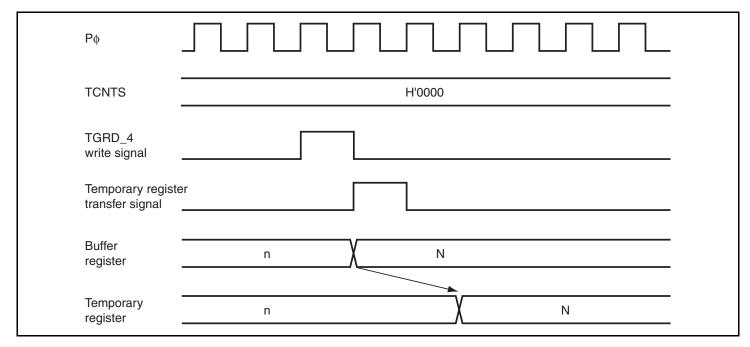

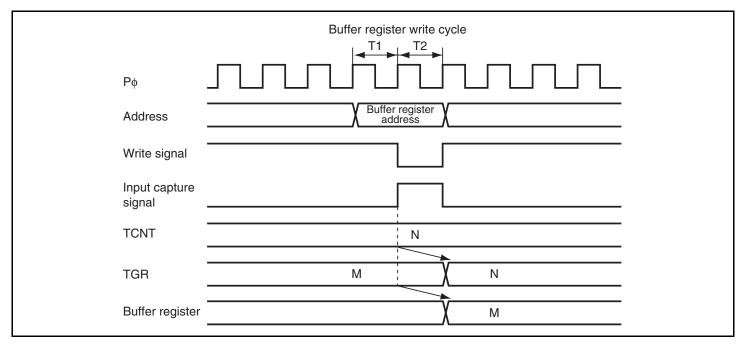

|      |         | Contention between Buffer Register Write and Input Capture             |     |

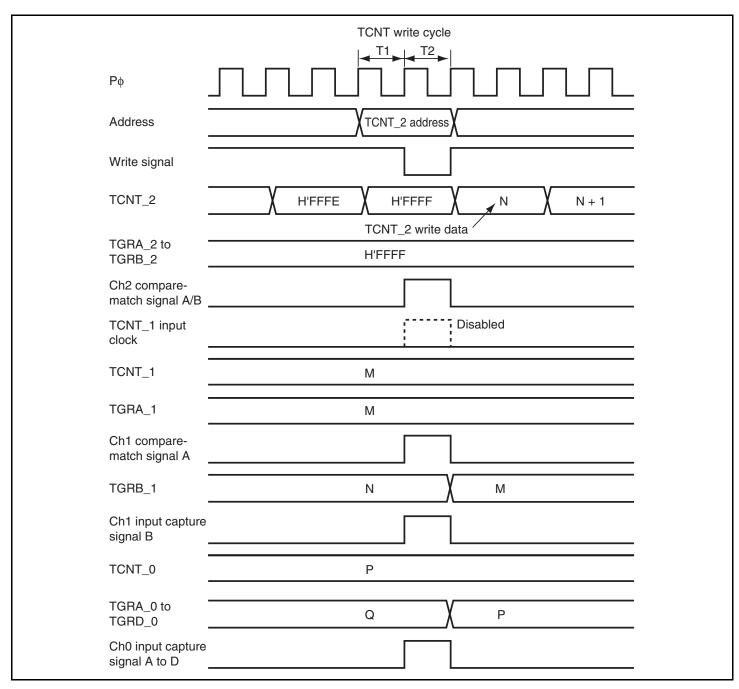

|      |         | 2 TCNT_2 Write and Overflow/Underflow Contention in Cascade Connection |     |

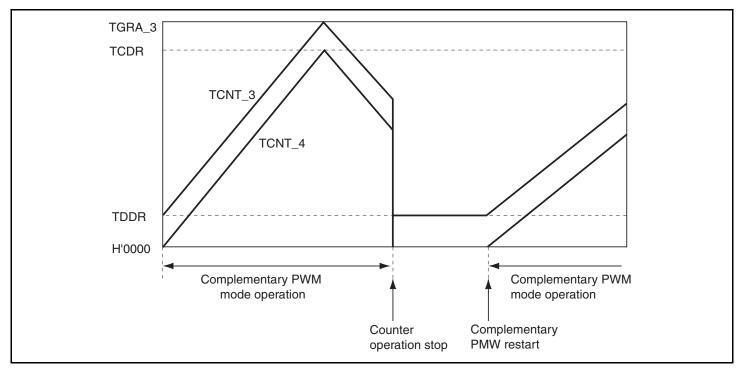

|      |         | Counter Value during Complementary PWM Mode Stop                       |     |

|      | 12.7.14 | Buffer Operation Setting in Complementary PWM Mode                     | 558 |

|       | 12.7.15 | Reset Sync PWM Mode Buffer Operation and Compare Match Flag        | 559 |

|-------|---------|--------------------------------------------------------------------|-----|

|       | 12.7.16 | Overflow Flags in Reset Synchronous PWM Mode                       | 560 |

|       | 12.7.17 | Contention between Overflow/Underflow and Counter Clearing         | 561 |

|       | 12.7.18 | Contention between TCNT Write and Overflow/Underflow               | 562 |

|       | 12.7.19 | Cautions on Transition from Normal Operation or                    |     |

|       |         | PWM Mode 1 to Reset-Synchronized PWM Mode                          | 562 |

|       | 12.7.20 | Output Level in Complementary PWM Mode and                         |     |

|       |         | Reset-Synchronized PWM Mode                                        | 563 |

|       | 12.7.21 | Interrupts in Module Standby Mode                                  | 563 |

|       | 12.7.22 | 2 Simultaneous Capture of TCNT_1 and TCNT_2 in Cascade Connection  | 563 |

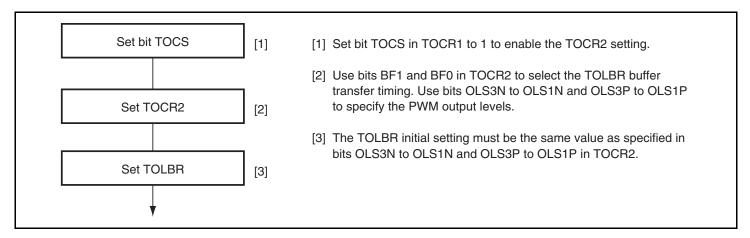

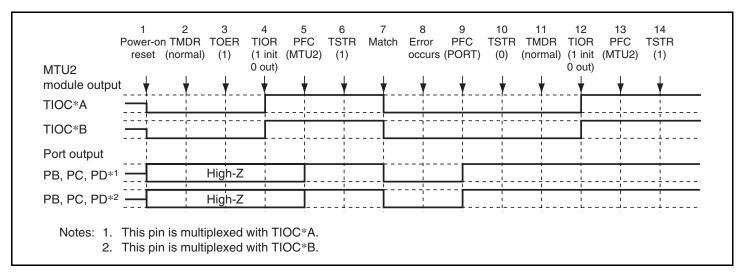

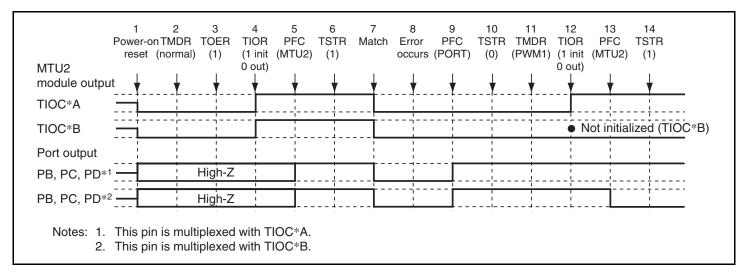

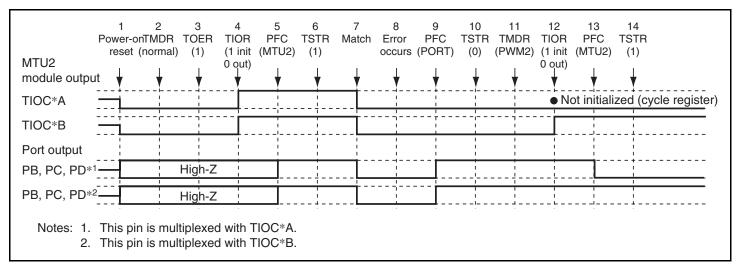

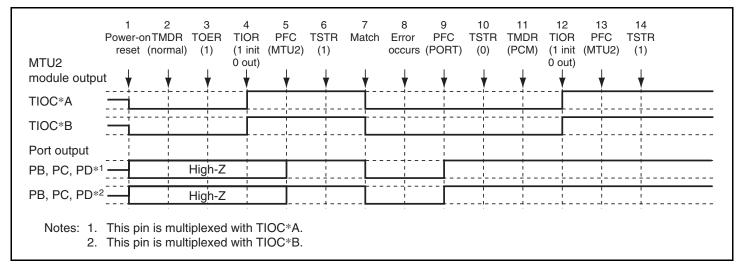

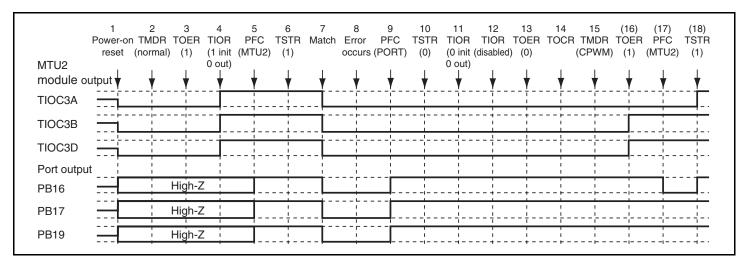

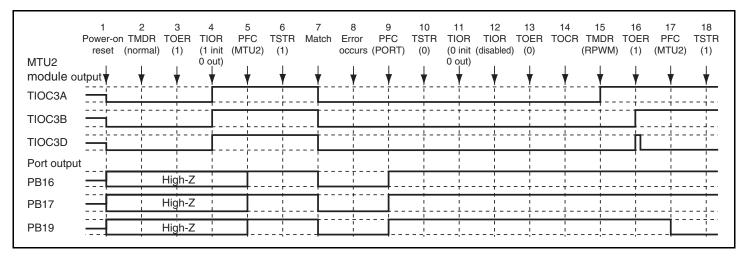

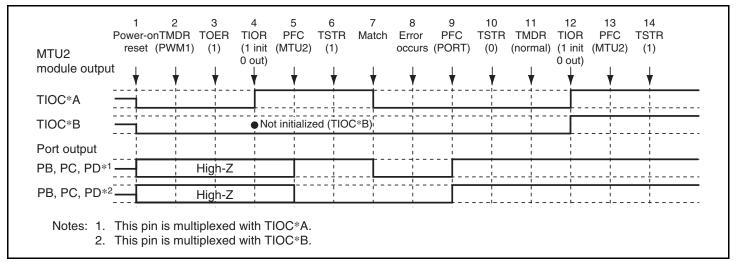

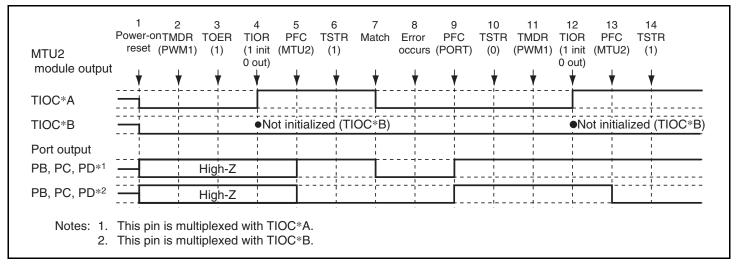

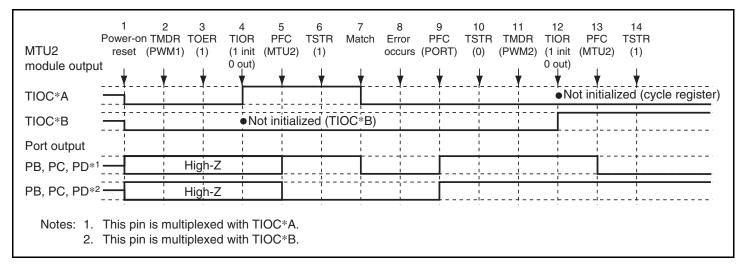

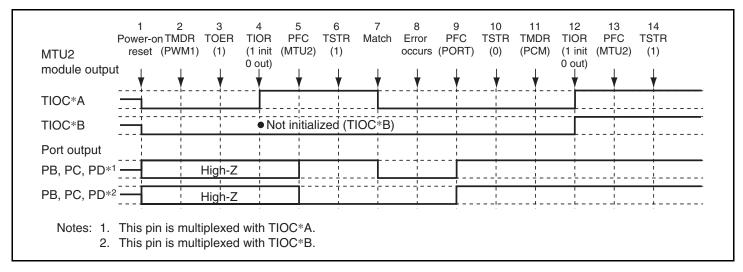

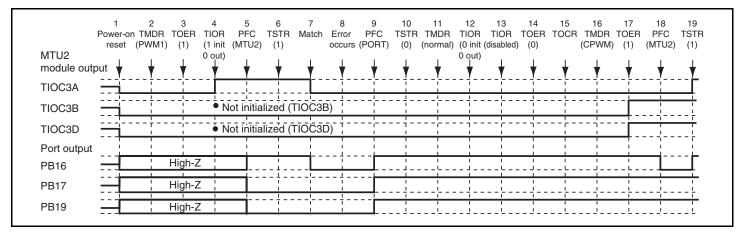

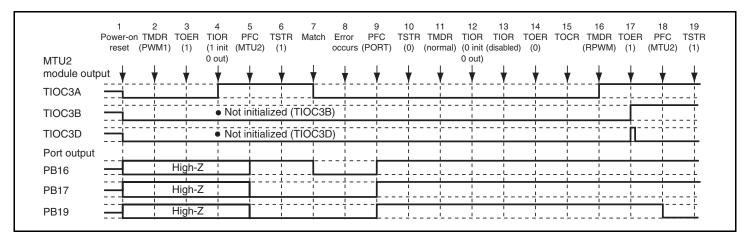

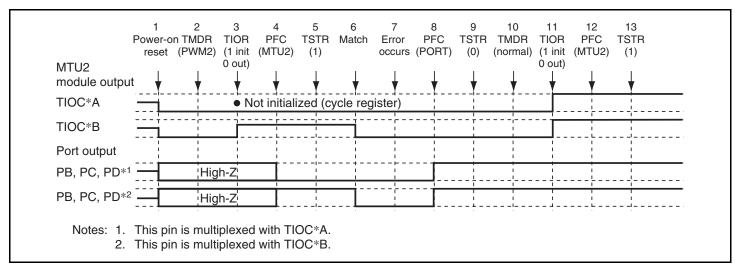

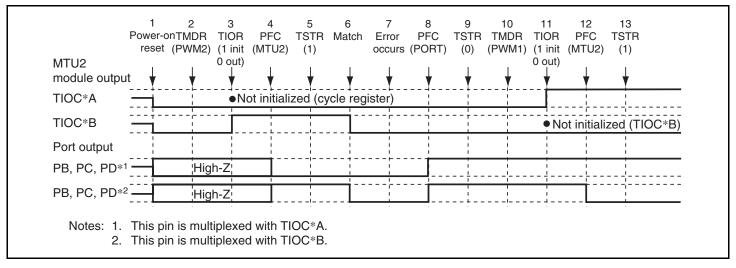

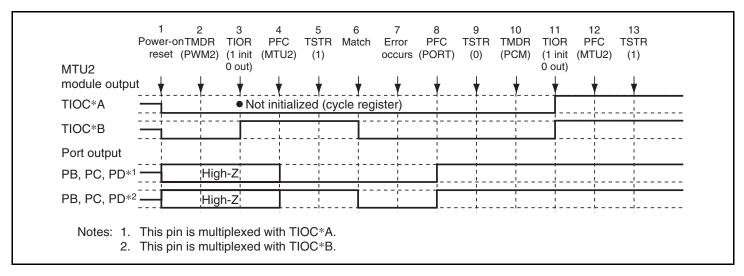

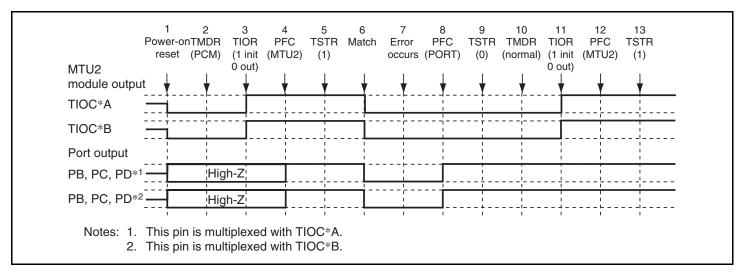

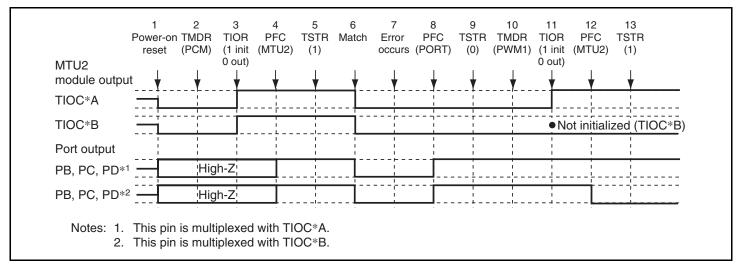

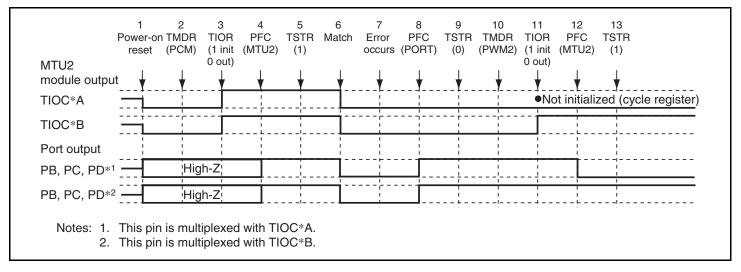

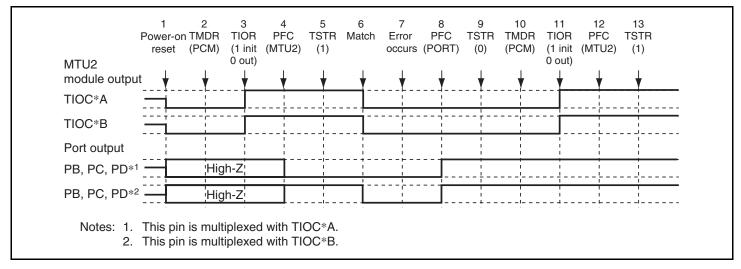

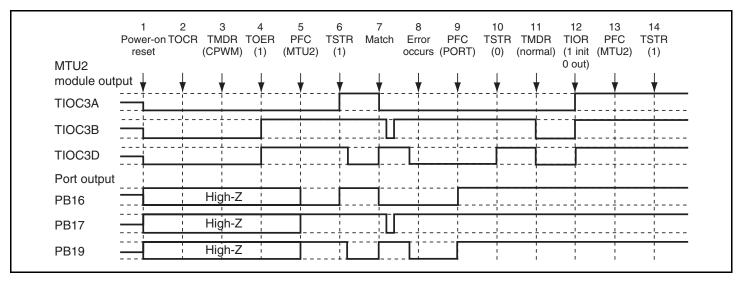

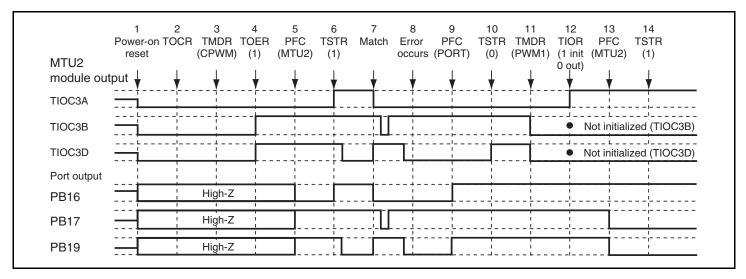

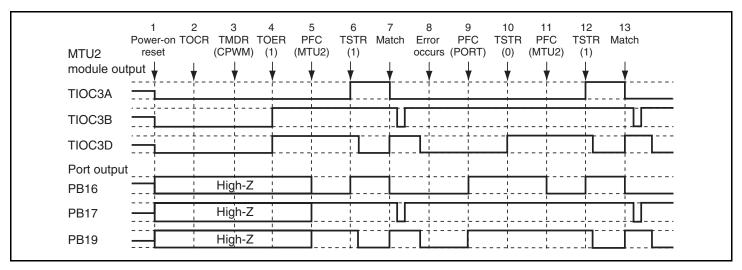

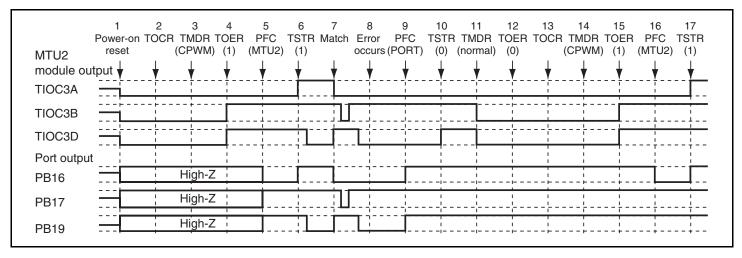

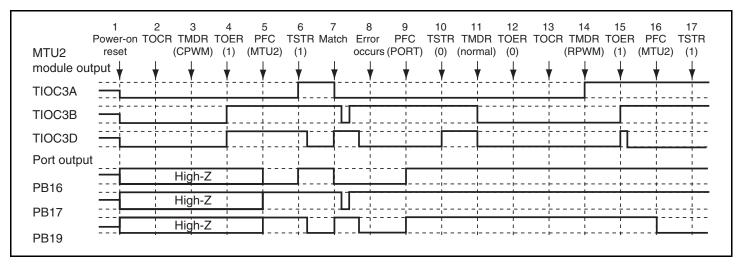

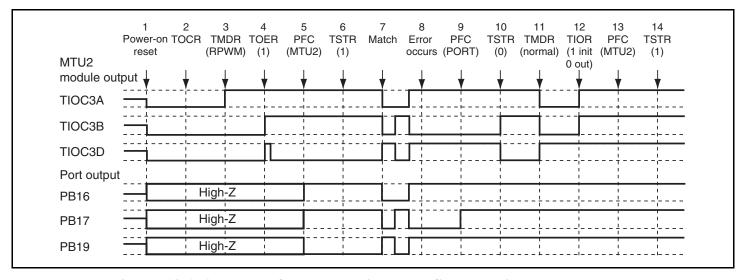

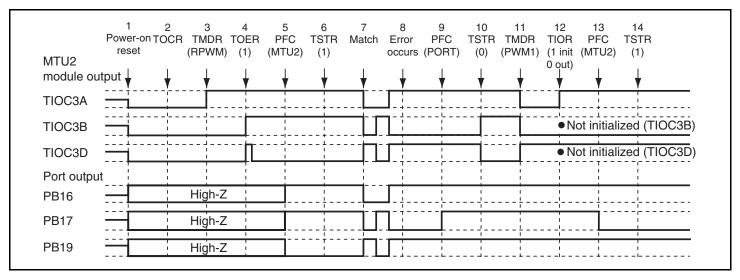

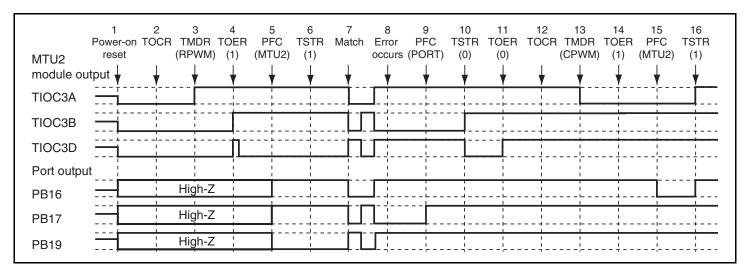

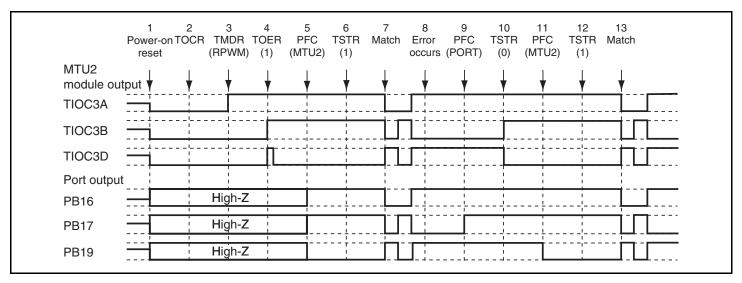

| 12.8  | MTU2    | Output Pin Initialization                                          | 564 |

|       | 12.8.1  | Operating Modes                                                    | 564 |

|       | 12.8.2  | Reset Start Operation                                              | 564 |

|       | 12.8.3  | Operation in Case of Re-Setting Due to Error During Operation, etc | 565 |

|       | 12.8.4  | Overview of Initialization Procedures and Mode Transitions in      |     |

|       |         | Case of Error during Operation, etc.                               | 566 |

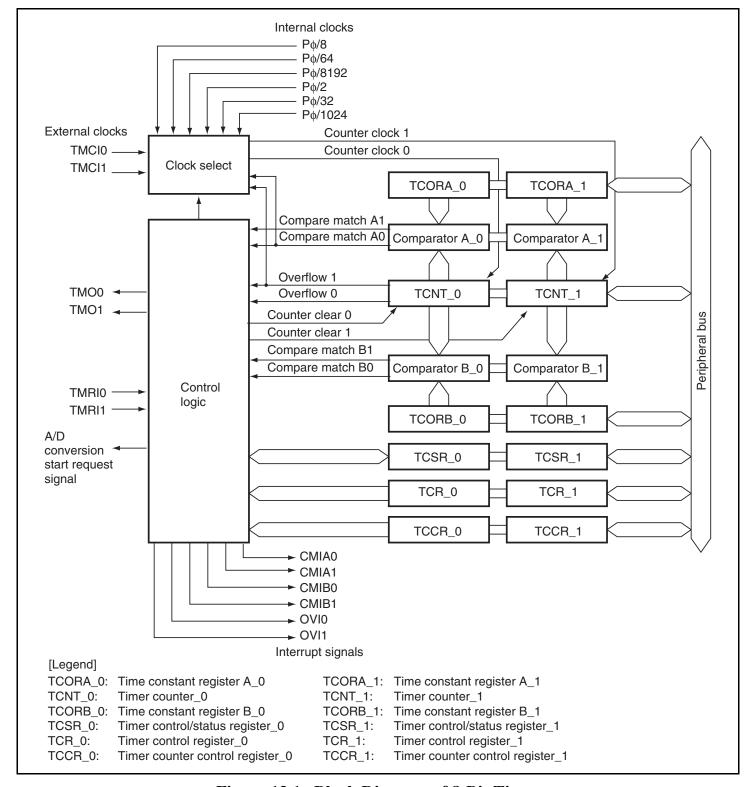

| Secti | ion 13  | 8-Bit Timers (TMR)                                                 | 597 |

| 13.1  |         | es                                                                 |     |

| 13.2  | Input/C | Output Pins                                                        | 599 |

| 13.3  | _       | er Descriptions                                                    |     |

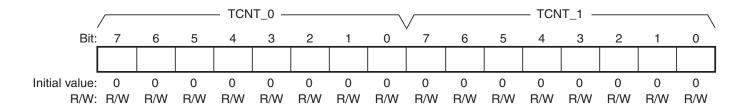

|       | 13.3.1  | Timer Counter (TCNT)                                               | 600 |

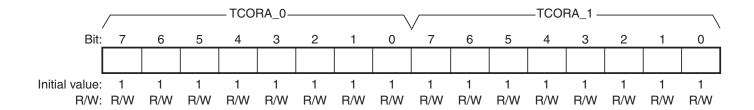

|       | 13.3.2  | Time Constant Register A (TCORA)                                   | 600 |

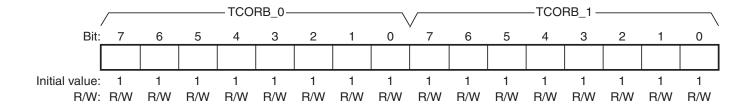

|       | 13.3.3  | Time Constant Register B (TCORB)                                   |     |

|       | 13.3.4  | Timer Control Register (TCR)                                       | 601 |

|       | 13.3.5  | Timer Counter Control Register (TCCR)                              | 603 |

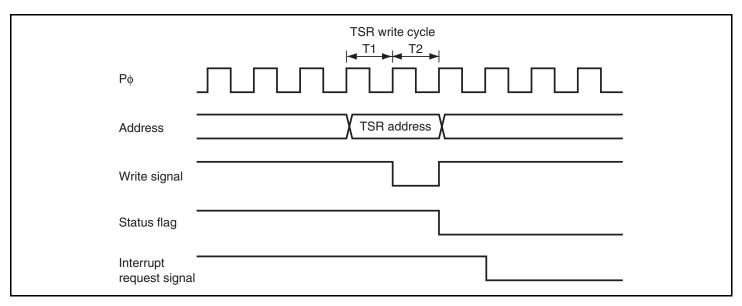

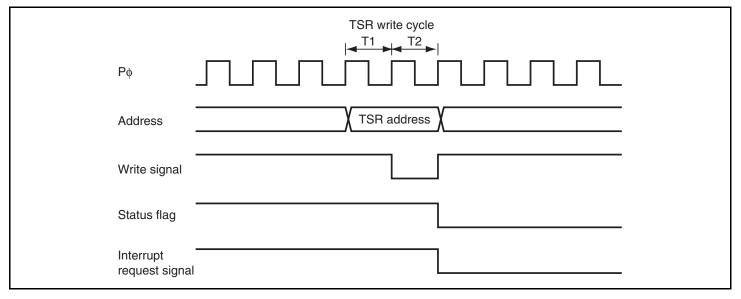

|       | 13.3.6  | Timer Control/Status Register (TCSR)                               | 605 |

| 13.4  |         | ion                                                                |     |

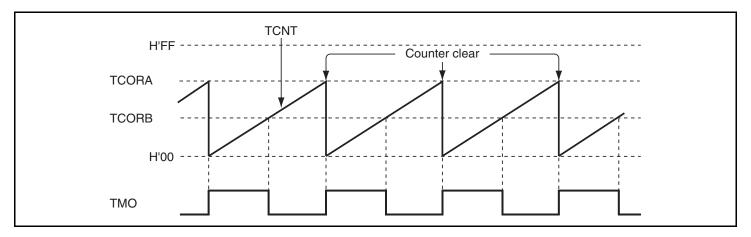

|       | 13.4.1  | Pulse Output                                                       | 609 |

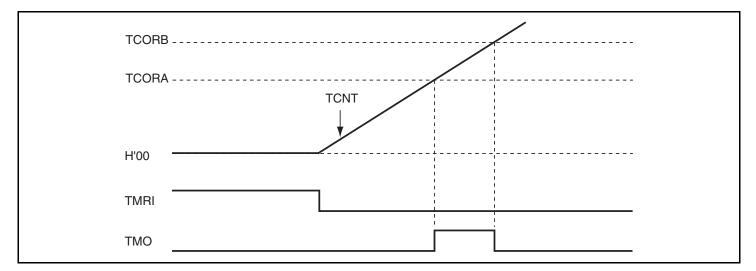

|       | 13.4.2  | Reset Input                                                        | 610 |

| 13.5  |         | ion Timing                                                         |     |

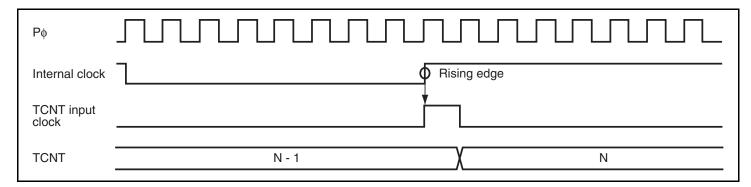

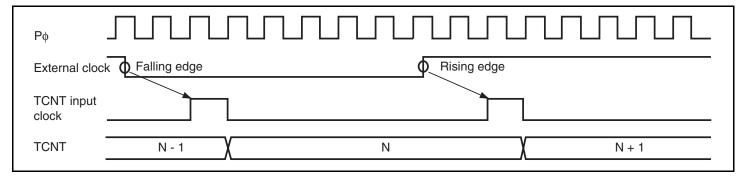

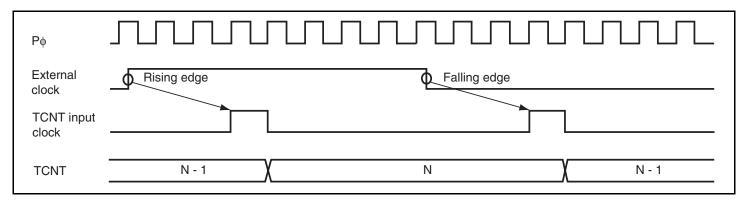

|       | _       | TCNT Count Timing                                                  |     |

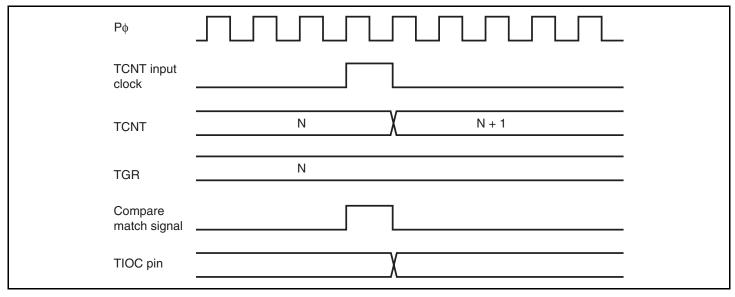

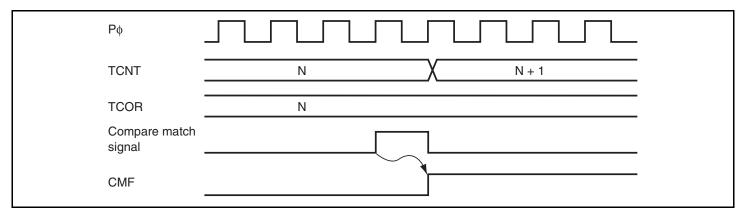

|       | 13.5.2  | Timing of CMFA and CMFB Setting at Compare Match                   |     |

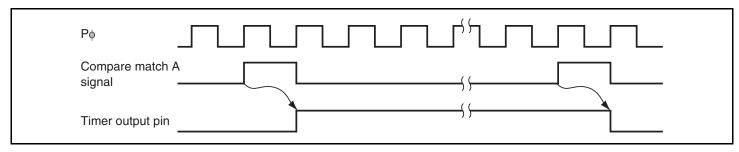

|       | 13.5.3  | Timing of Timer Output at Compare Match                            |     |

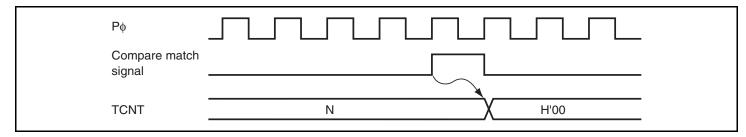

|       | 13.5.4  | Timing of Counter Clear by Compare Match                           |     |

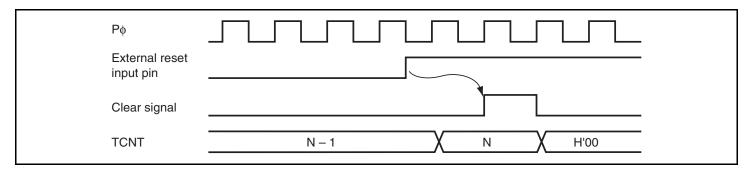

|       |         | Timing of TCNT External Reset                                      |     |

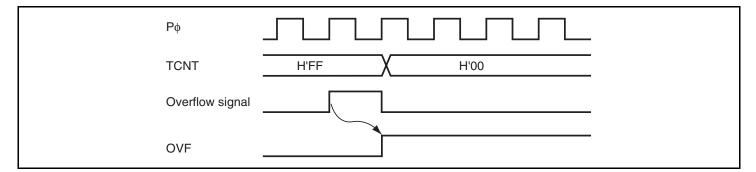

|       |         | Timing of Overflow Flag (OVF) Setting                              |     |

| 13.6  |         | ion with Cascaded Connection                                       |     |

|       | _       | 16-Bit Counter Mode                                                |     |

|       | 13.6.2  | Compare Match Count Mode                                           | 615 |

| 13.7 | Interrupt Sources |                                                 | 615 |

|------|-------------------|-------------------------------------------------|-----|

|      | 13.7.1            | Interrupt Sources                               | 615 |

|      | 13.7.2            | A/D Converter Activation                        | 616 |

| 13.8 | Usage             | Notes                                           | 616 |

|      | 13.8.1            | Notes on Setting Cycle                          | 616 |

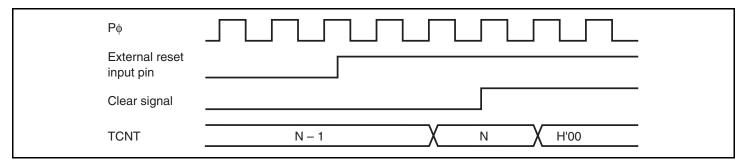

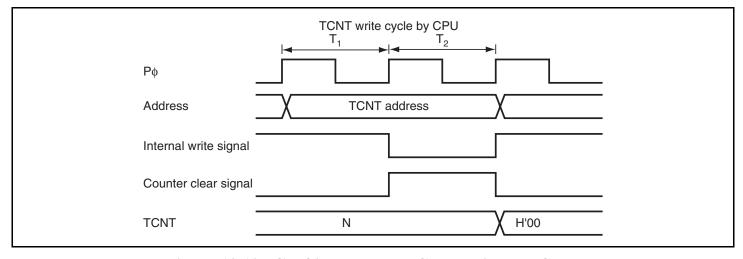

|      | 13.8.2            | Conflict between TCNT Write and Clear           | 616 |

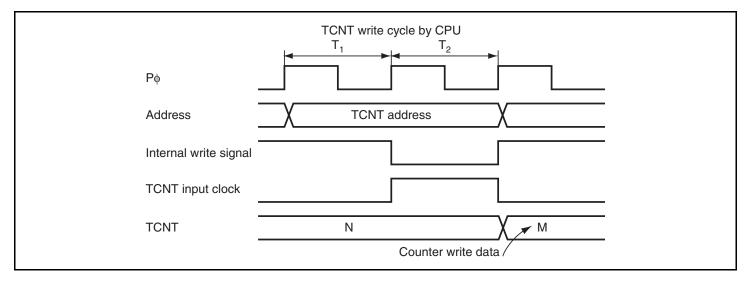

|      | 13.8.3            | Conflict between TCNT Write and Increment       | 617 |

|      | 13.8.4            | Conflict between TCOR Write and Compare Match   | 617 |

|      | 13.8.5            | Conflict between Compare Matches A and B        | 618 |

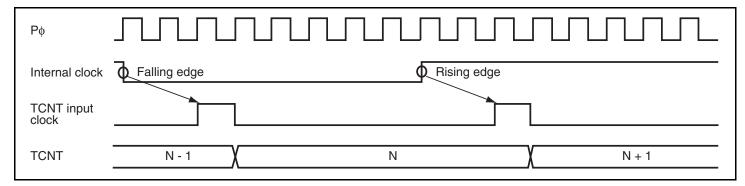

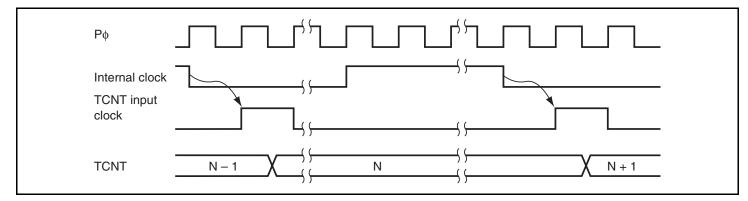

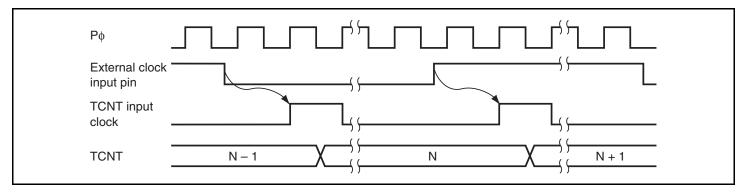

|      | 13.8.6            | Switching of Internal Clocks and TCNT Operation | 618 |

|      | 13.8.7            | Mode Setting with Cascaded Connection           | 620 |

|      | 13.8.8            | Module Standby Setting                          | 620 |

|      | 13.8.9            | Interrupts in Module Standby Mode               | 620 |

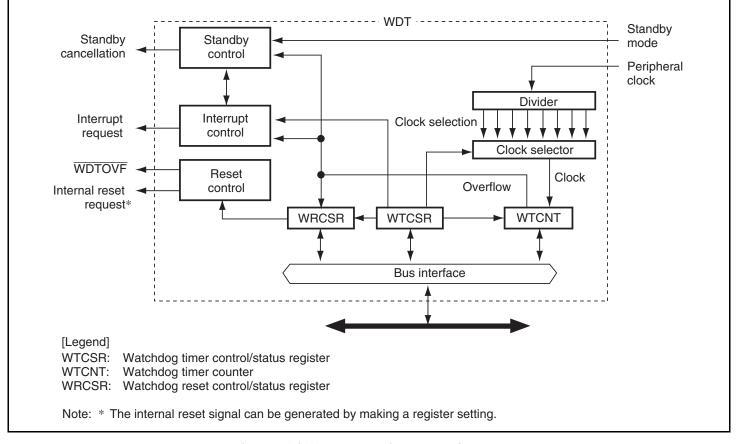

| Sect | ion 14            | Watchdog Timer (WDT)                            | 621 |

| 14.1 |                   | es                                              |     |

| 14.2 | Input/C           | Output Pin                                      | 622 |

| 14.3 |                   |                                                 |     |

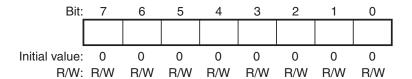

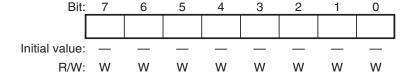

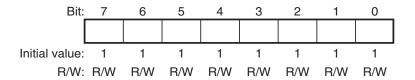

|      | 14.3.1            | Watchdog Timer Counter (WTCNT)                  | 623 |

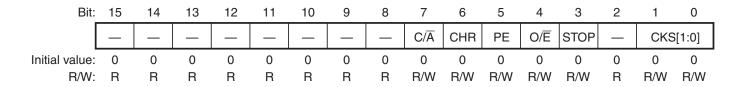

|      | 14.3.2            | Watchdog Timer Control/Status Register (WTCSR)  | 624 |

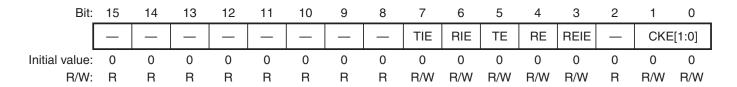

|      | 14.3.3            | Watchdog Reset Control/Status Register (WRCSR)  | 626 |

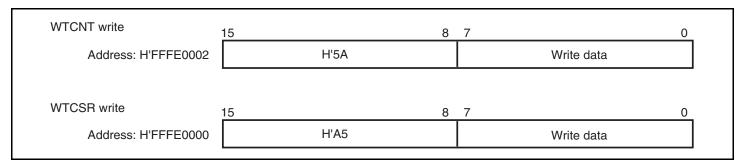

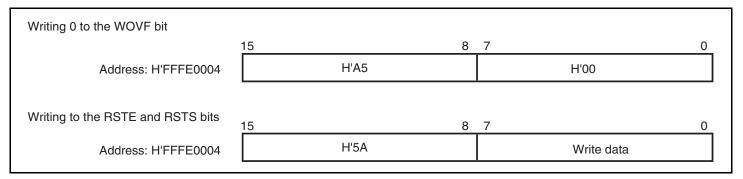

|      | 14.3.4            | Notes on Register Access                        | 627 |

| 14.4 | WDT U             | Usage                                           | 629 |

|      | 14.4.1            | Canceling Software Standby Mode                 | 629 |

|      | 14.4.2            | Changing the Frequency                          | 629 |

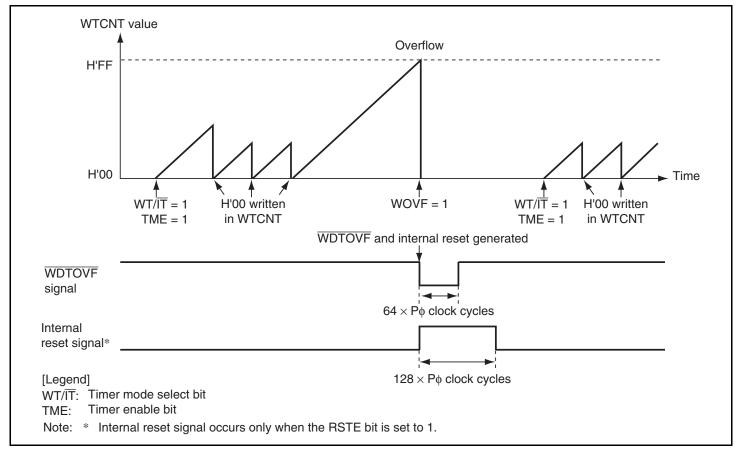

|      |                   | Using Watchdog Timer Mode                       |     |

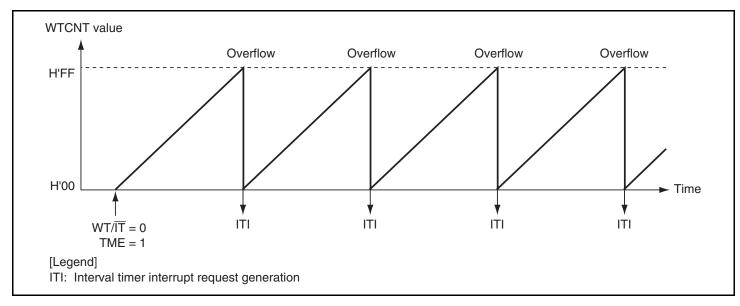

|      | 14.4.4            | Using Interval Timer Mode                       | 631 |

| 14.5 |                   | Notes                                           |     |

|      | _                 | Timer Variation                                 |     |

|      | 14.5.2            | Prohibition against Setting H'FF to WTCNT       | 632 |

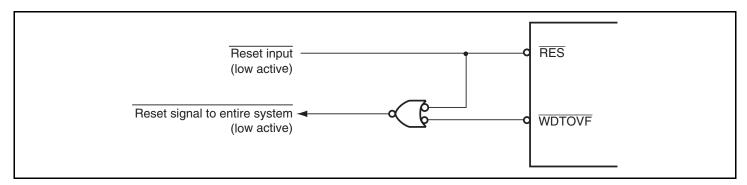

|      |                   | System Reset by WDTOVF Signal                   |     |

|      |                   | Manual Reset in Watchdog Timer Mode             |     |

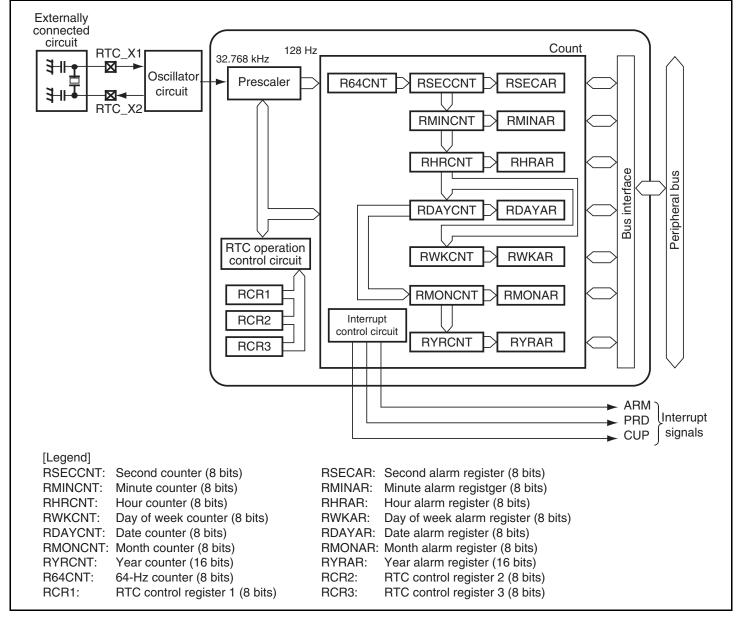

| Sect | ion 15            | Realtime Clock (RTC)                            | 635 |

| 15.1 |                   | es                                              |     |

| 15.2 |                   | Output Pin                                      |     |

| 15.3 | _                 | er Descriptions                                 |     |

| -    | _                 | 64-Hz Counter (R64CNT)                          |     |

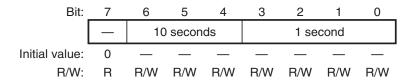

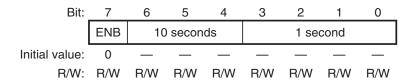

|      |                   | Second Counter (RSECCNT)                        |     |

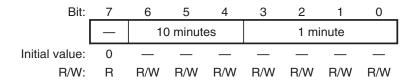

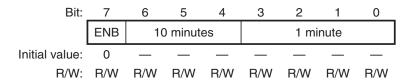

|      |                   | Minute Counter (RMINCNT)                        |     |

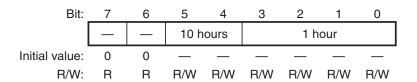

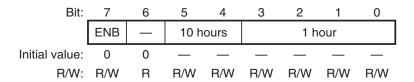

|       | 15.3.4  | Hour Counter (RHRCNT)                                   | 641 |

|-------|---------|---------------------------------------------------------|-----|

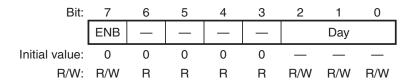

|       | 15.3.5  | Day of Week Counter (RWKCNT)                            | 642 |

|       | 15.3.6  | Date Counter (RDAYCNT)                                  | 643 |

|       | 15.3.7  | Month Counter (RMONCNT)                                 | 644 |

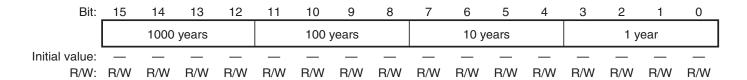

|       | 15.3.8  | Year Counter (RYRCNT)                                   | 645 |

|       | 15.3.9  | Second Alarm Register (RSECAR)                          | 646 |

|       | 15.3.10 | ) Minute Alarm Register (RMINAR)                        | 647 |

|       | 15.3.11 | Hour Alarm Register (RHRAR)                             | 648 |

|       | 15.3.12 | 2 Day of Week Alarm Register (RWKAR)                    | 649 |

|       | 15.3.13 | B Date Alarm Register (RDAYAR)                          | 650 |

|       | 15.3.14 | Month Alarm Register (RMONAR)                           | 651 |

|       | 15.3.15 | 5 Year Alarm Register (RYRAR)                           | 652 |

|       | 15.3.16 | 6 RTC Control Register 1 (RCR1)                         | 653 |

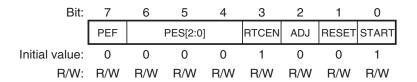

|       | 15.3.17 | 7 RTC Control Register 2 (RCR2)                         | 655 |

|       | 15.3.18 | RTC Control Register 3 (RCR3)                           | 657 |

| 15.4  | Operat  | ion                                                     | 658 |

|       | 15.4.1  | Initial Settings of Registers after Power-On            | 658 |

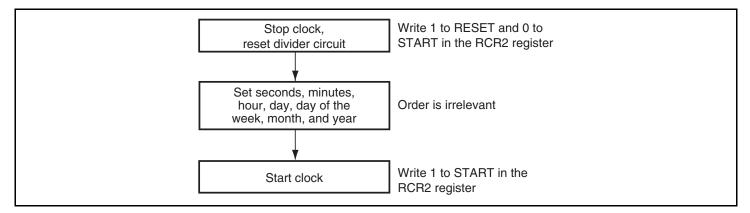

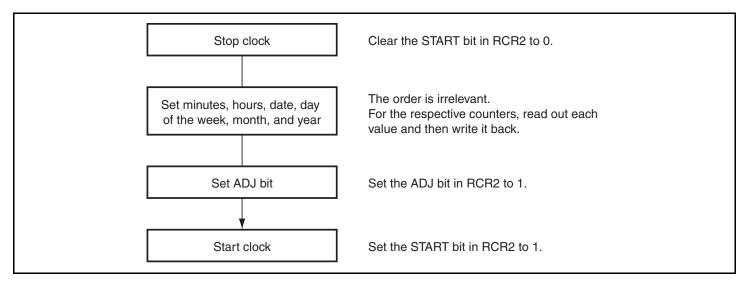

|       | 15.4.2  | Setting Time                                            | 658 |

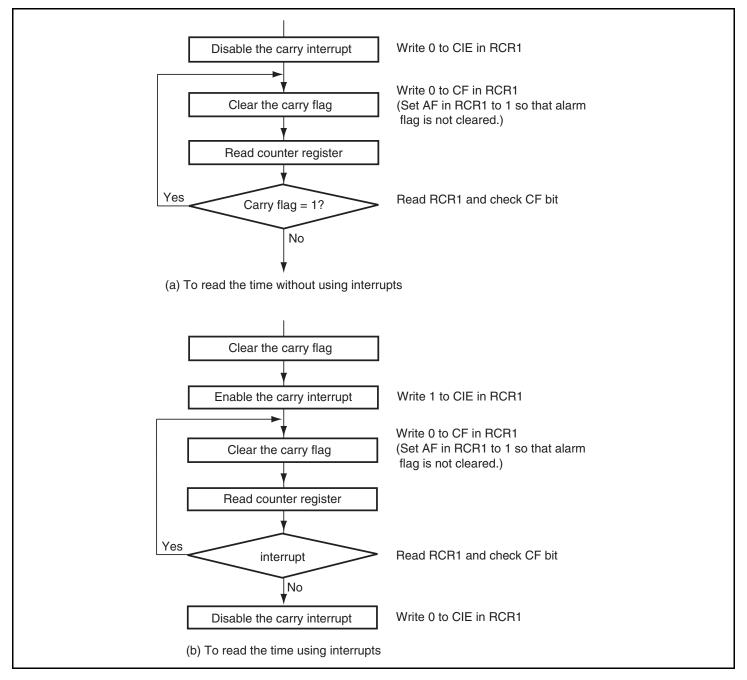

|       | 15.4.3  | Reading Time                                            | 659 |

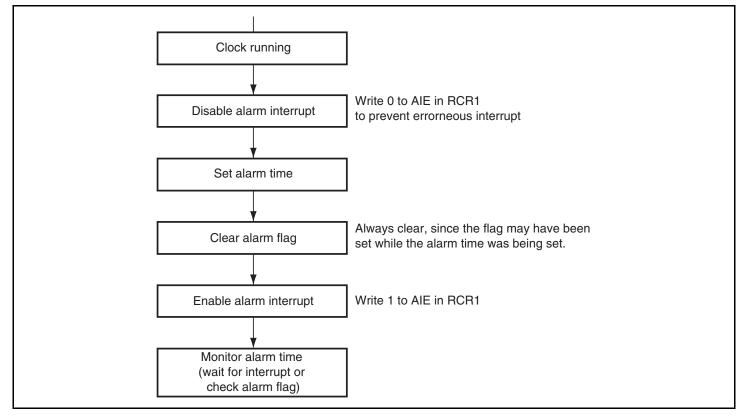

|       | 15.4.4  | Alarm Function                                          | 660 |

| 15.5  | Usage   | Notes                                                   | 661 |

|       | 15.5.1  | Register Writing during RTC Count                       | 661 |

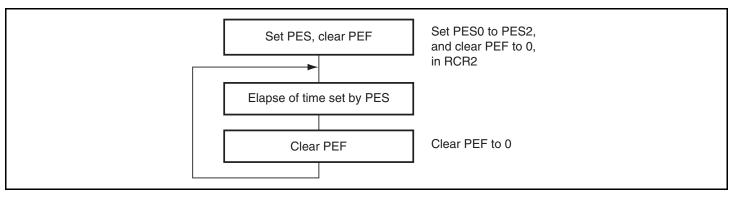

|       | 15.5.2  | Use of Realtime Clock (RTC) Periodic Interrupts         | 661 |

|       | 15.5.3  | Transition to Standby Mode after Setting Register       | 662 |

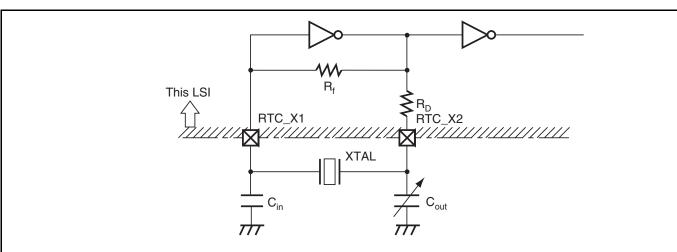

|       | 15.5.4  | Crystal Oscillator Circuit for RTC                      | 662 |

|       | 15.5.5  | Procedure for Setting the 30-Second Adjustment Function | 663 |

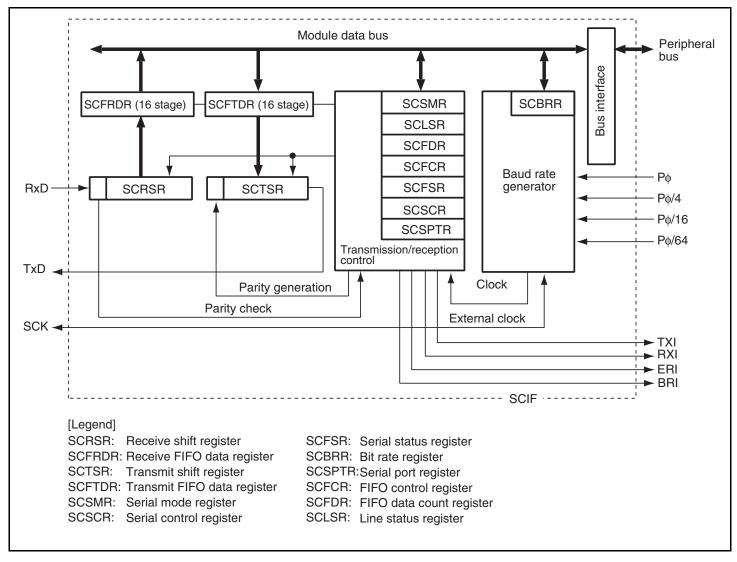

| Secti | ion 16  | Serial Communication Interface with FIFO (SCIF)         | 665 |

| 16.1  | Feature | es                                                      | 665 |

| 16.2  | Input/C | Output Pins                                             | 667 |

| 16.3  | Registe | er Descriptions                                         | 667 |

|       | 16.3.1  | Receive Shift Register (SCRSR)                          | 671 |

|       | 16.3.2  | Receive FIFO Data Register (SCFRDR)                     | 671 |

|       | 16.3.3  | Transmit Shift Register (SCTSR)                         | 672 |

|       | 16.3.4  | Transmit FIFO Data Register (SCFTDR)                    | 672 |

|       | 16.3.5  | Serial Mode Register (SCSMR)                            | 673 |

|       | 16.3.6  | Serial Control Register (SCSCR)                         | 676 |

|       | 16.3.7  | Serial Status Register (SCFSR)                          | 680 |

|       | 16.3.8  | Bit Rate Register (SCBRR)                               | 688 |

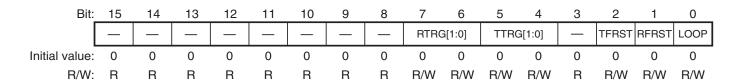

|       | 16.3.9  | FIFO Control Register (SCFCR)                           | 696 |

|      | 16.3.10 | FIFO Data Count Register (SCFDR)                                    | 698 |

|------|---------|---------------------------------------------------------------------|-----|

|      | 16.3.11 | Serial Port Register (SCSPTR)                                       | 699 |

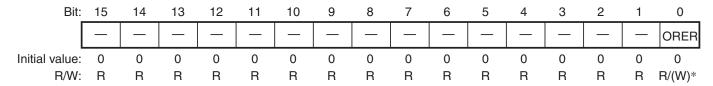

|      | 16.3.12 | 2 Line Status Register (SCLSR)                                      | 701 |

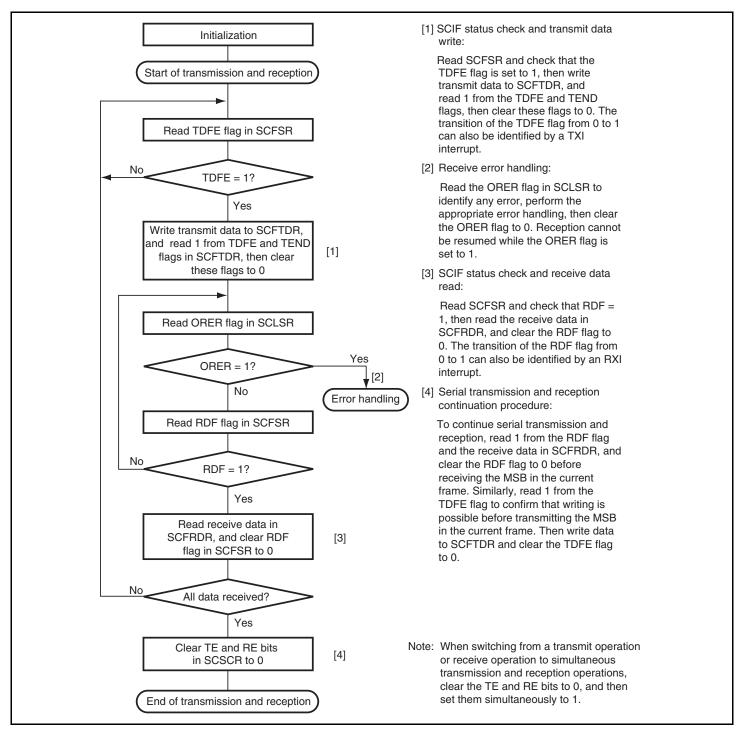

| 16.4 | Operat  | ion                                                                 | 702 |

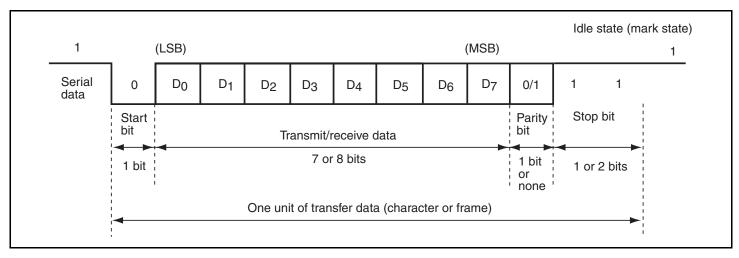

|      | 16.4.1  | Overview                                                            | 702 |

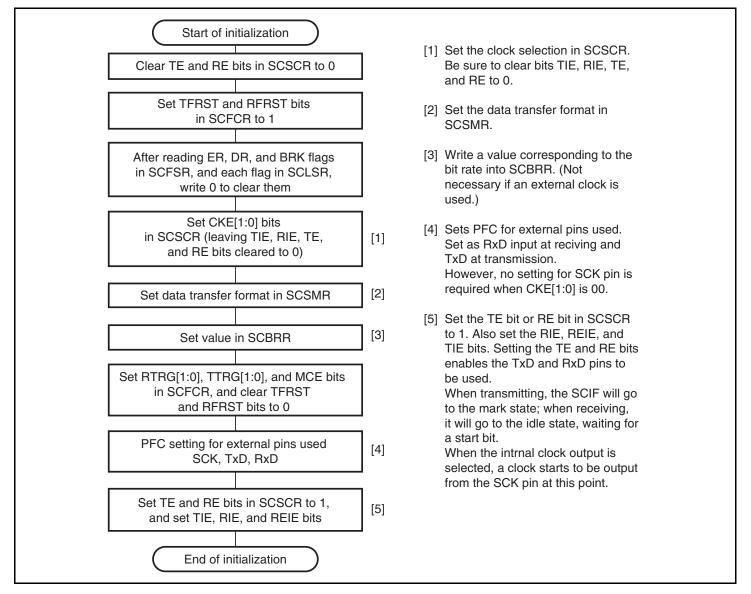

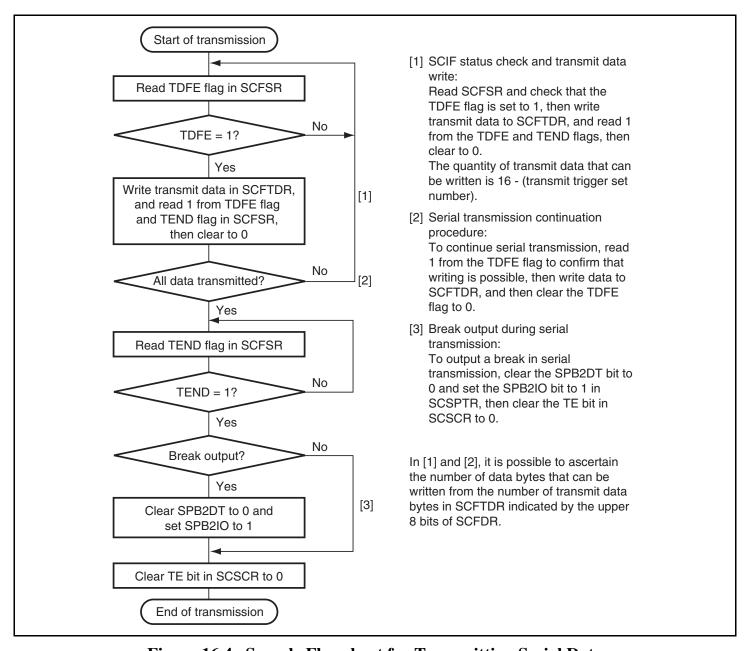

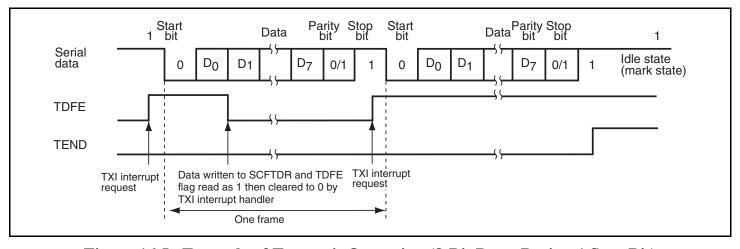

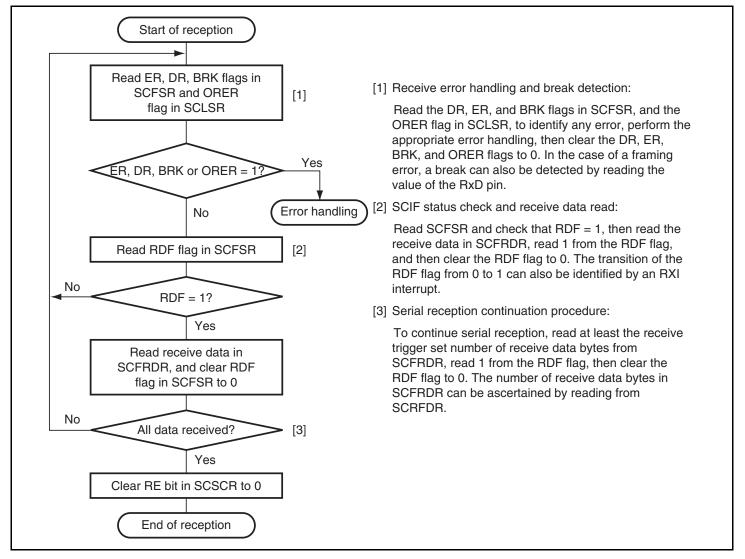

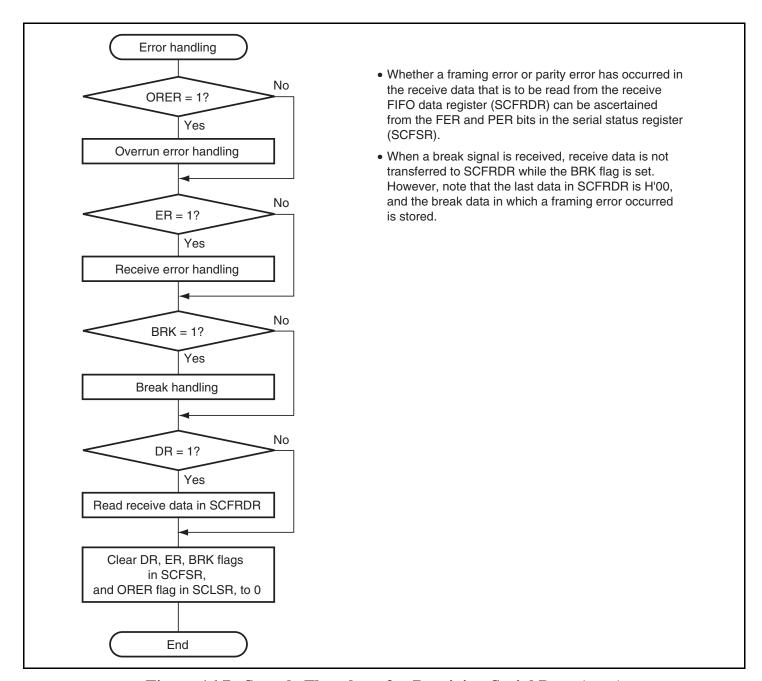

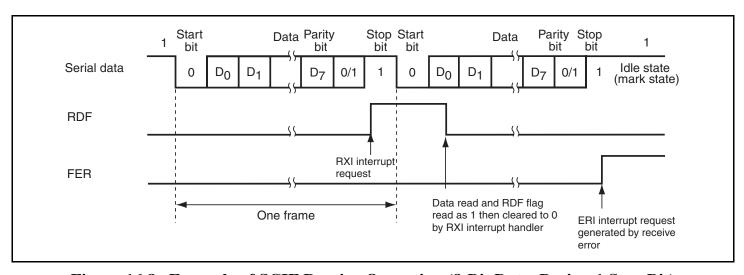

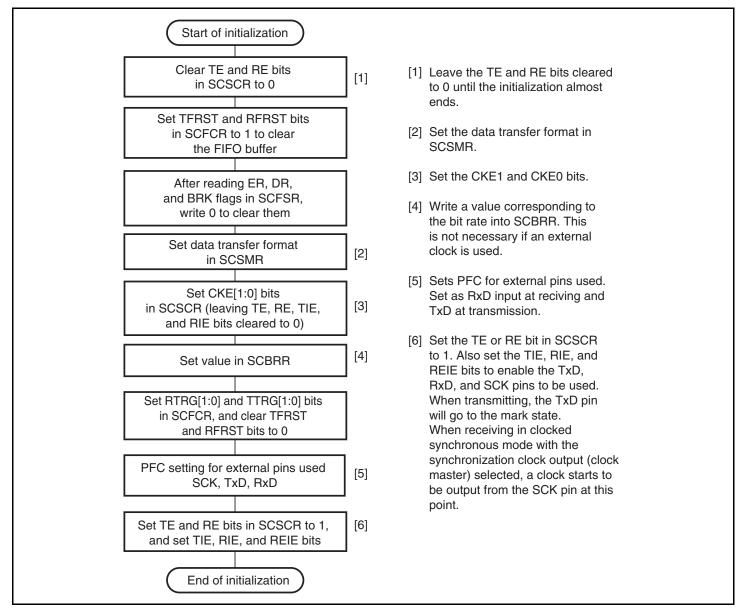

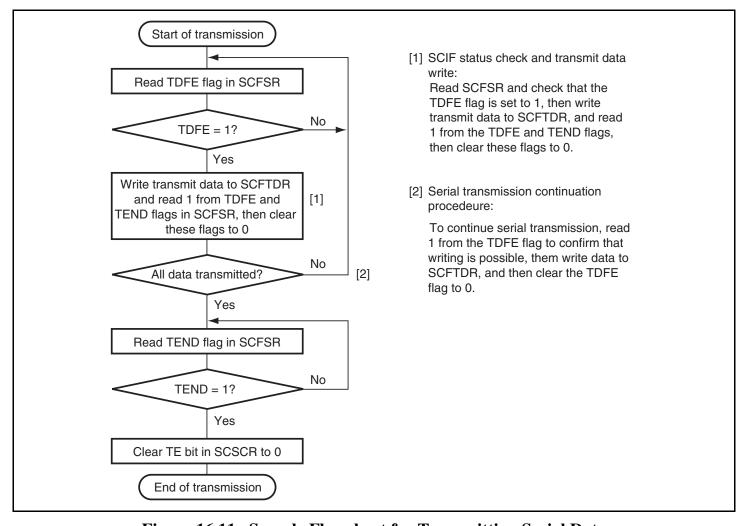

|      | 16.4.2  | Operation in Asynchronous Mode                                      | 704 |

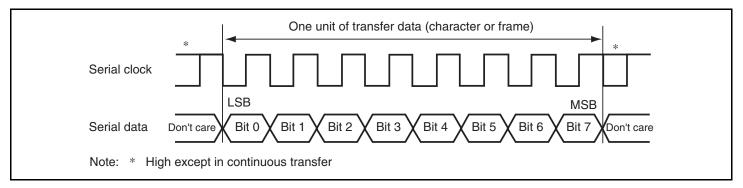

|      | 16.4.3  | Operation in Clocked Synchronous Mode                               | 713 |

| 16.5 | SCIF I  | nterrupts                                                           | 721 |

| 16.6 | Usage   | Notes                                                               | 722 |

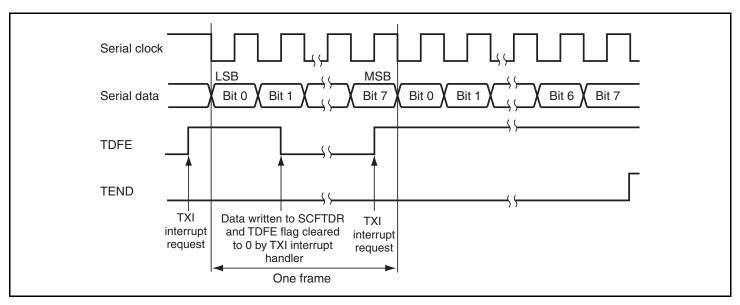

|      | 16.6.1  | SCFTDR Writing and TDFE Flag                                        | 722 |

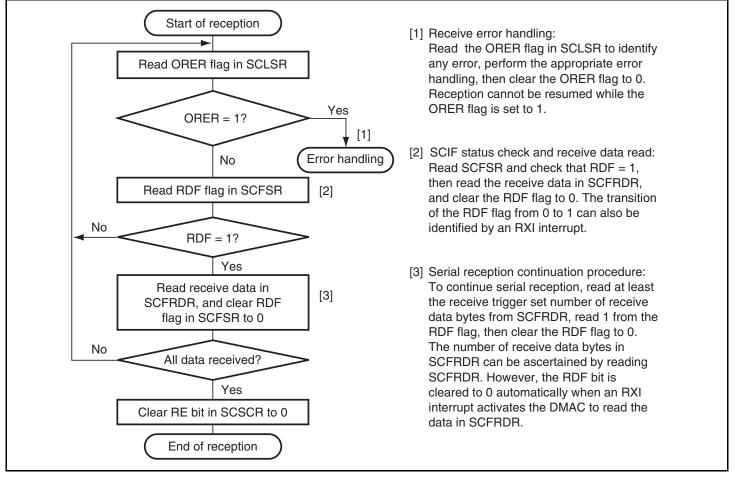

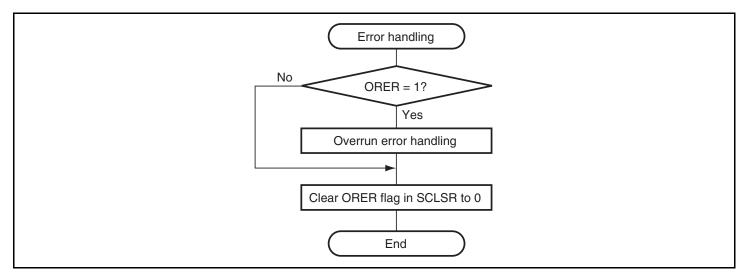

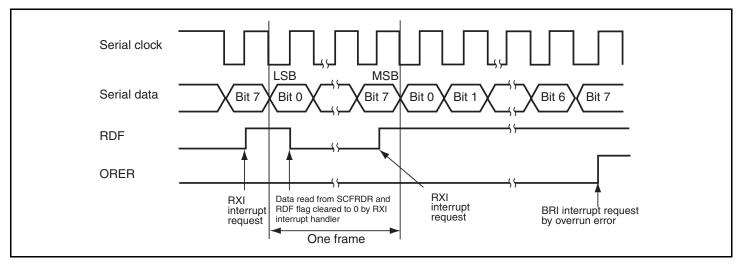

|      | 16.6.2  | SCFRDR Reading and RDF Flag                                         | 722 |

|      | 16.6.3  | Restriction on DMAC Usage                                           | 723 |

|      | 16.6.4  | Break Detection and Processing                                      | 723 |

|      | 16.6.5  | Sending a Break Signal                                              | 723 |

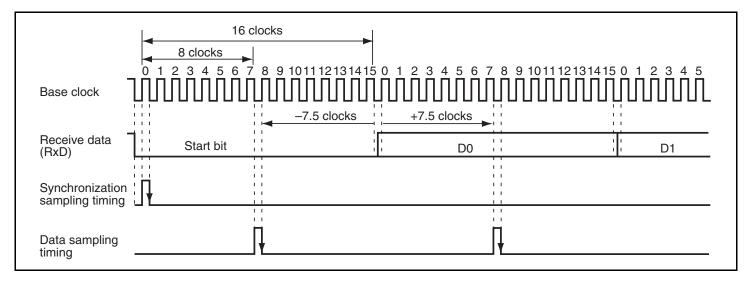

|      | 16.6.6  | Receive Data Sampling Timing and Receive Margin (Asynchronous Mode) | 724 |

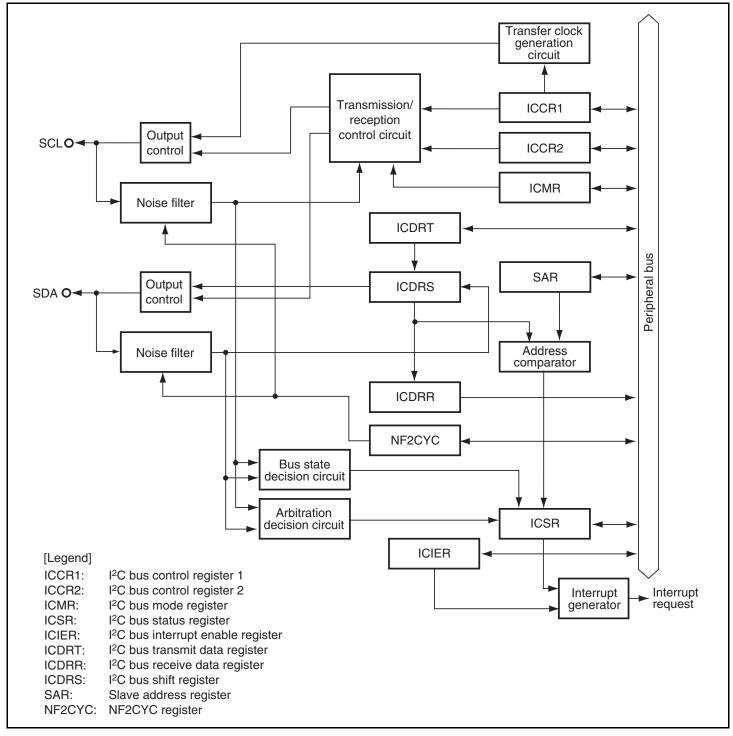

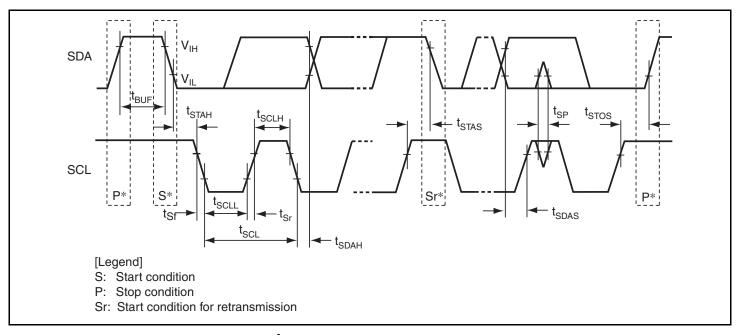

| Sect | ion 17  | I <sup>2</sup> C Bus Interface 3 (IIC3)                             | 725 |

| 17.1 | Feature | es                                                                  | 725 |

| 17.2 | Input/C | Output Pins                                                         | 727 |

| 17.3 | Registe | er Descriptions                                                     | 728 |

|      | 17.3.1  | I <sup>2</sup> C Bus Control Register 1 (ICCR1)                     | 729 |

|      | 17.3.2  | I <sup>2</sup> C Bus Control Register 2 (ICCR2)                     | 732 |

|      | 17.3.3  | I <sup>2</sup> C Bus Mode Register (ICMR)                           | 734 |

|      | 17.3.4  | I <sup>2</sup> C Bus Interrupt Enable Register (ICIER)              | 736 |

|      | 17.3.5  | I <sup>2</sup> C Bus Status Register (ICSR)                         | 738 |

|      | 17.3.6  | Slave Address Register (SAR)                                        | 741 |

|      | 17.3.7  | I <sup>2</sup> C Bus Transmit Data Register (ICDRT)                 | 742 |

|      | 17.3.8  | I <sup>2</sup> C Bus Receive Data Register (ICDRR)                  | 742 |

|      | 17.3.9  | I <sup>2</sup> C Bus Shift Register (ICDRS)                         | 742 |

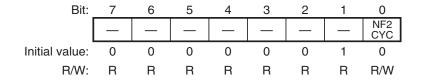

|      | 17.3.10 | NF2CYC Register (NF2CYC)                                            | 743 |

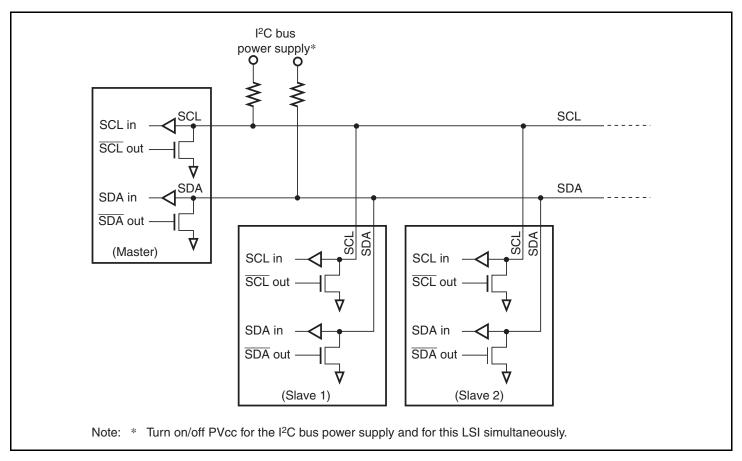

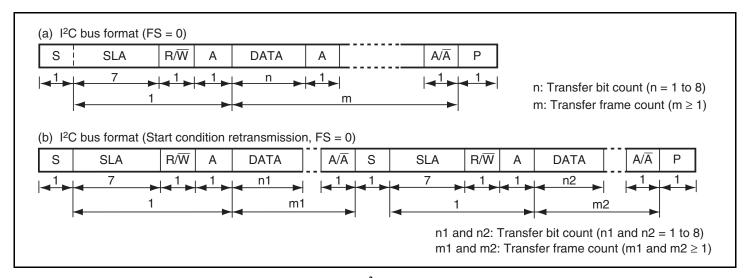

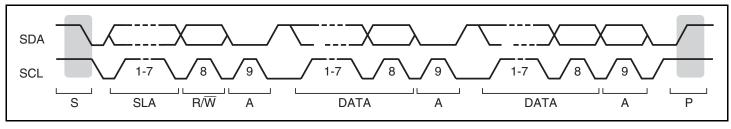

| 17.4 | Operat  | ion                                                                 | 744 |

|      | 17.4.1  | I <sup>2</sup> C Bus Format                                         | 744 |

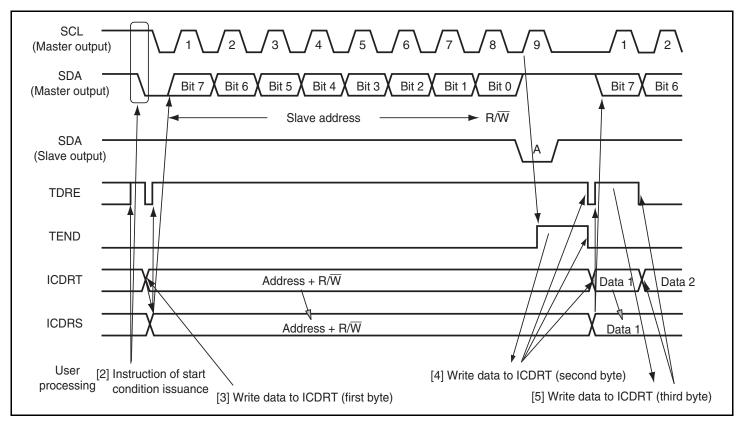

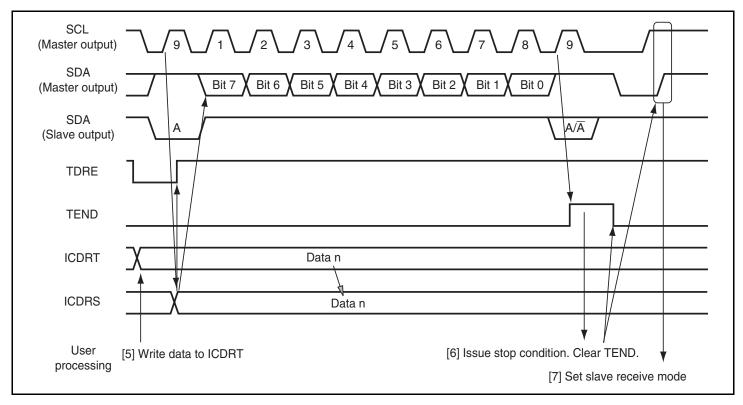

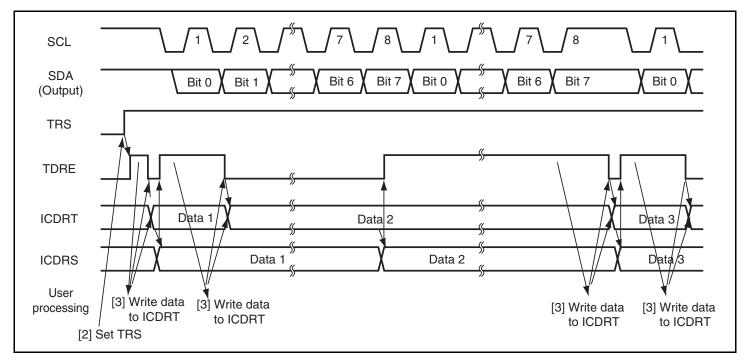

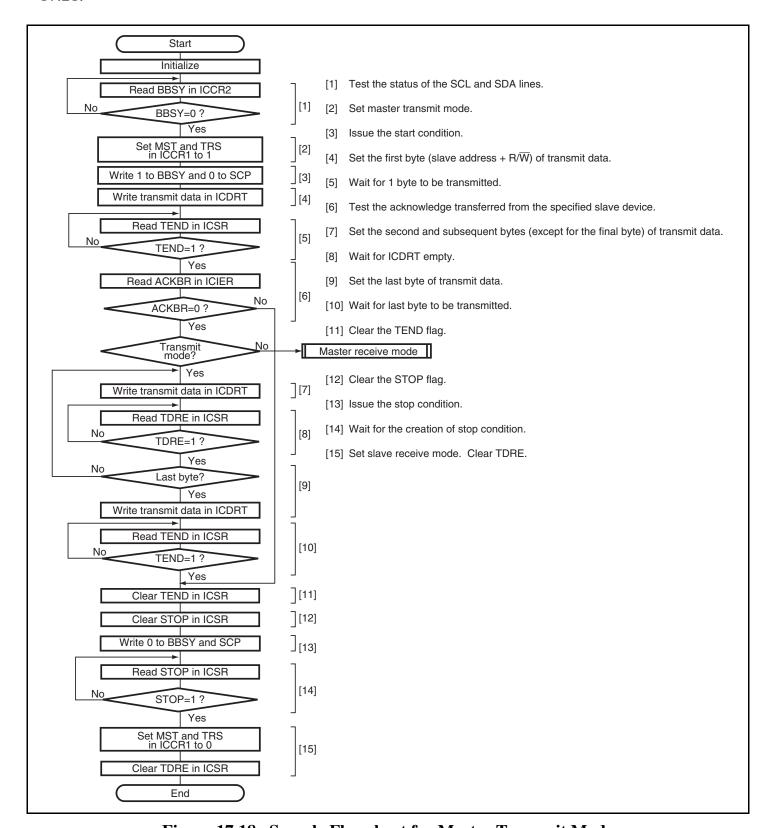

|      | 17.4.2  | Master Transmit Operation                                           | 745 |

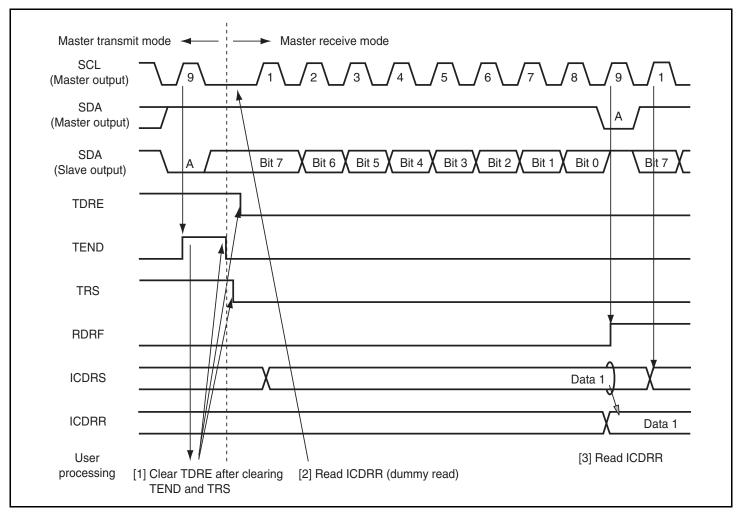

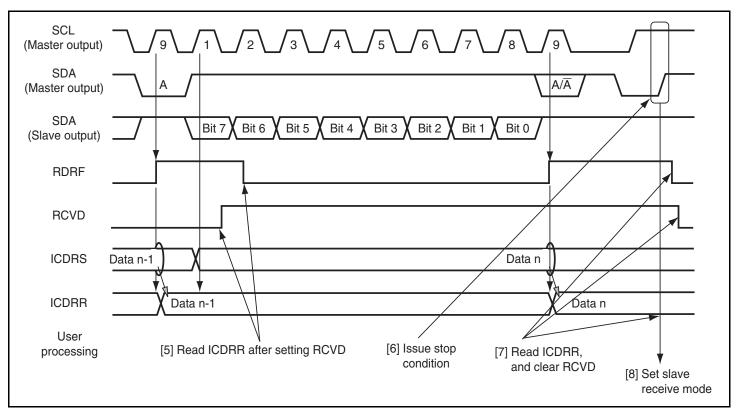

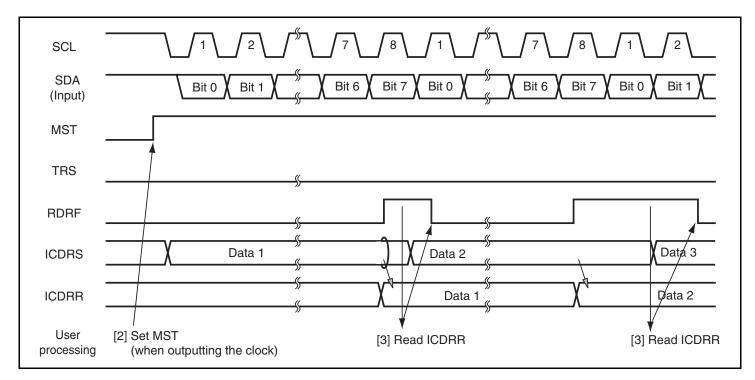

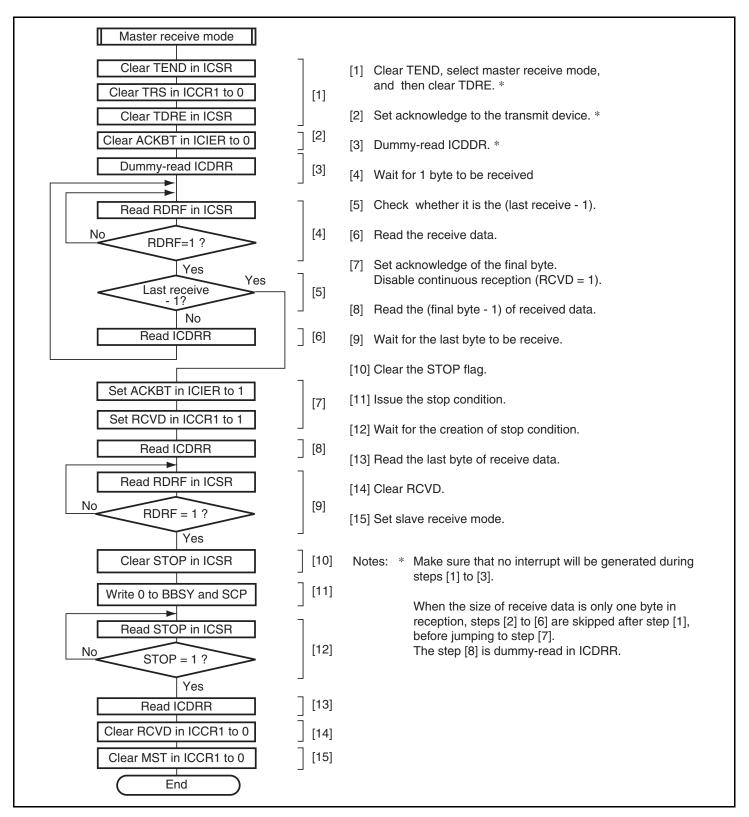

|      | 17.4.3  | Master Receive Operation                                            | 747 |

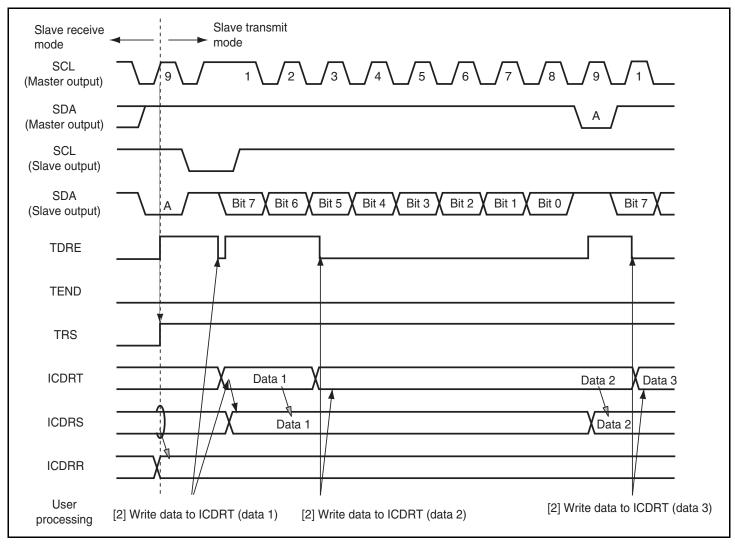

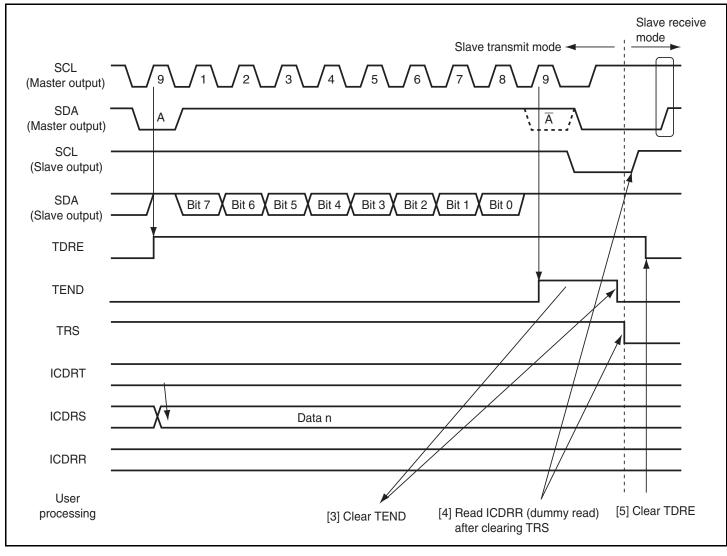

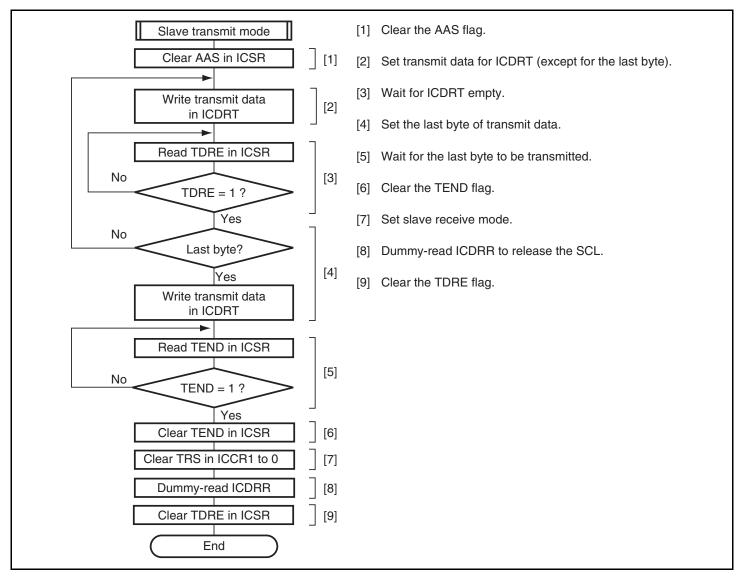

|      | 17.4.4  | Slave Transmit Operation                                            | 749 |

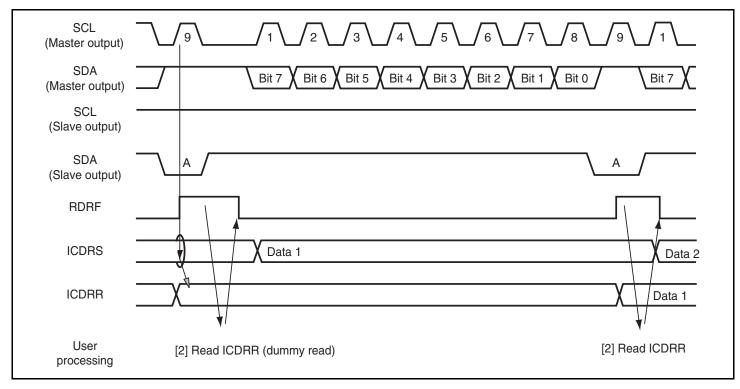

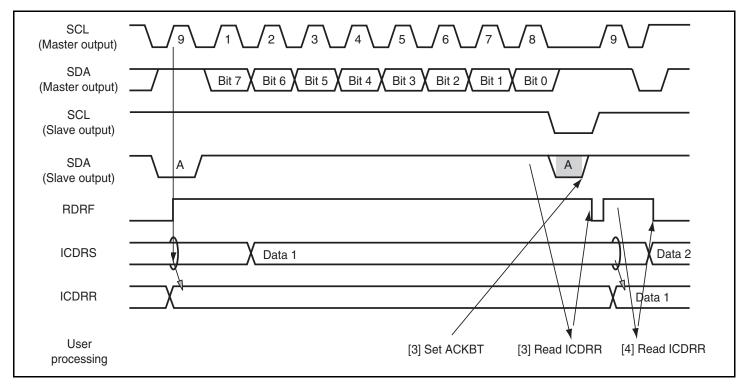

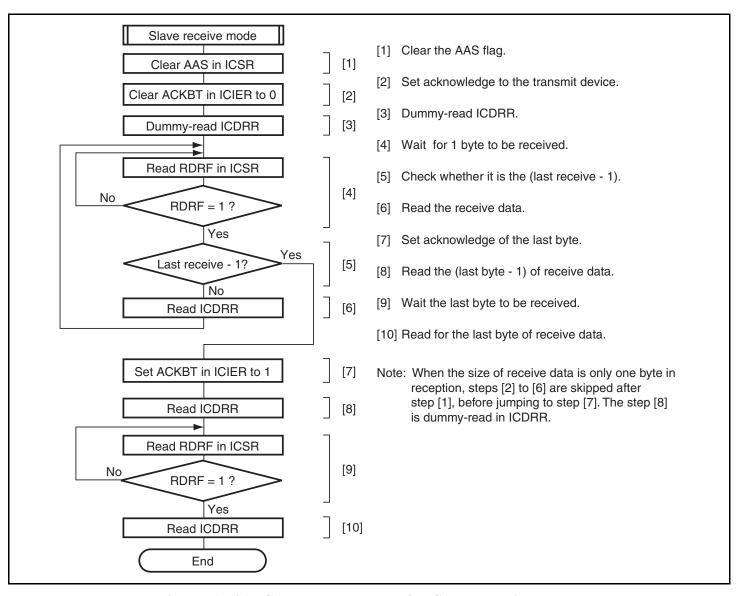

|      | 17.4.5  | 1                                                                   |     |

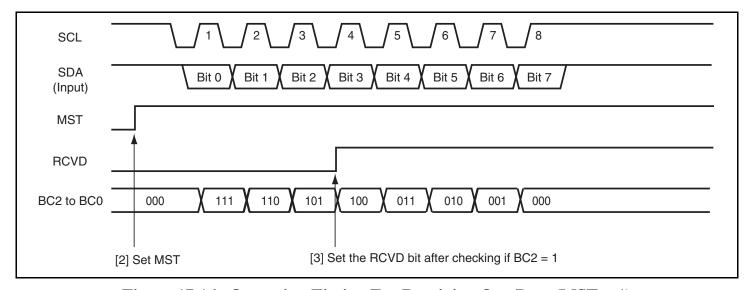

|      |         | Clocked Synchronous Serial Format                                   |     |

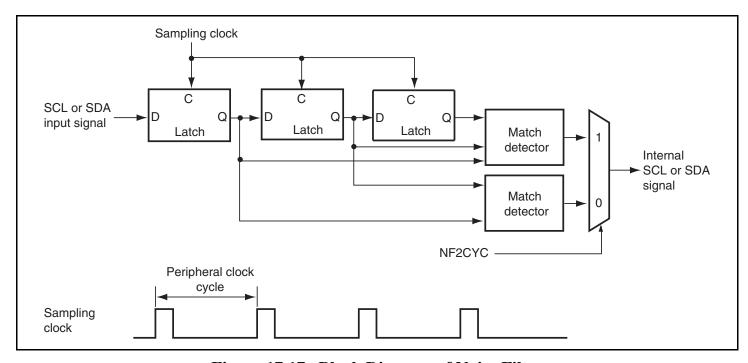

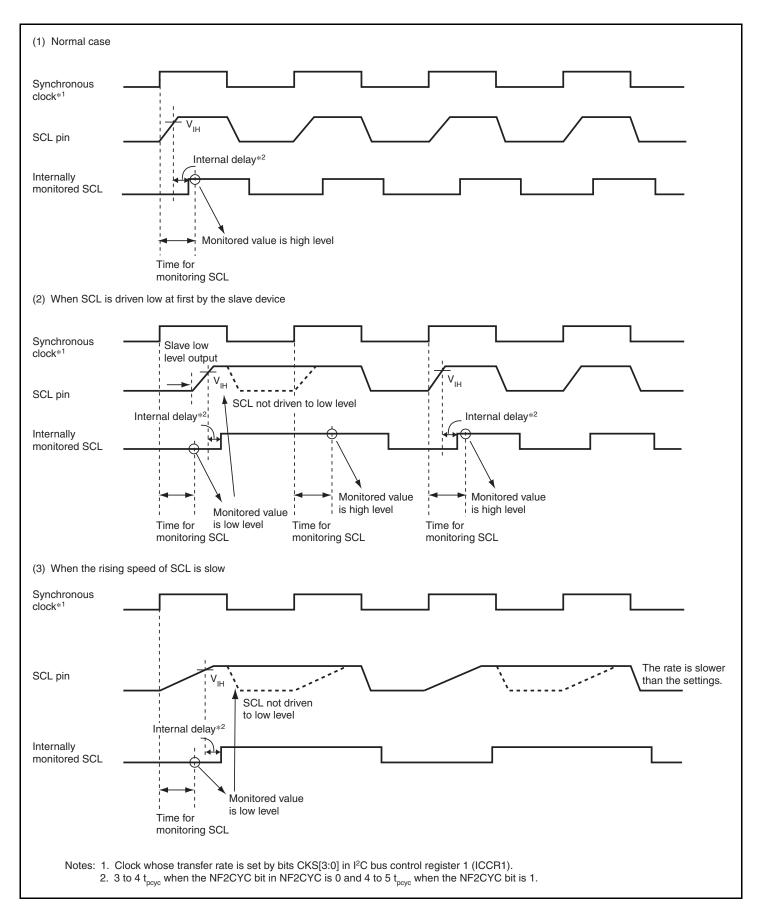

|      | 17.4.7  | Noise Filter                                                        | 757 |

|      | 17.4.8  | Example of Use                                                      | 758 |

| 17.5 | Interru | pt Requests                                                         | 762 |

| 17.6       | Bit Syı | it Synchronous Circuit                                          |     |  |

|------------|---------|-----------------------------------------------------------------|-----|--|

| 17.7       | Usage   | Note                                                            | 766 |  |

|            | 17.7.1  | Issuance of Stop Condition and Start Condition (Retransmission) | 766 |  |

|            | 17.7.2  | Settings for Multi-Master Operation                             | 766 |  |

|            | 17.7.3  | Reading ICDRR in Master Receive Mode                            | 766 |  |

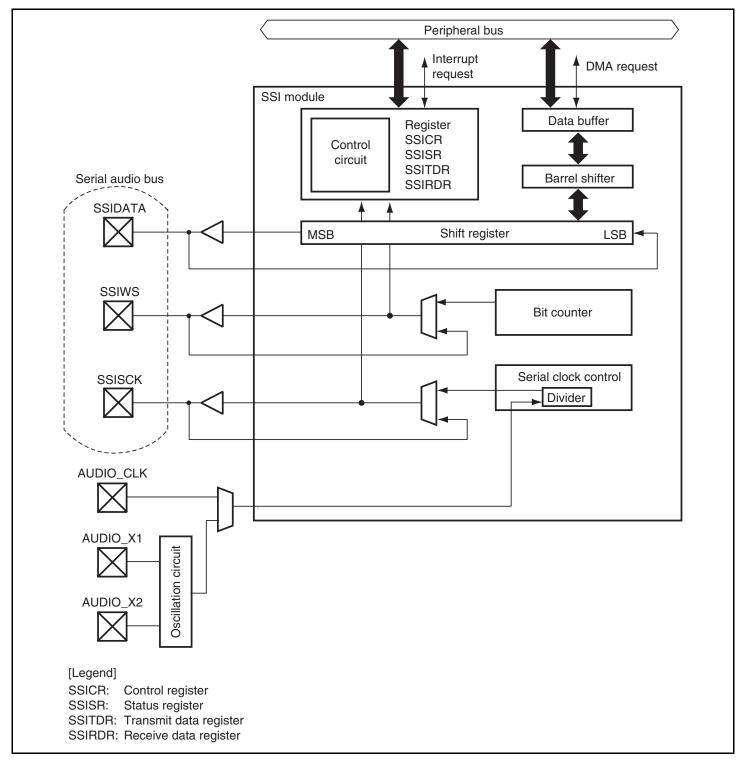

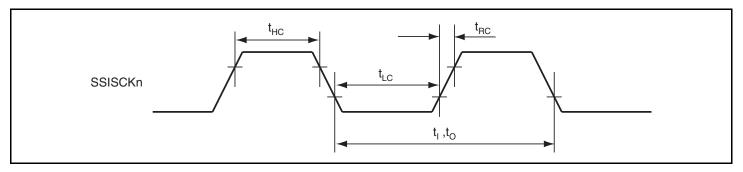

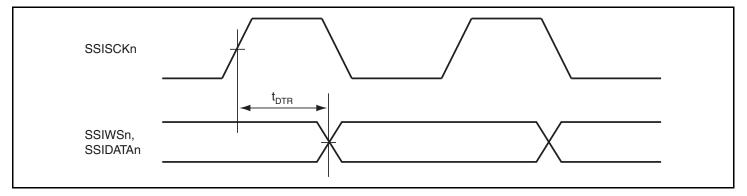

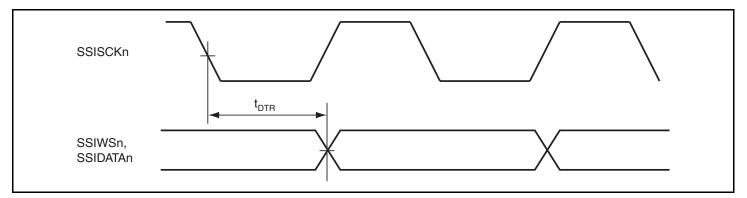

| Sect       | ion 18  | Serial Sound Interface (SSI)                                    | 767 |  |

| 18.1       | Feature | es                                                              | 767 |  |

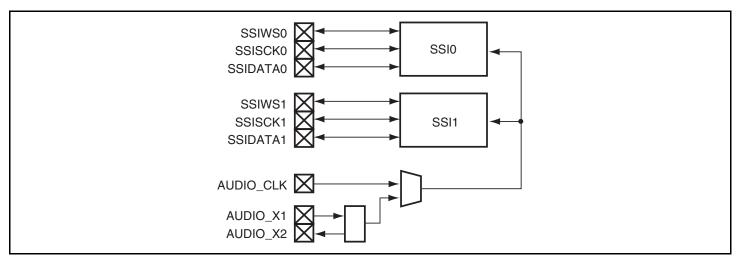

| 18.2       | Input/C | Output Pins                                                     | 769 |  |

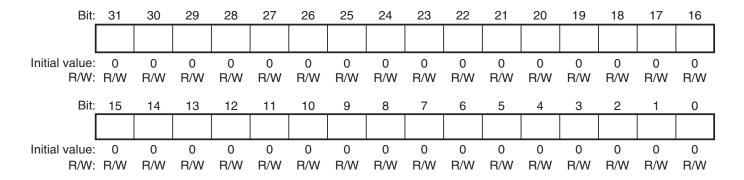

| 18.3       | Registe | er Description                                                  | 770 |  |

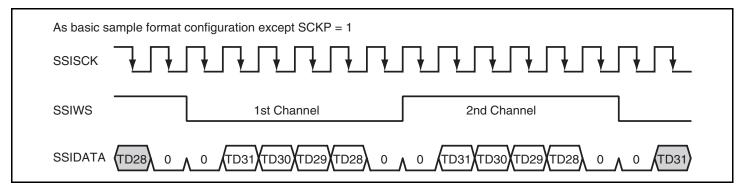

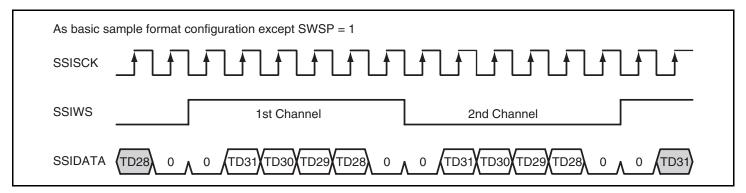

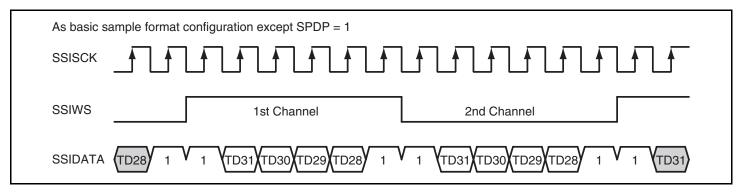

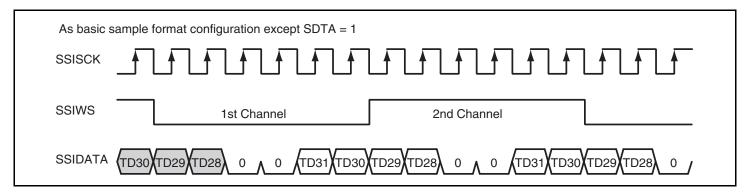

|            | 18.3.1  | Control Register (SSICR)                                        | 771 |  |

|            | 18.3.2  | Status Register (SSISR)                                         | 777 |  |

|            | 18.3.3  | Transmit Data Register (SSITDR)                                 | 782 |  |

|            | 18.3.4  | Receive Data Register (SSIRDR)                                  |     |  |

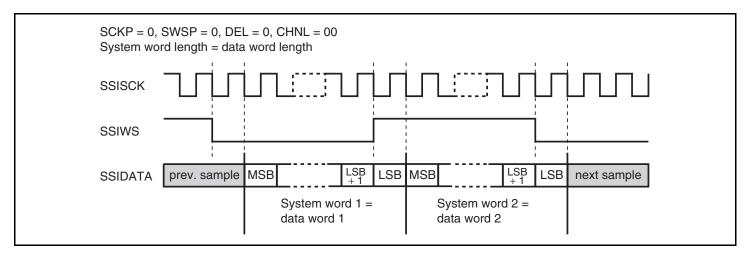

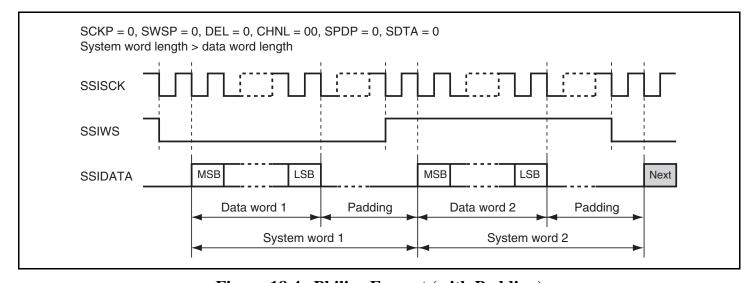

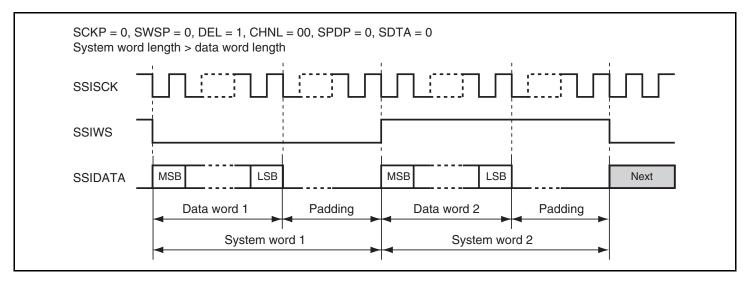

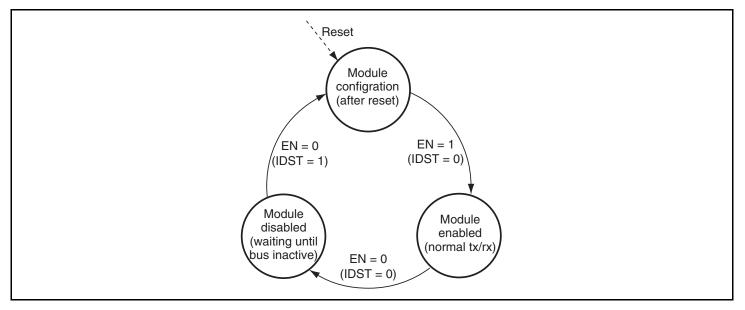

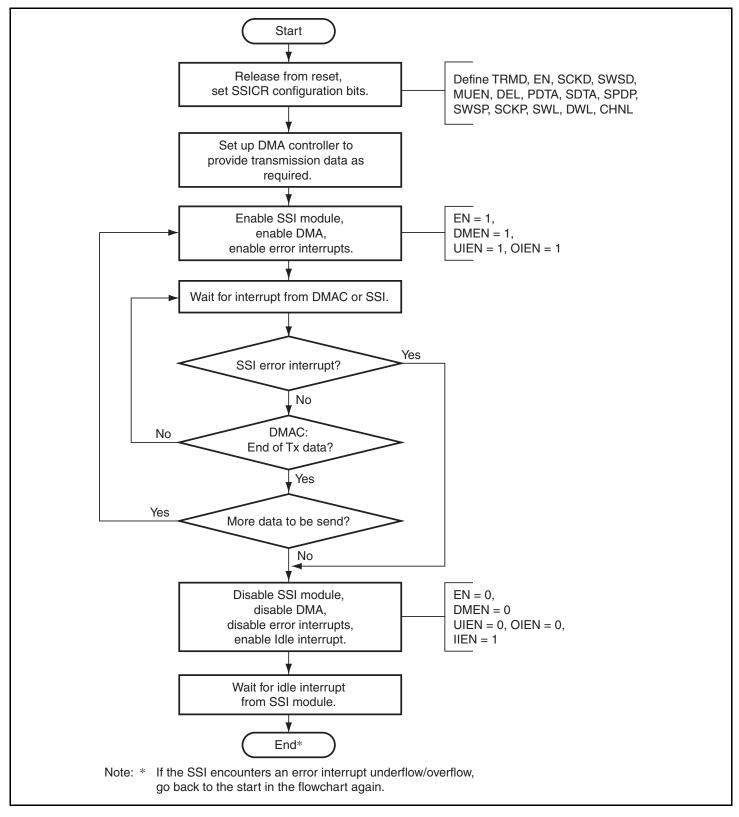

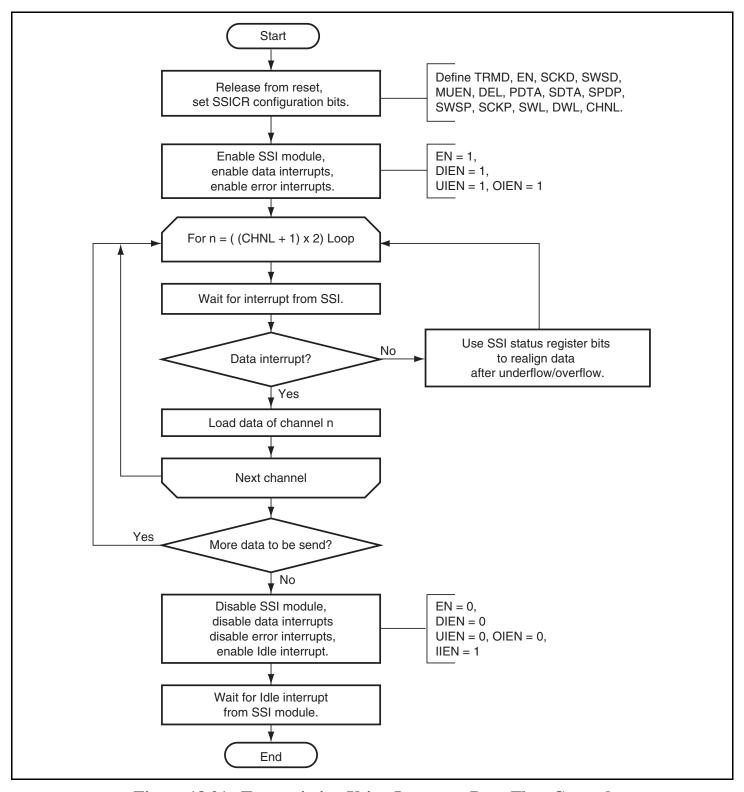

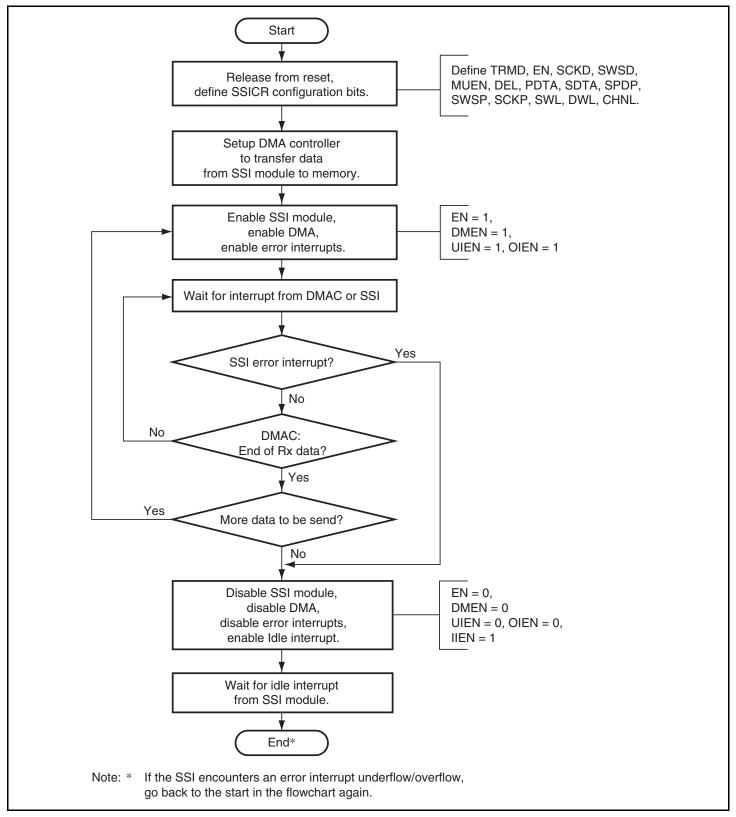

| 18.4       | Operat  | ion Description                                                 | 783 |  |

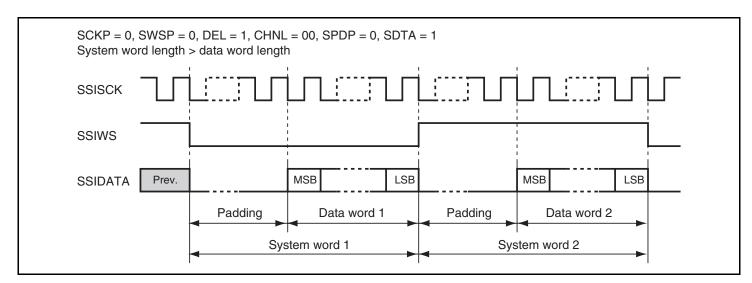

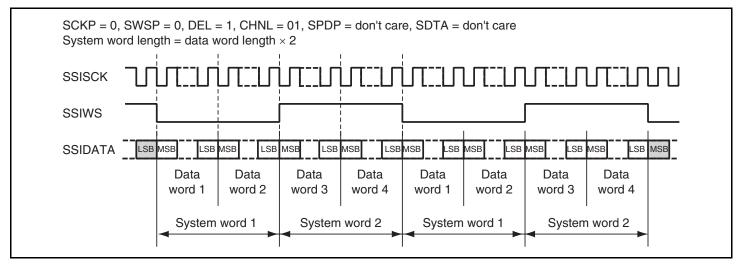

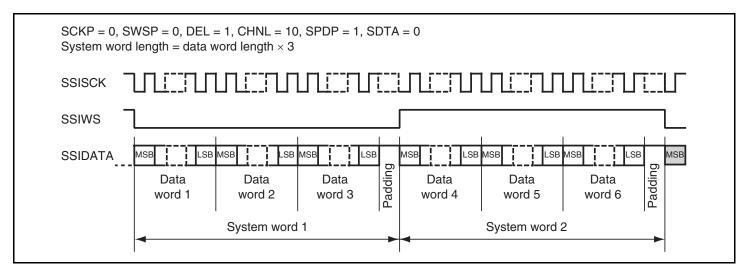

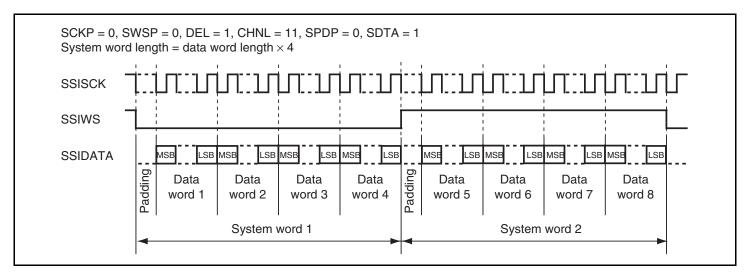

|            | _       | Bus Format                                                      |     |  |

|            | 18.4.2  | Non-Compressed Modes                                            | 784 |  |

|            | 18.4.3  | Operation Modes                                                 |     |  |

|            | 18.4.4  | Transmit Operation                                              | 795 |  |

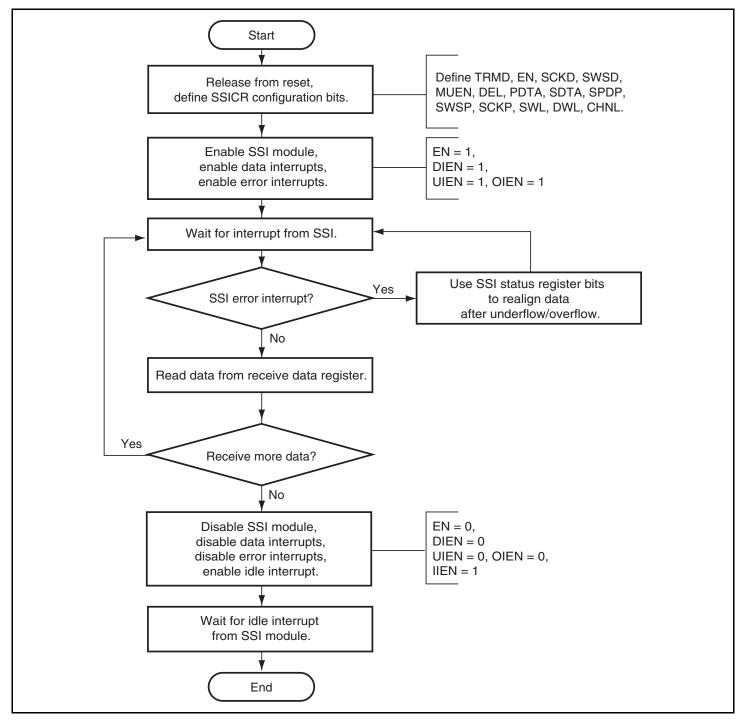

|            | 18.4.5  | Receive Operation                                               | 798 |  |

|            | 18.4.6  | Temporary Stop and Restart Procedures in Transmit Mode          |     |  |

|            | 18.4.7  | Serial Bit Clock Control                                        |     |  |

| 18.5       | Usage   | Notes                                                           | 802 |  |

|            | 18.5.1  | Limitations from Overflow during Receive DMA Operation          | 802 |  |

|            | 18.5.2  | -                                                               |     |  |

|            | 18.5.3  | Restriction on Stopping Clock Supply                            |     |  |

| <b>C</b> 4 | . 10    |                                                                 | 005 |  |

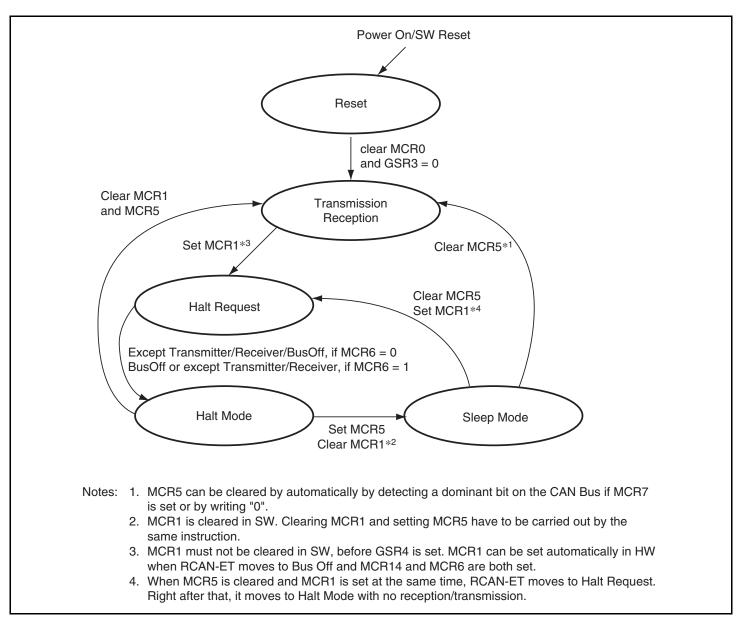

|            |         | Controller Area Network (RCAN-ET)                               |     |  |

| 19.1       |         | ary                                                             |     |  |

|            |         | Overview                                                        |     |  |

|            |         | Scope                                                           |     |  |

|            |         | Audience                                                        |     |  |

|            |         | References                                                      |     |  |

| 40.        |         | Features                                                        |     |  |

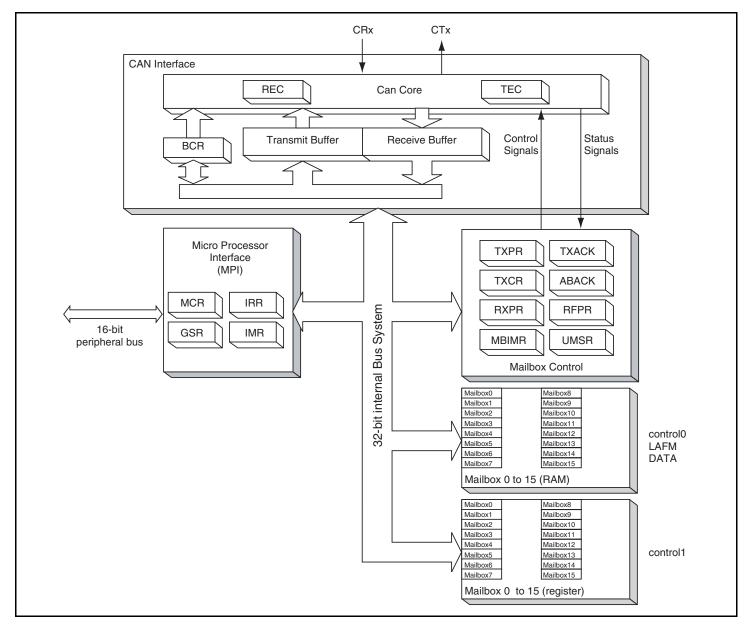

| 19.2       |         | ecture                                                          |     |  |

|            | 19.2.1  | Block Diagram                                                   |     |  |

|            |         | Functions of Each Block                                         |     |  |

|            |         | Input/Output Pins                                               |     |  |

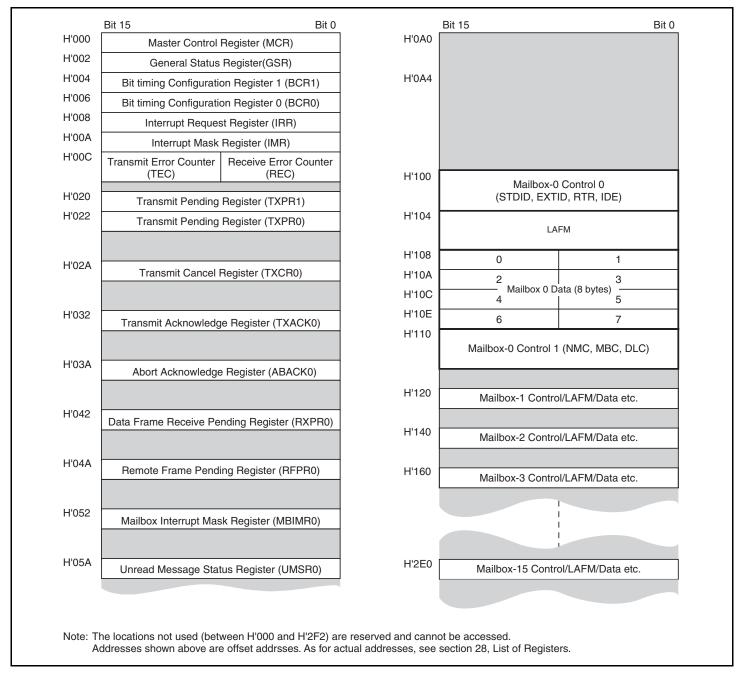

|            | 19.2.4  | Memory Map                                                      | 810 |  |

| 19.3 | Mailbo  | )X                                                           | 811 |

|------|---------|--------------------------------------------------------------|-----|

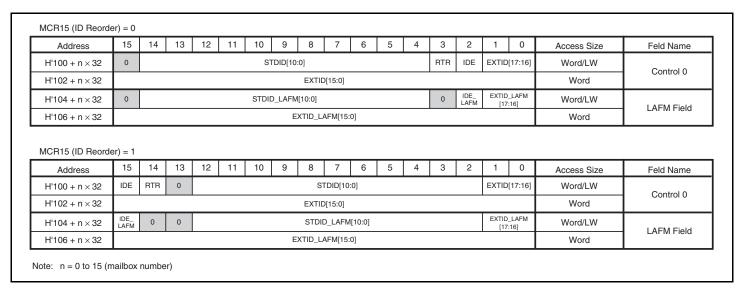

|      | 19.3.1  | Mailbox Structure                                            | 811 |

|      | 19.3.2  | Message Control Field                                        | 813 |

|      | 19.3.3  | Local Acceptance Filter Mask (LAFM)                          | 817 |

|      | 19.3.4  | Message Data Fields                                          | 818 |

| 19.4 | RCAN    | -ET Control Registers                                        | 819 |

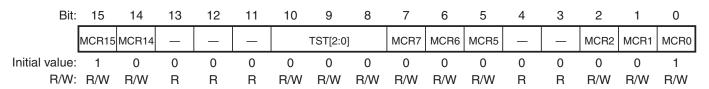

|      | 19.4.1  | Master Control Register (MCR)                                | 819 |

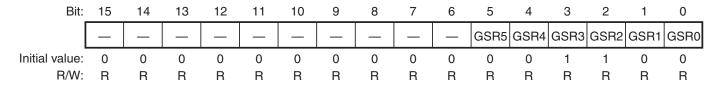

|      | 19.4.2  | General Status Register (GSR)                                | 825 |

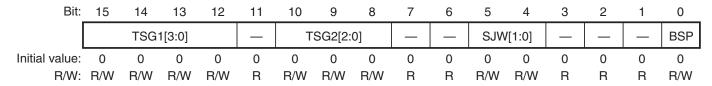

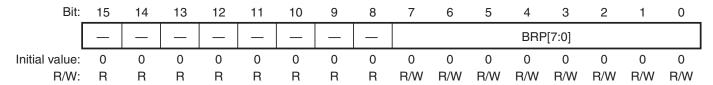

|      | 19.4.3  | Bit Configuration Register (BCR0, BCR1)                      | 828 |

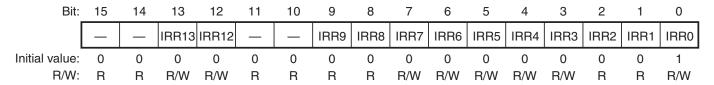

|      | 19.4.4  | Interrupt Request Register (IRR)                             | 833 |

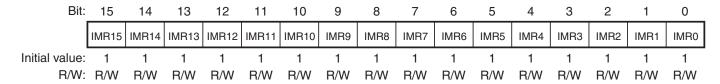

|      | 19.4.5  | Interrupt Mask Register (IMR)                                | 839 |

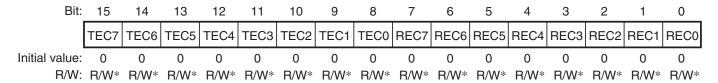

|      | 19.4.6  | Transmit Error Counter (TEC) and Receive Error Counter (REC) | 840 |

| 19.5 | RCAN    | -ET Mailbox Registers                                        | 841 |

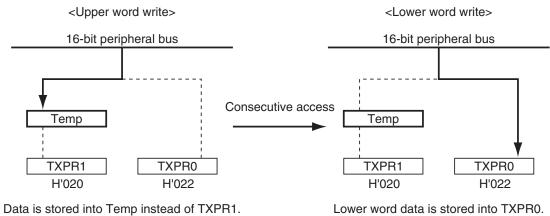

|      | 19.5.1  | Transmit Pending Register (TXPR0, TXPR1)                     | 842 |

|      | 19.5.2  | Transmit Cancel Register 0 (TXCR0)                           | 845 |

|      | 19.5.3  | Transmit Acknowledge Register 0 (TXACK0)                     | 846 |

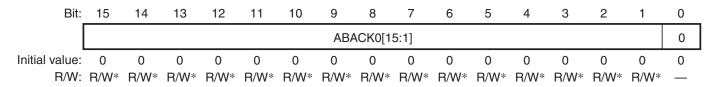

|      | 19.5.4  | Abort Acknowledge Register 0 (ABACK0)                        | 847 |

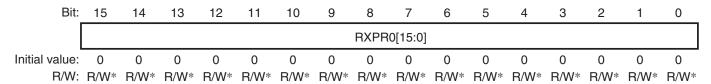

|      | 19.5.5  | Data Frame Receive Pending Register 0 (RXPR0)                | 848 |

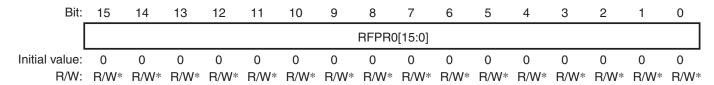

|      | 19.5.6  | Remote Frame Receive Pending Register 0 (RFPR0)              | 849 |

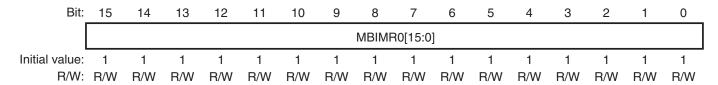

|      | 19.5.7  | Mailbox Interrupt Mask Register 0 (MBIMR0)                   | 850 |

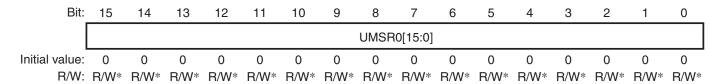

|      | 19.5.8  | Unread Message Status Register 0 (UMSR0)                     | 851 |

| 19.6 | Applic  | ation Note                                                   | 852 |

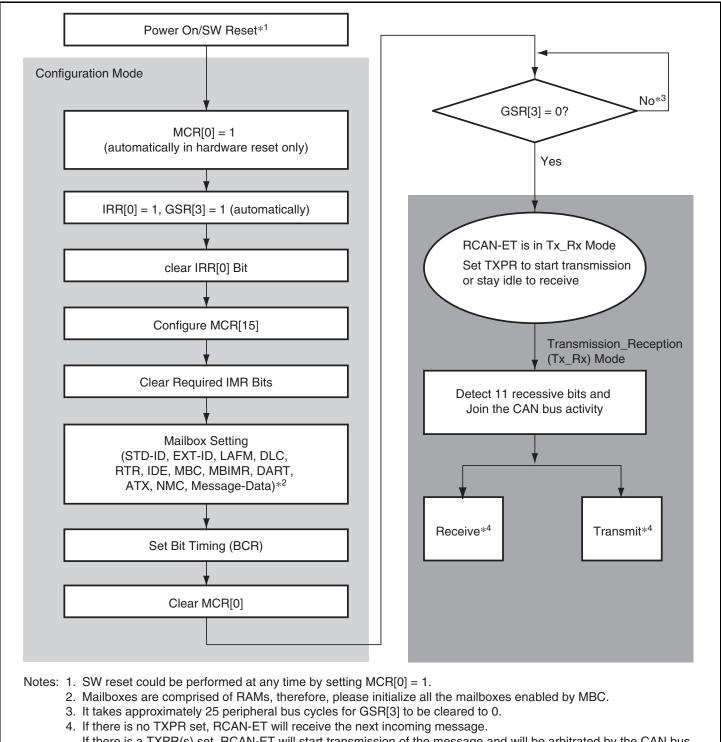

|      | 19.6.1  | Configuration of RCAN-ET                                     | 852 |

|      | 19.6.2  | Test Mode Settings                                           | 857 |

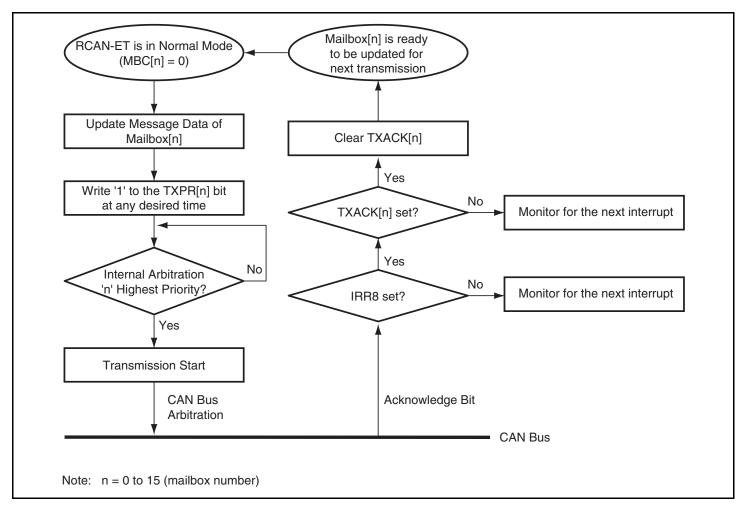

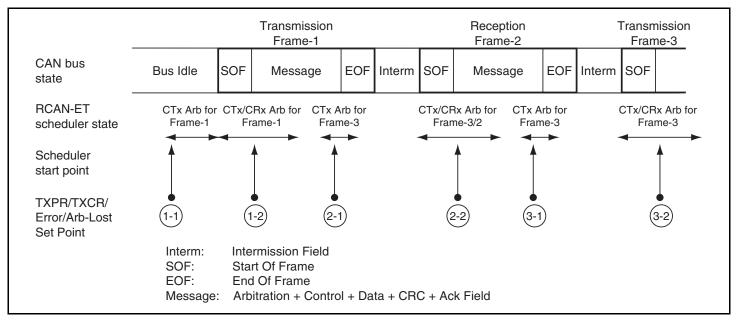

|      | 19.6.3  | Message Transmission Sequence                                | 859 |

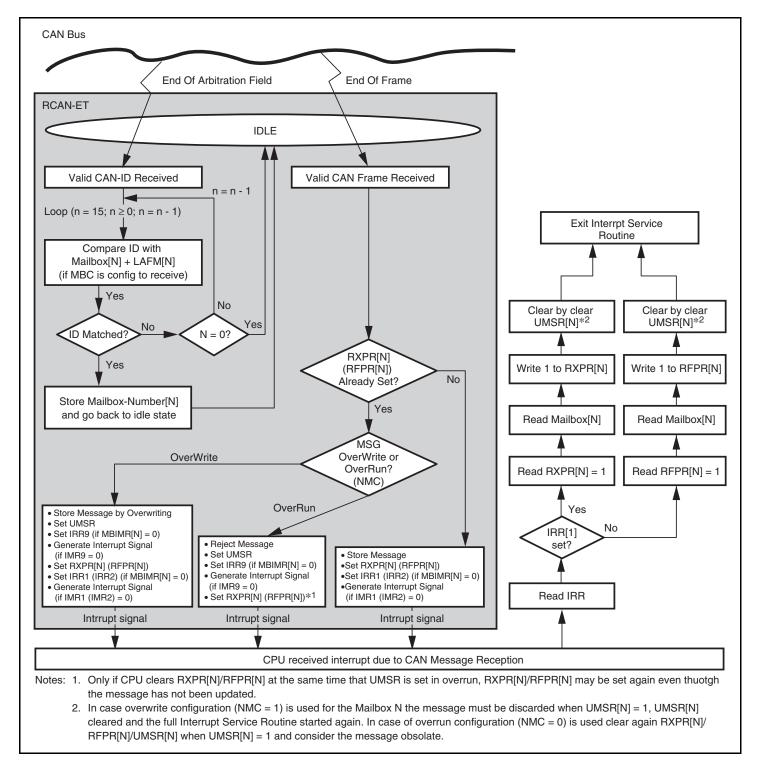

|      | 19.6.4  | Message Receive Sequence                                     | 861 |

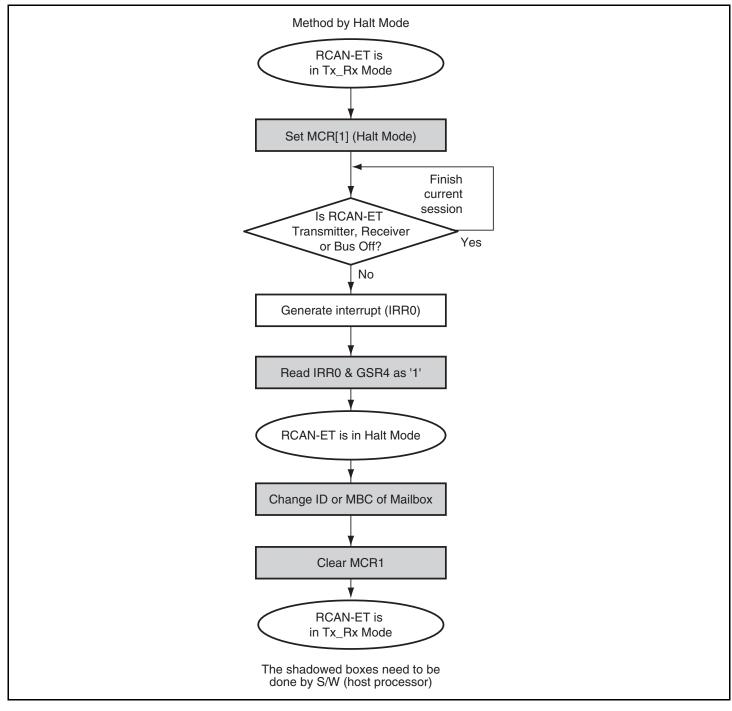

|      | 19.6.5  | Reconfiguration of Mailbox                                   | 863 |

| 19.7 | Interru | pt Sources                                                   | 865 |

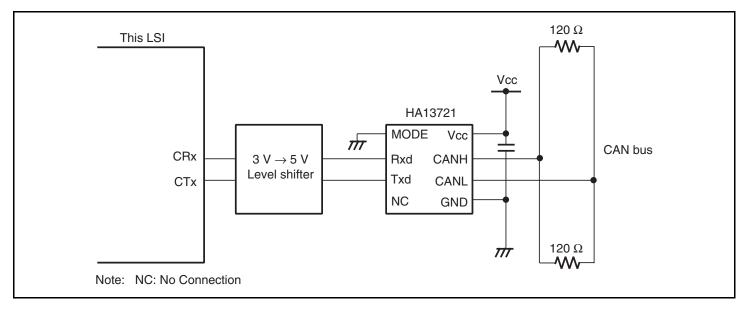

| 19.8 | CAN E   | Bus Interface                                                | 867 |

| 19.9 | Usage   | Notes                                                        | 868 |

|      | 19.9.1  | Module Standby Mode                                          | 868 |

|      | 19.9.2  | Reset                                                        | 868 |

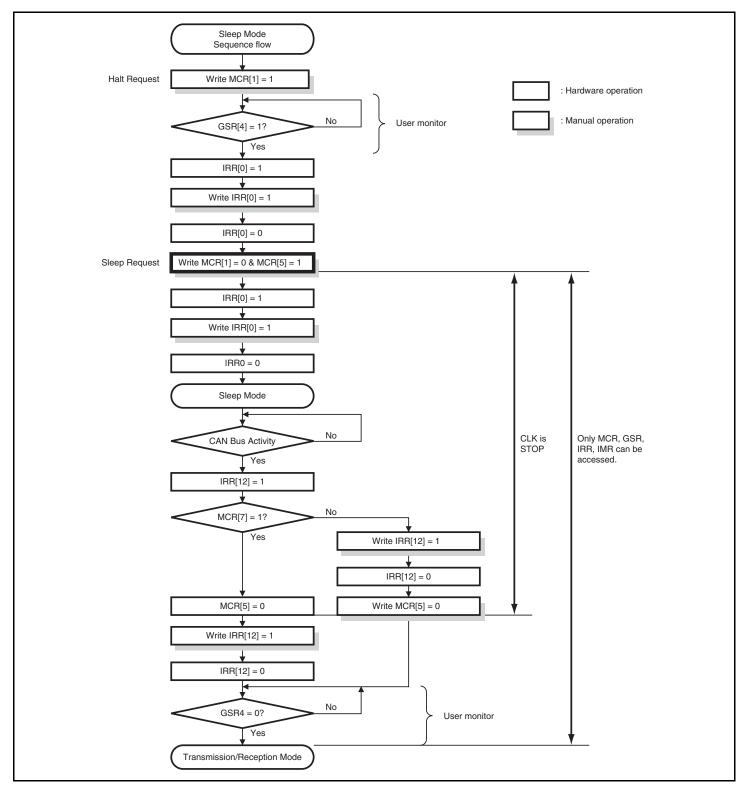

|      | 19.9.3  | CAN Sleep Mode                                               | 868 |

|      | 19.9.4  | Register Access                                              | 868 |

|      | 19.9.5  | Interrupts                                                   | 869 |

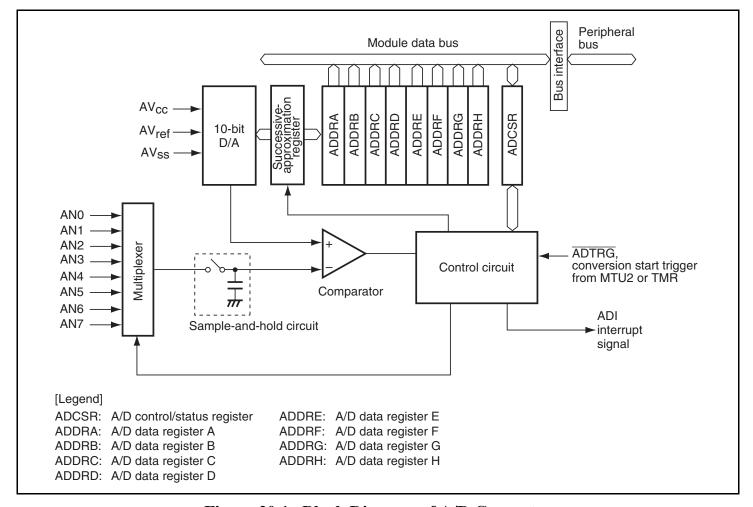

| Sect | ion 20  | A/D Converter (ADC)                                          | 871 |

| 20.1 | Feature | es                                                           | 871 |

| 20.2 | Input/C | Output Pins                                                  | 873 |

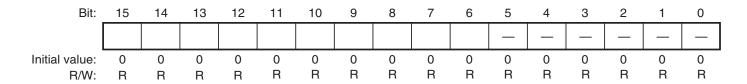

| 20.3 | Registe | er Configuration                                             | 874 |

|      | 20.3.1  | A/D Data Registers A to H (ADDRA to ADDRH)                    | 874 |

|------|---------|---------------------------------------------------------------|-----|

|      | 20.3.2  | A/D Control/Status Register (ADCSR)                           | 876 |

| 20.4 | Operat  | ion                                                           | 880 |

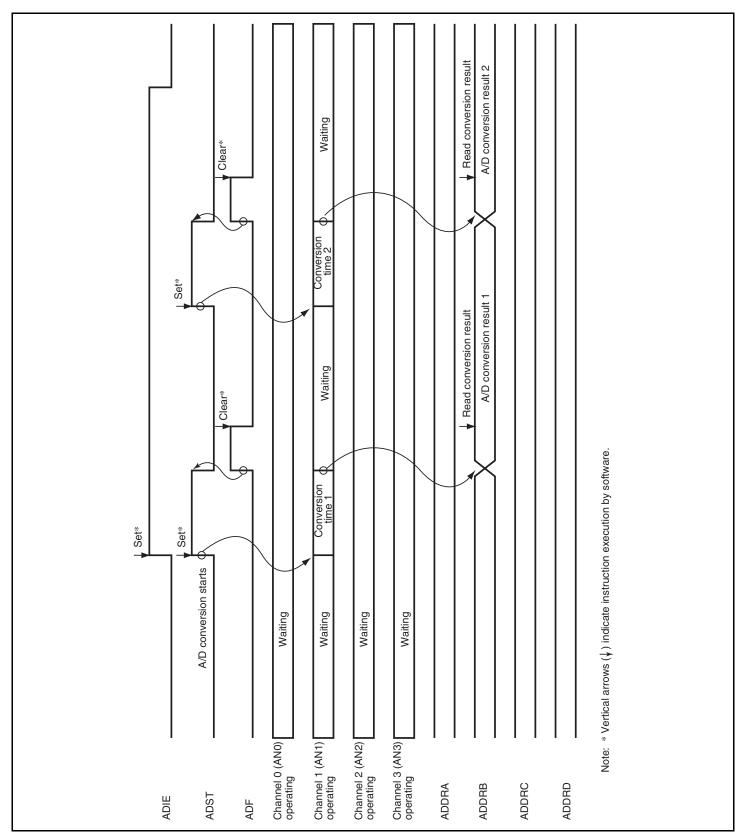

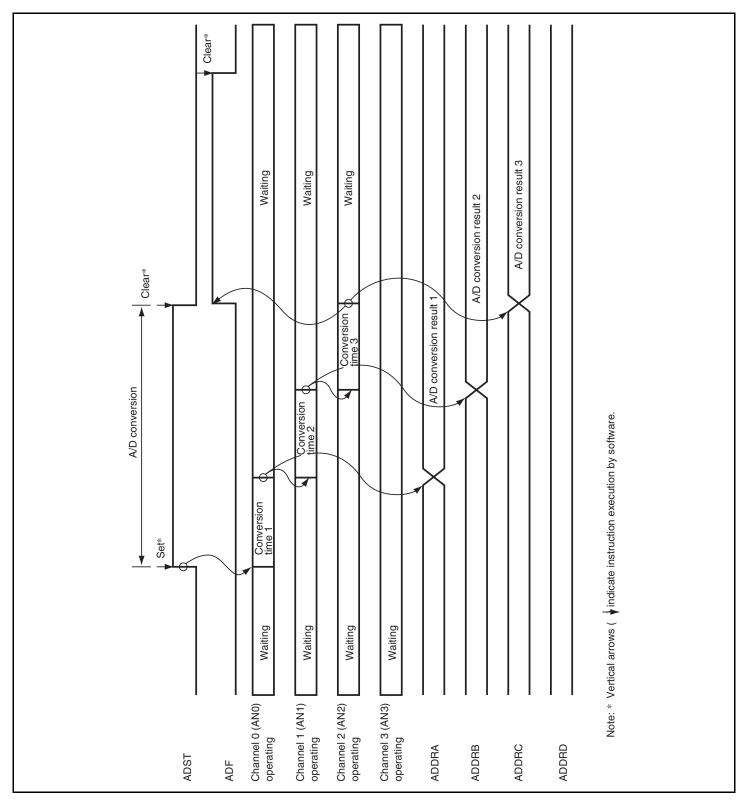

|      | 20.4.1  | Single Mode                                                   | 880 |

|      | 20.4.2  | Multi Mode                                                    | 883 |

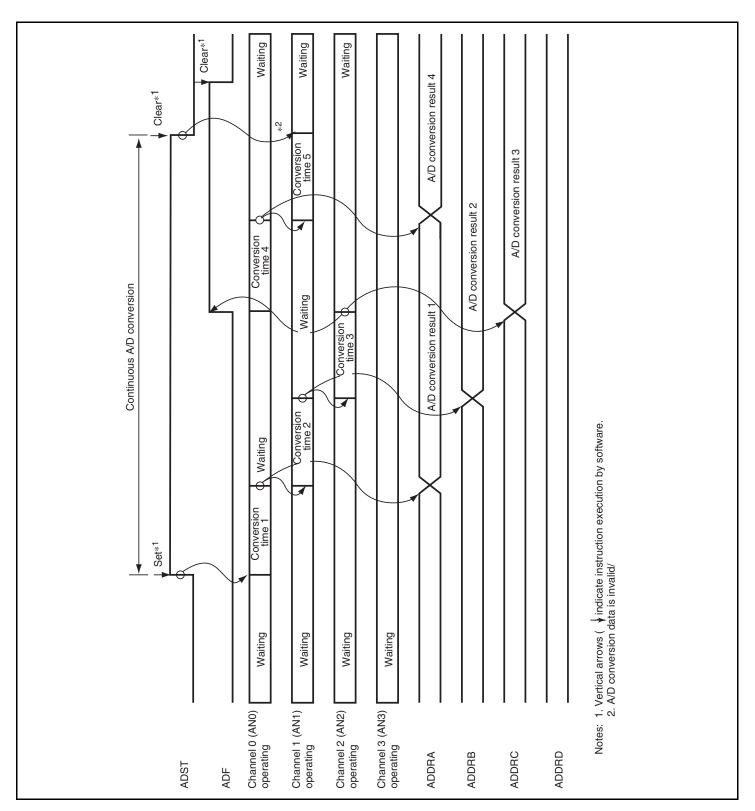

|      | 20.4.3  | Scan Mode                                                     | 885 |

|      | 20.4.4  | A/D Converter Activation by External Trigger, MTU2, or TMR    | 888 |

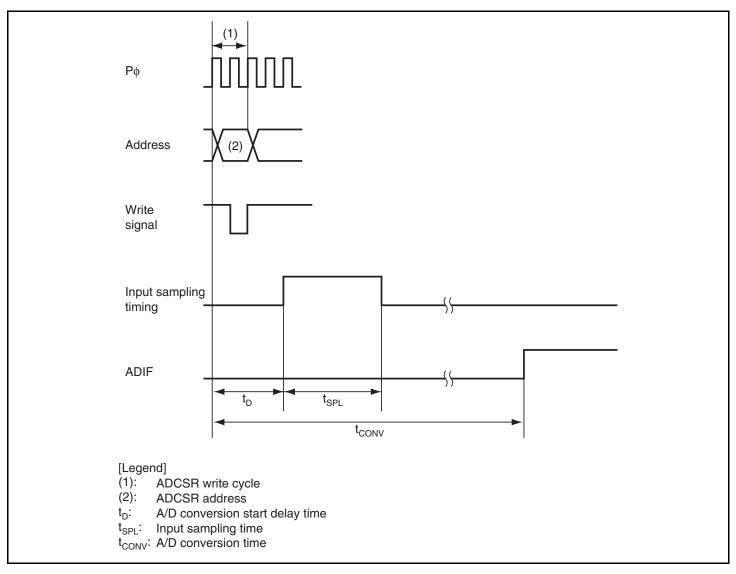

|      | 20.4.5  | Input Sampling and A/D Conversion Time                        | 888 |

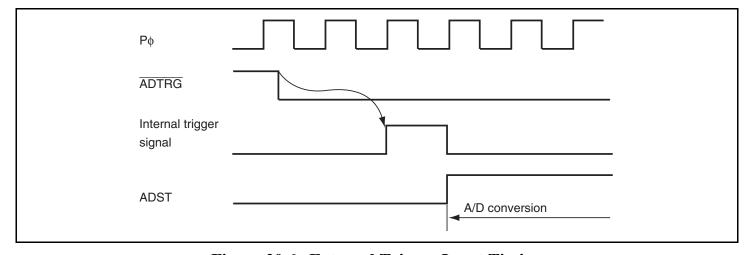

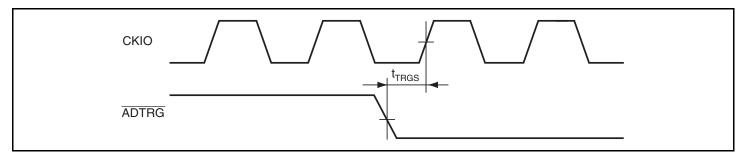

|      | 20.4.6  | External Trigger Input Timing                                 | 890 |

| 20.5 | Interru | pt Sources and DMAC Transfer Request                          | 891 |

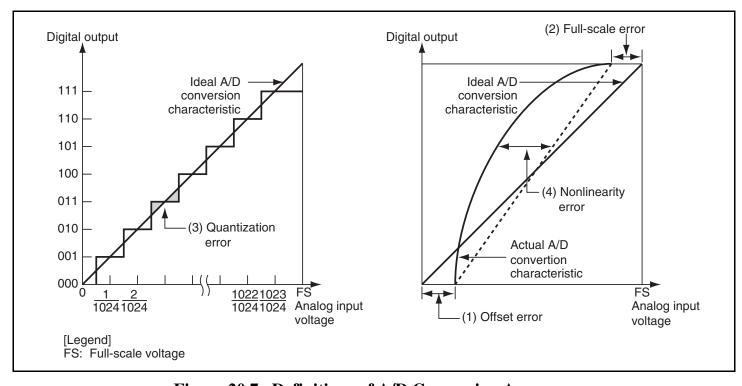

| 20.6 | Definit | ions of A/D Conversion Accuracy                               | 891 |

| 20.7 | Usage   | Notes                                                         | 893 |

|      | 20.7.1  | Module Standby Mode Setting                                   | 893 |

|      | 20.7.2  | Setting Analog Input Voltage                                  | 893 |

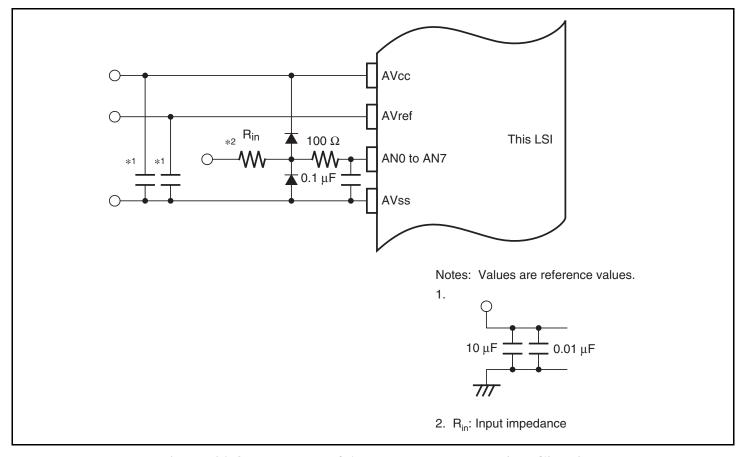

|      | 20.7.3  | Notes on Board Design                                         | 893 |

|      | 20.7.4  | Processing of Analog Input Pins                               | 894 |

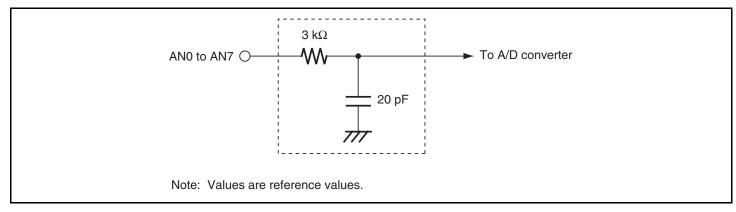

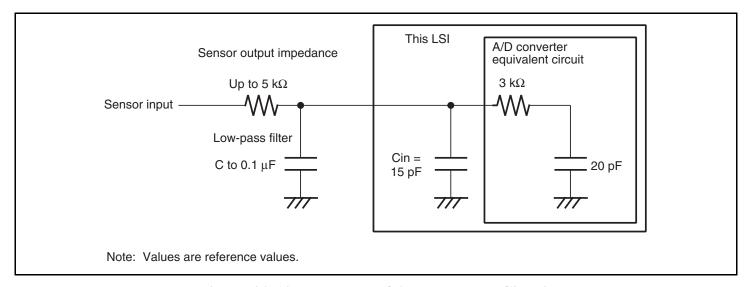

|      | 20.7.5  | Permissible Signal Source Impedance                           | 895 |

|      | 20.7.6  | Influences on Absolute Precision                              | 896 |

|      | 20.7.7  | Usage Note when Shifting to Single Mode during A/D Conversion | 896 |

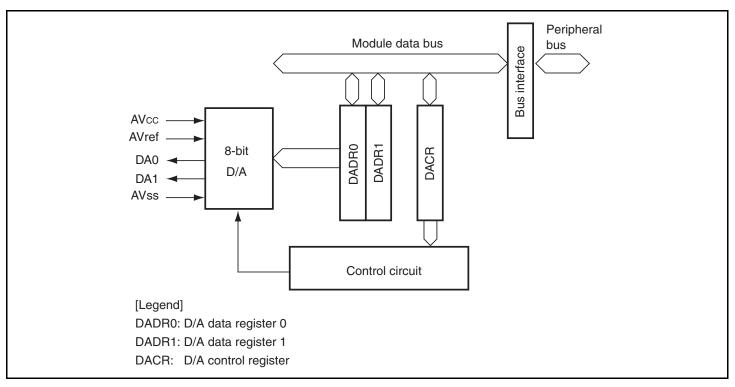

| Sect | ion 21  | D/A Converter (DAC)                                           | 897 |

| 21.1 | Feature | es                                                            | 897 |

| 21.2 | •       | Output Pins                                                   |     |

| 21.3 | Registe | er Descriptions                                               | 898 |

|      | 21.3.1  | D/A Data Registers 0 and 1 (DADR0 and DADR1)                  | 899 |

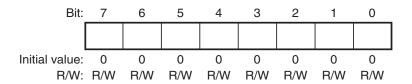

|      | 21.3.2  | D/A Control Register (DACR)                                   | 899 |

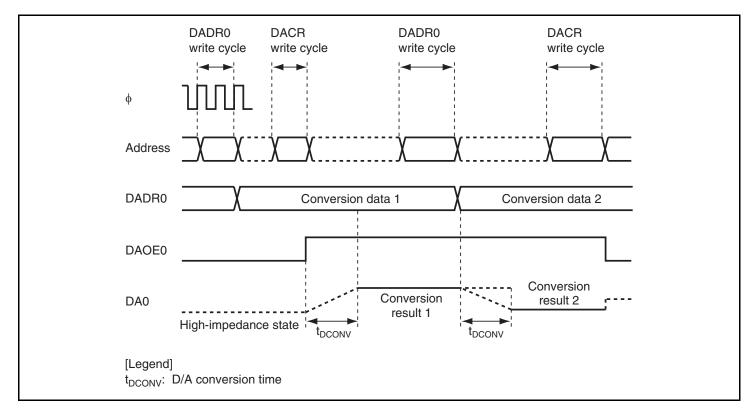

| 21.4 | Operat  | ion                                                           | 901 |

| 21.5 | Usage   | Notes                                                         | 902 |

|      | 21.5.1  | Module Standby Mode Setting                                   | 902 |

|      | 21.5.2  | D/A Output Hold Function in Software Standby Mode             | 902 |

|      | 21.5.3  | D/A Conversion and D/A Output in Deep Standby Mode            | 902 |

|      | 21.5.4  | Setting Analog Input Voltage                                  | 902 |

| Sect | ion 22  | I/O Ports                                                     | 903 |

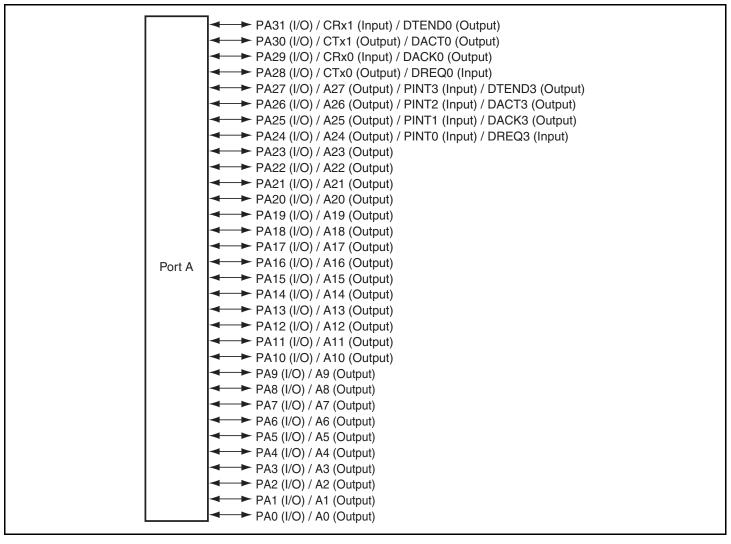

| 22.1 | Port A  |                                                               | 903 |

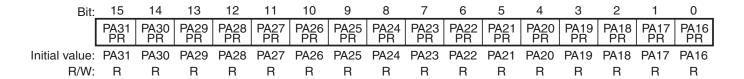

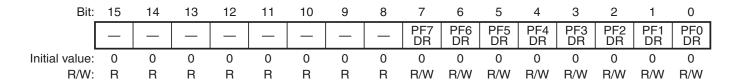

|      | 22.1.1  | Register Configuration                                        | 904 |

|      | 22.1.2  | Port A Data Registers H and L (PADRH and PADRL)               | 904 |

|      | 22.1.3  | Port A Port Registers H and L (PAPRH and PAPRL)               | 906 |

| 22.2 |         |                                                               |     |

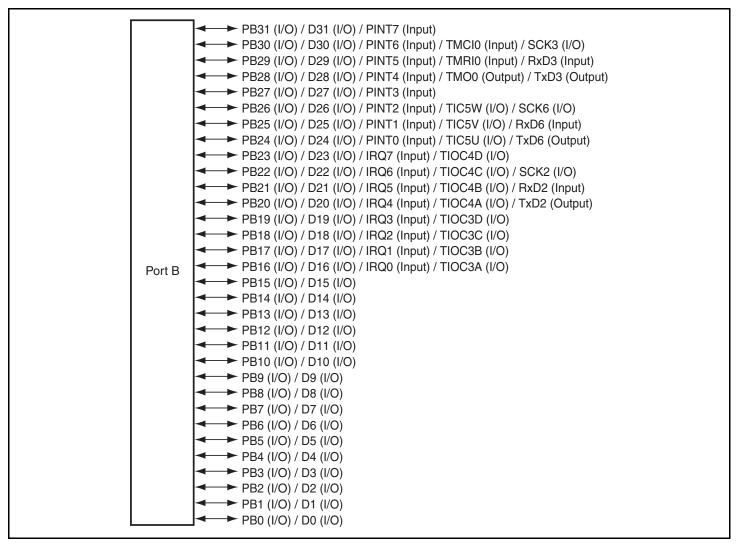

|      | 22.2.1  | Register Configuration                                        | 908 |

|              | 22.2.2 | Port B Data Registers H and L (PBDRH and PBDRL)    | 908 |

|--------------|--------|----------------------------------------------------|-----|

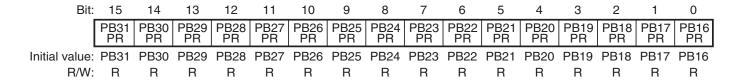

|              | 22.2.3 | Port B Port Registers H and L (PBPRH and PBPRL)    | 910 |

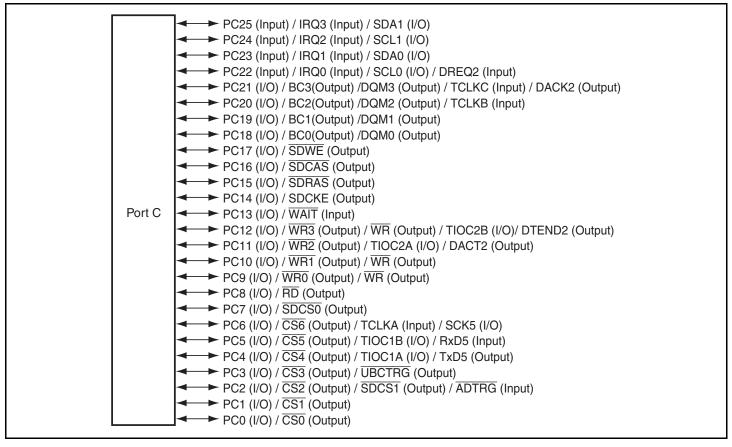

| 22.3         | Port C |                                                    | 911 |

|              | 22.3.1 | Register Configuration                             | 911 |

|              | 22.3.2 | Port C Data Registers H and L (PCDRH and PCDRL)    | 912 |

|              | 22.3.3 | Port C Port Registers H and L (PCPRH and PCPRL)    | 913 |

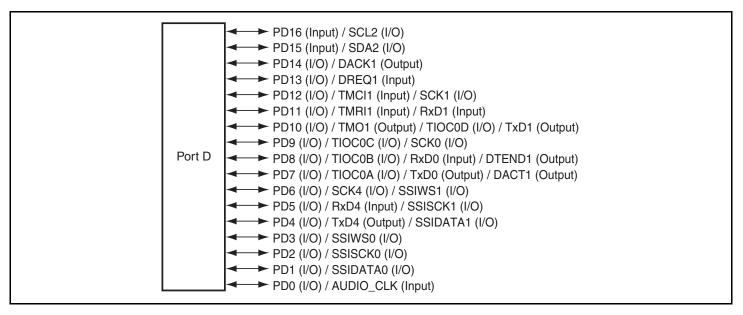

| 22.4         | Port D |                                                    | 914 |

|              | 22.4.1 | Register Configuration                             | 914 |

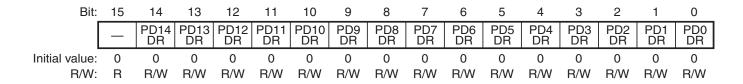

|              | 22.4.2 | Port D Data Register (PDDR)                        | 915 |

|              | 22.4.3 | Port D Port Registers H and L (PDPRH and PDPRL)    | 916 |

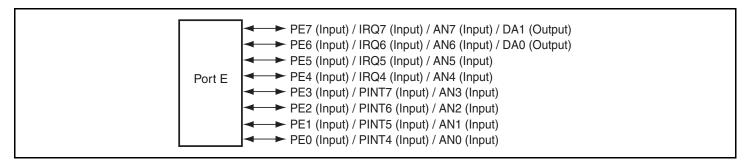

| 22.5         | Port E |                                                    | 917 |

|              | 22.5.1 | Register Configuration                             | 917 |

|              | 22.5.2 | Port E Port Register (PEPR)                        | 917 |

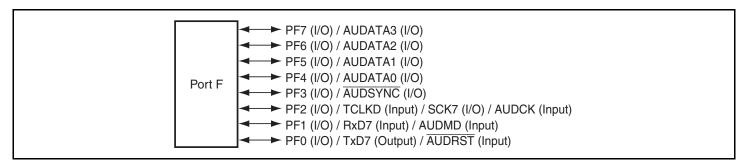

| 22.6         | Port F |                                                    | 918 |

|              | 22.6.1 | Register Configuration                             | 918 |

|              | 22.6.2 | Port F Data Register (PFDR)                        | 919 |

|              | 22.6.3 | Port F Port Register (PFPR)                        | 920 |

| Sect         | ion 23 | Pin Function Controller (PFC)                      | 921 |

| 23.1         |        | er Descriptions                                    |     |

|              | •      | Port A I/O Registers H and L (PAIORH and PAIORL)   |     |

|              |        | Port A Control Registers 1 to 8 (PACR1 to PACR8)   |     |

|              |        | Port B I/O Registers H and L (PBIORH and PBIORL)   |     |

|              |        | Port B Control Registers 1 to 8 (PBCR1 to PBCR8)   |     |

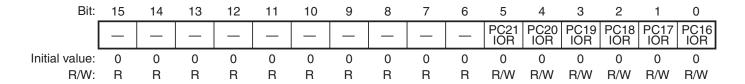

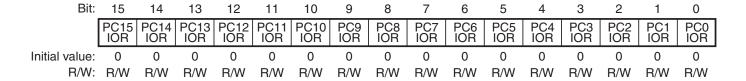

|              | 23.1.5 | Port C I/O Registers H and L (PCIORH and PCIORL)   | 956 |

|              |        | Port C Control Registers 1 to 7 (PCCR1 to PCCR7)   |     |

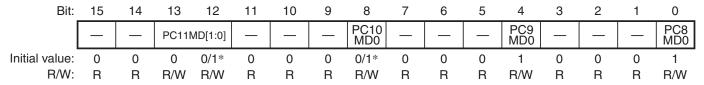

|              |        | Port D I/O Register (PDIOR)                        |     |

|              |        | Port D Control Registers 1 to 5 (PDCR1 to PDCR5)   |     |

|              |        | Port E Control Registers 1 and 2 (PECR1 and PECR2) |     |

|              |        | ) Port F I/O Register (PFIOR)                      |     |

|              |        | Port F Control Registers 1 and 2 (PFCR1 and PFCR2) |     |

| 23.2         |        | Note                                               |     |

| Sect         | ion 24 | On-Chip RAM                                        | 983 |

| 24.1         |        | es                                                 |     |

| 24.2         |        | Notes                                              |     |

| <del>-</del> | _      | Page Conflict                                      |     |

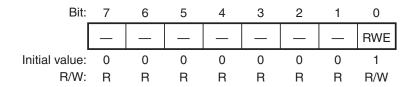

|              |        | RAME and RAMWE Bits                                |     |

| Sect | ion 25  | Power-Down Modes                                                     | 985  |

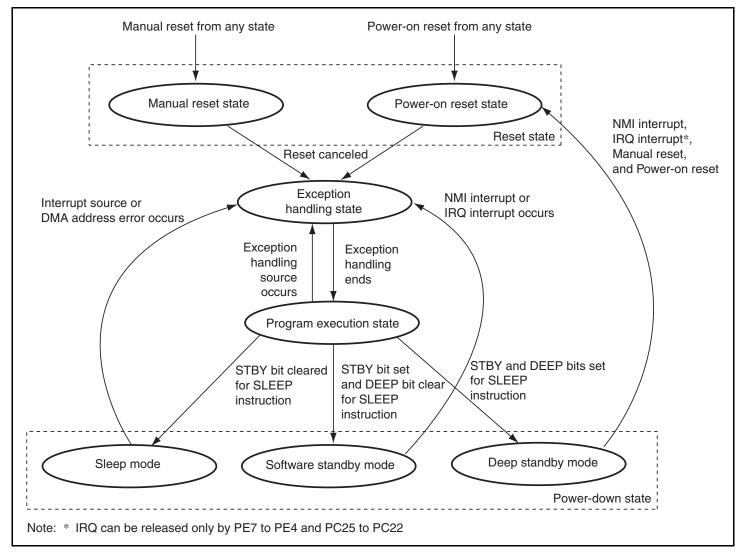

|------|---------|----------------------------------------------------------------------|------|

| 25.1 | Feature | es                                                                   | 985  |

|      | 25.1.1  | Power-Down Modes                                                     | 985  |

| 25.2 | Registe | er Descriptions                                                      | 987  |

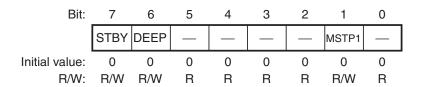

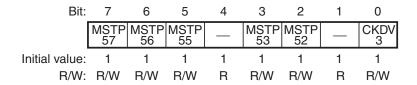

|      | 25.2.1  | Standby Control Register (STBCR)                                     | 988  |

|      | 25.2.2  | Standby Control Register 2 (STBCR2)                                  | 989  |

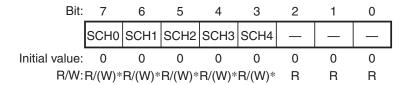

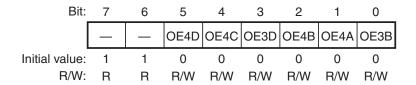

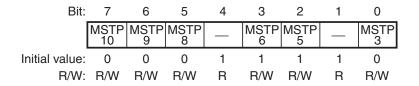

|      | 25.2.3  | Standby Control Register 3 (STBCR3)                                  | 991  |

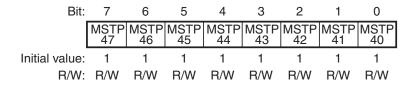

|      | 25.2.4  | Standby Control Register 4 (STBCR4)                                  | 992  |

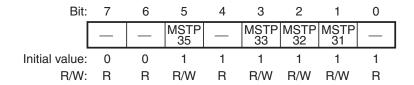

|      | 25.2.5  | Standby Control Register 5 (STBCR5)                                  | 994  |

|      | 25.2.6  | System Control Register 1 (SYSCR1)                                   | 996  |

|      | 25.2.7  | System Control Register 2 (SYSCR2)                                   | 997  |

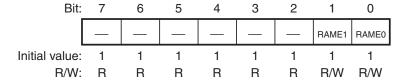

|      | 25.2.8  | RAM Retaining Area Specifying Register (RAMKP)                       | 998  |

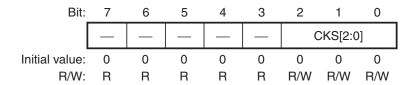

|      | 25.2.9  | Deep Standby Oscillation Settling Clock Select Register (DSCNT)      | 999  |

|      | 25.2.10 | Deep Standby Cancel Source Flag Register (DSFR)                      | 1000 |

| 25.3 | Operat  | ion                                                                  | 1002 |

|      | 25.3.1  | Sleep Mode                                                           | 1002 |

|      | 25.3.2  | Software Standby Mode                                                | 1003 |

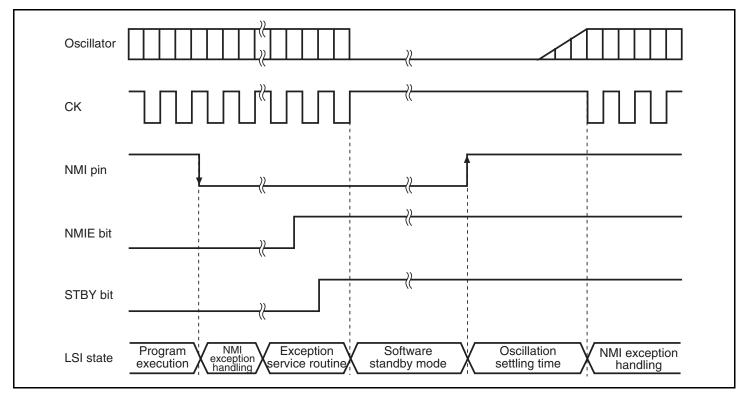

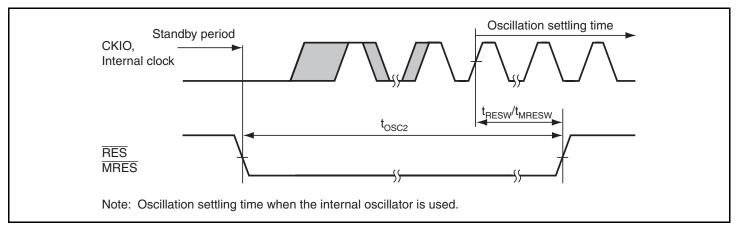

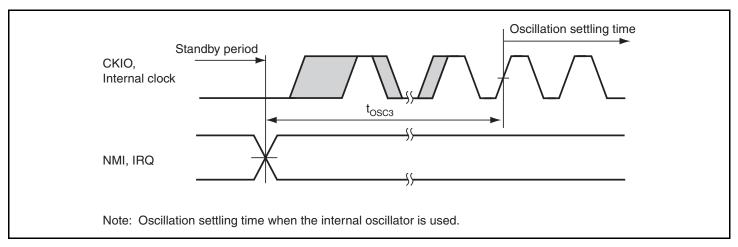

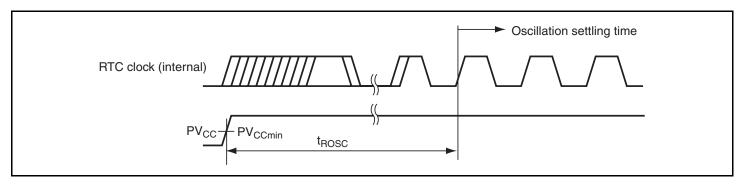

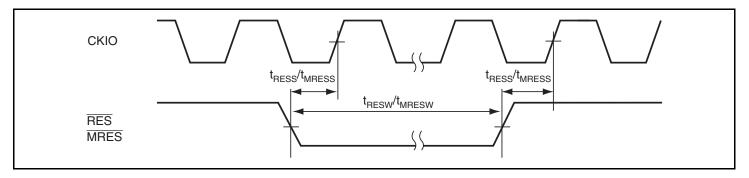

|      | 25.3.3  | Software Standby Mode Application Example                            | 1005 |

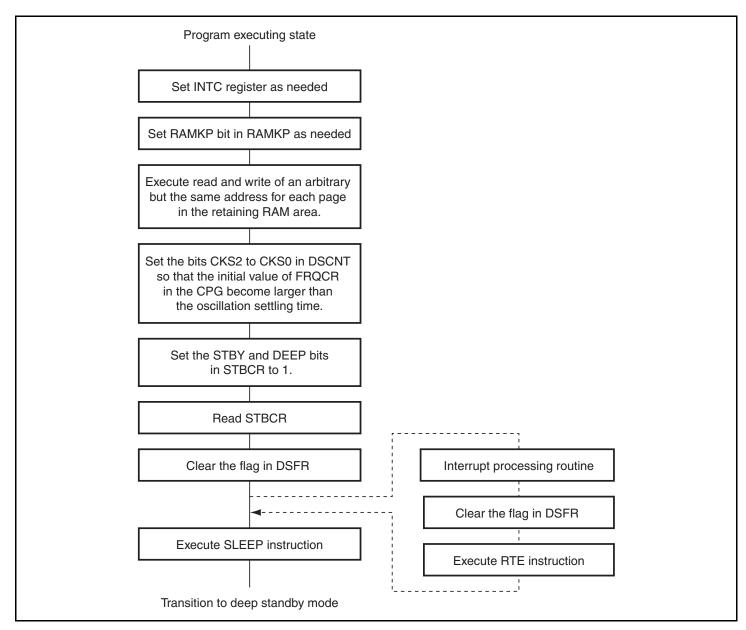

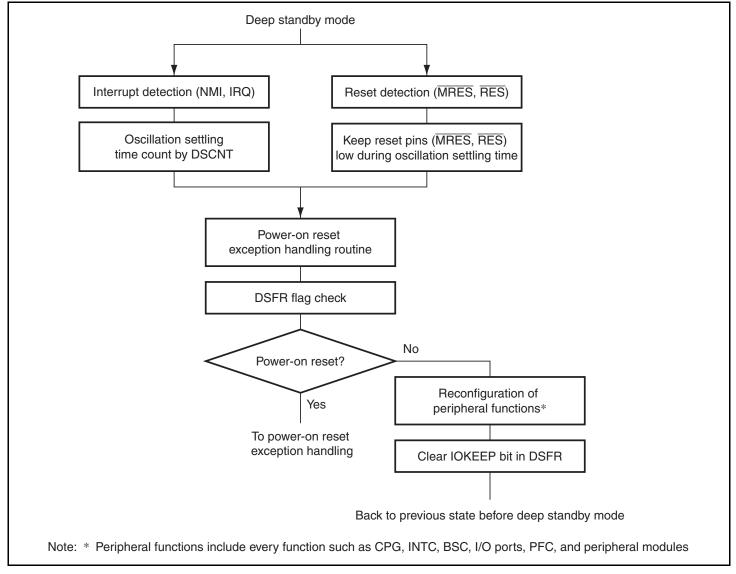

|      | 25.3.4  | Deep Standby Mode                                                    | 1006 |

|      | 25.3.5  | Module Standby Function                                              | 1011 |

| 25.4 | Usage   | Note                                                                 | 1011 |

|      | 25.4.1  | Note on Setting Registers                                            | 1011 |

|      | 25.4.2  | Note on Canceling Standby Mode when an External Clock is being Input | 1011 |

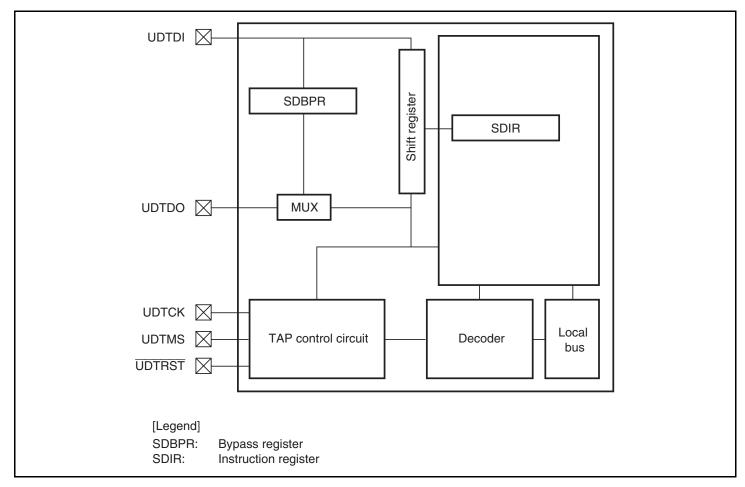

| Sect | ion 26  | User Debugging Interface (H-UDI)                                     | 1013 |

|      |         | es                                                                   |      |

| 26.2 |         | Output Pins                                                          |      |

| 26.3 |         | er Descriptions                                                      |      |

|      | _       | Bypass Register (SDBPR)                                              |      |

|      |         | Instruction Register (SDIR)                                          |      |

| 26.4 |         | ion                                                                  |      |

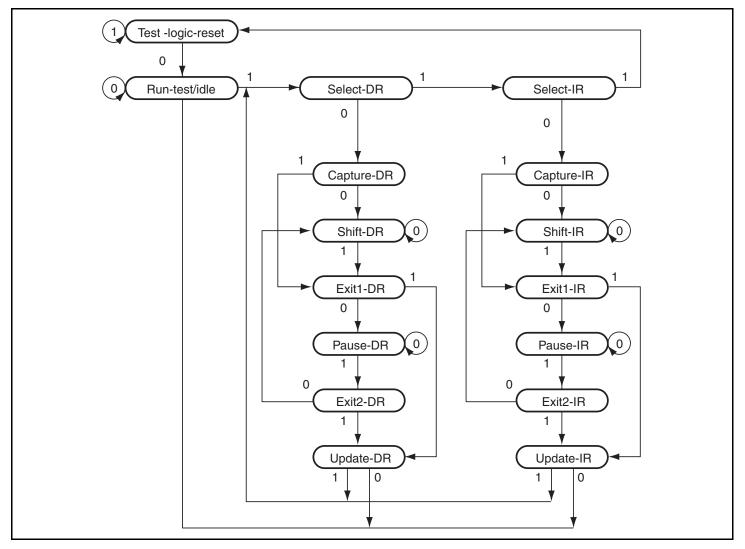

|      | 26.4.1  | TAP Controller                                                       | 1017 |

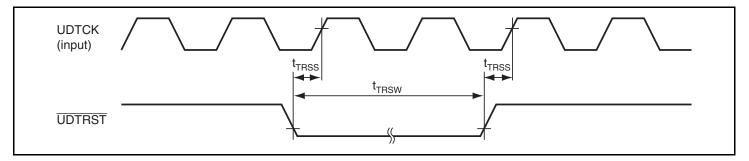

|      | 26.4.2  | Reset Types                                                          | 1018 |

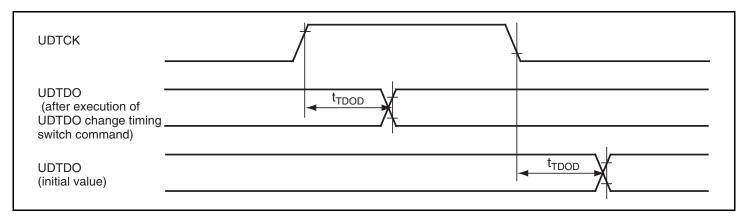

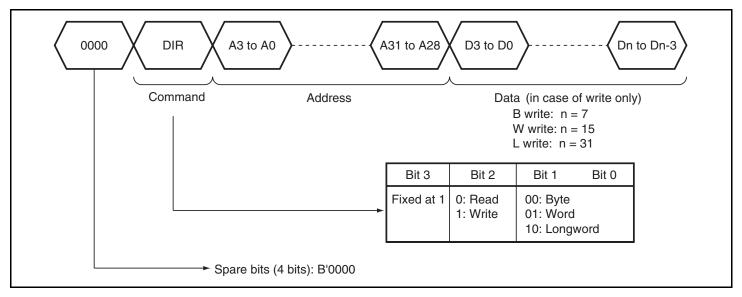

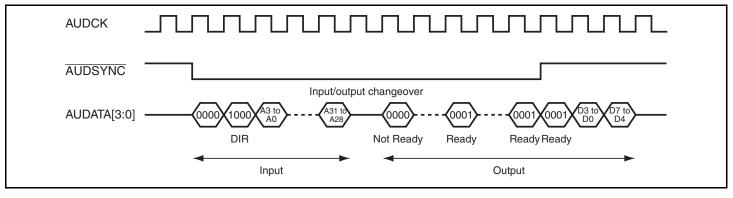

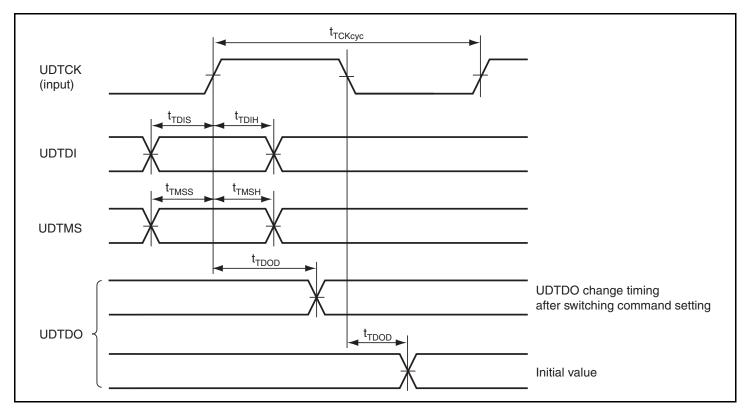

|      | 26.4.3  | UDTDO Output Timing                                                  | 1018 |

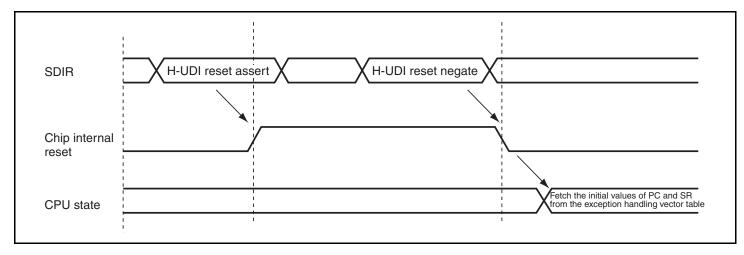

|      |         | H-UDI Reset                                                          |      |

|      | 26.4.5  | H-UDI Interrupt                                                      | 1019 |