# Contents

| eatures ·····                      | 1  |

|------------------------------------|----|

| Applications                       | 1  |

| Selection Guidelines for RESET and |    |

| he Watchdog Timer·····             | 1  |

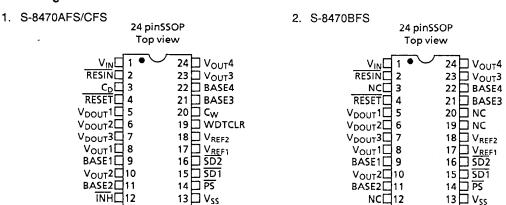

| Pin Assignment                     | 1  |

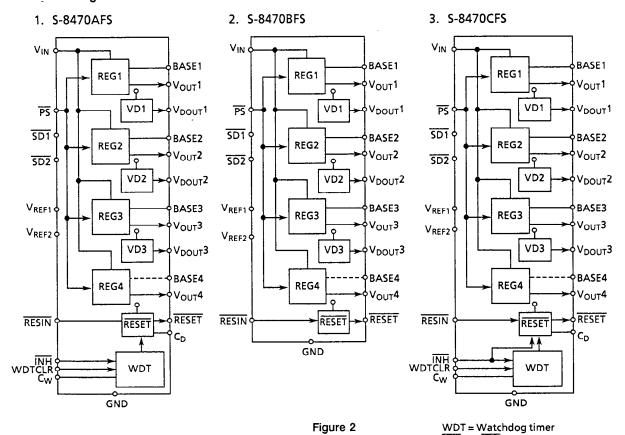

| Block Diagram······                | 2  |

| Options                            | 2  |

| Pin Description                    | 3  |

| Absolute Maximum Ratings           | 3  |

| Electrical Characteristics         | 4  |

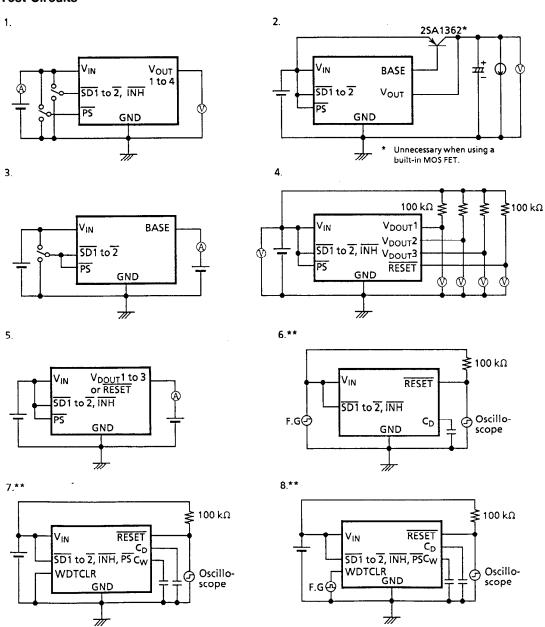

| Test Circuits                      | 6  |

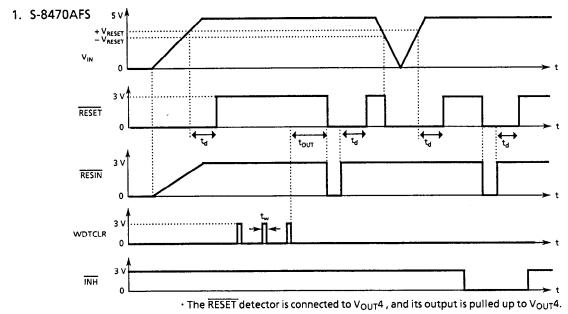

| Operation Timing Chart             | 7  |

| Operation                          | 8  |

| Transient Response······           | 11 |

| <del>-</del>                       | 34 |

| Application Circuit ······         | 41 |

|                                    | 41 |

|                                    | 42 |

| Markings ······                    | 42 |

| Taping                             | 43 |

### CMOS POWER MANAGEMENT IC

The S-8470 Series is a CMOS power management IC for portable telephones. It contains a watchdog timer circuit, in addition to four series-type voltage regulators and four voltage detectors.

#### Features

- · Four built-in high-precision voltage regulators with external transistors, whose accuracies are ±2%. REG4 can have a MOS FET built-in.

- These output voltages can be selected by 0.1 V step between 2 V and 6 V.

- · Four built-in high-precision voltage detectors, whose accuracies are ±2%.

- One of them can set a delay time with an external capacitor. (S-8470AFS/CFS)

- These detection voltages can be selected by 0.1 V step between 2 V and 6 V.

- The detection pins are selected from  $V_{\mbox{\scriptsize IN}}$  or  $V_{\mbox{\scriptsize OUT}}$  by option.

- Built-in watchdog timer circuit that detects MPU runaway and generates a RESET signal: Can set the time out period with an external capacitor (5 s max.) (S-8470AFS/CFS)

- · Low current consumption

- All voltage regulators and voltage detectors with the exception of RESET can be powered on/off. In the S-8470CFS, RESET can be powered on/off.

- There are 3 different type in the series, S-8470AFS/BFS/CFS, whose functions vary according to RESET signal and the watchdog timer.

- · 24-pin shrink SOP package (pin pitch : 0.8 mm)

#### Applications

- · Portable telephone

- · Next generation cordlessphone

- · Two-way radio equipment

- · Other portable equipment

#### ■ Selection Guidelines for RESET and the Watchdog Timer

Table 1

| Name of series | Functions                                                                                                         |

|----------------|-------------------------------------------------------------------------------------------------------------------|

| S-8470AFS      | Always operates RESET: (Delay time can be specified using an external capacitor) Can shutdown the watchdog timer. |

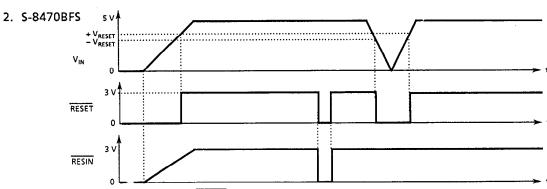

| S-8470BFS      | Always operates RESET.<br>No watchdog timer.                                                                      |

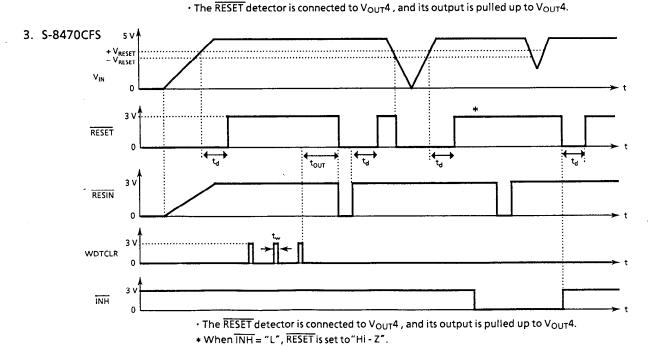

| S-8470CFS      | Can shutdown RESET: (Delay time can be specified using an external capacitor) and a watchdog timer.               |

#### Pin Assignment

Figure 1

#### Block Diagram

#### Options

Table 2

SD1and SD2 = Shutdown pin

| Item                                                                            | Applicable pin                        | Contents of option                                                                                      |

|---------------------------------------------------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------|

|                                                                                 | VD1                                   | One of V <sub>IN</sub> , V <sub>OUT</sub> 1, V <sub>OUT</sub> 2, V <sub>OUT</sub> 3, V <sub>OUT</sub> 4 |

| Pin to detect the voltage of                                                    | VD2                                   | One of V <sub>IN</sub> , V <sub>OUT</sub> 1, V <sub>OUT</sub> 2, V <sub>OUT</sub> 3, V <sub>OUT</sub> 4 |

| voltage detectors                                                               | VD3                                   | One of V <sub>IN</sub> , V <sub>OUT</sub> 1, V <sub>OUT</sub> 2, V <sub>OUT</sub> 3, V <sub>OUT</sub> 4 |

|                                                                                 | RESET                                 | One of V <sub>IN</sub> , V <sub>OUT</sub> 1, V <sub>OUT</sub> 2, V <sub>OUT</sub> 3 V <sub>OUT</sub> 4  |

|                                                                                 | VD1                                   | "L" or "Hi-Z"                                                                                           |

| Output voltage of voltage                                                       | VD2                                   | "L" or "Hi-Z"                                                                                           |

| detectors during shutdown                                                       | VD3                                   | "L" or "Hi-Z"                                                                                           |

|                                                                                 | RESET**                               | "L" or "Hi-Z"                                                                                           |

|                                                                                 | SD1*                                  | Shutdown of REG1, REG2, REG3, REG4, VD1, VD2, VD3                                                       |

| Shutdown control input                                                          | SD2*                                  | Shutdown of REG1, REG2, REG3, REG4, VD1, VD2, VD3                                                       |

| Shutdown prohibition                                                            |                                       | Shutdown prohibition of REG1, REG2, REG3, REG4, VD1, VD2, VD3                                           |

| Power transistor of voltage regulators                                          | REG4                                  | Internal or External                                                                                    |

| Output voltage of voltage regulators and detection voltage of voltage detectors | VD1 to VD3,<br>RESET,<br>REG1 to REG4 | Can be set freely by 0.1 V step between 2 V and 6 V (Accuracy: ±2%)                                     |

<sup>\*</sup> It cannot be allowed that shutdown of any circuit is controlled by two or more SD inputs.

Please contact our sales department on other options than Table 1.

<sup>\*\*</sup> RESET signal is output when INH = "L" (the S-8470CFS only)

# ■ Pin Description

Table 3

| Name                                          | Description                                                                                                                           | Shutdown        |  |  |  |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|

| VIN                                           | Positive power input of REG1 to REG4                                                                                                  |                 |  |  |  |

| BASE1                                         | Base current sink terminal to connect to the base of the external PNP transistor of REG1                                              | VIN             |  |  |  |

| V <sub>OUT</sub> 1                            | REG1 output                                                                                                                           |                 |  |  |  |

| BASE2                                         | Base current sink terminal to connect to the base of the external PNP transistor of REG2                                              | V <sub>IN</sub> |  |  |  |

| V <sub>OUT</sub> 2                            | REG2 output                                                                                                                           | Hi-Z            |  |  |  |

| BASE3                                         | Base current sink terminal to connect to the base of the external PNP transistor of REG3                                              | V <sub>IN</sub> |  |  |  |

| V <sub>OUT</sub> 3                            | REG3 output                                                                                                                           | Hi-Z            |  |  |  |

| BASE4                                         | Base current sink terminal to connect to the base of the external PNP transistor of REG4 (NC when using the built-in MOS FET of REG4) | VIN             |  |  |  |

| V <sub>OUT</sub> 4                            | REG4 output                                                                                                                           | Hi-Z            |  |  |  |

| SD1 to SD2                                    | Shutdown control signals input of REG1 to REG4 and VD1 to VD3                                                                         |                 |  |  |  |

| PS                                            | Current consumption alternative signal input of REG1 to REG4                                                                          |                 |  |  |  |

| V <sub>DOUT</sub> 1 to<br>V <sub>DOUT</sub> 3 | VD1 to VD3 Nch opendrain output                                                                                                       | L or Hi-Z       |  |  |  |

| RESET                                         | Nch opendrain output of voltage detector (VD) for generating RESET                                                                    | L or Hi-Z       |  |  |  |

| RESIN                                         | Compulsory RESET signal input of VD for generating RESET                                                                              |                 |  |  |  |

| C <sub>D</sub> *                              | Output terminal to connect the capacitor for output signal delay of VD for generating RESET                                           | L               |  |  |  |

| WDCLR*                                        | Clear signal input for watchdog timer (WDT)                                                                                           |                 |  |  |  |

| C <sub>W</sub> *                              | Output terminal to connect the capacitor for setting timeout period of WDT                                                            | L               |  |  |  |

| INH*                                          | S-8470AFS: Shutdown control signal input for the WDT S-8470CFS: Shutdown control signal input for the WDT and VD for generating RESET |                 |  |  |  |

| V <sub>REF1</sub> , V <sub>REF2</sub>         | Reference voltage output                                                                                                              |                 |  |  |  |

| GND                                           | Ground                                                                                                                                |                 |  |  |  |

<sup>\*</sup> Excluding the S-8470BFS

# ■ Absolute Maximum Ratings

Table 4

(Unless otherwise specified : Ta = 25°C)

| Symbol            | Applicable terminal                                                                     | Ratings                                                                                                                                                    | Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>IN</sub>   | V <sub>IN</sub> , SD1 to SD2, PS, RESIN,<br>WDTCLR, BASE1 to BASE4, INH                 | V <sub>SS</sub> – 0.3 to 12                                                                                                                                | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| V <sub>OUT</sub>  | V <sub>OUT</sub> 1, V <sub>OUT</sub> 2, V <sub>OUT</sub> 3, V <sub>OUT</sub> 4          | V <sub>SS</sub> – 0.3 to V <sub>IN</sub> + 0.3                                                                                                             | ٧                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| V <sub>DOUT</sub> | V <sub>DOUT</sub> 1 to V <sub>DOUT</sub> 3, RESET                                       | V <sub>SS</sub> - 0.3 to 12                                                                                                                                | ٧                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| lout              | V <sub>OUT</sub> 4                                                                      | 100                                                                                                                                                        | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PD                |                                                                                         | 650                                                                                                                                                        | mW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Topr              |                                                                                         | - 40 to +85                                                                                                                                                | °C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| T <sub>stq</sub>  |                                                                                         | - 40 to + 125                                                                                                                                              | ů                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                   | V <sub>IN</sub> Vout V <sub>DOUT</sub> I <sub>OUT</sub> P <sub>D</sub> T <sub>opr</sub> | V <sub>IN</sub> , SD1 to SD2, PS, RESIN, WDTCLR, BASE1 to BASE4, INH  VOUT VOUT1, VOUT2, VOUT3, VOUT4  VDOUT VDOUT1 to VDOUT3, RESET  IOUT VOUT4  PD  Topr | V <sub>IN</sub> V <sub>IN</sub> , SD1 to SD2, PS, RESIN, WDTCLR, BASE1 to BASE4, INH         V <sub>SS</sub> = 0.3 to 12           V <sub>OUT</sub> V <sub>OUT</sub> 1, V <sub>OUT</sub> 2, V <sub>OUT</sub> 3, V <sub>OUT</sub> 4         V <sub>SS</sub> = 0.3 to V <sub>IN</sub> + 0.3           V <sub>DOUT</sub> V <sub>DOUT</sub> 1 to V <sub>DOUT</sub> 3, RESET         V <sub>SS</sub> = 0.3 to 12           I <sub>OUT</sub> V <sub>OUT</sub> 4         100           P <sub>D</sub> 650           T <sub>Opr</sub> -40 to +85 |

<sup>\*</sup> When using a built-in MOS FET

DO NOT APPLY the voltage to  $V_{REF1}$ ,  $V_{REF2}$ ,  $C_W^{\star\star}$ , and  $C_D^{\star\star}$ . (\*\* Excluding the S-8470BFS)

#### **Electrical Characteristics**

1. General

Table 5

(Unless otherwise specified: Ta = 25°C)

|                           |     |                        |                     | (onless of                                                             |          | oc spec |      | 14 - 2 | <del>,</del>    |

|---------------------------|-----|------------------------|---------------------|------------------------------------------------------------------------|----------|---------|------|--------|-----------------|

| Parameter                 |     | Symbol                 | Applicable terminal | Test conditions                                                        | Min.     | Тур.    | Max. | Unit   | Test<br>circuit |

|                           |     | I <sub>REGON</sub>     | REG1 to 4           | SD1 to 2 = PS = "H"<br>V <sub>IN</sub> = 6 V                           | _        | 6.3     | 9    | μΑ     |                 |

|                           |     | I <sub>REGPS</sub>     | REG1 to 4           | SD1 to 2 = "H", PS = "L"<br>V <sub>IN</sub> = 6 V                      | _        | 1.4     | 2    | μA     |                 |

|                           | Ī   | IREGOF                 | REG1 to 4           | SD1 to 2 = "L", V <sub>IN</sub> = 6 V                                  | <b>—</b> | _       | 0.1  | μA     |                 |

|                           |     | IVDON                  | VD1 to 3            | SD1 to 2 = "H", V <sub>IN</sub> = 6 V                                  | <b> </b> | 1.0     | 2.0  | μA     |                 |

|                           |     | lvdof                  | VD1 to 3            | SD1 to 2 = "L", V <sub>IN</sub> = 6 V                                  |          | _       | 0.1  | μA     |                 |

|                           |     | IRESON                 | RESET               | INH = "H", V <sub>IN</sub> = 6 V                                       | _        | 1.7     | 3.5  | μĀ     | }               |

| Current                   |     | I <sub>RESOF</sub> **  | RESET               | SD1 to 2 = INH = "L"<br>V <sub>IN</sub> = 6 V                          | _        | _       | 0.5  | μΑ     |                 |

| $consumption \\ *$        |     | WDTON***               | WDT                 | INH = "H", V <sub>IN</sub> = 6 V                                       | _        | 1.7     | 3.5  | μΑ     | 1               |

|                           |     | l <sub>WDTOF</sub> *** | WDT                 | INH = "L", V <sub>IN</sub> = 6 V                                       | _        | _       | 0.3  | μА     | ] `             |

|                           |     | IREFON                 | VIN                 | V <sub>IN</sub> = 6 V                                                  | _        | 4.0     | 7.0  | μА     |                 |

|                           |     | REFOF****              | V <sub>IN</sub>     | SD1 to 2 = INH = "L"<br>V <sub>IN</sub> = 6 V                          | _        | _       | 0.2  | μΑ     |                 |

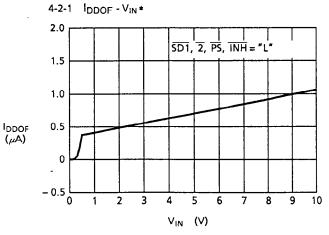

|                           | Ī   | IDDOF                  | V <sub>IN</sub>     | SD1 to 2 = INH = PS = "L"                                              | -        | _       | **** | μΑ     |                 |

| S-8470A                   | AFS | l <sub>DD1</sub>       | V <sub>IN</sub>     | SD1 to 2 = PS = "H", V <sub>IN</sub> = 6 V                             |          | 36      | 56   | μΑ     |                 |

| S-84700                   | CFS | I <sub>DD2</sub>       | V <sub>IN</sub>     | $\overline{SD1}$ to $2 = "H", PS = "L", V_{IN} = 6 V$                  | _        | 16      | 28   | μΑ     |                 |

| 5-8470                    | 3FS | l <sub>DD1</sub>       | V <sub>IN</sub>     | $SD1 \text{ to } 2 = PS = "H", V_{IN} = 6 \text{ V}$                   | _        | 34      | 53   | μA     | ]               |

|                           |     | I <sub>DD2</sub>       | V <sub>IN</sub>     | $\overline{SD1}$ to $2 = "H"$ , $\overline{PS} = "L"$ , $V_{IN} = 6 V$ |          | 14      | 25   | μΑ     |                 |

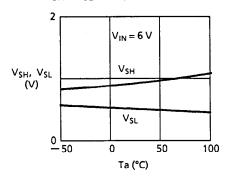

| Input threshol            | d   | V <sub>SL</sub>        | SD1 to 2, PS,       | V <sub>IN</sub> = 6 V "L"                                              |          |         | 0.3  | V      | 2, 4            |

| voltage                   |     | V <sub>SH</sub>        | RESIN, INH          | V <sub>IN</sub> = 6 V "H"                                              | 2.4      |         |      | V      | <u> </u>        |

| Operating inpu<br>voltage | ut  | V <sub>OP</sub>        | V <sub>IN</sub>     |                                                                        | 2.0      |         | 10   | V      | 1               |

- Current consumption per voltage regulator or detector when REG1 through 4 and  $\overline{\text{SD1}}$  and  $\overline{\text{2}}$ are connected to the V<sub>IN</sub> (excluding the BASE current of the external PNP transistor)

- Excluding S-8470AFS/BFS

Excluding S-8470BFS

- Excluding S-8470AFS

- Refer to the following current consumption calculation method (at the time of shutdown)(S-8470CFS).

At the time of shutdown (when  $\overline{SD1}$  to  $\overline{2}$  = "L" and  $\overline{INH}$  = "L"): When the IC is not provided with a shutdown prohibition circuit:

IREGOF × 4 + IVDOF × 3 + IRESOF + IWDTOF + IREFOF

During operation (when  $\overline{SD1}$  to  $\overline{2} = \overline{INH} = "H"$ ):

I<sub>REGON</sub> × 4 + I<sub>VDON</sub> × 3 + I<sub>RESON</sub> + I<sub>WDTON</sub> + I<sub>REFON</sub>

#### 2. Voltage regulator

Table 6

| (Unless otherwise specified : Ta = 25°C) |                              |                                             |                                                                              |          |       |       |             |                 |

|------------------------------------------|------------------------------|---------------------------------------------|------------------------------------------------------------------------------|----------|-------|-------|-------------|-----------------|

| Parameter                                | Symbol                       | Applicable terminals                        | Test conditions                                                              | Min.     | Тур.  | Max.  | Unit        | Test<br>circuit |

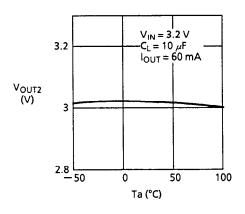

|                                          | V <sub>OUT</sub> 1           | V <sub>OUT</sub> 1                          | $V_{IN} = 3.2 \text{ V}, I_{OUT} = 60 \text{ mA}$                            | 2.94     | 3.00  | 3.06  | ٧           |                 |

| Output voltage                           | V <sub>OUT</sub> 2           | V <sub>OUT</sub> 2                          | $V_{IN} = 3.2 \text{ V}, I_{OUT} = 60 \text{ mA}$                            | 2.94     | 3.00  | 3.06  | >           |                 |

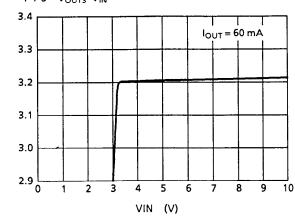

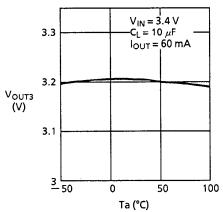

| Output vortage                           | V <sub>OUT</sub> 3           | V <sub>OUT</sub> 3                          | $V_{IN} = 3.4 \text{ V}, I_{OUT} = 60 \text{ mA}$                            | 3.136    | 3.200 | 3.264 | V           |                 |

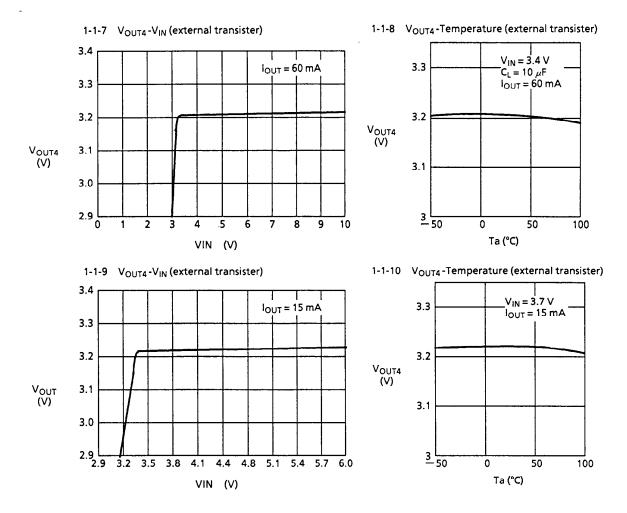

|                                          | V <sub>OUT</sub> 4*          | V <sub>OUT</sub> 4                          | $V_{IN} = 3.7 \text{ V}, I_{OUT} = 15 \text{ mA}$                            | 3.136    | 3.200 | 3.264 | V           |                 |

| Output voltage at the time of shutdown   | ***<br>V <sub>OSD1~4</sub>   | V <sub>OUT</sub> 1 to 4                     | V <sub>IN</sub> = 10 V, Load:1 MΩ                                            |          |       | 0.1   | <b>&gt;</b> |                 |

| I/O voltage<br>difference*               | V <sub>diff</sub>            | V <sub>OUT</sub> 4                          | I <sub>OUT</sub> = 15 mA                                                     | <b>—</b> | 0.2   | 0.35  | ٧           |                 |

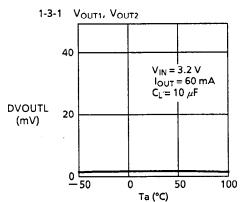

|                                          | ΔV <sub>OUTL</sub> 1         | V <sub>OUT</sub> 1                          | V <sub>IN</sub> = 3.2 to 4.8 V<br>I <sub>OUT</sub> = 60 mA                   | _        | 20    | 40    | m۷          |                 |

|                                          | ΔV <sub>OUTL</sub> 2         | V <sub>OUT</sub> 2                          | V <sub>IN</sub> = 3.2 to 4.8 V<br>l <sub>OUT</sub> = 60 mA                   |          | 20    | 40    | m۷          |                 |

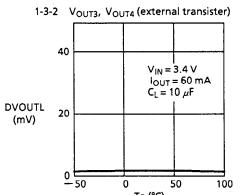

| Line regulation                          | ΔV <sub>OUTL</sub> 3         | V <sub>OUT</sub> 3                          | V <sub>IN</sub> = 3.4 to 4.8 V<br>I <sub>OUT</sub> = 60 mA                   | _        | 20    | 40    | mV          | 2               |

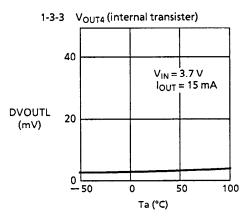

|                                          | ΔV <sub>ΟUΤL</sub> 4*        | V <sub>OUT</sub> 4                          | $V_{IN} = 3.7 \text{ to } 4.8 \text{ V}$<br>$I_{OUT} = 15 \text{ mA}$        | <b> </b> | 20    | 40    | mV          |                 |

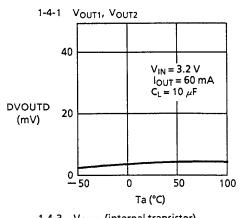

|                                          | ΔV <sub>OUTD</sub> 1         | V <sub>OUT</sub> 1                          | V <sub>IN</sub> = 3.2 V<br>I <sub>OUT</sub> = 1 to 60 mA                     | _        | 25    | 50    | mV          |                 |

| Load                                     | ΔV <sub>OUTD</sub> 2         | V <sub>OUT</sub> 2                          | V <sub>IN</sub> = 3.2 V<br>l <sub>OUT</sub> = 1 to 60 mA                     | _        | 25    | 50    | mV          |                 |

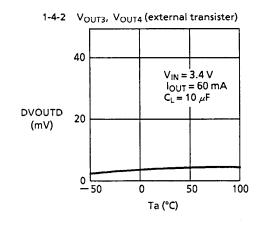

| regulation                               | ΔV <sub>ΟυΤD</sub> 3         | V <sub>OUT</sub> 3                          | V <sub>IN</sub> = 3.4 V<br>I <sub>OUT</sub> = 1 to 60 mA                     |          | 25    | 50    | m∨          |                 |

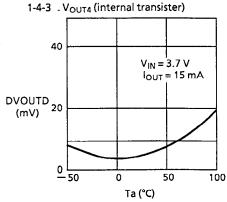

|                                          | ΔV <sub>OUTD</sub> 4*        | V <sub>OUT</sub> 4                          | $V_{IN} = 3.7 \text{ V}$<br>$I_{OUT} = 50 \mu\text{A to } 15 \text{mA}$      | _        | 25    | 50    | mV          |                 |

| Output voltage temp. coefficient         | ∆V <sub>OUT</sub><br>∆Ta     | V <sub>OUT</sub> 1 to<br>V <sub>OUT</sub> 4 | Ta = -40°C to +85°C                                                          | _        | **    | _     | mV/°C       |                 |

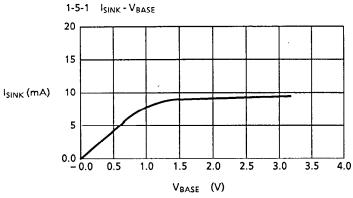

| Base sink<br>current                     | ***<br><sup>1</sup> SINK 1-4 | BASE1 to<br>BASE4                           | $V_{IN} = 3.2 \text{ V}, V_{DS} = 2 \text{ V}$<br>Base current of transistor | 1        | _     |       | mA          | 3               |

2SA1362 or one of whose  $V_{sat}$  is less than 0.1 V ( $I_{OUT}$  = 60 mA) is used as an external transistor.

\* When using a built-in MOS FET.

The specification when using an external transistor is the same as V<sub>OUT</sub>3.

\*\* Equation parameter :  $\pm 0.71 \times \frac{V_{OUT}1 \text{ to } V_{OUT}4 \text{ (typ.)}}{5.0}$

#### 3. Voltage detector

Table 7

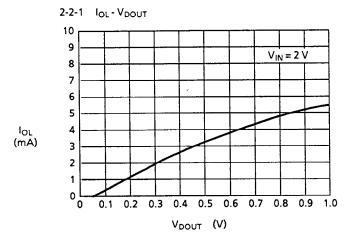

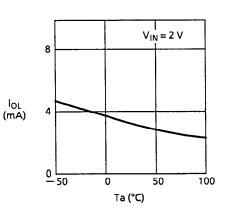

(Unless otherwise specified: Ta = 25°C) Applicable Test Test conditions Min. Parameter Symbol Typ. Max. Unit circuit terminals - V<sub>DET1</sub> V<sub>DOUT</sub>1 3.234 3.300 3.366 Detection - V<sub>DET2</sub> V<sub>DOUT</sub>2 3.724 3.800 3.876 V voltage - V<sub>DET3</sub> V<sub>DOUT</sub>3 3.626 3.700 3.774 ٧ RESET 2.94 3.00 3.06 ٧ - V<sub>RESET</sub> + VDET1 3.329 3.465 3.601 V V<sub>DOUT</sub>1 3.847 3.990 4.133 ٧ + V<sub>DET2</sub> V<sub>DOUT</sub>2 Release voltage + V<sub>DET3</sub> V<sub>DOUT</sub>3 3.743 3.885 4.027 ٧ + V<sub>RESET</sub> RESET 2.981 3.100 3.219 ٧ 4  $\triangle - V_{DET} V_{DOUT} 1 to 3,$ Detection vol. Ta = -40°C to +85°C mV/°C temp. coefficient ∆Ta RESET  $V_{DS} = 0.5 \text{ V}, V_{1N} = 2.0 \text{ V}$ Sink current loL 1.00 1.60 mΑ V<sub>DOUT</sub>1 to 3 RESET  $V_{DS} = 10 \text{ V}, \ V_{IN} = 10 \text{ V}$ 5 Leakage current 0.1  $\mu A$ LEAK Delay time\*\* RESET  $C_D = 4.7 \text{ nF}$ 31 45 59 6 ms td

\* Equation parameter:  $\pm 0.5 \times \frac{-V_{DET}1 \text{ to } -V_{DET}3 \text{ (typ.) or } -V_{RESET} \text{ (typ.)}}{4.2}$

<sup>\*\*\*</sup>  $I_{SINK4}$  and  $I_{BLEAK4}$  are not specified when using a built-in MOS FET.

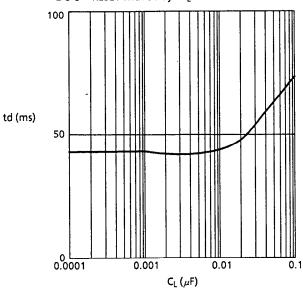

<sup>\*\*</sup> Equation parameter for the delay time (ms): 9.6 x capacitor (nF) (Excluding the S-8470BFS)

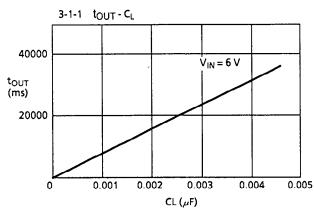

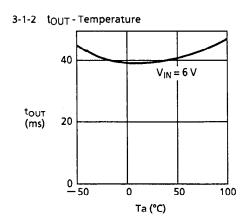

#### 4. Watchdog timer (Excluding the S-8470BFS)

Table 8

|                                 |                 |                      | (0                           | niess othe | erwise s | pecified | d: Ta = | 25°C)           |

|---------------------------------|-----------------|----------------------|------------------------------|------------|----------|----------|---------|-----------------|

| Parameter                       | Symbol          | Applicable terminals | Test conditions              | Min.       | Тур.     | Max.     | Unit    | Test<br>circuit |

| Timeout period*                 | tour            | RESET                | C <sub>W</sub> = 4.7 nF      | 31         | 45       | 59       | ms      | 7               |

| Input threshold V <sub>SL</sub> | V <sub>SL</sub> |                      | V <sub>IN</sub> = 3.3 V, "L" | _          | -        | 0.3      | >       |                 |

| voltage                         | V <sub>SH</sub> | WDTCLR               | V <sub>IN</sub> = 3.3 V, "H" | 1.5        | _        | _        | >       | 8               |

| Input pulse width               | t <sub>W</sub>  | WDTCLR               | V <sub>IN</sub> = 3.3 V, "H" | 50         | _        | 1000     | μ\$     | l               |

<sup>\*</sup> Equation parameter for the timeout period (ms): 9.6 × capacitor (nF)

# Test Circuits

Figure 3

\*\* Excluding the S-8470BFS

# Operation Timing Chart

Figure 4

#### Operation

The S-8470 Series consists of four voltage regulators, three voltage detectors, a shutdown input circuit, a voltage detector with delay circuit for generating RESET, and a watchdog timer. (The S-8470BFS is provided with neither a delay circuit for RESET nor a watchdog timer)

1. High-precision voltage regulators (REG1, REG2, REG3, and REG4)

The S-8470 Series contains four voltage regulators, each of whose output voltages can set independently by 0.1 V step between 2 V and 6 V. The accuracy of their output voltages is  $\pm 2\%$ .

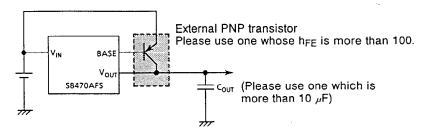

REG1, REG2 and REG3: Can be used as voltage regulator with large output current, by connecting a PNP transistor externally

REG4: Can be selected by option from large output current type by a PNP transistor and built-in MOS FET type.

The S-8470AFS has a reference voltage circuit. It outputs 1.2 V of reference voltage to  $V_{REF1}$ ,  $V_{REF2}$  terminal, which required 0.1  $\mu$ F of capacitor. This voltage is supplied to all the voltage regulators and detectors. This standard voltage circuit halts its function when  $\overline{SD1}$ ,  $\overline{2}$  and  $\overline{INH}$  are all turned "L." This enables the current consumption to be reduced to 0.2  $\mu$ A ( $I_{REF0F}$ ) (in the S-8470AFS, however, the standard voltage circuit is always operating). It becomes shutdown status ( $I_{REG0F} = 0.1 \ \mu$ A max.) when  $\overline{SD1}$  and  $\overline{SD2}$  go low.

The voltage regulator (REG4) with an internal MOSFET turns OFF the M1 transistor; or the voltage regulator with an external PNP transistor cuts off the sink current of the BASE, and shortcircuits between the BASE and the EMITTER of the external transistor via the internal transistor. This enables the output voltage to be set to approximately 0 V.

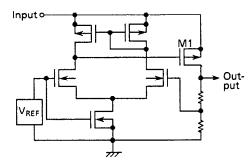

Figure 5 Voltage regulator with built-in MOS FET

$\overline{PS}$  changes the current consumption per voltage regulator: 9  $\mu A$  max. when  $\overline{PS}$  is high, and 2  $\mu A$  max. when  $\overline{PS}$  is low. This terminal is used for reducing current consumption, under voltage being kept to output to REG1 to REG4. Note that output load current (I<sub>OUT</sub>) must be less than 10 mA during 2  $\mu A$  max. mode.

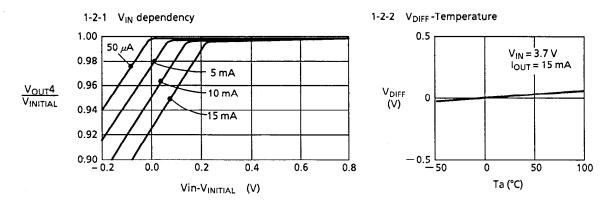

[I/O voltage diffrence V<sub>diff</sub>]

When using REG4 with built-in MOS FET, Vinitial represents the  $V_{OUT}$  when  $V_{IN} = 3.7$  V and  $l_{OUT} = 15$  mA. Inputting (Vinitial +  $V_{diff}$ ) to  $V_{IN}$  causes output of 95% of Vinitial to  $V_{OUT}$  temrinal.

NOTES: Because a short-circuit protection circuit and an thermal shutdown circuit are not mounted in REG1 to REG4, use REG1 to REG4 within the power dissipation of the package.

When using the built-in transistor at V<sub>OUT</sub>4, set PS to "H."

Figure 6 Voltage regulator with external PNP transistor

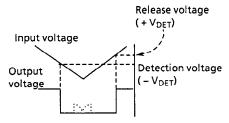

#### 2. Voltage detectors (VD1, VD2, and VD3)

The S-8470 Series has three voltage detectors, each of whose detection terminal is selected by option as Table 8. The power is suppplied from  $V_{IN}$ . The output forms are Nch opendrain. Using shutdown function by  $\overline{SD1}$  to  $\overline{SD2}$  realises a power save system. The output logic of voltage detectors during shutdown is selected from low and high impedance by option (see Table 9).

NOTE: Output is undefined when  $V_{IN}$  terminal voltage is less than 2 V.

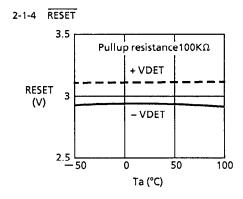

Please use about 100 k $\Omega$  of pull up resistor.

Figure 7 Waveform of voltage detector

Table 9 Detection voltage of voltage detectors

| Voltage detectors | Detected terminal                                             | Detection voltage value  | Output during shutdown |

|-------------------|---------------------------------------------------------------|--------------------------|------------------------|

| VD1 to VD3        | One of V <sub>IN</sub> , V <sub>OUT</sub> 1,                  | Can be set by 0.1 V step | "L" or "Hi-Z"          |

|                   | V <sub>OUT</sub> 2, V <sub>OUT</sub> 3 and V <sub>OUT</sub> 4 | between 2 V and 6 V      | (selected by option)   |

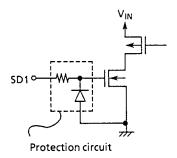

#### 3. Shutdown circuit (applied to SD1 to SD2, PS and INH)

The shutdown circuit, constructed by MOS transistor gate input, is high impedance, therefore input bias current is nearly zero or about 100 pA at most. The S-8470AFS is in shutdown status while  $\overline{\text{SD}}$  is low.

No element exists between power supply  $(V_{IN})$  of this circuit and  $\overline{SD1}$ , and input voltage up to 12 V (maximum rating) can be applied to  $\overline{SD1}$ , regardless of  $V_{IN}$  terminal input voltage.

Do not fail to connect  $\overline{SD1}$  to  $\overline{SD2}$ ,  $\overline{PS}$  and  $\overline{INH}^*$  to  $V_{IN}$ , while the shutdown circuit is not used.

\* Excluding the S-8470BFS

Figure 8 Shutdown input circuit

- **NOTES:** High level is specified at 2.4 V or more, and low level at 0.3 V or less. Some variation may occur depending on the supply voltage.

- ullet Negative voltage should not be applied because the  $V_{\text{IN}}$  terminal and GND terminal are connected by a protection diode.

- Do not float the input terminal or set voltages between levels low and high . This will increase the quiescent current.

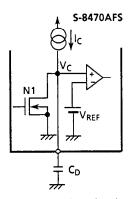

# 4. Voltage detector for generating RESET with delay circuit

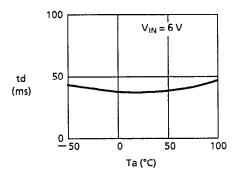

This is a voltage detector for generating  $\overline{RESET}$  with built-in delay circuit, whose output form is Nch opendrain. The voltage detector (VD) for generating  $\overline{RESET}$  runs all the while 2 V or more of voltage is applied to  $V_{IN}$ . The external capacitor ( $C_D$ ) is charged at the constant current by a constant current source ( $I_C$ =125 nA). Comparator output goes high when  $V_C$  is higher than the reference voltage ( $V_{REF}$ ), and a signal is output. The time until  $V_C$  becomes  $V_{REF}$  is the delay time (or undetected momentary power fail time or time-out period) and can be calculated by the following equation. Calculate the capacitor value from the necessary delay time.

Delay time (ms) = delay coefficient \*XC (nF)

\* 6.5≤ delay coefficient≤ 12.6 (9.6 typ., Ta = 25 °C)

Figure 9 Delay circuit

No delay occurs at a fall edge because the external capacitor discharges rapidly through transistor N1. Determine the capacitor value ( $\leq$ 70 nF) from the necessary delay time. Open the terminal if the delay time is unnecessary. (In this case, a propagation delay of about 400  $\mu$ s occurs, depending on the internal parasitic capacity.) If the C<sub>D</sub> terminal is connected to the GND terminal, VD for generating RESET does not release and RESET holds low.

The VD for generating RESET outputs RESET signal under two status besides voltage drop. One status is when RESET goes compulsory low by turning RESIN to low. Another is when the watchdog timer is timed out. In latter case, RESIN returns to high after the delay time to be set after timeout period. RESIN has the same characteristics as that of the input terminal of the shutdown circuit.

S-8470AFS: Regardless of the input state of  $\overline{SD1}$  and  $\overline{2}$ , it runs the VD for generating  $\overline{RESET}$ , as long as 2 V or more is applied to  $V_{IN}$ .

S-8470CFS: Turning  $\overline{\text{INH}}$  to "L" forces the output of the  $\overline{\text{RESET}}$  pin to go either "L" or "Hi-Z." (by option) However, it still functions as a voltage detector. If there is an interrupt forcing  $\overline{\text{RESET}}$  to go "L" while  $\overline{\text{INH}}$  is "L," when  $\overline{\text{INH}}$  goes "H,"  $\overline{\text{RESET}}$  goes "L." Also, when turning  $\overline{\text{SD}}$  1 and 2 to "L," it quits its voltage detection function. This allows the current consumption to be reduced to 0.5  $\mu$ A or less. The output at that time can be selected either "L" or "Hi-Z." (by option)

#### 4.2 Voltage Detector Without A Delay Circuit (S-8470BFS)

Regardless of the input state of  $\overline{\text{SD1}}$  and  $\overline{\text{2}}$ , VD for generating  $\overline{\text{RESET}}$  is operating. This is because VD for generating  $\overline{\text{RESET}}$  is provided with an independent the reference voltage circuit, as long as 2 V or more are applied to the V<sub>IN</sub>. The voltage detector for generating  $\overline{\text{RESET}}$  detects the drop in the voltage and also forces the  $\overline{\text{RESET}}$  output to go low by setting the  $\overline{\text{RESET}}$  pin to "L" (GND).

NOTES: • The RESIN pin has the same characteristic as in the input circuit of the power-off input pin.

- Keep open  $\overline{RESIN}$  when not used, because it is internally pulled up 100 k $\Omega$  to  $V_{IN}$ . Do not apply voltage except for the GND level to the  $C_D$  terminal.

- The output of the VD for generating  $\overline{\text{RESET}}$  is undefined when less than 2 V of voltage is applied to V<sub>IN</sub>. Please use about 100 k $\Omega$  of pull up resistor, because the output level is Nch open-drain.

Table 10 Detection voltage of VD for RESET

|                     |                                                                                                               | -                                            |                                    |

|---------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------|------------------------------------|

| Voltage<br>detector | Detected terminal                                                                                             | Detection voltage value                      | Outputs when the INH pin is "L." * |

| RESET               | One of V <sub>IN</sub> , V <sub>OUT</sub> 1,<br>V <sub>OUT</sub> 2, V <sub>OUT</sub> 3 and V <sub>OUT</sub> 4 | Can be set by 0.1 step<br>between 2 V and 6V | "L" or "Hi-Z" (by option)          |

For only S-8470CFS

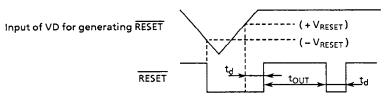

#### 5. Watchdog timer (Excluding the S-8470BFS)

If the voltage of input terminal of VD for generating RESET exceeds release voltage (+V<sub>RESET</sub>), RESET goes high. (A delay is enabled by mounting an external capacitor on the  $C_D$  terminal.) The timer is cleared if a positive pulse is input to the WDTCLR terminal within the timeout period (set by the value of the external capacitor mounted on the  $C_W$  terminal). However, if the positive pulse is not input, RESET goes low. If the voltage of input terminal is more than detection voltage (-V<sub>RESET</sub>), RESET goes high again after the delay time by the external capacitor mounted on the  $C_D$  terminal. This procedure is shown in Figure 10. To clear the watchdog timer, apply a positive pulse with width of 50 to 1000  $\mu$ s at height wave of 2.4 V or more to the WDTCLR terminal. (If a larger pulse is applied, a quiescent current of 1 mA continues to flow for the period beyond 1000  $\mu$ s.) The WDTCLR terminal has the same characteristics as the input circuit of the shutdown terminal. When you want to shut down the watch dog timer, set the INH pin to "L" (GND). In the S-8470CFS, turning the INH pin "L" forces output of the RESET pin to go "L" or "Hi-Z" (by option).

NOTE: • Do not open the C<sub>W</sub> terminal or apply voltage of except for the GND level.

If voltage is applied to the V<sub>IN</sub> terminal, the WDTCLR terminal should not be floated, or a

Timeout period  $t_{OUT}$  (ms) = 9.6 ×  $C_W$  capacitor value (nF,  $\leq$  520 nF)

Figure 10 Timing of the watchdog timer

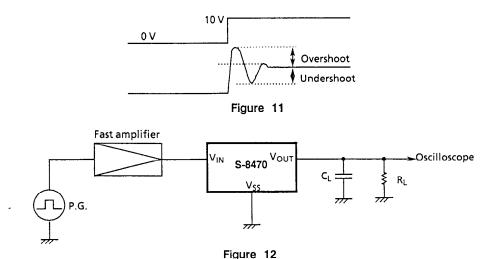

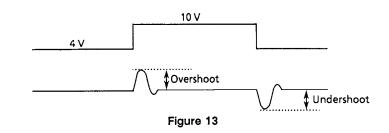

#### ■ Transient Response

#### 1. Transient Response Characteristics at Power ON

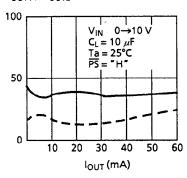

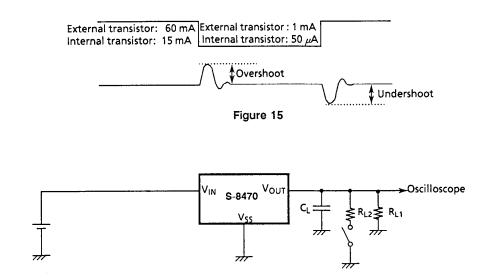

Overshoot or undershoot occurs in the output voltage at the power ON. This section describes parameter dependency characteristics for both overshoot and undershoot. For reference, Figure 12 depicts the measuring circuit.

Table 11 Transient Response Parameter Dependency at Power ON

| Parameter                       | Conditions                                 | Method to decrease overshoot | Method to decrease undershoot |

|---------------------------------|--------------------------------------------|------------------------------|-------------------------------|

| Output current l <sub>OUT</sub> | External: 60 mA max<br>Internal: 15 mA max |                              |                               |

| Load capacitance C <sub>L</sub> |                                            |                              | Increase                      |

| Power supply voltage VIN        | 10 V max                                   |                              |                               |

| Temperature Ta                  | -40 to +85°C                               | Low temperature              | Low temperature               |

# Reference Data When Powering On

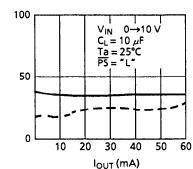

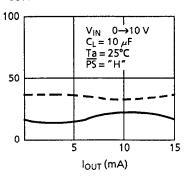

#### 1. I<sub>OUT</sub> dependency

#### 1.1 Vout1, Vout2

Ringing amount (mA)

# 1.2 Vout1, Vout2

Ringing

amount

(mA)

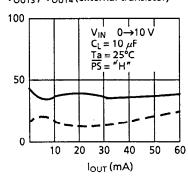

1.3 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transistor)

1.4 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transistor)

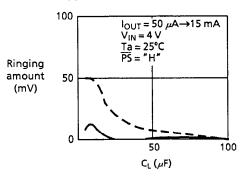

1.5 V<sub>OUT4</sub> (internal transistor)

Overshoot

---- Undershoot

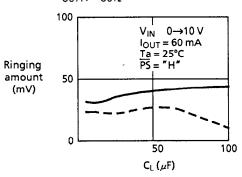

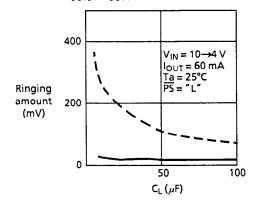

# 2. $C_L$ dependency

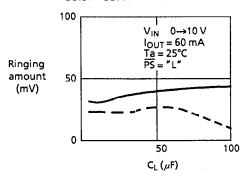

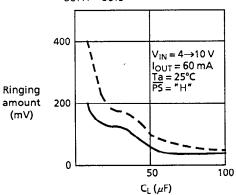

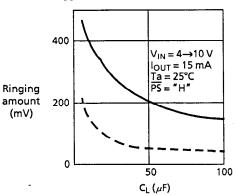

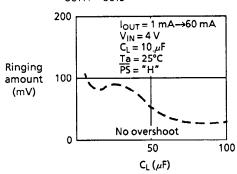

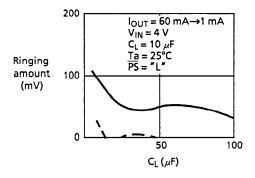

#### 2.1 Vout1, Vout2

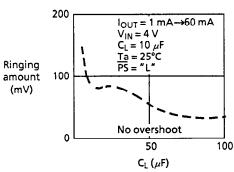

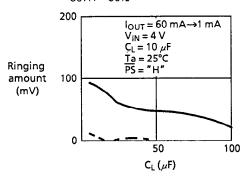

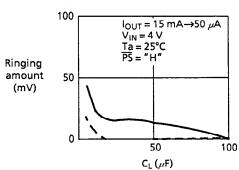

### 2.2 V<sub>OUT1</sub>, V<sub>OUT2</sub>

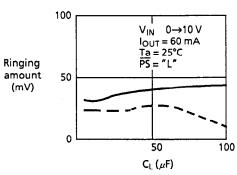

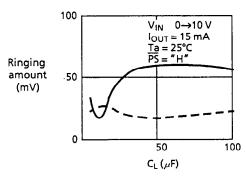

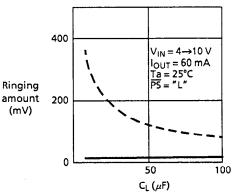

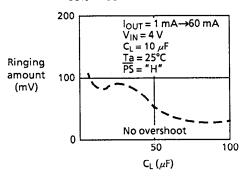

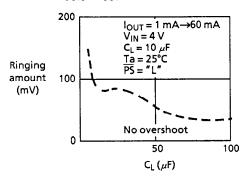

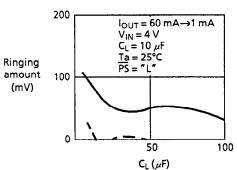

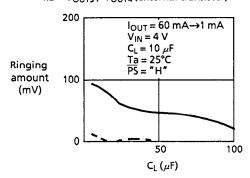

# 2.3 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transistor)

# 2.4 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transistor)

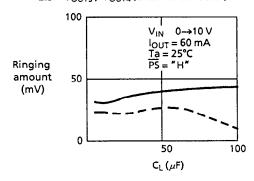

# 2.5 V<sub>OUT4</sub> (internal transistor)

# Overshoot Undershoot

# 3. V<sub>IN</sub> dependency

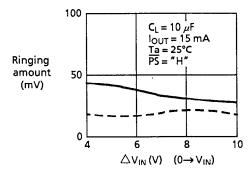

#### 3.1 Vout1, Vout2

# 3.5 V<sub>OUT4</sub> (internal transistor)

#### 3.2 Vout1, Vout2

# 3.4 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transistor)

Overshoot --- Undershoot

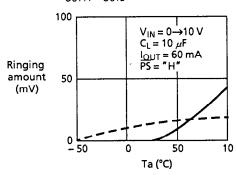

#### 4. Temperature dependency

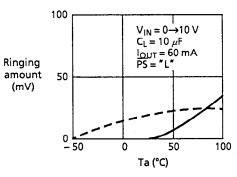

#### 4.1 Vout1, Vout2

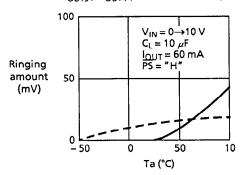

# 4.2 V<sub>OUT1</sub>, V<sub>OUT2</sub>

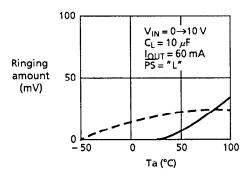

# 4.3 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transistor)

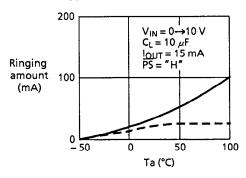

#### 4.4 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transistor)

# 4.5 V<sub>OUT4</sub> (internal transistor)

# Overshoot Undershoot

# 2. Transient Response Characteristics When Input Voltage Varies

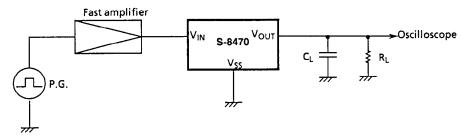

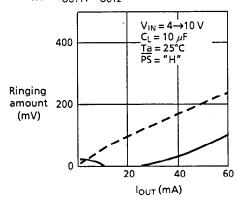

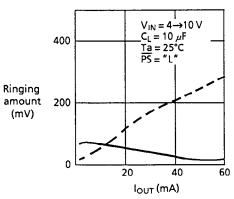

Overshoot or undershoot occurs in the output voltage when the input voltage varies. This section describes parameter dependency characteristics for both overshoot and undershoot. For reference, Figure 14 depicts the measuring circuit.

Figure 14 Measuring Circuit

Table 12 Transient Response Parameter Dependency When Input Voltage Varies

| Parameter               | Parameter Conditions N |                                            | Method to decrease overshoot | Method to decrease undershoot |

|-------------------------|------------------------|--------------------------------------------|------------------------------|-------------------------------|

| Output current          | lout                   | External: 60 mA max<br>Internal: 15 mA max | Decrease                     | Decrease                      |

| Load capacitance        | CL                     |                                            | Increase                     | Increase                      |

| Input voltage variation | $\triangle V_{IN}$     | 4~10 V                                     | Decrease                     | Decrease                      |

| Temperature             | Та                     | - 40 to 85 °C                              |                              | High temperature              |

# Reference Data When Input Voltage Varies

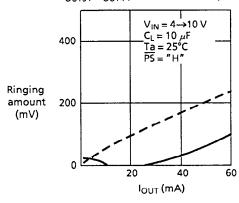

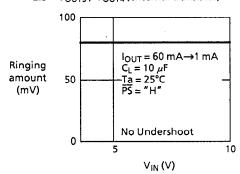

# 1. $I_{OUT}$ dependency ( $V_{IN} = 4 V \rightarrow 10 V$ )

#### 1.1 Vout1, Vout2

#### 1.2 V<sub>OUT1</sub>, V<sub>OUT2</sub>

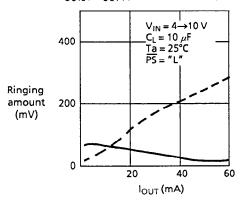

### 1.3 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transistor)

#### 1.4 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transistor)

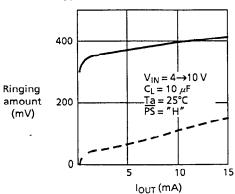

# 1.5 V<sub>OUT4</sub> (internal transistor)

# Overshoot ---- Undershoot

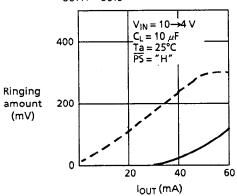

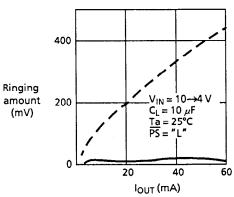

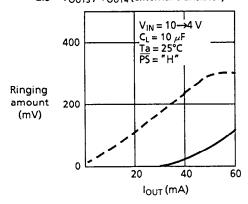

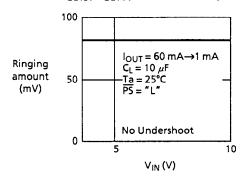

- 2. I<sub>OUT</sub> dependency (V<sub>IN</sub> = 10 V→4 V)

- 2.1 Vout1, Vout2

2.3 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transistor)

2.4 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transistor)

# 2.5 V<sub>OUT</sub> (internal transistor)

Overshoot

Undershoot

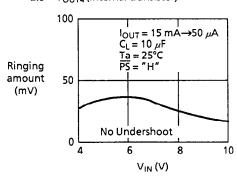

- 3.  $C_L$  dependency  $(V_{IN} = 4 V \rightarrow 10 V)$

- 3.1 Vout1, Vout2

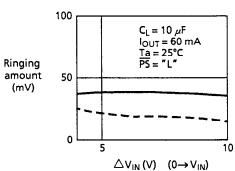

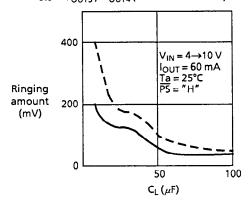

3.3 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transistor)

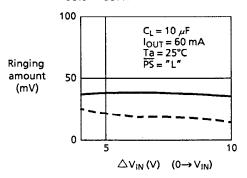

3.4 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transistor)

#### 3.5 V<sub>OUT4</sub> (internal transistor)

Overshoot

Undershoot

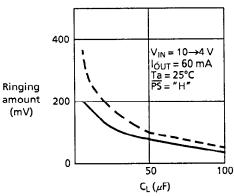

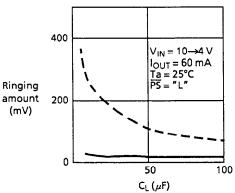

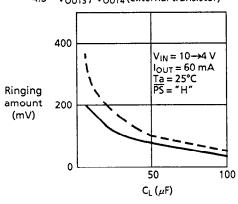

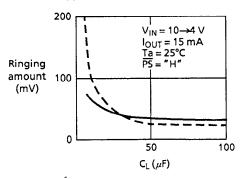

- 4.  $C_L$  dependency  $(V_{IN} = 10 V \rightarrow 4 V)$

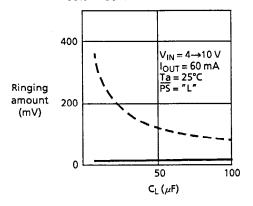

- 4.1 V<sub>OUT1</sub>, V<sub>OUT2</sub>

4.3 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transistor)

# 4.4 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transistor)

#### 4.5 V<sub>OUT4</sub> (internal transistor)

# Overshoot Undershoot

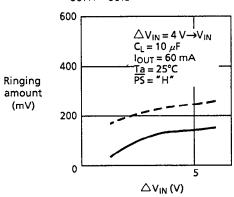

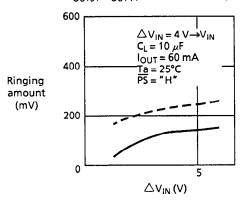

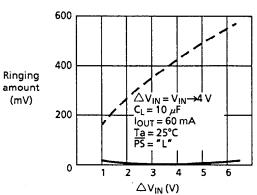

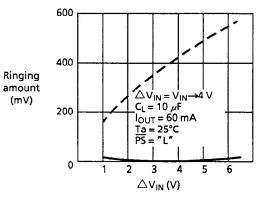

### 5. △V<sub>IN</sub> dependency (4 V→V<sub>IN</sub>)

# 5.1 V<sub>OUT1</sub>, V<sub>OUT2</sub>

#### 5.2 V<sub>OUT1</sub>, V<sub>OUT2</sub>

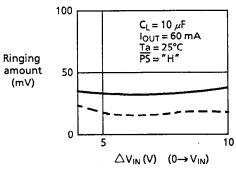

# 5.3 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transistor)

5.4 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transistor)

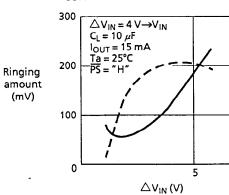

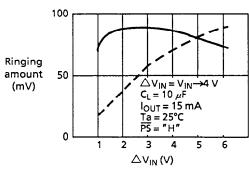

# 5.5 V<sub>OUT4</sub> (internal transistor)

Overshoot

---- Uncershoot

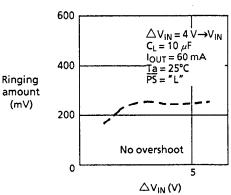

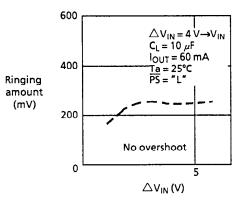

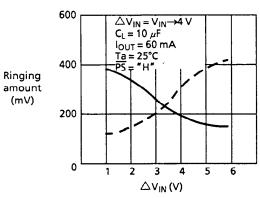

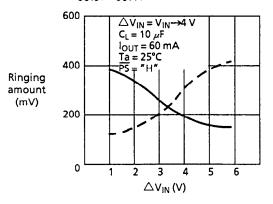

- 6. △V<sub>IN</sub> dependency (V<sub>IN</sub>→4 V)

- 6.1 Vout1, Vout2

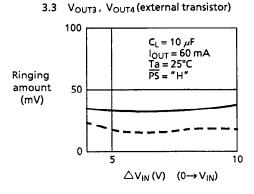

6.3 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transistor)

6.4 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transistor)

6.5 V<sub>OUT4</sub> (internal transistor)

Overshoot

---- Undershoot

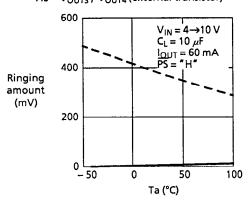

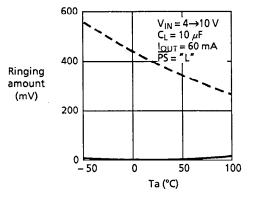

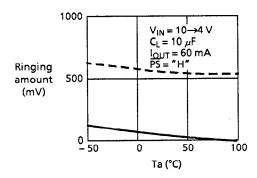

- 7. Temperature dependency (4 V→10 V)

- 7.1 V<sub>OUT1</sub>, V<sub>OUT2</sub>

Ringing amount (mV)  $V_{IN} = 4 \rightarrow 10 \text{ V}$   $C_L = 10 \mu\text{F}$   $l_{OUT} = 60 \text{ mA}$  PS = "H" Ta (°C)

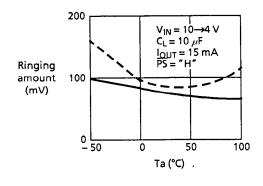

7.2 Vout1, Vout2

Ringing amount (mV) 200 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0 - 50 0

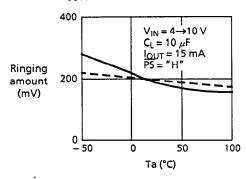

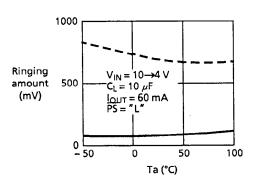

7.3 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transistor)

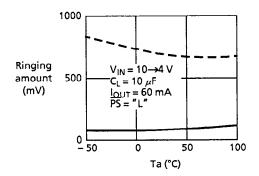

7.4 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transistor)

7.5 V<sub>OUT4</sub> (internal transistor)

----- Overshoot

Undershoot

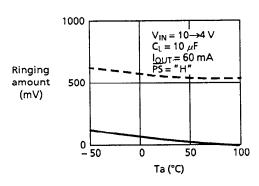

- 8. Temperature dependency (10 V→4 V)

- 8.1 Vout1, Vout2

8.3 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transistor)

8.5 V<sub>OUT4</sub> (internal transistor)

8.2 V<sub>OUT1</sub>, V<sub>OUT2</sub>

8.4 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transistor)

Overshoot

--- Undershoot

# 3. Transient Response Characteristics When Output Current Varies

Overshoot or undershoot occurs in the output voltage when the output current varies. This section describes parameter dependency characteristics for both overshoot and undershoot. For reference, Figure 16 depicts the measuring circuit.

Figure 16 Measuring Circuit

Table 13 Transient Response Parameter Dependency When Output Voltage Varies

| Parameter                |                 | Conditions                                                                            | Method to decrease overshoot | Method to decrease undershoot |

|--------------------------|-----------------|---------------------------------------------------------------------------------------|------------------------------|-------------------------------|

| Input voltage            | V <sub>IN</sub> |                                                                                       |                              | <u> </u>                      |

| Load capacitance         | CL              |                                                                                       | Increase                     | Increase                      |

| Output current variation | lout            | External : 60 mA $\leftrightarrow$ 1 mA Internal : 15 mA $\leftrightarrow$ 50 $\mu$ A | Decrease                     | Decrease                      |

| Temperature              | Та              | - 40 to 85 °C                                                                         |                              |                               |

# Reference Data When Output Current Varies

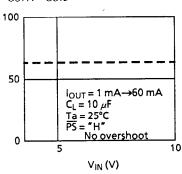

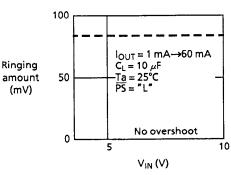

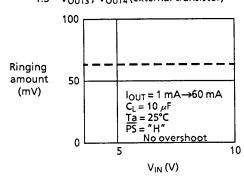

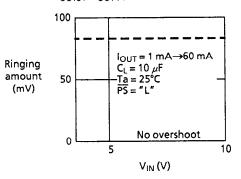

- 1.  $V_{IN}$  dependency (external transistor : 1 mA $\rightarrow$ 60 mA) internal transistor : 50  $\mu$ A $\rightarrow$ 15 mA)

- 1.1 Vout1, Vout2

Ringing amount (mV)

1.2 V<sub>OUT1</sub>, V<sub>OUT2</sub>

1.3 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transistor)

1.4 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transistor)

1.5 V<sub>OUT4</sub> (internal transistor)

OvershootUndershoot

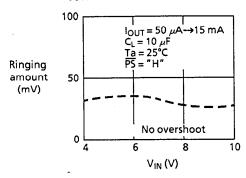

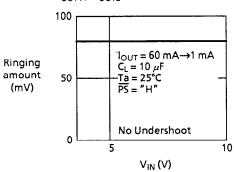

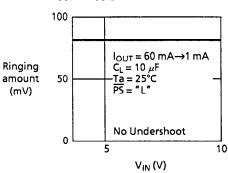

- 2.  $V_{IN}$  dependency (external transister : 60 mA $\rightarrow$ 1 mA ) internal transister : 15 mA $\rightarrow$ 50  $\mu$ A

- 2.1 V<sub>OUT1</sub>, V<sub>OUT2</sub>

2.3 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transister)

2.4 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transister)

2.5 V<sub>OUT4</sub> (internal transister)

- 3. C<sub>L</sub> dependency (external transister : 1 mA $\rightarrow$ 60 mA ) internal transister : 50  $\mu$ A $\rightarrow$ 15 mA

- 3.1 Vout1, Vout2

3.3 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transister)

3.4 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transister)

3.5 V<sub>OUT4</sub> (internal transister)

Overshoot

---- Undershoot

- 4. C<sub>L</sub> dependency (external transister : 60 mA→1 mA ) internal transister : 15 mA→50 μA

- 4.1 V<sub>OUT1</sub>, V<sub>OUT2</sub>

4.3 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transister)

4.4 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transister)

#### 4.5 V<sub>OUT4</sub> (internal transister)

\_\_\_\_\_ Overshoot

\_ \_ \_ \_ Undershoot

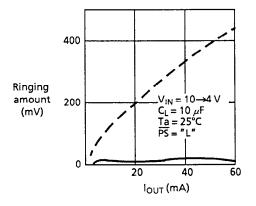

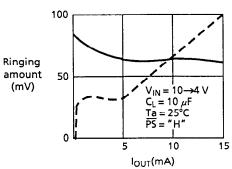

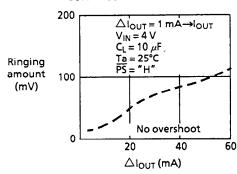

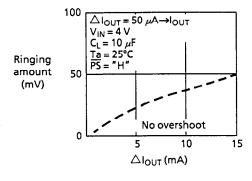

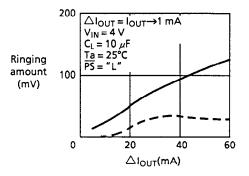

- 5.  $\triangle I_{OUT}$  dependency (external transister : 1 mA $\rightarrow I_{OUT}$ ) (internal transister : 50  $\mu$ A $\rightarrow I_{OUT}$ )

- 5.1 V<sub>OUT1</sub>, V<sub>OUT2</sub>

5.3 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transister)

5.5 V<sub>OUT4</sub> (internal transister)

5.2 V<sub>OUT1</sub>, V<sub>OUT2</sub>

5.4 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transister)

Overshoot

--- Undershoot

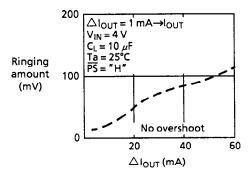

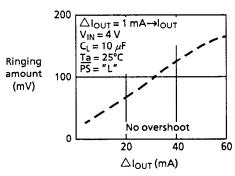

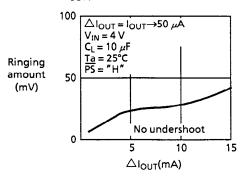

- 6. △I<sub>OUT</sub> dependency (external transister : I<sub>OUT</sub>→1 mA internal transister : I<sub>OUT</sub>→50 μA

- 6.1 V<sub>OUT1</sub>, V<sub>OUT2</sub>

6.2 V<sub>OUT1</sub>, V<sub>OUT2</sub>

6.3 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transister)

6.4 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transister)

# 6.5 V<sub>OUT4</sub> (internal transister)

Overshoot

---- Undershoot

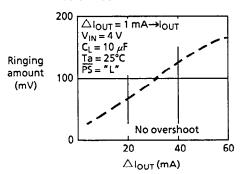

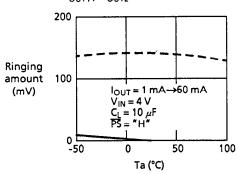

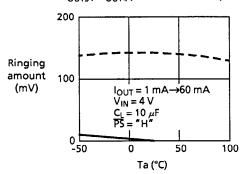

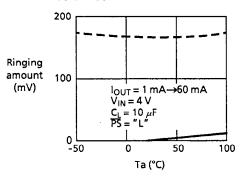

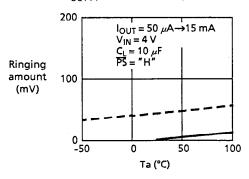

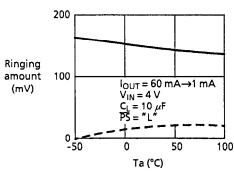

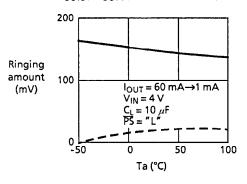

# 7. Temperature dependency

(external transister : 1 mA→60 mA ) internal transister : 50 μA→15 mA )

7.1 Vout1, Vout2

7.2 V<sub>OUT1</sub>, V<sub>OUT2</sub>

7.3 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transister)

7.4 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transister)

7.5 V<sub>OUT4</sub> (internal transister)

OvershootUndershoot

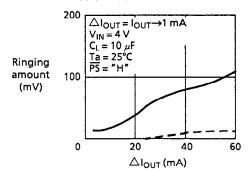

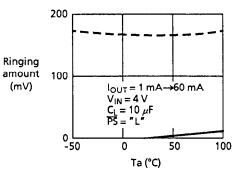

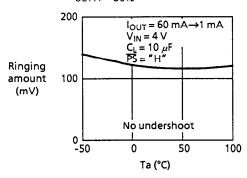

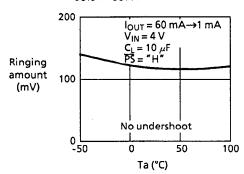

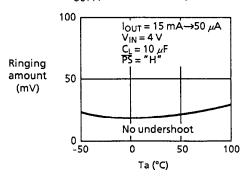

8. Temperature dependency

(external transister : 60 mA $\rightarrow$ 1 mA ) internal transister : 15 mA $\rightarrow$ 50  $\mu$ A

8.1 VOUT1, VOUT2

8.2 V<sub>OUT1</sub>, V<sub>OUT2</sub>

8.3 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transister)

8.4 V<sub>OUT3</sub>, V<sub>OUT4</sub> (external transister)

8.5 V<sub>OUT4</sub> (internal transister)

Overshoot

Undershoot

#### ■ Characteristics

#### 1. Voltage regulator

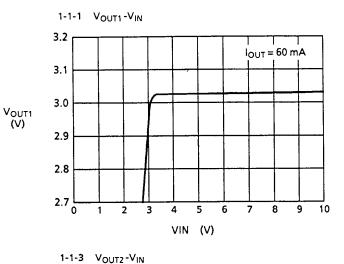

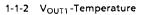

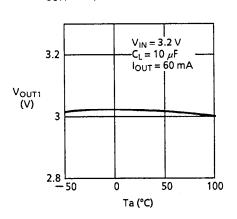

### 1-1 Output voltage characteristics

I<sub>OUT</sub> = 60 mA

1-1-4 V<sub>OUT2</sub>-Temperature

2.8

2.7 L 0

VIN (V)

1-1-6  $V_{OUT3}$ -Temperature

—— Overshoot

— — — Undershoot

V<sub>OUT3</sub> (V)

1-2 Input/Output voltage difference characteristics (V<sub>OUT4</sub> internal transistor)

V<sub>INITIAL</sub>: V<sub>OUT</sub> value when input voltage is 3.7 V

# 1-3 Input stability (△V<sub>OUT1</sub>, V<sub>OUT2</sub>V<sub>OUTL</sub>) - Temperature

Ta (°C)

1-4 Load stability ( $\triangle V_{OUTD}$ ) - Temperature

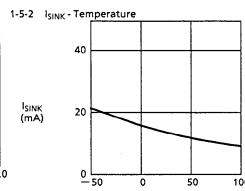

#### 1-5 Base sink current (ISINK) characteristics

0

Ta (°C)

50

100

### 2 Voltage detector

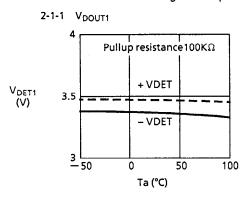

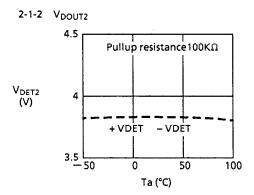

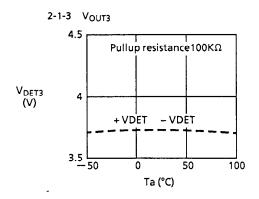

# 2-1 Detection Release voltage - Temperature

# 2-2 Sink current (IOL) characteristics

# 2-3 Dynamic responce

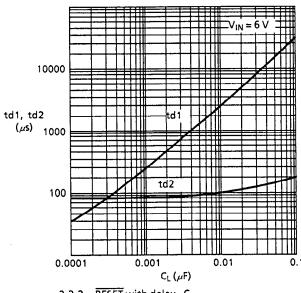

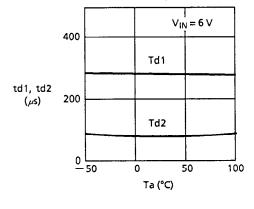

2-3-2 td1, td2 - Temperature

2-3-3 RESET with delay - CL

2-3-4 RESET with delay - Temperature

# 3 Watchdag Timer

# 3-1 Time out (t<sub>OUT</sub>) characteristics

#### 4 Overall characteristics

# 4-1 $V_{SH}$ , $V_{SL}$ - Temperature

SD1, SD2 RS, RESIN, INH WDTCLR

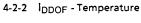

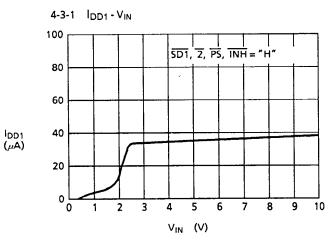

#### 4-2 Current consumption (IDDOF) characteristics

\* Without a shutdown prohibition. When the shut-down is not prohibited

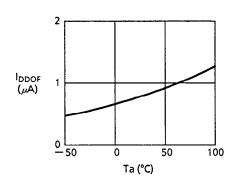

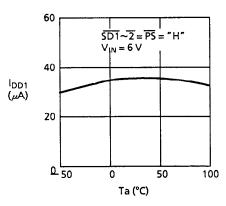

#### 4-3 Current consumption (IDD1) characteristics

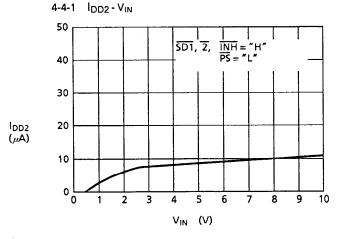

# 4-4 Current consumption (I<sub>DD2</sub>) characteristics

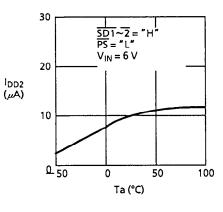

4-4-2 I<sub>DD2</sub> - Temperature

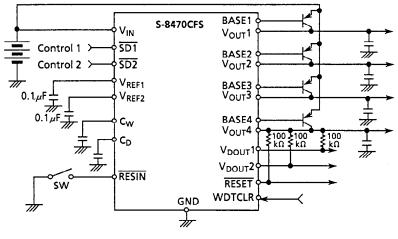

#### Application Circuit (S-8470CFS, REG4 external Tr)

#### Figure 17

#### Notes

- When using the internal transistor at V<sub>OUT</sub>4, always turn the PS "H." If you leave the PS "L," the transient response characteristics may deteriorate.

- The S-8470 series is not provided with a short-circuit protection circuit. In the event that short-circuit

occurs during the IC mounting operation, the resulting overcurrent may damage components on the IC.

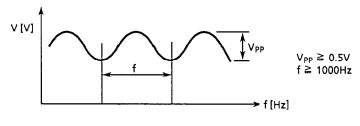

- · DO NOT APPLY the ripple voltage to the V<sub>IN</sub> under the following conditions:

Figure 18

- · Always attach a 10  $\mu$ F or more capacitor to the V<sub>OUT</sub> (V<sub>OUT</sub> 1 through 4).

- Attach an about 0.1 μF capacitor to V<sub>REF1</sub> and V<sub>REF2</sub>.

- $\cdot$  When the V<sub>IN</sub> voltage fluctuates over 1.5 V, set the through-rate for the V<sub>IN</sub> fluctuation to under 3 V/ms.

- When the S-8470 series detects the output voltage of the voltage regulator, overshoot or undershoot occurs in the voltage regulator depending upon operating conditions. Referring to the "Transient Response Characteristics," use the S-8470 series at the proper detection voltage and load capacitance.

- · A rise in the output voltage may occur in such an application that the output current of the external Tr. voltage regulator is less than 1 mA (when using the voltage regulator with an internal power Tr., it is 50  $\mu$ A).

- · When the external Tr. is connected to the voltage regulator, the base current increases if  $V_{IN} < V_{OUT}1$  through 4.

- When you design a new product for actual massproduction using the application circuits described herein, consider the tolerance, temperature and other characteristics of the parts you employ. Seiko Instruments Inc. shall not bear the responsibility for any patent infringement with regard to and/or arising from the circuits described herein.

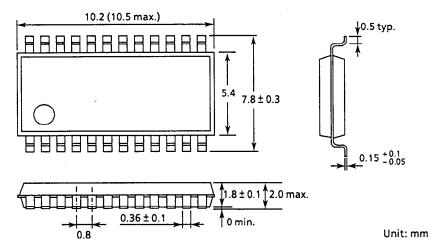

#### ■ Dimensions

24-pin SSOP

Figure 19

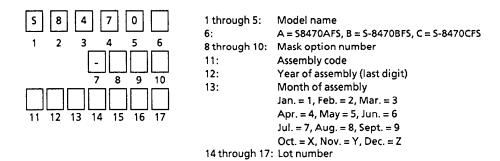

# ■ Marking

Figure 20

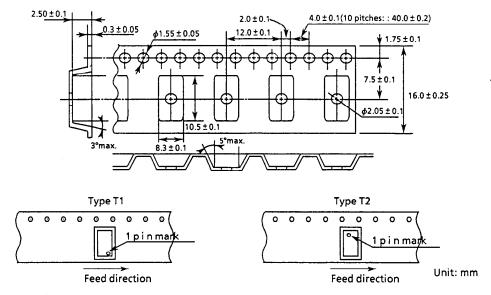

# ■ Taping

# 1. Tape specifications

Types T1 and T2 are available depending upon the direction of the IC on the tape.

Figure 21

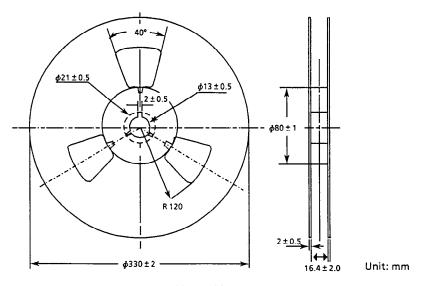

# 2. Reel specifications

1 reel holds 2000 ICs.

Figure 22