N-Channel Enhancement-Mode

Vertical DMOS Power FETs Quad Array

# **Ordering Information**

| BV <sub>pss</sub> /<br>BV <sub>pas</sub> | R <sub>DS(ON)</sub><br>(max) | Order Number / Package |               |

|------------------------------------------|------------------------------|------------------------|---------------|

|                                          |                              | 14-Pin P-Dip           | 14-Pin C-Dip* |

| 40V                                      | 2Ω                           | VN0204N6               | VN0204N7      |

| 60V                                      | 2Ω                           | VN0206N6               | VN0206N7      |

\*14-pin Side Brazed Ceramic Dip.

#### Features

ł

- 4 independent channels

- 4 electrically isolated die

- Commercial and Military versions available

- Freedom from secondary breakdown

- Low power drive requirement

- Low C<sub>iss</sub> and fast switching speeds

- High input impedance and high gain

#### Applications

- Motor control

- Convertors

- Amplifiers

- Switches

- D Power supply circuits

- Driver (Relays, Hammers, Solenoids, Lamps, Memories, Displays, Bipolar Transistors, etc.)

## **Thermal Characteristics**

| Package                                                  | Plastic<br>DIP | Ceramic<br>DIP |

|----------------------------------------------------------|----------------|----------------|

| 1 <sub>D</sub> continuous & I <sub>DR</sub> (single die) | 0.86A          | 1.0A           |

| I <sub>D</sub> pulsed* & I <sub>DRM</sub> *              | 4.0A           | 4.0A           |

| Power Dissipation @ T <sub>c</sub> = 25°C <sup>‡</sup>   | ЗW             | 4W             |

| θ <sub>ja</sub> (°C/W)                                   | 83.3           | 62.5           |

| θ <sub>ic</sub> (°C/W)                                   | 41.6           | 31.2           |

Puise test 300 µS pulse, 2% duty cycle.

<sup>‡</sup> Total for package.

1

## **Advanced DMOS Technology**

These enhancement-mode (normally-off) power transistors utilize a vertical DMOS structure and Supertex's well-proven silicongate manufacturing process. This combination produces devices with the power handling capabilities of bipolar transistors and with the high input impedance and negative temperature coefficient inherent in MOS devices. Characteristic of all MOS structures, these devices are free from thermal runaway and thermallyinduced secondary breakdown.

Supertex Vertical DMOS Power FETs are ideally suited to a wide range of switching and amplifying applications where high breakdown voltage, high input impedance, low input capacitance, and fast switching speeds are desired.

### **Electrical Characteristics**

Refer to VN02A Data Sheet for detailed characteristics.

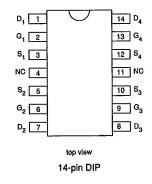

## **Pin Configuration**

10-29