#### 40MHz Non-Inverting Quad CMOS Driver

#### **Features**

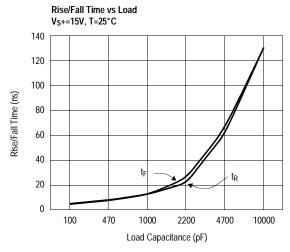

- Clocking Speeds Up To 40MHz

- 4 Channels

- 12 ns tr/tf at 1000pF Cload

- 1ns Rise and Fall Time Mismatch

- 1.5ns Prop Delay Mismatch

- Low Quiescent Current, <1mA

- Fast Output Enable Function, 12ns

- Wide Output Voltage Range

- 8V > VL > -5V

- $-2V \le VH \le 15V$

- 2A Peak Drive

- 3Ω On Resistance

- Input Level Shifters

- TTL/CMOS Input Compatible

### **Applications**

- CCD Drivers

- Digital Cameras

- Pin Drivers

- Clock / Line Drivers

- Ultrasound Transducer Drivers

- Ultrasonic and RF Generators

- Level Shifting

### **Ordering Information**

| Part No. Temp. Range |                | Package     | Outline # |

|----------------------|----------------|-------------|-----------|

| EL7457CU             | -40°C to +85°C | 16-Pin QSOP | MDP0040   |

| EL7457CS             | -40°C to +85°C | 16-Pin SO   | MDP0027   |

## **General Description**

The EL7457C is an ultra-high speed, non-inverting quad CMOS driver. It is capable of running at clock rates up to 40MHz and features 2A peak drive capability and a nominal on-resistance of just  $3\Omega$ . The EL7457C is ideal for driving highly capacitive loads, such as storage and vertical clocks in CCD applications. It is also well suited to ATE pin driving, level-shifting and clock-driving applications.

The EL7457C is capable of running from single or dual power supplies while using ground referenced inputs. Each output can be switched to either the high (VH) or low (VL) supply pins, depending on the related input pin. The inputs are compatible with both 3V and 5V CMOS and TTL logic. The output enable (OE) pin can be used to put the outputs into a high-impedance state. This is especially useful in CCD applications, where the driver should be disabled during power down.

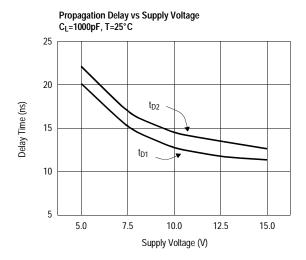

The EL7457C also features very fast rise and fall times which are matched to within 1ns. The propagation delay is also matched between rising and falling edges to within 2ns.

The EL7457C is available in both the 16-Pin QSOP and 16-Pin SOIC packages. It is specified for operation over the -40°C to +85°C temperature range.

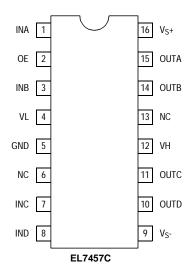

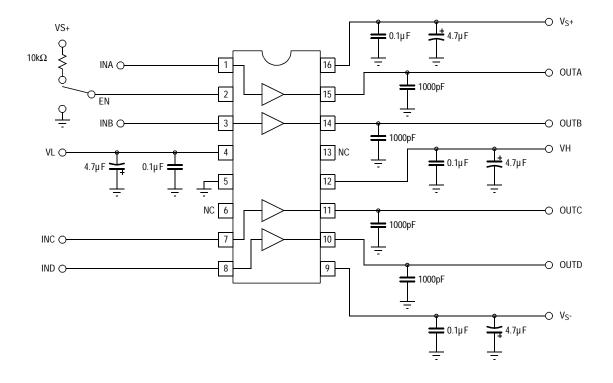

### **Pin Layout Diagram**

### 40MHz Non-Inverting Quad CMOS Driver

## Absolute Maximum Ratings $(T_A=25^{\circ}C)$

Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

Supply Voltage ( $V_S+$  to GND) +16.5V

Input Voltage

GND -0.3V,  $V_S$ + +0.3V

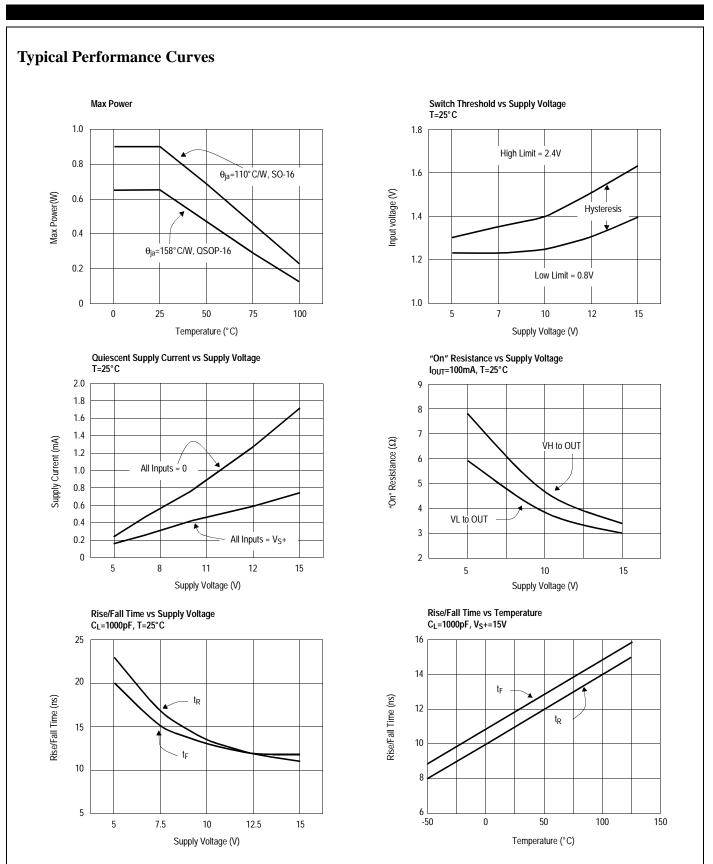

Continuous Output Current 100mA -65°C to +150°C Storage Temperature Range Ambient Operating Temperature -40°C to +85°C Operating Junction Temperature 125°C Power Dissipation: See Curves

2kV

#### **Important Note:**

All parameters having Min/Max specifications are guaranteed. Typ values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$ .

Maximum ESD

#### **Electrical Characteristics**

$V_{S}+$  = +5V,  $V_{S}-$  = -5V, VH = +5V, VL = -5V,  $T_{A}$  = 25°C, unless otherwise specified

| Parameter                         | Description                                  | Condition                  | Min  | Тур  | Max | Units |

|-----------------------------------|----------------------------------------------|----------------------------|------|------|-----|-------|

| Input                             | ·                                            |                            |      |      | •   | •     |

| $V_{IH}$                          | Logic "1" Input Voltage                      |                            | 2.0  |      |     | V     |

| I <sub>IH</sub>                   | Logic "1" Input Current                      | $V_{IH} = 5V$              |      | 0.1  | 10  | μΑ    |

| $V_{IL}$                          | Logic "0" Input Voltage                      |                            |      |      | 0.8 | V     |

| $I_{IL}$                          | Logic "0" Input Current                      | $V_{IL} = 0V$              |      | 0.1  | 10  | μΑ    |

| C <sub>in</sub> Input Capacitance |                                              |                            |      | 3.5  |     | pF    |

| R <sub>in</sub> Input Resistance  |                                              |                            |      | 50   |     | ΜΩ    |

| Output                            | ·                                            |                            |      |      |     |       |

| R <sub>OV1</sub>                  | ON Resistance VH to OUTx                     | $I_{OUT} = -100 \text{mA}$ |      | 4.5  | 6   | Ω     |

| R <sub>OV2</sub>                  | ON Resistance VL to OUTx                     | $I_{OUT} = +100 \text{mA}$ |      | 4    | 6   | Ω     |

| I <sub>Leak</sub>                 | Output Leakage Current                       | $VH = V_S +, VL = V_S -$   |      | 0.1  | 10  | μΑ    |

| I <sub>PK</sub>                   | Peak Output Current                          | Source                     |      | 2.0  |     | A     |

|                                   |                                              | Sink                       |      | 2.0  |     | A     |

| Power Supply                      |                                              |                            | •    |      | •   | •     |

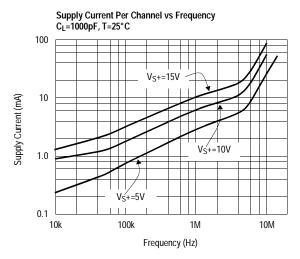

| Is Power Supply Current           |                                              | $Inputs = V_S +$           |      | 0.5  | 1.5 | mA    |

| Switching Cha                     | racteristics                                 |                            |      |      |     |       |

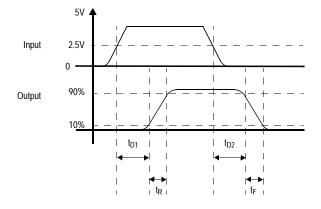

| $t_R$                             | Rise Time $C_L = 1000 pF$                    |                            | 13.5 |      | ns  |       |

| t <sub>F</sub>                    | Fall Time                                    | $C_L = 1000 pF$            |      | 13   |     | ns    |

| t <sub>RFdelta</sub>              | t <sub>R</sub> , t <sub>F</sub> Mismatch     | $C_{L} = 1000 pF$          |      | 0.5  |     | ns    |

| t <sub>D-1</sub>                  | Turn-Off Delay Time                          | $C_L = 1000pF$             |      | 12.5 |     | ns    |

| t <sub>D-2</sub>                  | Turn-On Delay Time                           | $C_L = 1000 pF$            |      | 14.5 |     | ns    |

| t <sub>Ddelta</sub>               | t <sub>D-1</sub> - T <sub>D-2</sub> Mismatch | $C_L = 1000 pF$            |      | 2    |     | ns    |

| T <sub>enable</sub>               | Enable Delay Time                            |                            |      | 12   |     | ns    |

| T <sub>disable</sub>              | Disable Delay Time                           |                            |      | 12   |     | ns    |

## **Electrical Characteristics**

$V_S +$  = +15V,  $V_S -$  = 0V, VH = +15V, VL = 0V,  $T_A$  = 25°C, unless otherwise specified

| Parameter                         | Description                                  | Condition                  | Min | Тур  | Max | Units |

|-----------------------------------|----------------------------------------------|----------------------------|-----|------|-----|-------|

| Input                             | •                                            |                            | •   |      |     |       |

| V <sub>IH</sub>                   | Logic "1" Input Voltage                      |                            | 2.4 |      |     | V     |

| I <sub>IH</sub>                   | Logic "1" Input Current                      | $V_{IH} = 5V$              |     | 0.1  | 10  | μΑ    |

| $V_{\rm IL}$                      | Logic "0" Input Voltage                      |                            |     |      | 0.8 | V     |

| $I_{IL}$                          | Logic "0" Input Current                      | $V_{IL} = 0V$              |     | 0.1  | 10  | μΑ    |

| C <sub>in</sub> Input Capacitance |                                              |                            |     | 3.5  |     | pF    |

| R <sub>in</sub>                   | Input Resistance                             |                            |     | 50   |     | ΜΩ    |

| Output                            |                                              |                            |     |      |     |       |

| R <sub>OV1</sub>                  | ON Resistance VH to OUT                      | $I_{OUT} = -100 \text{mA}$ |     | 3.5  | 5   | Ω     |

| R <sub>OV2</sub>                  | ON Resistance VL to OUT                      | $I_{OUT} = +100 \text{mA}$ |     | 3    | 5   | Ω     |

| I <sub>leak</sub>                 | Output Leakage Current                       | $VH = V_S +, VL = V_S -$   |     | 0.1  | 10  | μΑ    |

| I <sub>PK</sub>                   | Peak Output Current                          | Source                     |     | 2.0  |     | A     |

|                                   |                                              | Sink                       |     | 2.0  |     | A     |

| <b>Power Supply</b>               | •                                            |                            |     |      |     |       |

| I <sub>S</sub>                    | Power Supply Current                         | $Inputs = V_S +$           |     | 0.8  | 2   | mA    |

| Switching Cha                     | racteristics                                 |                            |     |      |     |       |

| t <sub>R</sub>                    | Rise Time                                    | $C_{L} = 1000 pF$          |     | 11   |     | ns    |

| t <sub>F</sub>                    | Fall Time                                    | $C_{L} = 1000 pF$          |     | 12   |     | ns    |

| t <sub>RFdelta</sub>              | t <sub>R</sub> , t <sub>F</sub> Mismatch     | $C_{L} = 1000 pF$          |     | 1    |     | ns    |

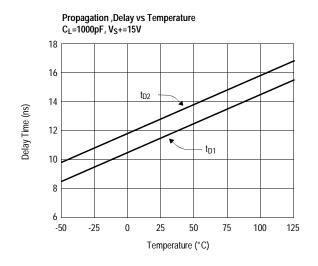

| t <sub>D-1</sub>                  | Turn-Off Delay Time                          | $C_{L} = 1000 pF$          |     | 11.5 |     | ns    |

| t <sub>D-2</sub>                  | Turn-On Delay Time                           | $C_{L} = 1000 pF$          |     | 13   |     | ns    |

| t <sub>Ddelta</sub>               | t <sub>D-1</sub> - t <sub>D-2</sub> Mismatch | $C_L = 1000 pF$            |     | 1.5  |     | ns    |

| Tenable                           | Enable Delay Time                            |                            |     | 12   |     | ns    |

| T <sub>disable</sub>              | Disable Delay Time                           |                            |     | 12   |     | ns    |

## 40MHz Non-Inverting Quad CMOS Driver

## **Typical Performance Curves (cont.)**

## 40MHz Non-Inverting Quad CMOS Driver

## **Nominal Operating Voltage Range**

| PIN                                  | MIN                     | MAX         |

|--------------------------------------|-------------------------|-------------|

| V <sub>S</sub> + to V <sub>S</sub> - | 5V                      | 15V         |

| V <sub>S</sub> - to GND              | -5V                     | 0V          |

| VH                                   | V <sub>S</sub> - + 2.5V | $V_{S}$ +   |

| VL                                   | V <sub>S</sub> -        | $V_{S}^{+}$ |

| VH to VL                             | 0V                      | 15V         |

| VL to V <sub>S</sub> -               | 0V                      | 8V          |

## **Timing Diagrams**

## **Standard Test Configuration**

## EL7457C 40MHz Non-Inver

## 40MHz Non-Inverting Quad CMOS Driver

## **Pin Description**

| Pin | Name             | Function                                 | Equivalent Circuit    |

|-----|------------------|------------------------------------------|-----------------------|

| 1   | INA              | Input Channel A                          | INPUT O VS- Circuit 1 |

| 2   | OE               | Output Enable                            | (Reference Circuit 1) |

| 3   | INB              | Input Channel B                          | (Reference Circuit 1) |

| 4   | VL               | Low Voltage Input Pin                    | (Reference Circuit 1) |

| 5   | GND              | Input Logic Ground                       |                       |

| 6   | NC               | No Connection                            |                       |

| 7   | INC              | Input Channel C                          | (Reference Circuit 1) |

| 8   | IND              |                                          |                       |

| 9   |                  | Input Channel D                          | (Reference Circuit 1) |

| 10  | V <sub>S</sub> - | Negative Supply Voltage Output Channel D |                       |

| 10  | GUID             | Output Chaimer D                         | OUTPUT  VL  Circuit 2 |

| 11  | OUTC             | Output Channel C                         | (Reference Circuit 2) |

| 12  | VH               | High Voltage Input Pin                   |                       |

| 13  | NC               | No Connection                            |                       |

| 14  | OUTB             | Output Channel B                         | (Reference Circuit 2) |

| 15  | OUTA             | Output Channel A                         | (Reference Circuit 2) |

| 16  | V <sub>S</sub> + | Positive Supply Voltage                  |                       |

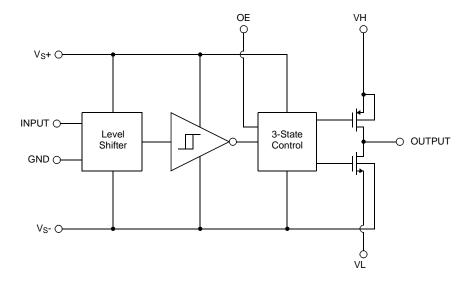

## **Block Diagram**

### 40MHz Non-Inverting Quad CMOS Driver

## **Application Information:**

#### **Product Description**

The EL7457C is a high performance 40MHz ultra-high speed quad driver. Each channel of the EL7457C consists of a single P-channel high side driver and a single N-channel low side driver. These  $3\Omega$  devices will pull the output (OUT<sub>X</sub>) to either the high or low voltage, on VH and VL respectively, depending on the input logic signal (IN<sub>X</sub>). It should be noted that there is only one set of high and low voltage pins.

A common output enable (OE) pin is available on the EL7457C. This pin, when pulled low will put all outputs in to the high impedance state.

The EL7457C is available in both the 16-pin SOIC and the space saving 16-pin QSOP packages. The relevant package should be chosen depending on the calculated power dissipation.

#### **Supply Voltage Range and Input Compatibility**

The EL7457C is designed for operation on supplies from 5V to 15V with 10% tolerance (i.e. 4.5V to 16.5V). The table on page 6 shows the specifications for the relationship between the  $V_{S^+}$ ,  $V_{S^-}$ , VH, VL and GND pins. The EL7457C does not contain a true analog switch and therefore VL should always be less than VH.

All input pins are compatible with both 3V and 5V CMOS signals With a positive supply  $(V_S+)$  of 5V, the EL7457C is also compatible with TTL inputs.

#### **Power Supply Bypassing**

When using the EL7457C, it is very important to use adequate power supply bypassing. The high switching currents developed by the EL7457C necessitate the use of a bypass capacitor on both the positive and negative supplies. It is recommended that a  $4.7\mu F$  tantalum capacitor be used in parallel with a  $0.1\mu F$  low-inductance ceramic MLC capacitor. These should be placed as close to the supply pins as possible. It is also recommended that the VH and VL pins have some level of bypassing, especially if the EL7457C is driving highly capacitive loads.

#### **Power Dissipation Calculation**

When switching at high speeds, or driving heavy loads, the EL7457C drive capability is limited by the rise in die temperature brought about by internal power dissipation. For reliable operation die temperature must be kept below  $T_{jmax}$  (125°C). It is necessary to calculate the power dissipation for a given application prior to selecting the package type.

Power dissipation may be calculated:

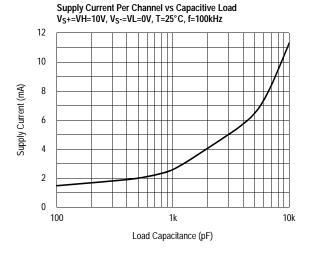

$$PD = (V_S \times I_S) + \sum_{1}^{4} (C_{INT} \times V_S^2 \times f) + (C_L \times V_{OUT}^2 \times f)$$

where:

- V<sub>S</sub> is the total power supply to the EL7457C (from V<sub>S</sub>+ to V<sub>S</sub>-),

- Vout is the swing on the output (VH VL),

- C<sub>L</sub> is the load capacitance,

- C<sub>INT</sub> is the internal load capacitance (50pF max.),

- Is is the quiescent supply current (3mA max.) and

- f is frequency

Having obtained the application's power dissipation, a maximum package thermal coefficient may be determined, to maintain the internal die temperature below  $T_{\rm jmax}$ .

$$\theta_{ja} = \frac{(T_{jmax} - T_{max})}{PD}$$

where:

- T<sub>imax</sub> is the maximum junction temperature (125°C),

- T<sub>max</sub> is the maximum operating temperature,

- PD is the power dissipation calculated above.

Using the value of  $\theta_{ja}$ , a suitable package for the application may be selected.

In applications with a  $\theta_{ja}$  greater than 158°C/W, a 16-pin QSOP may be used. A 16-pin SOIC is suitable for applications with a  $\theta_{ja}$  value greater than 110°C/W. However,

# EL7457C 40MHz Non-Inverting Quad CMOS Driver 57

| if the calculated value of $\theta_{ja}$ is less than 110°C/W, the application must be derated to prevent premature failure of the device, either by reducing the switching fre- | quency, the capacitive load or the maximum operating temperature. |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

|                                                                                                                                                                                  |                                                                   |

|                                                                                                                                                                                  |                                                                   |

|                                                                                                                                                                                  |                                                                   |

|                                                                                                                                                                                  |                                                                   |

|                                                                                                                                                                                  |                                                                   |

|                                                                                                                                                                                  |                                                                   |

|                                                                                                                                                                                  |                                                                   |

|                                                                                                                                                                                  |                                                                   |

|                                                                                                                                                                                  |                                                                   |

|                                                                                                                                                                                  |                                                                   |

|                                                                                                                                                                                  |                                                                   |

40MHz Non-Inverting Quad CMOS Driver

#### **General Disclaimer**

Specifications contained in this data sheet are in effect as of the publication date shown. Elantec, Inc. reserves the right to make changes in the circuitry or specifications contained herein at any time without notice. Elantec, Inc. assumes no responsibility for the use of any circuits described herein and makes no representations that they are free from patent infringement.

#### Élantec, Inc.

675 Trade Zone Blvd. Milpitas, CA 95035

Telephone: (408) 945-1323

(888) ÉLANTEC

(408) 945-9305 Fax:

European Office: +44-118-977-6080

#### WARNING - Life Support Policy

Elantec, Inc. products are not authorized for and should not be used within Life Support Systems without the specific written consent of Elantec, Inc. Life Support systems are equipment intended to support or sustain life and whose failure to perform when properly used in accordance with instructions provided can be reasonably expected to result in significant personal injury or death. Users contemplating application of Elantec, Inc. Products in Life Support Systems are requested to contact Elantec, Inc. factory headquarters to establish suitable terms & conditions for these applications. Elantec, Inc.'s warranty is limited to replacement of defective components and does not cover injury to persons or property or other consequential damages.