# **PRODUCTION DATASHEET**

#### DESCRIPTION

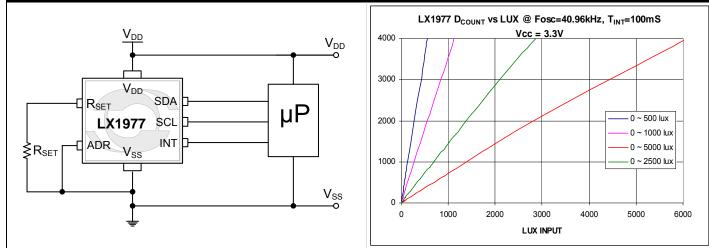

The LX1977 is a CMOS based Ambient Light Sensor (ALS) with an  $I^2C$  compatible SMBus interface.

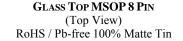

This device is ideal for controlling display back lighting systems of low cost consumer products such as TV, portable computers, handheld devices, or medical devices. The LX1977 is optimized for a linear, accurate, and very repeatable input and output transfer function. The device also features adjustable input range and gain.

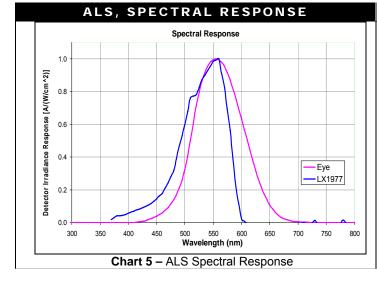

The LX1977 has a spectral response that emulates the human eye. Specially designed circuitry produces peak spectral response at 555 nm, with IR response less than 10% above 810 nm.

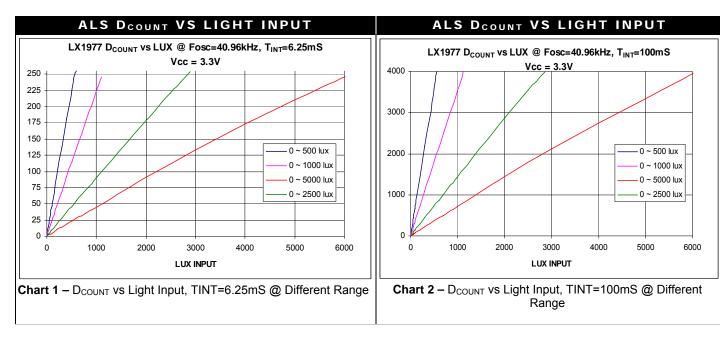

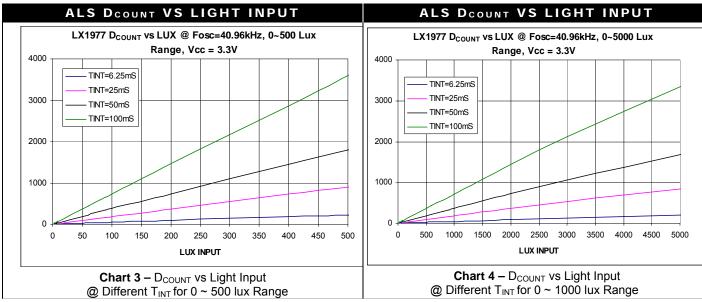

Input dynamic range of this device is adjustable via SMBus command. It can be set to either  $0 \sim 500 \text{ lux}$ ,  $0 \sim 1000 \text{ lux}$ ,  $0 \sim 2500 \text{ lux}$  or  $0 \sim 5000 \text{ lux}$ .

ALS internal compensation ensures photodiode dark current are at very low levels, providing high output accuracy at low ambient light levels.

The LX1977 integrates a 12-bit Sigma-Delta A/D converter that converts the ALS photodiode output into a digital word. This value is read via the  $I^2C$  compatible SMBus interface.

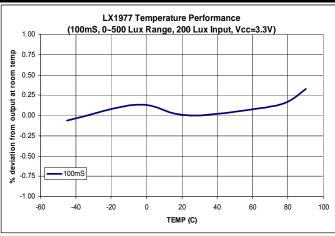

The LX1977 ALS is internally optimized to an accuracy of approximately 5% over temperature. The high accuracy and repeatability of this device eliminates the need of calibration during product production, which results in reduced assembly time and lower production cost.

The LX1977 is available in an 8-pin MSOP package, and is operational over the ambient temperature range -40°C to 85°C.

# KEY FEATURES

LX1977

- Human Eye Spectral Response

- Very Low IR Sensitivity

- 12-bit Resolution

- 5% Typical Accuracy

- Rejection to 50/60Hz Interference

- Programmable Integration Time

- Programmable Interrupt Pin

- I<sup>2</sup>C compatible SMBus Interface

- Easy Processor Interface

- No Optical Filter Needed

# APPLICATIONS

- Backlight Control for Notebook

- Backlight Control for TV

- Handheld Devices

- Medical Devices

Note: I<sup>2</sup>C is a trade mark of Philips

|                                       | PACK                                                                                                                              | AGE ORDER INFO             | THERMAL DATA                                                                                                                                    |  |  |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| T <sub>A</sub> (°C)                   | DU                                                                                                                                | 3 x 5 Glass Top MSOP 8-pin | $\theta_{\rm JA} = 152 \ ^{\circ}{\rm C/W}$                                                                                                     |  |  |

| $\mathbf{I}_{\mathbf{A}}(\mathbf{C})$ |                                                                                                                                   | RoHS Compliant / Pb-free   | THERMAL RESISTANCE-JUNCTION TO AMBIENT                                                                                                          |  |  |

| -40 to 85                             | -40 to 85 <b>LX1977IDU</b><br>Note: Available in Tape & Reel. Append the letters "TR" to the part number.<br>(i.e. LX1977IDU -TR) |                            | Junction Temperature Calculation: $T_J = T_A + (P_D \times \theta_{JA})$ .                                                                      |  |  |

| Note: Av                              |                                                                                                                                   |                            | The $\theta_{JA}$ numbers are guidelines for the thermal performance of the device/pc-board system. All of the above assume no ambient airflow. |  |  |

| ABSOLU |  | RATINGS |  |

|--------|--|---------|--|

|        |  |         |  |

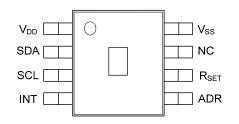

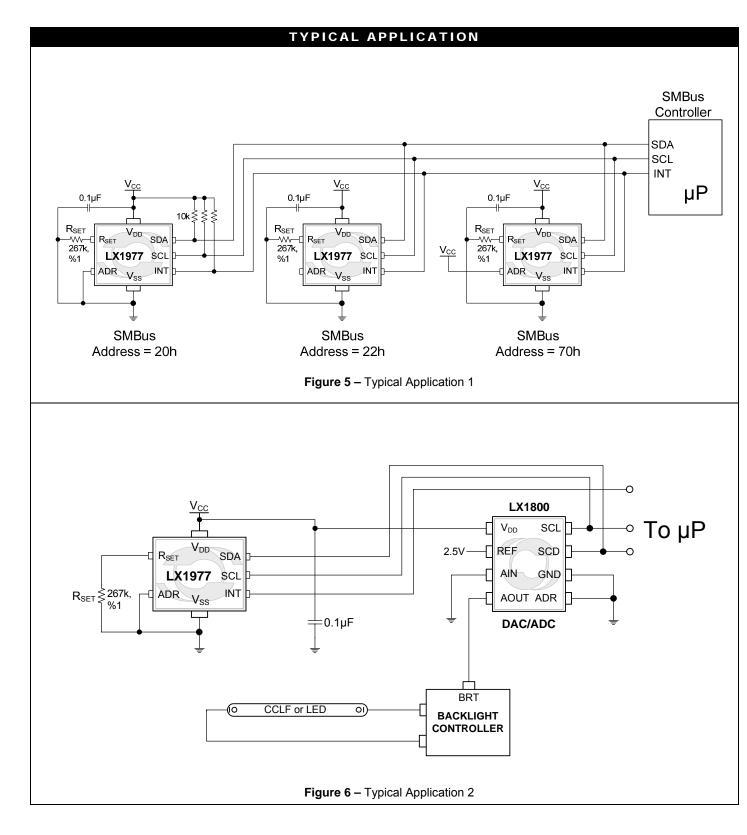

PACKAGE PIN OUT

Notes: Exceeding these ratings could cause damage to the device. All voltages are with respect to Ground. Currents are positive into, negative out of specified terminal.

www.Microsemi.com

**PRODUCTION DATASHEET**

## PRODUCT HIGHLIGHT

# PACKAGE PHOTO

Figure 2 – Product Photo

|                  | FUNCTIONAL PIN DESCRIPTION |       |                                                                                                                                                                                       |  |  |  |  |  |

|------------------|----------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Name             | Pin #                      | Dir   | Description                                                                                                                                                                           |  |  |  |  |  |

| $V_{\text{DD}}$  | 1                          | PWR   | Power Supply Voltage                                                                                                                                                                  |  |  |  |  |  |

| SDA              | 2                          | I / O | SMBus Data – Connect To SMBus Data Line                                                                                                                                               |  |  |  |  |  |

| SCL              | 3                          | Ι     | SMBus Clock – Connect To SMBus Clock Line                                                                                                                                             |  |  |  |  |  |

| INT              | 4                          | 0     | Interrupt Output Pin, Active Low, Open Drain                                                                                                                                          |  |  |  |  |  |

| ADR              | 5                          | I     | SMBus Address – The Address For This Device Is Determined By The State Of This Pin.<br>ADR = GND sets address 20H, ADR = OPEN sets address 22H, ADR=V <sub>DD</sub> sets address 70H. |  |  |  |  |  |

| R <sub>SET</sub> | 6                          | I     | Gain Setting. For Gain Fine Adjustment. Typically, connect this pin to ground through a 1% 267k resistor.                                                                             |  |  |  |  |  |

| NC               | 7                          |       | No Connection Pin                                                                                                                                                                     |  |  |  |  |  |

| V <sub>ss</sub>  | 8                          | PWR   | Ground Reference For Power And Signal Output                                                                                                                                          |  |  |  |  |  |

LX1977

## **PRODUCTION DATASHEET**

### ELECTRICAL CHARACTERISTICS

Unless otherwise specified, the following specifications apply over the operating ambient temperature  $0^{\circ}C \le T_A \le 70^{\circ}C$  and the

| Parameter                                                                                  | Symbol              | <b>Test Conditions / Comment</b>                                                | Min   | Тур   | Max   | Units  |  |

|--------------------------------------------------------------------------------------------|---------------------|---------------------------------------------------------------------------------|-------|-------|-------|--------|--|

| Power Supply                                                                               |                     |                                                                                 | ·     |       |       |        |  |

| Operational Voltage                                                                        | V <sub>DD</sub>     | Note 5                                                                          | 3.0   |       | 4.5   | V      |  |

| Supply Current                                                                             | I <sub>DD</sub>     |                                                                                 |       |       | 0.2   | mA     |  |

| Supply Current                                                                             | I <sub>DD</sub>     | Shut Down ALS                                                                   |       |       | 15    | μA     |  |

| INTERNAL                                                                                   |                     |                                                                                 |       |       | 1     | 1      |  |

| Internal Oscillator Frequency For                                                          |                     | 3.0V ≤V <sub>DD</sub> .≤ 3.6V                                                   | 38.91 | 40.96 | 43.00 |        |  |

| Internal Oscillator Frequency                                                              | Fosc                | 3.0V ≤V <sub>DD</sub> .≤ 4.5V                                                   | 36.86 | 40.96 | 45.06 | - kHz  |  |

| ALS RESPONSE                                                                               |                     |                                                                                 |       |       |       |        |  |

| Peak Spectral Response                                                                     | $\lambda_{PR(ALS)}$ |                                                                                 |       | 555   |       | nm     |  |

| Infrared Response                                                                          | $\Delta_{IR}$       | $E_{V(white)}$ = 100 lux, $E_{V(810nm)}$ = 14.6µW/cm <sup>2</sup> ,<br>Note 3   | -8    |       | 8     | %      |  |

| Full Scale ADC Output Value                                                                | D <sub>COUNT</sub>  | T <sub>INT</sub> = 100 ms, Note 4                                               |       |       | 4095  |        |  |

| @ $F_{OSC}$ = 40.96kHz,<br>RANGE SEL = 00b (0 ~ 500 lux)                                   | D <sub>COUNT</sub>  | T <sub>INT</sub> = 50 ms, Note 4                                                |       |       | 2047  | Counts |  |

| $RANGE\_SEL = 01b (0 \sim 1000 lux)$                                                       | D <sub>COUNT</sub>  | T <sub>INT</sub> = 25 ms, Note 4                                                |       |       | 1023  |        |  |

| RANGE_SEL = $10b (0 \sim 5000 \text{ lux})$<br>RANGE_SEL = $11b (0 \sim 2500 \text{ lux})$ | D <sub>COUNT</sub>  | T <sub>INT</sub> = 6.25 ms, Note 4                                              |       |       | 255   |        |  |

| Enable Time                                                                                | t <sub>on</sub>     | Software Enable                                                                 |       | 100   |       | μs     |  |

|                                                                                            |                     | Software Disable                                                                |       | 100   |       | μs     |  |

| Dynamic Response Time                                                                      |                     | Light Input Change From 200 lux to 20 lux                                       |       | 1     |       | ms     |  |

| T <sub>R(10%~90%)</sub>                                                                    |                     | Light Input Change From 20 lux to 200 lux                                       |       | 1     |       | 1115   |  |

| ADC                                                                                        |                     |                                                                                 |       |       |       |        |  |

| Non-Linearity                                                                              | DNL                 | T <sub>INT</sub> = 100ms, RANGE_SEL=00b<br>Note 6                               | -5    |       | 5     | %      |  |

| ALS                                                                                        |                     |                                                                                 |       |       |       |        |  |

| ADC Output Count                                                                           |                     | E <sub>V</sub> = 200 lux, Note 1,2                                              | 346   | 372   | 398   | Count  |  |

| (a) $F_{OSC} = 40.96 \text{kHz}$ , $T_{INT} = 50 \text{ms}$                                | D <sub>COUNT</sub>  | E <sub>v</sub> = 500 lux, Note 1,2                                              | 880   | 931   | 982   |        |  |

| $RANGE\_SEL = 01b (0 \sim 1000 lux)$                                                       |                     | E <sub>v</sub> = 1000 lux, Note 1,2                                             | 1768  | 1861  | 1955  |        |  |

| ADC Output Count                                                                           |                     | E <sub>v</sub> = 100 lux, Note 1,2                                              | 692   | 745   | 797   |        |  |

| @ $F_{OSC} = 40.96 \text{kHz}, T_{INT} = 100 \text{ms}$                                    | D <sub>COUNT</sub>  | E <sub>V</sub> = 200 lux, Note 1,2                                              | 1403  | 1489  | 1575  | Coun   |  |

| $RANGE\_SEL = 00b (0 \sim 500 lux)$                                                        |                     | E <sub>v</sub> = 500 lux, Note 1,2                                              | 3537  | 3723  | 3909  | -      |  |

|                                                                                            |                     | E <sub>V</sub> = 200 lux                                                        |       | 733   |       | +      |  |

| ADC Output Count<br>(a) $F_{OSC} = 40.96$ kHz, $T_{INT} = 100$ ms                          | D <sub>COUNT</sub>  | E <sub>V</sub> = 500 lux                                                        |       | 1808  |       | Coun   |  |

| $RANGE\_SEL = 01b (0 \sim 1000 lux)$                                                       | 00011               | E <sub>V</sub> = 1000 lux                                                       |       | 3535  |       | -      |  |

| ADC Output Count                                                                           |                     | E <sub>V</sub> = 500 lux                                                        |       | 364   |       |        |  |

| ADC Output Count<br>(a) $F_{OSC} = 40.96$ kHz, $T_{INT} = 100$ ms                          | D <sub>COUNT</sub>  | E <sub>V</sub> = 1000 lux                                                       |       | 713   |       | Coun   |  |

| $RANGE\_SEL = 10b (0 \sim 5000 lux)$                                                       |                     | E <sub>V</sub> = 2000 lux                                                       |       | 1437  |       |        |  |

| ADC Output Count                                                                           |                     | E <sub>V</sub> = 500 lux                                                        |       | 734   | 1     | 1      |  |

| (a) F <sub>OSC</sub> = 40.96kHz, T <sub>INT</sub> = 100ms                                  | D <sub>COUNT</sub>  | E <sub>V</sub> = 1000 lux                                                       |       | 1433  |       | Coun   |  |

| $RANGE\_SEL = 11b (0 \sim 2500 lux)$                                                       |                     | E <sub>V</sub> = 2000 lux                                                       |       | 2851  | 1     | 1      |  |

| Dark ADC Count Value                                                                       | D <sub>COUNT</sub>  | $E_V$ = 0 lux, T <sub>A</sub> = 25°C, RANGE_SEL=00b,<br>T <sub>INT</sub> =100mS |       | 0     | 4     | Coun   |  |

LX1977

Copyright © 2010 Rev. 1.0, 2010-03-25

# Microsemi

Page 3

Analog Mixed Signal Group 11861 Western Avenue, Garden Grove, CA. 92841, 714-898-8121, Fax: 714-893-2570

## **PRODUCTION DATASHEET**

## ELECTRICAL CHARACTERISTICS

Unless otherwise specified, the following specifications apply over the operating ambient temperature  $0^{\circ}C \le T_{A} \le 70^{\circ}C$  and the following test conditions:  $3.0V \le V_{DD} \le 4.5V$

| Parameter                    | Symbol                             | <b>Test Conditions / Comment</b>                                                                          | Min | Тур | Max | Units           |

|------------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------|-----|-----|-----|-----------------|

|                              |                                    | $E_V = 0 \text{ lux}, T_A = 70^{\circ}\text{C}, \text{RANGE}SEL=00b, T_{INT}=100\text{mS}, \text{Note 7}$ |     |     | 18  |                 |

| SMBUS INTERFACE              |                                    |                                                                                                           |     |     |     |                 |

| Clock Frequency              | F <sub>CLK</sub>                   |                                                                                                           | 10  |     | 400 | kHz             |

| High Level Input Voltage     | V <sub>SDA</sub>                   |                                                                                                           | 0.8 |     |     | V               |

| Low Level Input Voltage      | V <sub>SCL</sub>                   |                                                                                                           |     |     | 2.1 | V               |

| Input Leakage Current        | I <sub>SDA</sub> /I <sub>SCL</sub> |                                                                                                           | -5  |     | 5   | μA              |

| SDA Low Output Voltage       | V <sub>SDA</sub>                   | I <sub>SDA</sub> = 3mA                                                                                    |     |     | 0.4 | V               |

| SDA Current Sinking Capacity | I <sub>SDA</sub>                   |                                                                                                           | 3   |     |     | mA              |

| INT Low Output Voltage       | V <sub>INT</sub>                   | I <sub>INT</sub> = 3mA                                                                                    |     |     | 0.4 | V               |

| INT Leakage Current          | I <sub>LEAK</sub>                  |                                                                                                           | -10 |     | 10  | μA              |

| ADR High Level Input Voltage |                                    |                                                                                                           | 80% |     |     | V <sub>DD</sub> |

| ADR Open                     | V <sub>ADR</sub>                   |                                                                                                           | 40% |     | 60% | V <sub>DD</sub> |

| ADR Low Level Input Voltage  | 1                                  |                                                                                                           |     |     | 20% | $V_{DD}$        |

| ADR Input Leakage Current    | I <sub>ADR</sub>                   |                                                                                                           | -10 |     | 10  | μA              |

Notes:

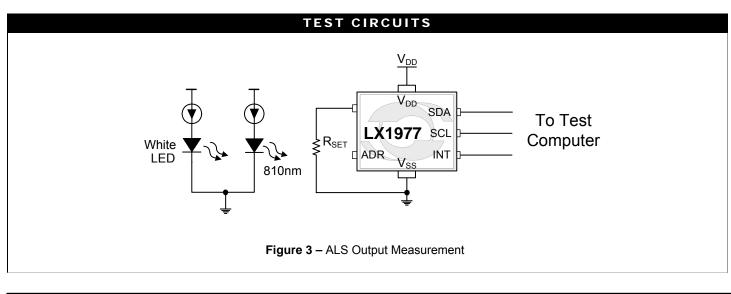

1. In production, the input irradiance is supplied from a point source which is a white LED.

2. See Figure 3

3.  $\Delta_{IR} = \frac{D_{COUNT}(E_{V(WHITE)} + E_{V(IR)}) - D_{COUNT}(E_{V(WHITE)})}{2}$

DCOUNT (EV(WHITE))

4. Guarantee by scan tests.

5. Specifications in the EC table are for 3.0V ~ 4.5V. Device is operational down to 2.5V and up to 5.0V with relaxed specifications.

$6. \ Gain1 = (D_{COUNT}2-D_{COUNT}1) / (Lux2-Lux1), \ Gain2 = (D_{COUNT}3-D_{COUNT}2) / (Lux3-Lux2), \ DNL1 = (Gain1 * 2 / (Gain1+Gain2) -1) \%, \ DNL2 = (Gain2 * 2 / (Gain1+Gain2) -1) \%. \ Lux1 = 100 \ lux, \ Lux2 = 200 \ lux, \ Lux3 = 500 \ lux.$

7. For the setting RANGE\_SEL=00b and  $T_{INT}$ =100mS, the full scale output is typical 3723 decimal. A dark ADC output count of maximum 18 at  $T_A$  = 70°C is only 0.5% of 3723.

# LX1977

# **SMBus Ambient Light Sensor**

**PRODUCTION DATASHEET**

## APPLICATION NOTE

### **BASIC FUNCTIONALITY**

The LX1977 is an ALS with an  $I^2C$  compatible SMBus interface. It contains a high sensitivity close to human eye response photodiode, a 12-bit Sigma-Delta ADC and a SMBus interface. The Sigma-Delta ADC converts photodiode current to digital values that correspond to the light incident on the photodiode. The integrating nature of the ADC allows the device to reject 50Hz and 60Hz flicker noise from environmental lighting.

The Sigma-Delta ADC provides the flexibility to set different conversion times, or integration time. It has four conversion time selections to meet different application requirements. The clock source for the ADC is also selectable from either an internal clock or a SMBus clock. For internal clock selection, the device features full speed (40.96kHz) and guarter speed (10.24kHz) selection. The ADC conversion result is stored in a 12-bit register for read back even when another conversion is in process.

### **SMBus INTERFACE**

LX1977 is a nine-register device which uses SMBus or I<sup>2</sup>C protocols to communicate with the host system. All registers are defined as full byte wide. Some registers contain reserved (undefined) bits with a default value of "0", or are read only bits that are status indicators. Six of the nine registers are capable of both read and write, and three registers are read only. See the LX1977 Register Definitions section for details.

The LX1977 communicates over the SMBus and operates in a "slave" mode receiving commands and sending / receiving data to / from the host or "master". Only standard two-wire SMBus and I<sup>2</sup>C compatible serial bus and protocols may be used for this device. The LX1977 can be configured for one of the three addresses by connecting the ADR input pin to ground, V<sub>DD</sub>, or simply leaving it OPEN.

| Table  | 1. | A ddmoor | atuannina | aadaa |

|--------|----|----------|-----------|-------|

| I able | 1: | Address  | strapping | codes |

| <b>Option</b> # | ADR             | Hex Address |

|-----------------|-----------------|-------------|

| 1               | GND             | 20h         |

| 2               | OPEN            | 22h         |

| 3               | V <sub>DD</sub> | 70h         |

In this document, the device address is always expressed as full 8 bit address. The high nibble of the address is from bit 7 to bit 4. In the low nibble, bit 0 is always the R/W bit and in 8 bit address format it is considered 0.

The address could be changed dynamically. The requirement is that after the change, the LX1977 ALS should be disabled and then enabled either via bit 6 of register 00h or a V<sub>DD</sub> power cycle.

Table 2: Address = 20h

| 1 | 7             | 1  | 1 | 8         | 1 | 1 |

|---|---------------|----|---|-----------|---|---|

| S | Slave Address | Wr | Α | Data Byte | Α | Р |

|   | 0010000       | 0  |   |           |   |   |

#### Table 3: Address = 22h

| 1 | 7             | 1  | 1 | 8         | 1 | 1 |

|---|---------------|----|---|-----------|---|---|

| S | Slave Address | Wr | Α | Data Byte | Α | Р |

|   | 0010001       | 0  |   |           |   |   |

Table 4: Address = 70h

| 1 | 7             | 1  | 1 | 8         | 1 | 1 |

|---|---------------|----|---|-----------|---|---|

| S | Slave Address | Wr | Α | Data Byte | Α | Ρ |

|   | 0111000       | 0  |   |           |   |   |

### **SMBus PROTOCOL**

The only required command protocols are SMBus Send Byte, Receive Byte, Read Byte / Word, and the Write Byte / Word protocols. See Table 7 ~ Table 12 for details.

Writes to registers can be performed by either the SMBus Write Byte / Word protocols and / or by internal IC logic, depending on the register type (see Table 13). Send Byte protocol can only be used on the Command / Status register (register 00h).

Read can be performed on all registers by issuing the Read Byte / Word protocol. Note that Receive Byte protocol can only be used on the Command / Status register (register 00h) for a quick test of the status bits. Read Only registers can be written only by internal logics. Their contents will not be affected by SMBus write commands.

When LX1977 is initially powered, it will first test the address selection pin input to determine its own address and then look for its unique address each time it detects a "Start Condition". If the address does not match, the LX1977 ignores all bus activity until it encounters another "Start Condition". If the address is a match, the LX1977 acknowledges that it has detected its address and a W/R bit to either read or write. If the

Microsemi

# SMBus Ambient Light Sensor

# **PRODUCTION DATASHEET**

## APPLICATION NOTE

W/R bit is a "0", signifying a "Write" command, the next byte of data sent from the host will be a Data Byte or a Command Code (also called index), depending on whether there is a Stop Condition afterwards. If there is a Stop Condition, then the received byte is a data byte (not a Command Code or register index) to the LX1977 and this command will be sent to register 00h and executed. Note that this is considered a Send Byte Protocol, which can only be used on register 00h as stated before. If there is no Stop Condition detected, then the received byte is a Command Code (or register index). In this case, either one or two bytes of data will follow. The index points to an internal register in the LX1977 that will be the object of the subsequent data transfer.

In a Write protocol, the LX1977 will acknowledge the receipt of a valid index. After the index, there will be another byte / word of data; this byte of data will be loaded into the indexed register. In LX1977 Read / Write word protocols, the Command Code (or register index) will always be the lower byte data register address. The higher byte of the data will be loaded into the register corresponding to the lower byte register index / command code incremented by 1.

The LX1977 will ignore all additional bus activity once it has acknowledged the receipt of the data byte(s) followed by a "Stop Condition", and until the next "Start Condition" is detected. Note that receipt of a "Stop Condition" or "Start Condition" will reset the address detection state machine. The LX1977 does not support "Packet Error Code".

The host can read the contents of register 00h which contains the device status bits by issuing a simple Receive Byte protocol. In this command line, the W/R bit is set to a "1". Upon the receipt of a Receive Byte protocol, the LX1977 will acknowledge that it has detected its address and a valid W/R bit; the device will then put a copy of the register 00h data onto the bus.

The host can read the contents of the indexed register(s) within the LX1977 using a Read Byte / Word protocol. In this protocol, the host first will send a Write command indicating the device address and Command Code. After the write command is issued, the host initiates a repeat "Start Condition" followed by issuing a Read from device's address.

In Read protocol, the Command Code is the index of the register(s) to be read. The repeat "Start Condition" will be followed by the Slave address (refer to Table 11 and Table 12) and a read command bit. Upon receipt of a Read command, the LX1977 will acknowledge that it has detected its address and a valid Read bit. Subsequently, one byte of data starting from the indexed register address will be put onto the bus. A NACK from the host signifies the end of the Read command. If instead, an ACK is received, then the LX1977 will put another byte of data from the next incremented register address onto the bus. A NACK will signify the end of the Read command. Once the LX1977 has placed the byte(s) of data on the serial bus, it will ignore all additional bus activity until the next "Start Condition" is detected.

LX1977

# **PRODUCTION DATASHEET**

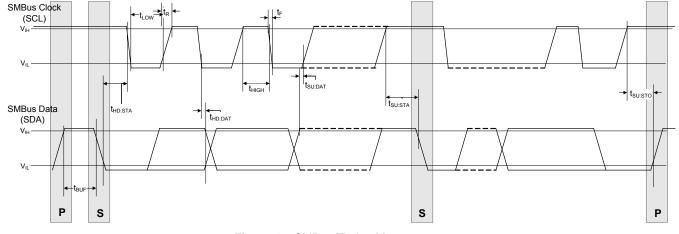

# SMBUS COMMON AC SPECIFICATIONS

The diagram below illustrates the various SMBus timings and sets the context for the specifications to follow. Note that the following are not production tested specifications, but are common SMBus protocol specifications practiced.

| Symbol              | Parameter                                                                                    | FAST_N | Units |       |

|---------------------|----------------------------------------------------------------------------------------------|--------|-------|-------|

| Symbol              | r al ameter                                                                                  | MIN    | MAX   | Units |

| F <sub>SMB</sub>    | SMBus Operating Frequency                                                                    | 10     | 400   | kHz   |

| T <sub>BUF</sub>    | Bus free time between Stop and Start Condition                                               | 1.3    | -     | μs    |

| T <sub>HD:STA</sub> | Hold time after (Repeated) Start Condition. After this period, the first clock is generated. | 0.6    | -     | μs    |

| T <sub>SU:STA</sub> | Repeated Start Condition setup time                                                          | 0.6    | -     | μs    |

| T <sub>SU:STO</sub> | Stop Condition setup time                                                                    | 0.6    | -     | μs    |

| T <sub>HD:DAT</sub> | Data hold time                                                                               | 0      | 0.9   | μs    |

| T <sub>SU:DAT</sub> | Data setup time                                                                              | 100    | -     | ns    |

| T <sub>LOW</sub>    | Clock low period                                                                             | 1.3    | -     | μs    |

| T <sub>HIGH</sub>   | Clock high period                                                                            | 0.6    | -     | μs    |

| T <sub>F</sub>      | Clock / Data Fall Time                                                                       | -      | 300   | ns    |

| T <sub>R</sub>      | Clock / Data Rise Time                                                                       | -      | 300   | ns    |

| T <sub>POR</sub>    | Time in which a device must be operational after power-on reset                              |        | 500   | ms    |

| C <sub>IN</sub>     | Capacitance for SCL or SDA pin                                                               |        | 10    | pF    |

## Table 5: SMBus (I<sup>2</sup>C compatible) Timing

LX1977

PRODUCTION DATASHEET

## **SMBUS COMMUNICATION PROTOCOL**

LX1977 employs the following SMBus 2.0 protocols that are also compatible to  $I^2C$  protocols. Protocols used to communicate with LX1977 must be per standard SMBus specification version 2.0 or higher.

- Send Byte

- Receive Byte

- Write Byte

- Write Word

- Read Byte

- Read Word

The individual protocol format is shown in tables below. For a complete description of SMBus protocols, please review the SMBus Specification at <u>www.smbus.org/specs</u>.

|              |                                                    |                 |               |               |   | 0                                                                         |       | • |                                  |    |

|--------------|----------------------------------------------------|-----------------|---------------|---------------|---|---------------------------------------------------------------------------|-------|---|----------------------------------|----|

|              |                                                    | S               | Slave Address | Wr            | Α | Data Byte                                                                 | Α     | Р |                                  |    |

|              |                                                    |                 |               |               | X |                                                                           | X     |   |                                  |    |

| S<br>Wr<br>P | Start Cone<br>Write (bit<br>Stop Cone<br>Master-to | value<br>lition | e of 0)       | Rd<br>A<br>Co |   | Read (bit value o<br>Acknowledge ('0<br><b>nd Code</b><br>Slave-to-Master | ' for |   | CK, or '1' for a NACK<br>Address | .) |

**Table 6: SMBus Packet Protocol Diagram Element Key**

Grey shading represents cycles during which the LX1977 "owns" or "drives" the Data line. All other cycles are driven by the host.

| Table 7: Send Byte Protocol |  | Table | 7: | Send | Byte | Protocol | : |

|-----------------------------|--|-------|----|------|------|----------|---|

|-----------------------------|--|-------|----|------|------|----------|---|

| 1 | 7             | 1  | 1 | 8         | 1 | 1 |

|---|---------------|----|---|-----------|---|---|

| S | Slave Address | Wr | Α | Data Byte | Α | Р |

|   |               | 0  |   |           |   |   |

### **Table 8: Receive Byte Protocol:**

| 1 | 7             | 1  | 1 | 8         | 1 | 1 |

|---|---------------|----|---|-----------|---|---|

| S | Slave Address | Rd | Α | Data Byte | A | Р |

|   |               | 1  |   |           | 1 |   |

#### **Table 9: Write Byte Protocol:**

| 1 | 7             | 1  | 1 | 8            | 1 | 8         | 1 | 1 |

|---|---------------|----|---|--------------|---|-----------|---|---|

| S | Slave Address | Wr | Α | Command Code | Α | Data Byte | Α | Р |

|   |               | 0  |   |              |   |           |   |   |

#### **Table 10: Write Word Protocol:**

| 1 | 7             | 1  | 1 | 8            | 1 | 8             | 1 | 8              | 1 | 1 |

|---|---------------|----|---|--------------|---|---------------|---|----------------|---|---|

| S | Slave Address | Wr | Α | Command Code | Α | Data Byte Low | Α | Data Byte High | Α | Р |

|   |               | 0  |   |              |   |               |   |                |   |   |

Downloaded from Elcodis.com electronic components distributor

### **PRODUCTION DATASHEET**

#### **Table 11: Read Byte Protocol:**

| 1 | 7             | 1  | 1 | 8            | 1 | 1 | 7             | 1  | 1 | 8         | 1 | 1 |

|---|---------------|----|---|--------------|---|---|---------------|----|---|-----------|---|---|

| S | Slave Address | Wr | Α | Command Code | Α | S | Slave Address | Rd | Α | Data Byte | A | Р |

|   |               | 0  |   |              |   |   |               | 1  |   |           | 1 |   |

### Table 12: Read Word Protocol:

| 1 | 7             | 1  | 1 | 8            | 1 | 1 | 7             | 1  | 1 | 8             | 1 | 8              | 1 | 1 |

|---|---------------|----|---|--------------|---|---|---------------|----|---|---------------|---|----------------|---|---|

| S | Slave Address | Wr | Α | Command Code | Α | S | Slave Address | Rd | Α | Data Byte Low | Α | Data Byte High | Α | Р |

|   |               | 0  |   |              |   |   |               | 1  |   |               |   |                | 1 |   |

### **SMBUS REQUIREMENTS**

- When the ALS SMBus interface is not powered, it will not affect other SMBus traffic that may occur. The SMBus interface pins should be in high impedance mode when the interface is not powered.

- SMBus pull-up resistors should be provided on the system, and is not provided by the LX1977 device.

- The ALS shall NACK any SMBus operation directed to it that addresses a register that is not defined in this specification.

## **SMBus DE-FEATURING**

Package Error Correction, Alarm function and the Address Resolution protocols are not supported by this device.

## **LX1977 REGISTER DEFINITIONS**

| Register(hex) | <b>R / W</b> |                           | Description                                          |

|---------------|--------------|---------------------------|------------------------------------------------------|

| 00h           | R / W        | Command / Status          | Device Control and Status                            |

| 01h           | R / W        | Device Control            | ALS ADC Control                                      |

| 02h           | R / W        | Low-Threshold LSB         | Lower byte of the Interrupt low threshold window     |

| 03h           | R / W        | Low-Threshold MSB         | Higher 4 bits of the Interrupt low threshold window  |

| 04h           | R / W        | High-Threshold LSB        | Lower byte of the Interrupt high threshold window    |

| 05h           | R / W        | High-Threshold MSB        | Higher 4 bits of the Interrupt high threshold window |

| 06h           | R            | LSB of D <sub>COUNT</sub> | Lower byte of the ADC result                         |

| 07h           | R            | MSB of D <sub>COUNT</sub> | Higher 4 bits of the ADC result                      |

| 08h           | R            | ID Register               | Part Identification                                  |

### Table 13: LX1977 Register Definitions

Detailed descriptions of the individual register are shown below.

LX1977

177613

**PRODUCTION DATASHEET**

Command Register 00h (R / W)

|           |              | Та           | ble 14: Comm | and Register ( | loh          |              |           |

|-----------|--------------|--------------|--------------|----------------|--------------|--------------|-----------|

| 7         | 6            | 5            | 4            | 3              | 2            | 1            | 0         |

| ADC_FLAG  | ALS_ENA      | START_ADC    | ADC_MOD      | ADC_CLK        | INT_FLAG     | INT_ENA      | OV        |

| Read Only | Read / Write | Read / Write | Read / Write | Read / Write   | Read / Write | Read / Write | Read Only |

### Index Address = 00000000b or 00h Access = Read / Write Default = 0000000b

This register contains bits for configuring and controlling LX1977 and also bits showing LX1977 operation status.

## **Bit Definitions:**

- ADC\_FLAG (bit 7, R): This is a status bit and is a read only bit. When START\_ADC is set to 1, 0 on this bit indicates ADC conversion is in process, 1 indicates conversion is done and the D<sub>COUNT</sub> data is ready in register 06h & 07h. Setting START\_ADC to 1 will clear ADC\_FLAG bit and start a new conversion regardless the status of the ADC converter. The time needed to finish a conversion will depend on the T<sub>INT</sub>\_SET setting in Device Control Register 01h bit 0 & 1.

- ALS\_ENA (bit 6, R / W): 0 on this bit means power down ALS and ADC of this device, 1 means power up ALS and ADC.

- START\_ADC (bit 5, R / W): Writing 1 to this bit will start a new ADC conversion and clear the ADC\_FLAG bit. Writing 0 to this bit stops (or disable) ADC conversion and also resets the internal interrupt persistent control counter when ADC\_MOD bit is set to 1. When this bit is 0, ADC\_FLAG bit will not be meaningful.

- ADC\_MOD (bit 4, R / W): 0 on this bit sets ADC to one time conversion mode and 1 sets ADC to continuous mode when START\_ADC bit is set to 1.

Note:

These two bits should be controlled together. When these two bits are set to 11, LX1977 will be in continuous mode. When a restart of the continuous mode is need, 01 should be written to these bits and then 11 should be written afterwards. In this case, ADC\_FLAG, INT\_FLAG and the internal counter for INT\_PERSIST\_CTRL will be reset to 0.

| START_ADC<br>(Bit 5) | ADC_MOD<br>(Bit 4) | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                    | 0                  | Disable ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0                    | 1                  | Disable ADC and reset internal interrupt persistent control counter, ADC_FLAG and INT_FLAG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1                    | 0                  | <ul> <li>Set ADC to one time conversion mode and start the conversion. ADC_FLAG bit will indicate conversion status, 0 on this bit means conversion is in process, 1 means conversion is done and data is ready in register 06h and 07h. Interrupt persistent control function is not applicable to this mode.</li> <li>Note: <ol> <li>When this mode is set, the ADC_FLAG will be set to zero right away.</li> <li>When conversion is done, Bit 5 and Bit 4 will be changed from 10 to 00 automatically. If a new conversion is needed, 10 should be written to Bit5 and Bit 4 again.</li> </ol> </li> </ul> |

### Table 15: Bit 5 & 4 Definitions

Copyright © 2010 Rev. 1.0, 2010-03-25

# Microsemi

Analog Mixed Signal Group 11861 Western Avenue, Garden Grove, CA. 92841, 714-898-8121, Fax: 714-893-2570

### **PRODUCTION DATASHEET**

| 1 | 1 | Set ADC to continuous conversion mode and start conversion. ADC_FLAG indicates conversion status, 0 means conversion is in process, 1 means previous conversion is done and data is ready in register 07h and 08h. Actually, after the first conversion, this bit will be always 1. Interrupt function applies to this mode. |

|---|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |   | Note: When this mode is set, the ADC_FLAG will be set to zero right away.                                                                                                                                                                                                                                                    |

ADC\_CLK (bit 3, R / W): Selects the internal ADC clock speed when CLK\_SEL (bit 7) of register 01h is 0

- = 0, select clock speed to normal (40.96 kHz)

- = 1, select clock speed to  $\frac{1}{4}$  normal (10.24 kHz)

When clock speed is selected, the selectable integration time set will be determined automatically. For example, when  $ADC\_CLK = 1$ , the selectable integration time will be 25ms, 100ms, 200ms or 400ms. Please refer to Table 24 for details.

INT\_FLAG (bit 2, R / W): Interrupt Status Report

- = 0, no interrupt or was cleared. This bit can be set to 1 or 0 by SMBus command. Setting zero to this bit will set the INT pin to high regardless of the previous state. When it is set to zero, the internal counter for **INT\_PERSIST\_CTRL** will be reset to 0.

- = 1, interrupt triggered. When this bit is 1 and INT\_ENA = 1, the INT pin will be asserted low and stay low until this bit is set to zero or INT\_ENA = 0. Writing 1 to this bit will override any internal setting and generate an interrupt if INT\_ENA = 1. This function is useful for testing user hardware and debugging software.

### Note:

ADC will continue to run regardless of the interrupt status unless it is stopped by setting **START\_ADC** bit to 0. Note that the ADC integration time is much longer than the interrupt response time. Data output of the ADC that generated the interrupt must be read immediately as the next sampled data by the ADC will write over the  $D_{COUNT}$  register during continuous conversion mode.

INT\_ENA (bit 1, R / W): Interrupt Enable Bit

- = 0, Disable interrupt pin function

- = 1, Enable interrupt pin function

## Note:

- (1) When INT\_ENA = 0, the INT pin function will be disabled. However, the INT\_FLAG function could still be used as software interrupt to monitor the ALS readings. The user can still set the thresholds and read the INT\_FLAG status periodically or when it is needed instead of reading the ALS data and calculating. If the INT\_FLAG = 1, then it means the ALS reading is outside the boundaries. If this function is not needed, the user just simply ignores the INT\_FLAG bit status.

- (2) When **INT\_ENA = 1**, the INT pin will perform the normal interrupt function.

- (3) When **ALS\_ENA = 0**, the INT pin will be set to high regardless of its previous status.

## OV (bit 0, R): Overflow Indicator.

- = 0, if  $D_{COUNT}$  has reached the maximum value and this bit is still 0, it means that the input light has reached the maximum range but not over.

- = 1, 1 on this bit indicates that the  $D_{COUNT}$  has reached the maximum value and the input light is over the selected range limit. Bigger range should be selected.

# Table 16: Maximum Count for Different T<sub>INT</sub> Time

| Full Scale ADC Output Value<br>@ F <sub>OSC</sub> = 40.96kHz, | D <sub>COUNT</sub> | T <sub>INT</sub> = 100 ms | 4095 | Counts |

|---------------------------------------------------------------|--------------------|---------------------------|------|--------|

| $RANGE\_SEL = 00b (0 \sim 500 lux)$                           | D <sub>COUNT</sub> | T <sub>INT</sub> = 50 ms  | 2047 |        |

Downloaded from Elcodis.com electronic components distributor

11861 Western Avenue, Garden Grove, CA. 92841, 714-898-8121, Fax: 714-893-2570

**PRODUCTION DATASHEET**

| RANGE_SEL = $01b (0 \sim 1000 \text{ lux})$<br>RANGE_SEL = $10b (0 \sim 5000 \text{ lux})$ | D <sub>COUNT</sub> | T <sub>INT</sub> = 25 ms   | 1023 |  |

|--------------------------------------------------------------------------------------------|--------------------|----------------------------|------|--|

| RANGE_SEL = $11b (0 \sim 2500 \text{ lux})$                                                | D <sub>COUNT</sub> | T <sub>INT</sub> = 6.25 ms | 255  |  |

Note:

ADC output count will be always in the range as specified in the above table. For example, if the  $T_{INT}$  is set to 6.25ms, the ADC output count will be less or equal to 255

### **Register 00h and Send / Receive Byte Protocols application:**

When host wants to send control command(s) that is contained in Register 00, for example Enable / Disable ALS or Start ADC conversion, the Send Byte Protocol could be used to simplify the communication. In Send Byte Protocol, bit 7 of the Data Byte field should be set to 1 indicating this is a direct command and this command should be put into Register 00h and executed. The example is shown in Table 17.

| 1 | 7             | 1  | 1 | Bit 7    | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | 1 | 1 |

|---|---------------|----|---|----------|-------|-------|-------|-------|-------|-------|-------|---|---|

| s | Slave Address | Wr | Α | CMD_FLAG |       |       |       |       |       |       |       | Α | Р |

|   |               | 0  |   | 1        |       |       |       |       |       |       |       |   |   |

Write Byte Protocol could also be used to implement the same function but with a longer communication time.

When using Write Byte / Word protocol to send command / data to registers (including register 00h), bit 7 in command code field should be set to 0 to indicate this byte is for the register address. Bit 6, 5 & 4 except for the Register Address bits (bit 3, 2, 1 & 0) need to be set to zero also. These bits in this command are used for internal test purpose. The detailed Write Byte / Read Byte protocols are shown below.

### **Table 18: Write Byte Protocol**

| 1 | 7             | 1  | 1 | Bit 7    | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | 1 | 8         |   | 1 |

|---|---------------|----|---|----------|-------|-------|-------|-------|--------|-------|-------|---|-----------|---|---|

| S | Slave Address | Wr | Α | CMD_FLAG | 0     | 0     | 0     | Re    | gister | Addre | ess   | Α | Data Byte | Α | Р |

|   |               | 0  |   | 0        |       |       |       |       | 00 ~   | 08h   |       |   |           |   |   |

Register 00h could be read back by the host via Receive Byte protocol or Read Byte protocol. When LX1977 receives a Receive Byte protocol, it will send a copy of register 00 data back to the host. When it receives Read Byte protocol, it will put register 00 data in the Data Byte field and send the data back to host. See Table 11 & Table 19 for details.

#### **Table 19: Read Byte Protocol**

| 1 | 7             | 1  | 1 | Bit 7    | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2   | Bit 1   | Bit 0 | 1 | 1 | 7             | 1  | 1 | 8         |   | 1 |

|---|---------------|----|---|----------|-------|-------|-------|-------|---------|---------|-------|---|---|---------------|----|---|-----------|---|---|

| S | Slave Address | Wr | Α | CMD_FLAG | 0     | 0     | 0     | F     | Registe | r Addre | ess   | Α | S | Slave Address | Rd | Α | Data Byte | Α | Ρ |

|   |               | 0  |   | 0        |       |       |       |       | 00      | ~ 08h   |       |   |   |               | 1  |   |           | 1 |   |

### Examples of setting register 00h by using Send Byte Protocol

One of the sample LX1977 settings and Send Byte protocol could be as shown below.

### **Table 20: Sample Send Byte Protocol**

| 1 | 7             | 1  | 1 | Bit 7    | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | 1 | 1 |

|---|---------------|----|---|----------|-------|-------|-------|-------|-------|-------|-------|---|---|

| S | Slave Address | Wr | Α | CMD_FLAG |       |       |       |       |       |       |       | Α | Р |

|   |               | 0  |   | 1        | 1     | 1     | 1     | 0     | 0     | 1     | 1     |   |   |

Downloaded from Elcodis.com electronic components distributor

11861 Western Avenue, Garden Grove, CA. 92841, 714-898-8121, Fax: 714-893-2570

# **PRODUCTION DATASHEET**

This protocol will send commands to LX1977 and will write the command byte into register 00h for configuring the device settings.

- 1) Bit 6 will enable LX1977 ALS function

- 2) Bit 5, 4 will set ADC mode to Continuous Conversion Mode and start ADC

- 3) Bit 3 will select 40.96 kHz clock frequency as the Sigma-Delta ADC clock

- 4) Bit 2 will clear the interrupt flag no matter what it was

- 5) Bit 1 will enable the interrupt function

- 6) Bit 0 will be ignored since bit 0 of register 00h is a read only bit

### Device Control Register 01h (R / W)

### Table 21: Control Register 01h

| 7            | 6            | 5     | 4                | 3       | 2               | 1 | 0 |  |

|--------------|--------------|-------|------------------|---------|-----------------|---|---|--|

| CLK_SEL      | RANG         | E_SEL | T <sub>INT</sub> | SET     | INT_PERSIST_SET |   |   |  |

| Read / Write | Read / Write |       | Read             | / Write | Read / Write    |   |   |  |

Index Address = 00000001b or 01h Access = Read / Write Default = 0000000b

### **Bit Definitions:**

CLK\_SEL (bit 7, R / W): Selects the source of the ADC clock

- = 0, use internal clock (the actual speed will depend on bit 3 of register 00h setting)

- = 1, use SMBus host SCL clock. Since the clock gap between protocols is inconsistent, this mode is not recommended.

RANGE\_SEL (bit 6, 5, R / W): Selects the detectable input light range.

Table 22: ADC T<sub>INT</sub>, Range and Resolution @ ADC Clock = 40.96 kHz

| <b>D</b> '' | D'4 5 | Full Scale<br>Range (lux) |                                               | <b>Resolution in Lux /Count</b>             |                                              |                                               |  |  |  |  |  |

|-------------|-------|---------------------------|-----------------------------------------------|---------------------------------------------|----------------------------------------------|-----------------------------------------------|--|--|--|--|--|

| Bit 6       | Bit 5 |                           | $T_{INT} = 6.25 \text{ ms}$ $D_{COUNT} = 233$ | $T_{INT} = 25 \text{ ms}$ $D_{COUNT} = 931$ | $T_{INT} = 50 \text{ ms}$ $D_{COUNT} = 1861$ | $T_{INT} = 100 \text{ ms}$ $D_{COUNT} = 3723$ |  |  |  |  |  |

| 0           | 0     | 0~500                     | 2.15                                          | 0.54                                        | 0.27                                         | 0.13                                          |  |  |  |  |  |

| 0           | 1     | 0~1000                    | 4.29                                          | 1.07                                        | 0.54                                         | 0.27                                          |  |  |  |  |  |

| 1           | 0     | 0~5000                    | 21.46                                         | 5.37                                        | 2.69                                         | 1.34                                          |  |  |  |  |  |

| 1           | 1     | 0~2500                    | 10.73                                         | 2.68                                        | 1.34                                         | 0.67                                          |  |  |  |  |  |

| Table 23. ADC Tau   | <b>Range and Resolution</b> | @ ADC Clo | ck – 10 24 kHz  |

|---------------------|-----------------------------|-----------|-----------------|

| Table 23. ADC TINT, | Kange and Kesolution        | W ADC CIU | LK – 10.24 KIIZ |

| Die   | D     | Full Scale  |                                             | <b>Resolution in Lux /Count</b>              |                                               |                                               |  |  |  |  |  |

|-------|-------|-------------|---------------------------------------------|----------------------------------------------|-----------------------------------------------|-----------------------------------------------|--|--|--|--|--|

| Bit 6 | Bit 5 | Range (lux) | $T_{INT} = 25 \text{ ms}$ $D_{COUNT} = 233$ | $T_{INT} = 100 \text{ ms}$ $D_{COUNT} = 931$ | $T_{INT} = 200 \text{ ms}$ $D_{COUNT} = 1861$ | $T_{INT} = 400 \text{ ms}$ $D_{COUNT} = 3723$ |  |  |  |  |  |

| 0     | 0     | 0~500       | 2.15                                        | 0.54                                         | 0.27                                          | 0.13                                          |  |  |  |  |  |

| 0     | 1     | 0~1000      | 4.29                                        | 1.07                                         | 0.54                                          | 0.27                                          |  |  |  |  |  |

| 1     | 0     | 0~5000      | 21.46                                       | 5.37                                         | 2.69                                          | 1.34                                          |  |  |  |  |  |

Downloaded from Elcodis.com electronic components distributor

### **Microsemi** Analog Mixed Signal Group

11861 Western Avenue, Garden Grove, CA. 92841, 714-898-8121, Fax: 714-893-2570

Page 13

**PRODUCTION DATASHEET**

| 1 | 1 | $0 \sim 2500$ | 10.73 | 2.68 | 1.34 | 0.67 |

|---|---|---------------|-------|------|------|------|

When range is selected, the  $D_{COUNT}$  values with different input lux will also change. Please refer to the EC table for the values of  $0 \sim 500 \text{ lux}$ ,  $0 \sim 1000 \text{ lux}$ ,  $0 \sim 5000 \text{ and } 0 \sim 2500 \text{ lux}$  light input. The equations for calculating between  $D_{COUNT}$  and lux are shown below.

T<sub>INT</sub>\_SET (bit 4, 3, R / W): ADC integration (conversion) time control. The relationship between bit settings and integration times are shown in table below.

|          |          |                           |                               |             | 3                                             |                               |             |  |  |  |  |  |  |

|----------|----------|---------------------------|-------------------------------|-------------|-----------------------------------------------|-------------------------------|-------------|--|--|--|--|--|--|

|          |          | Conversion Time / Reading |                               |             |                                               |                               |             |  |  |  |  |  |  |

|          |          | Register 00h, B           | it $3 = 0$ , ADC Clock        | = 40.96kHz  | Register 00h, Bit 3 = 1, ADC Clock = 10.24kHz |                               |             |  |  |  |  |  |  |

| Bit<br>4 | Bit<br>3 | Integration Time          | Nominal Full<br>Range Reading | Max Reading | Integration Time                              | Nominal Full<br>Range Reading | Max Reading |  |  |  |  |  |  |

| 0        | 0        | 6.25 ms                   | 233                           | 255         | 25 ms                                         | 233                           | 255         |  |  |  |  |  |  |

| 0        | 1        | 25 ms                     | 931                           | 1023        | 100 ms                                        | 931                           | 1023        |  |  |  |  |  |  |

| 1        | 0        | 50 ms                     | 1861                          | 2047        | 200 ms                                        | 1861                          | 2047        |  |  |  |  |  |  |

| 1        | 1        | 100 ms                    | 3723                          | 4095        | 400 ms                                        | 3723                          | 4095        |  |  |  |  |  |  |

**Table 24: ALS ADC Integration Time**

### Light input Lux and D<sub>COUNT</sub> calculation:

LX1977 output  $D_{COUNT}$  is in a linear relationship with the light input lux.  $D_{COUNT}$  full scale values are determined by integration time as shown above. In the Electrical Characteristics table,  $D_{COUNT}$  values are listed in accordance with the specified light input at ADC Clock = 40.96 kHz, integration time = 100ms and at 0 ~ 500 lux, 0 ~ 1000 lux, 0 ~ 5000 lux and 0 ~ 2500 lux range.  $D_{COUNT}$  values are related to integration time and the measurement range selected. Below are the conversion methods between  $D_{COUNT}$  and light input lux at different integration time.

$D_{COUNT} = (Input (lux) / Range) \times (Nominal Full Range Reading)$  Refer to Table 24

For example:  $0 \sim 500$  lux range, 100 lux input, integration time = 50ms

$D_{COUNT} = 100/500 \times 1861 = 372$  Refer to Table 24

For example:  $0 \sim 1000$  lux range, 500 lux input, integration time = 100ms

$D_{COUNT} = 500/1000 \times 3723 = 1862$  Refer to Table 24

- = 000, generate interrupt after ADC conversion

- = 001, generate interrupt if ADC result out of range

- = 010, generate interrupt if ADC result out of range for 2 consecutive  $T_{INT}$  time

- = 011, generate interrupt if ADC result out of range for 3 consecutive  $T_{INT}$  time

- = 100, generate interrupt if ADC result out of range for 4 consecutive  $T_{INT}$  time

- = 101, generate interrupt if ADC result out of range for 5 consecutive  $T_{INT}$  time

- = 110, generate interrupt if ADC result out of range for 10 consecutive  $T_{INT}$  time

Downloaded from Elcodis.com electronic components distributor

## **PRODUCTION DATASHEET**

= 111, generate interrupt if ADC result out of range for 15 consecutive  $T_{INT}$  time

Note:

- (1) When INT\_FLAG of register 00h is cleared via SMBus command after an interrupt response, the internal counter for INT\_PERSIST\_CTRL will be reset to 0.

- (2) For out-of-range conditions in the same direction, the persistence counter increments. If within the programmed T<sub>INT</sub> time period, anytime an ADC conversion completes and the result is no longer out-of-range, the count starts over. If the output result is between the thresholds (in-range), then counter resets to '0'. If the value goes out of range in the other direction, the counter starts over at '1'.

- (3) Note that once the interrupt is triggered and the INT pin is asserted low, the INT pin will stay low until INT FLAG bit is set to zero or INT ENA is set to 0.

- (4) Generating an interrupt for x consecutive  $T_{INT}$  integration time only applies to continuous conversion mode.

### Register 01h and Write / Read Byte Protocols application:

For programming register 01h, a Write Byte protocol should be used.

When using Write Byte / Word protocol to send command / data to registers (including register 00h), bit 7 in command code field should be set to 0 to indicate this byte is for the register address. Other bits (bit 6, 5 & 4) except for the Register Address bits (bit 3, 2, 1 & 0) need to be set to zero also. The detailed Write Byte / Read Byte protocols are shown below.

Note: Register 01h should be set prior to register 00h in order to get meaningful ALS read out.

| Tab | le 25: | Writ | e Byte | e Prot | cocol: |  |

|-----|--------|------|--------|--------|--------|--|

|     |        |      |        |        |        |  |

| 1 | 7             | 1  | 1 | Bit 7    | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | 1 | 8         |   | 1 |

|---|---------------|----|---|----------|-------|-------|-------|-------|-------|-------|-------|---|-----------|---|---|

| S | Slave Address | Wr | Α | CMD_FLAG | 0     | 0     | 0     | 0     | 0     | 0     | 1     | Α | Data Byte | Α | Р |

|   |               | 0  |   | 0        |       |       |       | 01h   |       |       |       |   |           |   |   |

Register 01h could be read back by the host by using a Read Byte protocol. When LX1977 receives a Read Byte protocol, it will put register 01h data into the Data Byte field and send the data back to the host. Please see Table 11 & Table 19 for details.

| 1 | 7             | 1  | 1 | Bit 7    | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | 1 | 1 | 7             | 1  | 1 | 8         |   | 1 |

|---|---------------|----|---|----------|-------|-------|-------|-------|-------|-------|-------|---|---|---------------|----|---|-----------|---|---|

| S | Slave Address | Wr | Α | CMD_FLAG | 0     | 0     | 0     | 0     | 0     | 0     | 1     | Α | s | Slave Address | Rd | Α | Data Byte | Α | Р |

|   |               | 0  |   | 0        |       |       |       |       | 0     | lh    |       |   |   |               | 1  |   |           | 1 |   |

## Examples of setting register 01h by using Write Byte Protocol

Write Byte protocol is shown below (only the Data Byte is in detail, please refer to Table 26).

| 1 | 7             | 1  | 1 |              | 1 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | 1 | 1 |

|---|---------------|----|---|--------------|---|-------|-------|-------|-------|-------|-------|-------|-------|---|---|

| S | Slave Address | Wr | Α | Command Code | Α |       |       |       |       |       |       |       |       | Α | Р |

|   |               | 0  |   |              |   | 0     | 0     | 0     | 1     | 0     | 1     | 0     | 1     |   |   |

Table 27: Write Byte Protocol:

The above example will write data byte 15h into register 01h to set the following configurations:

## **PRODUCTION DATASHEET**

- Bit 7 will select the internal clock 1)

- 2) Bit 6 & 5 will set detectable range to  $0 \sim 500$  lux

- Bit 4, 3 will set the integration time or conversion time to either 50ms or 200ms depending on register 00h bit 3 3) setting. If bit 3 is 0, then the integration time is 50ms, otherwise it is 200ms

- 4) Bit 2, 1 & 0 will set LX1977 to generate interrupt after D<sub>COUNT</sub> is above the high threshold for 5 consecutive times or below the low threshold for 5 consecutive times

Register 01h could be read back by the host by using Read Byte protocol. When LX1977 receives Read Byte protocol, it will put register 01 data in the Data Byte field and send back to host. See Table 11 for details.

### Low Threshold Register 02h, 03h (R / W)

|              |              |              |              | •            | 8            |              |              |

|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| 7            | 6            | 5            | 4            | 3            | 2            | 1            | 0            |

| Bit 7        | Bit 6        | Bit 5        | Bit 4        | Bit 3        | Bit 2        | Bit 1        | Bit 0        |

| Read / Write |

#### Table 28: Low Threshold Lower Byte Register 02h

### Table 29: Low Threshold Higher 4 bits Register 03h

| _ |       |       |       |       |              |              |              |              |  |  |  |  |  |  |

|---|-------|-------|-------|-------|--------------|--------------|--------------|--------------|--|--|--|--|--|--|

|   | 7     | 6     | 5     | 4     | 3            | 2            | 1            | 0            |  |  |  |  |  |  |

|   | 0     | 0     | 0     | 0     | Bit 11       | Bit 10       | Bit 9        | Bit 8        |  |  |  |  |  |  |

|   | N / A | N / A | N / A | N / A | Read / Write | Read / Write | Read / Write | Read / Write |  |  |  |  |  |  |

#### Index Address = 00000010b, 00000011b or 02h, 03h Access = Read / Write **Default** = 0000000b, 0000000b

These two registers set the low threshold value of the interrupt function. If the ALS readout  $D_{COUNT}$  is lower than this value for the period of time set per INT\_PERSIST\_CTRL (register 01h bit 2, 1, 0), the INT\_FLAG will be set to 1 and if the **INT\_ENA** is 1, the INT pin will be pulled low to indicate an interrupt on the INT pin.

For example, if **INT\_ENA** is set to 1 and **INT\_PERSIST\_CTRL = 101** and the integration time is set to 100ms, and if the  $D_{COUNT}$  value is lower than this register value for consecutive five times, i.e. 5 x 100 = 500ms, then an interrupt flag **INT\_FLAG** will be set and if **INT\_ENA = 1**, the INT pin will be asserted low. If the **INT\_PERSIST\_CTRL** programmed time period is not reached and a new D<sub>COUNT</sub> value is between this Low Threshold value and the High Threshold value, the counter for INT\_PERSIST\_CTRL will be reset to zero. If the INT\_PERSIST\_CTRL programmed time period is not reached and a new  $D_{COUNT}$  value is greater than the High Threshold value, the counter starts over at '1'.

Bit 7 to bit 4 in register 03h are always zero and can not be changed.

### High Threshold Register 04h, 05h (R / W)

Downloaded from Elcodis.com electronic components distributor

#### Table 30: High Threshold Lower Byte Register 04h

| 7            | 6            | 5            | 4            | 3            | 2            | 1            | 0            |

|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Bit 7        | Bit 6        | Bit 5        | Bit 4        | Bit 3        | Bit 2        | Bit 1        | Bit 0        |

| Read / Write |

|       | Table 51: High Threshold Higher 4 bits Register USh |       |       |              |              |              |              |  |  |  |  |  |  |

|-------|-----------------------------------------------------|-------|-------|--------------|--------------|--------------|--------------|--|--|--|--|--|--|

| 7     | 6                                                   | 5     | 4     | 3            | 2            | 1            | 0            |  |  |  |  |  |  |

| 0     | 0                                                   | 0     | 0     | Bit 11       | Bit 10       | Bit 9        | Bit 8        |  |  |  |  |  |  |

| N / A | N / A                                               | N / A | N / A | Read / Write | Read / Write | Read / Write | Read / Write |  |  |  |  |  |  |

## Table 21. High Thussheld Highen 4 bits Desiston 05h

Copyright © 2010 Rev. 1.0, 2010-03-25

**PRODUCTION DATASHEET**

Index Address = 00000100b, 00000101b or 04h, 05h Access = Read / Write Default = 11111111b, 00001111b

These two registers set the high threshold value of the interrupt function. If the ALS readout D<sub>COUNT</sub> is higher than this value for the period of time set per **INT\_PERSIST\_CTRL** (register 01h bit 2, 1, 0), The **INT\_FLAG** will be set to 1 and if the **INT\_ENA** is 1, the INT pin will be pulled low to indicate an interrupt on the INT pin.

For example, if **INT\_PERSIST\_CTRL** = 101 and the integration time is set to 100ms, and if the  $D_{COUNT}$  value is higher than this register value for consecutive five times, i.e. 5 x 100 = 500ms, then an interrupt flag **INT\_FLAG** will be set and if **INT\_ENA** = 1, the INT pin will be asserted low. If the **INT\_PERSIST\_CTRL** programmed time period is not reached and a new  $D_{COUNT}$  value is between the Low Threshold value and this High Threshold value, the counter for **INT\_PERSIST\_CTRL** will be reset to zero. If the **INT\_PERSIST\_CTRL** programmed time period is not reached and a new  $D_{COUNT}$  value is lower than Low Threshold value, the counter starts over at '1'.

Bit 7 to bit 4 in register 05h are always zero and can not be changed.

### ALS ADC Data Register 06h, 07h (R)

| 7          | 6          | 5          | 4          | 3          | 2          | 1          | 0          |

|------------|------------|------------|------------|------------|------------|------------|------------|

| Data bit 7 | Data bit 6 | Data bit 5 | Data bit 4 | Data bit 3 | Data bit 2 | Data bit 1 | Data bit 0 |

| a bit 7 | Data bit 6 | Data bit 5 | Data bit 4 | Data bit 3 | Data bit 2 | Data bit 1 | Data b |

|---------|------------|------------|------------|------------|------------|------------|--------|

|         |            |            |            |            |            |            |        |

Table 33: ALS ADC DCOUNT Higher Byte Register 07h

| 7 | 6 | 5 | 4 | 3           | 2           | 1          | 0          |

|---|---|---|---|-------------|-------------|------------|------------|

| 0 | 0 | 0 | 0 | Data bit 11 | Data bit 10 | Data bit 9 | Data bit 8 |

Index Address = 00000110b, 00000111b or 06h, 07h Access = Read Only Default = 00000000h, 00000000h

After each ADC conversion, the ADC output data will be stored in registers 06h and 07h. Once the data is stored, the ADC will start another conversion again. Note that registers 06h and 07h act as a buffer between the ADC output counter and the SMBus interface. Therefore, even when an ADC conversion is in process, the last conversion result will still be available in the registers to read.

Note that for the purpose of ADC data integrity control, when  $T_{INT}$  is greater than 6.25ms (in 40.96kHz Mode), or  $T_{INT}$  is greater than 25ms (in 10.24kHz Mode), Read Word Protocol should be used to read the two bytes of ADC data. If data is read by using Read Byte Protocol two consecutive times to read register 06h and 07h sequentially, the data in these registers might be updated before the time of executing the second Read Byte Protocol. Thus, the second read byte may not correspond to the original value

When  $T_{INT}$  is set to 6.25ms (in 40.96kHz Mode) or 25ms (in 10.24 kHz Mode), Read Byte Protocol could be used to read out the lower byte to reduce the communication time. Since for these integration times, the ADC results will be always less or equal to 255 and only data in register 06h will be relevant. The ADC result is updated per the integration time set by  $T_{INT}$ \_SET (register 01h, bit 4, 3) when ADC is enabled by START\_ADC (register 00h, bit 5).

These two registers can be read any time even while the ADC conversion is in process. When an ADC conversion is in process, the read data will correspond to the last conversion result.

LX1977

**PRODUCTION DATASHEET**

### Identification Register 08h (R)

# Table 34: Identification Register 08h

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|

| MFG4 | MFG3 | MFG2 | MFG1 | MFG0 | REV2 | REV1 | REV0 |

| 0    | 0    | 0    | 0    | 1    | 1    | 0    | 0    |

Index Address = 00001000b or 08h Access = Read Only Default = 00001100b

**PRODUCTION DATASHEET**

www.Microsemi.com

LX1977

**PRODUCTION DATASHEET**

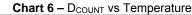

### DCOUNT VS TEMP

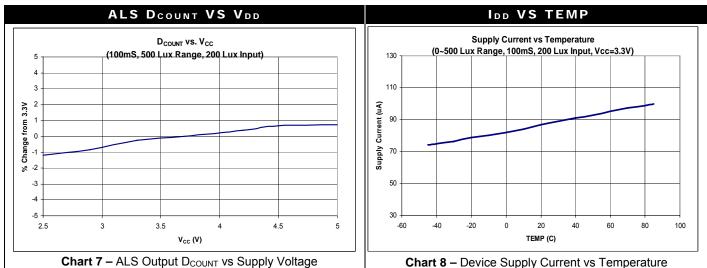

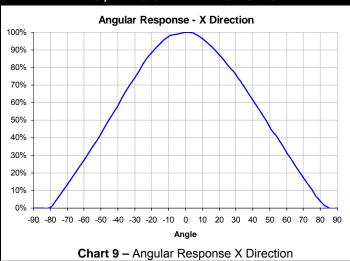

# ALS, ANGULAR RESPONSE

## ALS, ANGULAR RESPONSE

LX1977

Copyright © 2010 Rev. 1.0, 2010-03-25

Downloaded from Elcodis.com electronic components distributor

### **Microsemi** Analog Mixed Signal Group 11861 Western Avenue, Garden Grove, CA. 92841, 714-898-8121, Fax: 714-893-2570

Page 20

# LX1977

# **SMBus Ambient Light Sensor**

**PRODUCTION DATASHEET**

www.Microsemi.com

# LX1977

(SMBus) Ambient Light Sensor

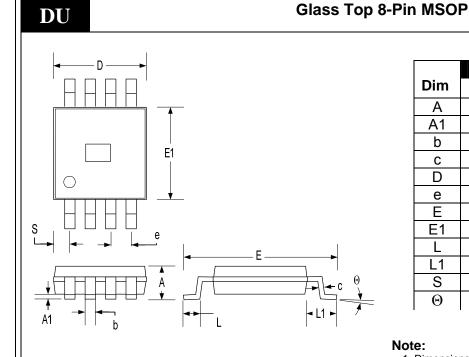

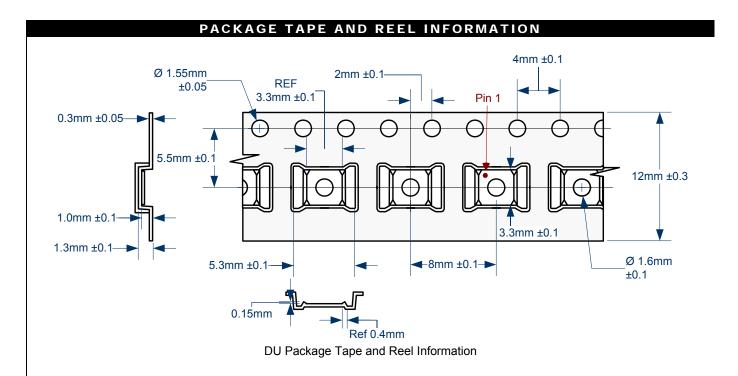

# PACKAGE DIMENSIONS

|     | MILLIM    | IETERS | INCHES    |       |  |

|-----|-----------|--------|-----------|-------|--|

| Dim | MIN       | MAX    | MIN       | MAX   |  |

| Α   | _         | 1.10   | _         | 0.043 |  |

| A1  | 0.05      | 0.15   | 0.002     | 0.006 |  |

| b   | 0.26      | 0.41   | 0.010     | 0.016 |  |

| С   | 0.13      | 0.23   | 0.005     | 0.009 |  |

| D   | 2.90      | 3.10   | 0.114     | 0.122 |  |

| е   | 0.65      | BSC    | 0.025 BSC |       |  |

| E   | 4.75      | 5.05   | 0.187     | 0.198 |  |

| E1  | 2.90      | 3.10   | 0.114     | 0.122 |  |

| L   | 0.41      | 0.71   | 0.016     | 0.028 |  |

| L1  | 0.95 BSC  |        | 0.037 BSC |       |  |

| S   | 0.525 BSC |        | 0.021 BSC |       |  |

| Θ   | 3°        |        | 3°        |       |  |

### Note:

1. Dimensions do not include mold flash or protrusions; these shall not exceed 0.155mm(.006") on any side. Lead dimension shall not include solder coverage.

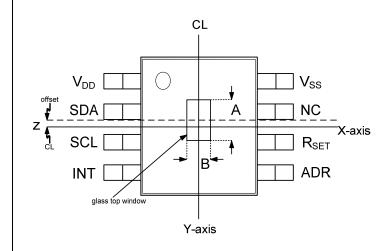

|     | MILLIMETERS | MILS |

|-----|-------------|------|

| Dim | Тур         | Тур  |

| Α   | 0.76        | 30   |

| В   | 0.5         | 20   |

| Z   | 0.2         | 7.8  |

#### Note:

- CL represents the centered X and Y axis of the 1. package.