## Boot Capacitor Regulation in LM25007 Constant-On-Time (COT) Converter

National Semiconductor Application Note 2129 Vijay Choudhary March 14, 2011

### The Issue

LM25000 series of constant-on-time (COT) integrated regulators provide a simple, cost-effective way of implementing a step down buck regulator with nearly fixed frequency. Nonsynchronous operation reduces switching frequency at very light load resulting in higher efficiency than a comparable fixed frequency converter. The non-synchronous operation, however, causes two problems related to boot capacitor regulation under certain operating conditions.

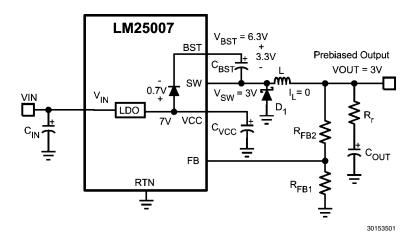

Bootstrap capacitor ( $C_{BST}$ ) may have insufficient voltage during startup if a voltage is present at the output of the converter

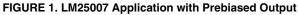

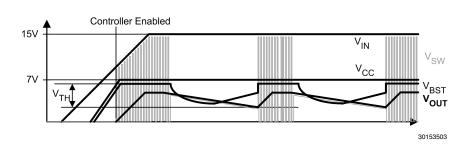

see *Figure 1*. This voltage is usually referred to as prebias. Since, at startup, there is no current in the inductor (L), the prebias voltage at the output appears at the switch node. If this prebias voltage is high such that the boot capacitor voltage  $(V_{BST}=V_{CC}-V_{SW})$  is lower than the threshold voltage  $(V_{TH})$  of high side gate, the high side switch fails to turn 'on' and the converter fails to startup see *Figure 2*. This condition persists until prebias is removed. A prebias is often caused by some leakage path in downstream circuits, e.g., a logic circuit or FPGA with a pin pulled high, or leftover charge from a previous power down.

A similar situation may occur under light load or no load conditions see *Figure 3*. At light load/no load, the inductor current is discontinuous causing the diode (D1) to turn off for a relatively long off time. During this time the bootstrap capacitor ( $C_{BST}$ ) may discharge to a level below the top side FET gate drive threshold ( $V_{TH}$ ), which is normally around 5V. Under these conditions the top side FET fails to turn on and the output voltage is no longer regulated. Since there is no current in the inductor, this output voltage appears at the switch node  $(V_{SW}=V_{OUT})$ . As  $V_{OUT}$ , and therefore VSW, drops, the bootstrap capacitor voltage rises and is given by  $V_{BST} = V_{CC}$ - $V_{OUT}$ . When  $V_{CC}$ - $V_{OUT} > V_{TH}$ , the hi-side FET turns on again and the switching resumes bringing the VOUT to the target level. At that time, if the low load condition persists, the whole cycle will repeat itself, causing a hiccup mode operation in which  $V_{OUT}$  fall to  $V_{CC}$ - $V_{TH}$  and rises back to the target level. This loss of regulation is undesirable in many applications.

AN-2129

FIGURE 3. Hiccup Mode Operation at No Load

### **The Solution**

For prebiased startup problem, the source of prebias should be removed if possible. If the prebias source is some leakage path in the downstream logic circuit, the system designer should consider the option of tying unused logic pin, which is the source of leakage, low. In some cases, this leakage path may be difficult to identify, or a necessary part of design. In other cases, the source of prebias may be a stiff source, e.g., a battery or super capacitor at the output of the converter. The system designer can choose from the techniques described below depending on the constraints of his design.

#### **INCREASING BOOT CAPACITOR (CBST)**

The designer can increase the boot capacitor value so that during no load boot capacitor is not discharged below the gate threshold of high side switch before  $V_{OUT}$ , and hence  $V_{FB}$ , falls below the reference. The hiccup free operation should be verified for whole input voltage ( $V_{IN}$ ) range. The designer

#### **RAISING VBST USING EXTERNAL CIRCUIT**

should not exceed the recommended boot capacitor value in the datasheet. This method does not help in case of prebiased output.

#### **REDUCING FEEDBACK RESISTORS (RFB1, RFB2)**

In no load condition, feedback Resistors, FB1 and FB2, constitute the total load at the output of the converter. These should be chosen so that  $V_{OUT}$  and hence  $V_{FB}$  fall below the reference level faster than  $V_{BST}$  falls below the gate threshold ( $V_{TH}$ ). The hiccup free operation should be verified for whole input voltage ( $V_{IN}$ ) range.

For prebiased outputs during startup, reducing the feedback resistors effectively pulls the V<sub>OUT</sub> and V<sub>SW</sub> closer to ground, thereby raising the boot capacitor ( $C_{BST}$ ) voltage. The extent of this pull down however depends on the strength and voltage level of the prebias source. This method of counteracting prebias is limited to weak prebias sources or leftover charge on output capacitor ( $C_{OUT}$ ) from previous power cycle.

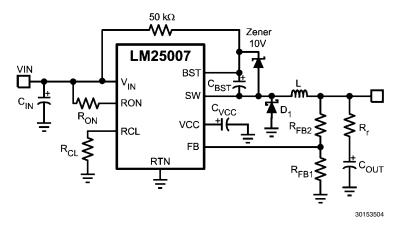

FIGURE 4. Raising Boot Capacitor Voltage Using External Circuit

If none of the simpler solutions presented above are sufficient, an external pull up circuit can be used to raise the boot capacitor voltage (V<sub>BST</sub>) above gate threshold (V<sub>TH</sub>) of high side switch. An example circuit is shown in *Figure 4*. The 50kΩ pull up resistor pulls BST pin up while limiting the current drawn from V<sub>IN</sub>. The 10V zener prevents the boot capacitor voltage

from exceeding the maximum voltage rating between BST and SW pins. This method is effective for no load as well as prebiased output conditions. The designer should select the pull up resistor to optimize the voltage drop across it and the power dissipation in the pull up resistor and the zener.

www.national.com

## Notes

AN-2129

# Notes

For more National Semiconductor product information and proven design tools, visit the following Web sites at: www.national.com

| Products                       |                              | Design Support                  |                                |

|--------------------------------|------------------------------|---------------------------------|--------------------------------|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH® Tools                  | www.national.com/webench       |

| Audio                          | www.national.com/audio       | App Notes                       | www.national.com/appnotes      |

| Clock and Timing               | www.national.com/timing      | Reference Designs               | www.national.com/refdesigns    |

| Data Converters                | www.national.com/adc         | Samples                         | www.national.com/samples       |

| Interface                      | www.national.com/interface   | Eval Boards                     | www.national.com/evalboards    |

| LVDS                           | www.national.com/lvds        | Packaging                       | www.national.com/packaging     |

| Power Management               | www.national.com/power       | Green Compliance                | www.national.com/quality/green |

| Switching Regulators           | www.national.com/switchers   | Distributors                    | www.national.com/contacts      |

| LDOs                           | www.national.com/ldo         | Quality and Reliability         | www.national.com/quality       |

| LED Lighting                   | www.national.com/led         | Feedback/Support                | www.national.com/feedback      |

| Voltage References             | www.national.com/vref        | Design Made Easy                | www.national.com/easy          |

| PowerWise® Solutions           | www.national.com/powerwise   | Applications & Markets          | www.national.com/solutions     |

| Serial Digital Interface (SDI) | www.national.com/sdi         | Mil/Aero                        | www.national.com/milaero       |

| Temperature Sensors            | www.national.com/tempsensors | SolarMagic™                     | www.national.com/solarmagic    |

| PLL/VCO                        | www.national.com/wireless    | PowerWise® Design<br>University | www.national.com/training      |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2010 National Semiconductor Corporation

For the most current product information visit us at www.national.com

AN-2129

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959

National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com

www.national.com