# FAN6754 Highly Integrated Green- Mode PWM Controller

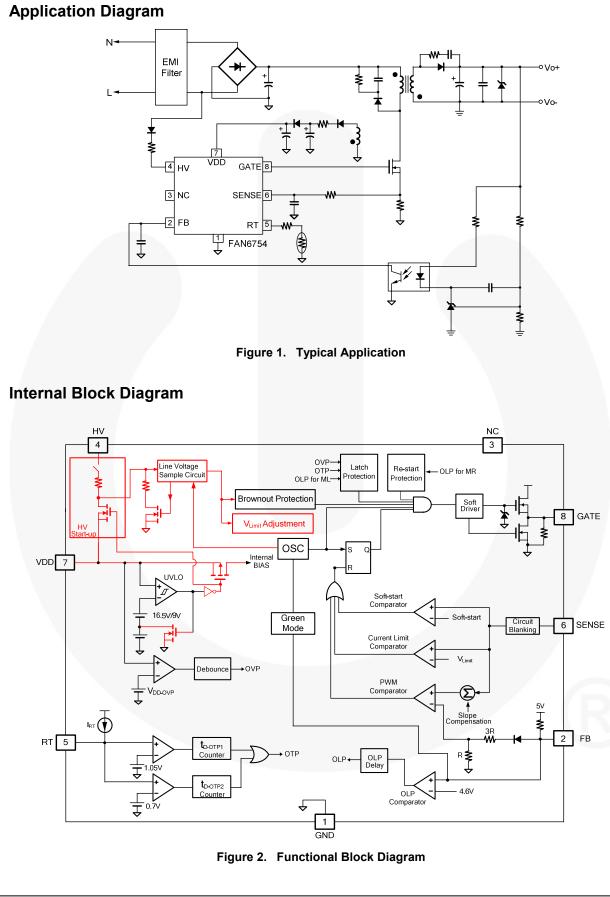

Brownout and V<sub>Limit</sub> Adjustment by HV Pin

## **Features**

- High-Voltage Startup

- AC Input Brownout Protection with Hysteresis

- Monitor HV to Adjust V<sub>Limit</sub>

- Low Operating Current: 1.7mA

- Linearly Decreasing PWM Frequency to 22KHz

- Frequency Hopping to Reduce EMI Emission

- Fixed PWM Frequency: 65KHz

- Peak-Current-Mode Control

- Cycle-by-Cycle Current Limiting

- Leading-Edge Blanking (LEB)

- Internal Open-Loop Protection

- GATE Output Maximum Voltage Clamp: 13V

- V<sub>DD</sub> Under-Voltage Lockout (UVLO)

- V<sub>DD</sub> Over-Voltage Protection (OVP)

- Programmable Over-Temperature Protection (OTP)

- Internal Latch Circuit (OVP, OTP)

- Open-Loop Protection (OLP); Restart for MR, Latch for ML

- Built-in 8ms Soft-Start Function

- Internal OTP Sensor with Hysteresis

# Applications

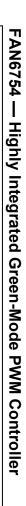

General-purpose switch-mode power supplies and flyback power converters, including:

Power Adapters

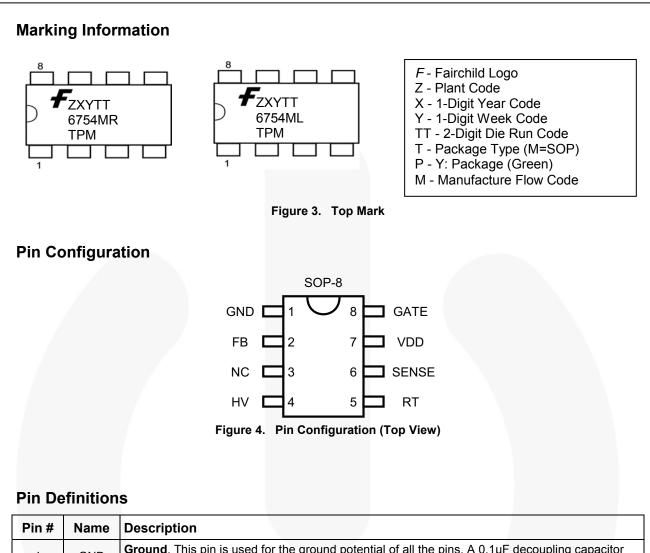

**Ordering Information**

## Description

The highly integrated FAN6754 PWM controller provides several features to enhance the performance of flyback converters. To minimize standby power consumption, a proprietary green-mode function provides off-time modulation to continuously decrease the switching frequency under light-load conditions.

Under zero-load and very light-load conditions, FAN6754 saves PWM pulses by entering deep burst mode. This burst mode function enables the power supply to meet international power conservation requirements.

FAN6754 integrates a frequency-hopping function internally to reduce EMI emission of a power supply with minimum line filters. Built-in synchronized slope compensation is accomplished by proprietary HV monitor to adjust  $V_{\text{Limit}}$  for constant output power limit over universal AC input range. Also, the gate output is clamped at 13V to protect the external MOSFET from over-voltage damage.

Other protection functions include AC input brownout protection with hysteresis and  $V_{\text{DD}}$  over-voltage protection. For over-temperature protection, an external NTC thermistor can be applied to sense the external switcher's temperature. When  $V_{\text{DD}}$  OVP or OTP are activated, an internal latch circuit is used to latch-off the controller. The latch mode is reset when the  $V_{\text{DD}}$  supply is removed.

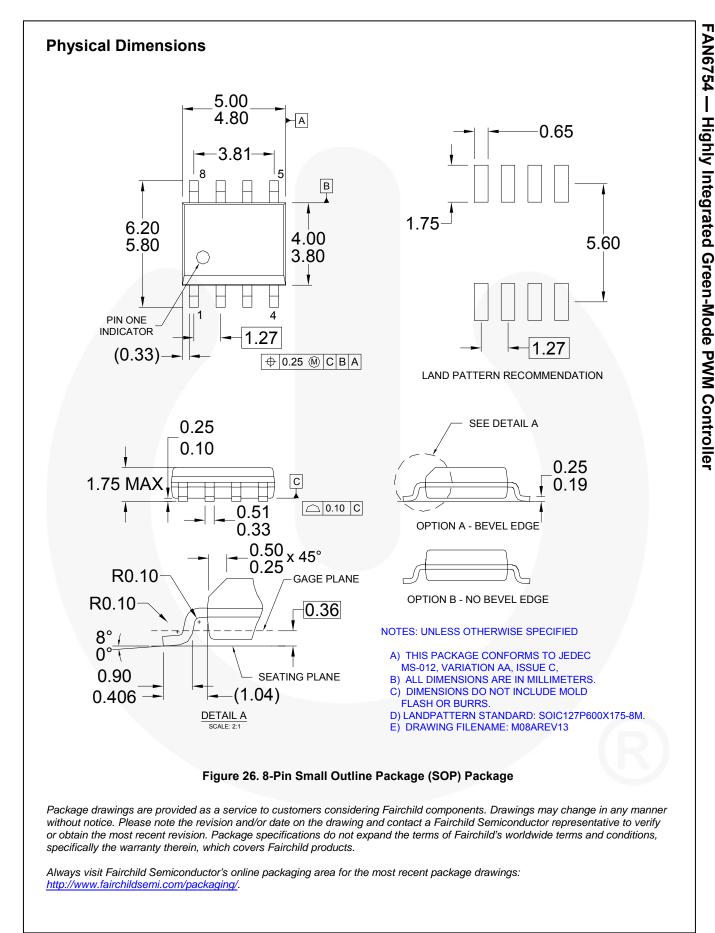

FAN6754 is available in an 8-pin SOP package.

| Part Number | Operating<br>Temperature<br>Range | Eco<br>Status | Package                            | Packing Method |  |

|-------------|-----------------------------------|---------------|------------------------------------|----------------|--|

| FAN6754MRMY | -40 to +105°C                     | Croon         | 9 Din Small Outling Deckage (SOD)  | Tana & Daal    |  |

| FAN6754MLMY | -40 t0 + 105 C                    | Green         | 8-Pin, Small Outline Package (SOP) | Tape & Reel    |  |

Ø For Fairchild's definition of Eco Status, please visit: <u>http://www.fairchildsemi.com/company/green/rohs\_green.html</u>.

© 2009 Fairchild Semiconductor Corporation FAN6754 • Rev. 1.0.1

www.fairchildsemi.com

© 2009 Fairchild Semiconductor Corporation FAN6754 • Rev. 1.0.1

| Pin # | Name  | Description                                                                                                                                                                                                                                                                                                                                                                                  |

|-------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | GND   | <b>Ground</b> . This pin is used for the ground potential of all the pins. A 0.1µF decoupling capacitor placed between VDD and GND is recommended.                                                                                                                                                                                                                                           |

| 2     | FB    | <b>Feedback</b> . The output voltage feedback information from the external compensation circuit is fed into this pin. The PWM duty cycle is determined by this pin and the current-sense signal from Pin 6. FAN6754 performs an open-loop protection (OLP); if the FB voltage is higher than a threshold voltage (around 4.6V) for more than 55ms, the controller latches off the PWM.      |

| 3     | NC    | No Connection.                                                                                                                                                                                                                                                                                                                                                                               |

| 4     | HV    | <b>High Voltage Startup</b> . This pin is connected to the line input via a 1N4007 and 200k0 resistors to achieve brownout and high/low line compensation. Once the voltage on the HV pin is lower than the brownout voltage, PWM output turns off. High/low line compensation dominates the cycle-by-cycle current limiting to achieve constant output power limiting with universal input. |

| 5     | RT    | <b>Over-Temperature Protection</b> . An external NTC thermistor is connected from this pin to GND. The impedance of the NTC decreases at high temperatures. Once the voltage on the RT pin drops below the threshold voltage, the controller latches off the PWM.                                                                                                                            |

| 6     | SENSE | <b>Current Sense</b> . This pin is used to sense the MOSFET current for the current-mode PWM and current limiting.                                                                                                                                                                                                                                                                           |

| 7     | VDD   | <b>Supply Voltage</b> . IC operating current and MOSFET driving current are supplied using this pin.<br>This pin is connected to an external bulk capacitor of typically 47µF. The threshold voltage for turn-on and turn-off is 16.5V and 9V, respectively. The operating current is lower than 2mA.                                                                                        |

| 8     | GATE  | <b>Gate Drive Output</b> . The totem-pole output driver for the power MOSFET. It is internally clamped below 13V.                                                                                                                                                                                                                                                                            |

© 2009 Fairchild Semiconductor Corporation FAN6754 • Rev. 1.0.1

FAN6754 — Highly Integrated Green-Mode PWM Controller

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol             | Parameter                                           |                                   | Min. | Max. | Unit |

|--------------------|-----------------------------------------------------|-----------------------------------|------|------|------|

| V <sub>VDD</sub>   | DC Supply Voltage <sup>(1, 2)</sup>                 |                                   |      | 30   | V    |

| V <sub>FB</sub>    | FB Pin Input Voltage                                |                                   | -0.3 | 7.0  | V    |

| V <sub>SENSE</sub> | SENSE Pin Input Voltage                             |                                   | -0.3 | 7.0  | V    |

| V <sub>RT</sub>    | RT Pin Input Voltage                                |                                   | -0.3 | 7.0  | V    |

| V <sub>HV</sub>    | HV Pin Input Voltage                                |                                   |      | 500  | V    |

| PD                 | Power Dissipation (T <sub>A</sub> <50°C)            |                                   |      | 400  | mW   |

| $\Theta_{JA}$      | Thermal Resistance (Junction-to-Air)                |                                   |      | 141  | °C/W |

| TJ                 | Operating Junction Temperature                      |                                   | -40  | +125 | °C   |

| T <sub>STG</sub>   | Storage Temperature Range                           |                                   | -55  | +150 | °C   |

| TL                 | Lead Temperature (Wave Soldering or IR, 10 Seconds) |                                   |      | +260 | °C   |

| ESD                | Electrostatic Discharge Capability,                 | Human Body Model,<br>JESD22-A114  |      | 4.5  | kV   |

| ESD                | All pins except HV pin                              | Charged Device Model, JESD22-C101 |      | 1500 | V    |

Notes:

1. All voltage values, except differential voltages, are given with respect to the network ground terminal.

2. Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device.

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol          | Parameter                     | Conditions | Min. | Тур. | Max. | Unit |

|-----------------|-------------------------------|------------|------|------|------|------|

| TA              | Operating Ambient Temperature |            | -40  |      | +105 | °C   |

| R <sub>HV</sub> | HV Startup Resistor           |            | 150  | 200  | 250  | k50  |

| FAN6754 — H      |

|------------------|

| ighly l          |

| ntegrated Green- |

| Green-Mode P     |

| PWM              |

| WM Controller    |

-

## **Electrical Characteristics**

$V_{DD}$ =15V and T<sub>A</sub>=25°C unless otherwise noted.

| Symbol                 | Parameter                                                                          | Conditions                                                          | Min.                        | Тур.                        | Max.                        | Units |

|------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------|-----------------------------|-----------------------------|-------|

| V <sub>DD</sub> Sectio | on                                                                                 |                                                                     | •                           |                             |                             |       |

| V <sub>OP</sub>        | Continuously Operating Voltage                                                     |                                                                     |                             |                             | 24                          | V     |

| V <sub>DD-ON</sub>     | Start Threshold Voltage                                                            |                                                                     | 15.5                        | 16.5                        | 17.5                        | V     |

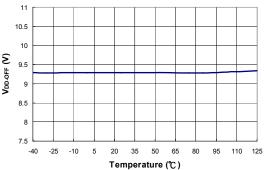

| $V_{\text{DD-OFF}}$    | Minimum Operating Voltage                                                          |                                                                     | 8                           | 9                           | 10                          | V     |

| V <sub>DD-OLP</sub>    | I <sub>DD-OLP</sub> Off Voltage                                                    |                                                                     | 5.5                         | 6.5                         | 7.5                         | V     |

| $V_{\text{DD-LH}}$     | Threshold Voltage on VDD Pin for<br>Latch-Off Release Voltage                      |                                                                     | 3.5                         | 4.0                         | 4.5                         | V     |

| V <sub>DD-AC</sub>     | Threshold Voltage on VDD Pin for<br>Disable AC recovery to avoid<br>Startup Failed |                                                                     | V <sub>DD-OFF</sub><br>+2.5 | V <sub>DD-OFF</sub><br>+3.0 | V <sub>DD-OFF</sub><br>+3.5 | V     |

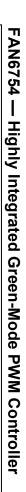

| I <sub>DD-ST</sub>     | Startup Current                                                                    | V <sub>DD-ON</sub> – 0.16V                                          |                             |                             | 30                          | μA    |

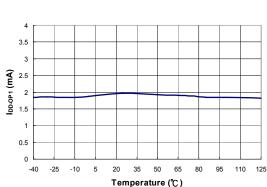

| IDD-OP1                | Operating Supply Current when<br>PWM operation                                     | V <sub>DD</sub> =20V, FB=3V Gate<br>Open                            |                             | 1.7                         | 2.0                         | mA    |

| I <sub>DD-OP2</sub>    | Operating Supply Current when<br>Gate Stop                                         | V <sub>DD</sub> =20V, FB=3V                                         |                             | 1.2                         | 1.5                         | mA    |

| I <sub>LH</sub>        | Operating Current at PWM-Off<br>Phase Under Latch-Off<br>Conduction                | V <sub>DD</sub> =5V                                                 | 30                          | 60                          | 90                          | μA    |

| I <sub>DD-OLP</sub>    | Internal Sink Current Under Latch-<br>Off Conduction                               | V <sub>DD-OLP</sub> +0.1V                                           | 170                         | 200                         | 230                         | μA    |

| V <sub>DD-OVP</sub>    | V <sub>DD</sub> Over-Voltage Protection                                            |                                                                     | 24                          | 25                          | 26                          | V     |

| t <sub>d-vddovp</sub>  | V <sub>DD</sub> Over-Voltage Protection<br>Debounce Time                           |                                                                     | 75                          | 165                         | 255                         | μs    |

| HV Sectio              | n                                                                                  |                                                                     |                             |                             |                             |       |

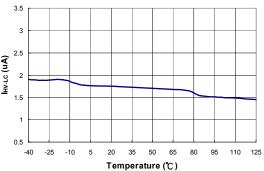

| I <sub>HV</sub>        | Supply Current from HV Pin                                                         | V <sub>AC</sub> =90V(V <sub>DC</sub> =120V),<br>V <sub>DD</sub> =0V | 1.50                        | 2.75                        | 4.00                        | mA    |

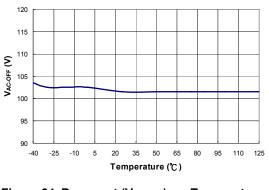

| V <sub>AC-OFF</sub>    | Brownout Threshold                                                                 | DC Source Series<br>R=200k $\Omega$ to HV Pin<br>See Equation 1     | 92                          | 102                         | 112                         | V     |

| V <sub>AC-ON</sub>     | Brownin Threshold                                                                  | DC Source Series<br>R=200k $\Omega$ to HV Pin<br>See Equation 2     | 104                         | 114                         | 124                         | V     |

| $	riangle V_{AC}$      | V <sub>AC-ON</sub> - V <sub>AC-OFF</sub>                                           | DC Source Series<br>R=200kΩ to HV Pin                               | 6                           | 12                          | 18                          | V     |

| 4                      | Line Voltage Comple Ovela                                                          | FB > V <sub>FB-N</sub>                                              |                             | 220                         |                             |       |

| ts-cycle               | Line Voltage Sample Cycle                                                          | FB < V <sub>FB-G</sub>                                              |                             | 650                         |                             | μs    |

| t <sub>H-TIME</sub>    | Line Voltage Hold Period                                                           |                                                                     |                             | 20                          |                             | μs    |

| 4                      |                                                                                    | FB > V <sub>FB-N</sub>                                              | 65                          | 75                          | 85                          | ms    |

| t <sub>D-AC-OFF</sub>  | PWM Turn-off Debounce Time                                                         | FB < V <sub>FB-G</sub>                                              | 180                         | 235                         | 290                         | ms    |

Continued on the following page...

© 2009 Fairchild Semiconductor Corporation FAN6754 • Rev. 1.0.1

5

© 2009 Fairchild Semiconductor Corporation FAN6754 • Rev. 1.0.1

FAN6754 — Highly Integrated Green-Mode PWM Controller

# Electrical Characteristics (Continued)

$V_{\text{DD}}\text{=}15V$  and  $T_{\text{A}}\text{=}25^{\circ}\text{C}$  unless otherwise noted.

| Symbol               | Parameter                                         | Conditions                                 | Min.  | Тур.  | Max.  | Units |

|----------------------|---------------------------------------------------|--------------------------------------------|-------|-------|-------|-------|

| Oscillator           | Section                                           |                                            |       |       |       | •     |

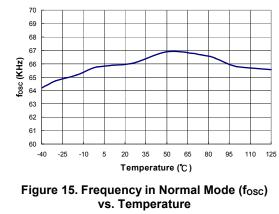

| 4                    | Fraguescuis Namel Made                            | Center Frequency                           | 61    | 65    | 69    |       |

| fosc                 | Frequency in Normal Mode                          | Hopping Range                              | ±3.7  | ±4.2  | ±4.7  | KHz   |

| <b>t</b>             | Honning Doried                                    | FB > V <sub>FB<sup>-</sup>N</sub>          | 3.9   | 4.4   | 4.9   | ms    |

| t <sub>HOP</sub>     | Hopping Period                                    | FB=V <sub>FB</sub> -G                      | 10.2  | 11.5  | 12.8  | ms    |

| fosc-g               | Green-Mode Frequency                              |                                            | 19    | 22    | 25    | KHz   |

| $\mathbf{f}_{DV}$    | Frequency Variation vs. V <sub>DD</sub> Deviation | V <sub>DD</sub> =11V to 22V                |       |       | 5     | %     |

| f <sub>DT</sub>      | Frequency Variation vs. Temperature Deviation     | T <sub>A</sub> =-40 to +105°C              |       |       | 5     | %     |

| Feedback             | Input Section                                     |                                            | É .   |       |       |       |

| Av                   | Input Voltage to Current-Sense Attenuation        |                                            | 1/4.5 | 1/4.0 | 1/3.5 | V/V   |

| Z <sub>FB</sub>      | Input Impedance                                   |                                            | 14    | 16    | 18    | kΩ    |

| $V_{\text{FB-OPEN}}$ | Output High Voltage                               | FB Pin Open                                | 4.8   | 5.0   | 5.2   | V     |

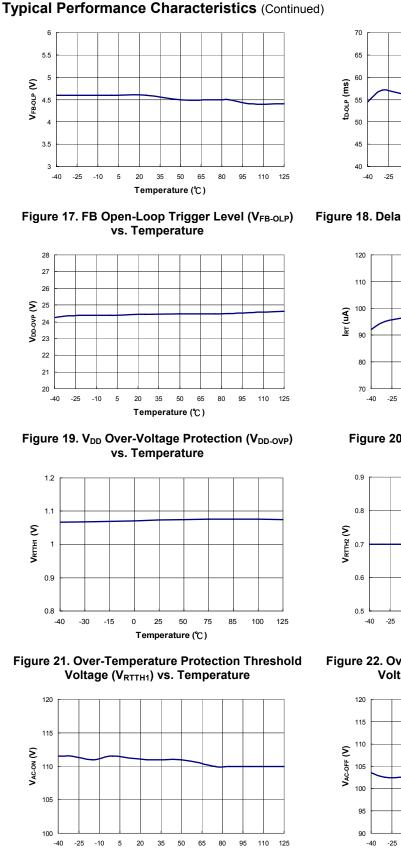

| $V_{FB-OLP}$         | FB Open-Loop Trigger Level                        |                                            | 4.3   | 4.6   | 4.9   | V     |

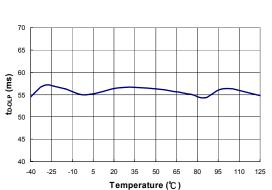

| t <sub>D-OLP</sub>   | Delay Time of FB Pin Open-Loop Protection         |                                            | 50    | 55    | 60    | ms    |

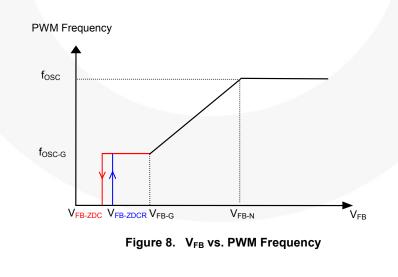

| V <sub>FB-N</sub>    | Green-Mode Entry FB Voltage                       | Pin, FB Voltage<br>(FB=V <sub>FB-N</sub> ) | 2.6   | 2.8   | 3.0   | V     |

|                      |                                                   | Hopping Range                              | ±3.7  | ±4.2  | ±4.7  | kHz   |

| V <sub>FB-G</sub>    | Green-Mode Ending FB Voltage                      | Pin, FB Voltage<br>(FB=V <sub>FB-G</sub> ) | 2.1   | 2.3   | 2.5   | V     |

|                      |                                                   | Hopping Range                              | ±1.27 | ±1.45 | ±1.62 | kHz   |

| $V_{\text{FB-ZDCR}}$ | FB Threshold Voltage for Zero-Duty Recovery       |                                            | 1.9   | 2.1   | 2.3   | V     |

| V <sub>FB-ZDC</sub>  | FB Threshold Voltage for Zero-Duty                |                                            | 1.8   | 2.0   | 2.2   | V     |

Continued on the following page ...

© 2009 Fairchild Semiconductor Corporation FAN6754 • Rev. 1.0.1

|                             | and T <sub>A</sub> =25°C unless otherwise noted.    |                                                               |       |                      |       |       |

|-----------------------------|-----------------------------------------------------|---------------------------------------------------------------|-------|----------------------|-------|-------|

| Symbol                      | Parameter                                           | Conditions                                                    | Min.  | Тур.                 | Max.  | Units |

| Feedback                    | Input Section                                       |                                                               |       |                      |       |       |

| Current-S                   | ense Section                                        |                                                               |       |                      |       |       |

| t <sub>PD</sub>             | Delay to Output                                     |                                                               |       | 100                  | 250   | ns    |

| t <sub>LEB</sub>            | Leading Edge Blanking Time                          |                                                               | 230   | 280                  | 330   | ns    |

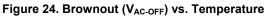

| V <sub>Limit-L</sub>        | Current Limit at Low Line (V <sub>AC</sub> =86V)    | $V_{DC}$ =122V, Series R=200k $\Omega$ to HV                  | 0.43  | 0.46                 | 0.49  | V     |

| V <sub>Limit-H</sub>        | Current Limit tat High Line (V <sub>AC</sub> =259V) | $V_{DC}$ =366V, Series R=200k $\Omega$ to HV                  | 0.36  | 0.39                 | 0.42  | V     |

| tss                         | Period During Soft-Start Time                       | Startup Time                                                  | 7     | 8                    | 9     | ms    |

| GATE Sec                    | ction                                               |                                                               |       |                      |       |       |

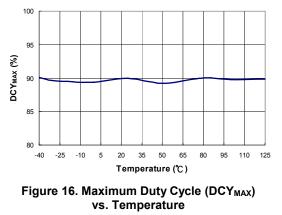

| $DCY_{MAX}$                 | Maximum Duty Cycle                                  |                                                               | 86    | 89                   | 92    | %     |

| $V_{\text{GATE-L}}$         | Gate Low Voltage                                    | V <sub>DD</sub> =15V, I <sub>O</sub> =50mA                    |       |                      | 1.5   | V     |

| V <sub>GATE-H</sub>         | Gate High Voltage                                   | V <sub>DD</sub> =12V, I <sub>O</sub> =50mA                    | 8     |                      |       | V     |

| tr                          | Gate Rising Time                                    | $V_{DD}$ =15V, C <sub>L</sub> =1nF                            |       | 100                  |       | ns    |

| t <sub>f</sub>              | Gate Falling Time                                   | V <sub>DD</sub> =15V, C <sub>L</sub> =1nF                     |       | 50                   |       | ns    |

| V <sub>GATE-</sub><br>CLAMP | Gate Output Clamping Voltage                        | V <sub>DD</sub> =22V                                          | 9     | 13                   | 17    | V     |

| RT Sectio                   | n                                                   |                                                               |       |                      |       |       |

| R <sub>RT</sub>             | Internal Resistor from RT Pin                       |                                                               | 9.50  | 10.55                | 11.60 | KΩ    |

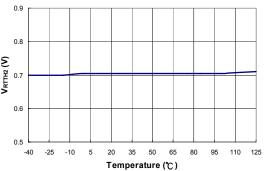

| V <sub>RTTH1</sub>          | Over-Temperature Protection Threshold               | $0.7V < V_{RT} < 1.05V$ , after 12ms Latch Off                | 1.000 | 1.035                | 1.070 | v     |

| V <sub>RTTH2</sub>          | Voltage                                             | V <sub>RT</sub> < 0.7V, After 100µs<br>Latch Off              | 0.65  | 0.70                 | 0.75  | v     |

|                             |                                                     | $V_{RTTH2} < V_{RT} < V_{RTTH1}$<br>FB > $V_{FB-N}$           | 14    | 16                   | 18    |       |

| t <sub>D-OTP1</sub>         | Over-Temperature Latch-Off Debounce                 | $V_{RTTH2} < V_{RT} < V_{RTTH1}$<br>FB < $V_{FB-G}$           | 40    | 51                   | 62    | ms    |

|                             |                                                     | $V_{RT} < V_{RTTH2}$ , FB > $V_{FB-N}$                        | 110   | 185                  | 260   |       |

| t <sub>D-OTP2</sub>         |                                                     | V <sub>RT</sub> < V <sub>RTTH2</sub> , FB < V <sub>FB-G</sub> | 320   | 605                  | 890   | μs    |

| Over-Tem                    | perature Protection Section (OTP)                   |                                                               |       |                      |       |       |

| T <sub>OTP</sub>            | Protection Junction Temperature                     |                                                               |       | +135                 |       | °C    |

| T <sub>Restart</sub>        | Restart Junction Temperature                        |                                                               |       | T <sub>OTP</sub> -25 | /     | °C    |

© 2009 Fairchild Semiconductor Corporation FAN6754 • Rev. 1.0.1

Downloaded from **Elcodis.com** electronic components distributor

Temperature (°C)

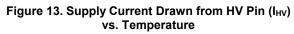

Figure 10. Operation Supply Current (IDD-OP1) vs. Temperature

Figure 12. Minimum Operating Voltage (VDD-OFF) vs. Temperature

Figure 14. HV Pin Leakage Current After Startup (I<sub>HV-LC</sub>) vs. Temperature

© 2009 Fairchild Semiconductor Corporation FAN6754 • Rev. 1.0.1

FAN6754 — Highly Integrated Green-Mode PWM Controller

Figure 23. Brownin (V<sub>AC-ON</sub>) vs. Temperature

Temperature (°C)

Figure 18. Delay Time of FB Pin Open-Loop Protection (t<sub>D-OLP</sub>) vs. Temperature

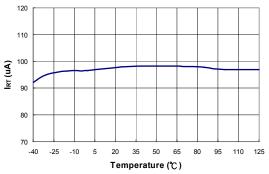

Figure 20. Output Current from RT Pin (I<sub>RT</sub>) vs. Temperature

Figure 22. Over-Temperature Protection Threshold Voltage (V<sub>RTTH2</sub>) vs. Temperature

© 2009 Fairchild Semiconductor Corporation FAN6754 • Rev. 1.0.1

П

## **Functional Description**

#### **Startup Current**

For startup, the HV pin is connected to the line input through an external diode and resistor;  $R_{HV}$ , (1N4007 / 150K $\Omega$  recommended). Peak startup current drawn from the HV pin is ( $V_{AC} \times \sqrt{2}$ ) /  $R_{HV}$  and charges the hold-up capacitor through the diode and resistor. When the  $V_{DD}$  capacitor level reaches  $V_{DD-ON}$ , the startup current switches off. At this moment, the  $V_{DD}$  capacitor only supplies the FAN6754 to keep the  $V_{DD}$  until the auxiliary winding of the main transformer provides the operating current.

## **Operating Current**

Operating current is around 1.7mA. The low operating current enables better efficiency and reduces the requirement of  $V_{DD}$  hold-up capacitance.

### **Green-Mode Operation**

The proprietary green-mode function provides off-time modulation to reduce the switching frequency in light-load and no-load conditions.  $V_{FB}$ , which is derived from the voltage feedback loop, is taken as the reference. Once  $V_{FB}$  is lower than the threshold voltage ( $V_{FB-N}$ ), switching frequency is continuously decreased to the minimum green-mode frequency of around 22KHz.

#### **Current Sensing / PWM Current Limiting**

Peak-current-mode control is utilized to regulate output voltage and provide pulse-by-pulse current limiting. The switch current is detected by a sense resistor into the SENSE pin. The PWM duty cycle is determined by this current-sense signal and V<sub>FB</sub>, the feedback voltage. When the voltage on the SENSE pin reaches around V<sub>COMP</sub> = (V<sub>FB</sub>-0.6)/4, the switch cycle is terminated immediately. V<sub>COMP</sub> is internally clamped to a variable voltage around 0.46V for low-line output power limit.

## Leading-Edge Blanking (LEB)

Each time the power MOSFET is switched on, a turn-on spike occurs on the sense-resistor. To avoid premature termination of the switching pulse, a leading-edge blanking time is built in. During this blanking period, the current-limit comparator is disabled and cannot switch off the gate driver.

## **Under-Voltage Lockout (UVLO)**

The turn-on and turn-off thresholds are fixed internally at 16.5V and 9V, respectively. During startup, the hold-up capacitor must be charged to 16.5V through the startup resistor to enable the IC. The hold-up capacitor continues to supply  $V_{DD}$  until the energy can be delivered from auxiliary winding of the main transformer.  $V_{DD}$  must not drop below 9V during startup. This UVLO hysteresis window ensures that hold-up capacitor is adequate to supply  $V_{DD}$  during startup.

## Gate Output / Soft Driving

The BiCMOS output stage is a fast totem-pole gate driver. Cross conduction has been avoided to minimize heat dissipation, increase efficiency, and enhance reliability. The output driver is clamped by an internal 13V Zener diode to protect power MOSFET transistors against undesirable gate over voltage. A soft driving waveform is implemented to minimize EMI.

#### Soft-Start

For many applications, it is necessary to minimize the inrush current at startup. The built-in 8ms soft-start circuit significantly reduces the startup current spike and output voltage overshoot.

#### **Slope Compensation**

The sensed voltage across the current-sense resistor is used for peak-current-mode control and cycle-by-cycle current limiting. Built-in slope compensation improves stability and prevents sub-harmonic oscillation. FAN6754 inserts a synchronized, positive-going, ramp at every switching cycle.

### **Constant Output Power Limit**

When the SENSE voltage across sense resistor R<sub>SENSE</sub> reaches the threshold voltage, around 0.46V for low-line condition, the output GATE drive is turned off after a small delay, t<sub>PD</sub>. This delay introduces an additional current proportional to t<sub>PD</sub> • V<sub>IN</sub> / L<sub>P</sub>. Since the delay is nearly constant regardless of the input voltage V<sub>IN</sub>, higher input voltage results in a larger additional current and the output power limit is higher than under low input line voltage. To compensate this variation for a wide AC input range, a power-limiter is controlled by the HV pin to solve the unequal power-limit problem. The power limiter is fed to the inverting input of the current limiting comparator. This results in a lower current limit at high-line inputs than at low-line inputs.

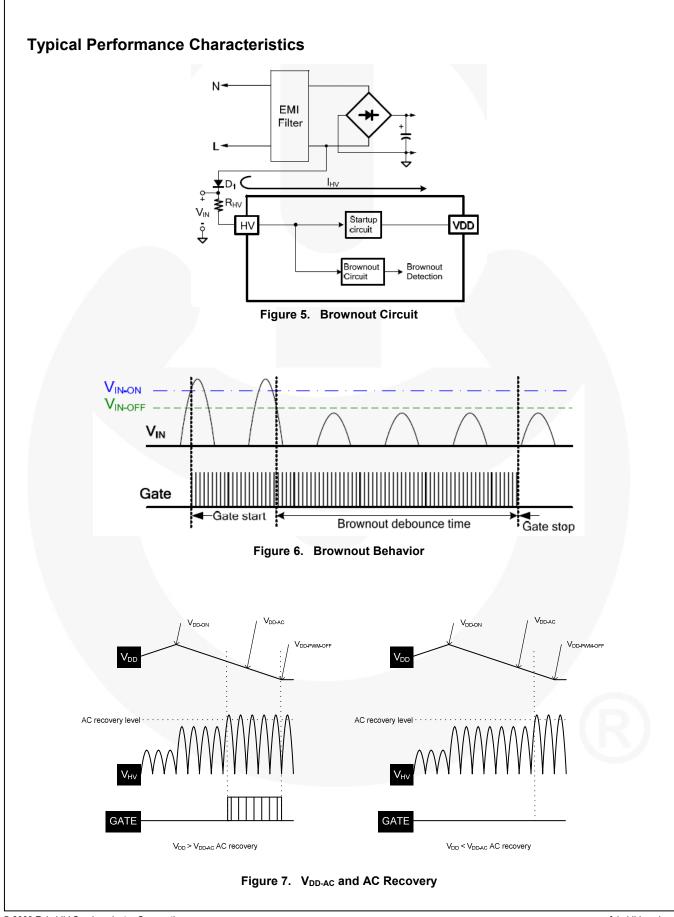

# Brownout and Constant Power Limited by HV Pin

Unlike previous PWM controllers, FAN6754's HV pin can detect the AC line voltage brownout function and adjust the current limit level. Using a fast diode and startup resistor to sample the AC line voltage, the peak value refreshes and is stored in a register at each sampling cycle. When internal update time is met, this peak value is used for brownout and current-limit level judgment. Equation 1 and 2 calculate the level of brownin or brownout converted to RMS value. For power saving, FAN6754 enlarges the sampling cycle to lower the power loss from HV sampling at light load condition.

$$V_{AC-ON}(RMS) = (0.9V \times \frac{(R_{HV} + 1.6)}{1.6}) / \sqrt{2}$$

(1)

$$V_{AC-OFF}(RMS) = (0.81V \times \frac{(R_{HV}+1.6)}{1.6}) / \sqrt{2}$$

; the unit of  $R_{HV}$  is k $\Omega$  (2)

© 2009 Fairchild Semiconductor Corporation FAN6754 • Rev. 1.0.1 The HV pin can perform current limit to shrink the tolerance of OCP (Over-Current Protection) under full range of AC voltage, to linearly current limit curve as shown in Figure 25. FAN6754 also shrinks the  $V_{\text{limit}}$  level by half to lower the  $I^2R_{\text{SENSE}}$  loss to increase the heavy-load efficiency.

#### Figure 25. Linearly Current Limit Curve

#### **V**<sub>DD</sub> Over-Voltage Protection (OVP)

$V_{\text{DD}}$  over-voltage protection prevents damage due to abnormal conditions. If the  $V_{\text{DD}}$  voltage is over the over-voltage protection voltage ( $V_{\text{DD-OVP}}$ ) and lasts for  $t_{\text{D-VDDOVP}}$ , the PWM pulses are disabled until the  $V_{\text{DD}}$  voltage drops below the UVLO, then starts again. Over-voltage conditions are usually caused by open feedback loops.

#### **Thermal Protection**

An NTC thermistor,  $R_{NTC}$ , in series with resistor  $R_A$ , can be connected from the RT pin to ground. A constant current  $I_{RT}$  is output from the RT pin. The voltage on the RT pin can be expressed as  $V_{RT}=I_{RT} \cdot (R_{NTC} + R_{PTC})$ , where  $I_{RT}$  is 100µA. At high ambient temperature,  $R_{NTC}$ is smaller, such that  $V_{RT}$  decreases. When  $V_{RT}$  is less than 1.035V ( $V_{RTTH1}$ ), the PWM turns off after 16ms ( $t_{D-OTP1}$ ). If  $V_{RT}$  is less than 0.7V ( $V_{RTTH2}$ ), PWM turns off after 185µs ( $t_{D-OTP2}$ ).

#### **Limited Power Control**

The FB voltage increases every time the output of the power supply is shorted or overloaded. If the FB voltage remains higher than a built-in threshold for longer than  $t_{D-OLP}$ , PWM output is turned off. As PWM output is turned off,  $V_{DD}$  begins decreasing.

When  $V_{DD}$  goes below the turn-off threshold (9V) the controller is totally shut down and,  $V_{DD}$  is continuously discharged to  $V_{DD-OLP}$  (6.5V) by  $I_{DD-OLP}$  to lower the average input power. This is called two-level UVLO.  $V_{DD}$  is cycled again. This protection feature continues as long as the overloading condition persists. This prevents the power supply from overheating due to overloading conditions.

#### **Noise Immunity**

Noise on the current sense or control signal may cause significant pulse-width jitter, particularly in continuousconduction mode. Slope compensation helps alleviate this problem. Good placement and layout practices should be followed. Avoiding long PCB traces and component leads, locating compensation and filter components near the FAN6754, and increasing the power MOS gate resistance improve performance.

© 2009 Fairchild Semiconductor Corporation FAN6754 • Rev. 1.0.1

© 2009 Fairchild Semiconductor Corporation FAN6754 • Rev. 1.0.1

## EZSWITCH™\* E-7

Fairchild® Fairchild Semiconductor® FACT Quiet Series™ FACT FAST® FastvCore™ FETBench™

MegaBuck™ MICROCOUPLER™ MicroFET™ MicroPak™ MicroPak2™ MillerDrive™ MotionMax™ Motion-SPM™ OptoHiT™ OPTOLOGIC<sup>®</sup> **OPTOPLANAR®**

SignalWise™ SmartMax™ SMART START SPM<sup>6</sup> **STEALTH™** SuperFET™ SuperSOT™-3 SuperSOT™-6 SuperSOT™-8 SupreMOS™ SyncFET™ Sync-Lock™

#### GENERAL The Power Franchise® wer

TinyBoost™

TinyBuck™

TinyCalc™

TinyLogic<sup>®</sup>

TINYOPTOM

TinyPower™

П

AN6754 — Highly Integrated Green-Mode PWM Controller

TinyPVM™ TinyWire™ TriFault Detect™ TRUECURRENT\*\* µSerDes™ UHC Ultra FRFET™ UniFET™ VCXTM VisualMax<sup>™</sup>

XS™

\* Trademarks of System General Corporation, used under license by Fairchild Semiconductor.

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELABILITY, FUNCTION, OR DESIGN, FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN, NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

As used herein

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- 2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com, under Sales Support

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

#### PRODUCT STATUS DEFINITIONS

| Datasheet Identification | Product Status        | Definition                                                                                                                                                                                             |

|--------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in<br>any manner without notice.                                                                       |

| Preliminary              | First Production      | Datasheet contains preliminary data, supplementary data will be published at a later date. Fairchild<br>Semiconductor reserves the right to make changes at any time without notice to improve design. |

| No Identification Needed | Full Production       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes<br>at any time without notice to improve the design.                                               |

| Obsolete                 | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor.<br>The datasheet is for reference information only.                                                    |

Rev. 146

© 2009 Fairchild Semiconductor Corporation FAN6754 • Rev. 1.0.1